1

Изобретение относится к .вычислительной технике и вдожет быть использовано в качестве самостоятельного функционального блока, обеснечивающего предварительную обработку информации с частотных датчиков при стыковке их с ЦВМ, а также ш /составе вычислительных устройств, предназначенных для непосредственной обработки частотно-И1Мпульсных сигналов.

Известно аналого-цифровое устройство для воспроизведения функций двух переменных, основанное на интерполяционном полиноме Лагранжа в кусочно-линейной логической форме, содержащее входные лреобразователи, запоминающий блок, интерполятор и блок оценки.

Однако этим устройствам свойственна низкая точность реализации функциональной зависимости (xiy), обусловленная погрещностями аналого-цифровых преобразований, а также погрещностью сложной аналоговой части преобразователя-интерполятора.

Цель -изобретения - псувыщение. точности функционального преобразования при сохранении непрерывного характера обработки информации. Для осуществления этой цели в устройство введены блок сравнения, делители частоты, блок формирования частоты коррекции, реверсивный счетчИк, схемы «И и «ИЛИ, причем входы блока сравнения соединены соответственно со вторым входом устройства и выходом одного из делителей частоты, установочный вход которого подключен к одно1му из выходов блока сравнения, два других выхода блока сравнення соединены с первыми входами схем «И, вторые входы которых через блок формирования частот коррекция подключены к выходам интерполятора, ОД1ИЦ из (ВЫХОДОВ которого связан с входами делителей частоты; выходы схем «И подключены к первым входам схем «ИЛИ, /вторые входы которых соединены соответственно со вторььм входом устройства и с выходом второго делителя частоты, выходы схем «ИЛИ .подключены к входам реверсивного счетчика, выходы состояний которого соединены с входами интерполятора и запоминающего блока, другие входы которого подключены к выходам состояний триггеров преобразователя частота-код, частотным входом соединенного с интерполятором, а кодовые выходы запоминающего блока подключены к соответствующим входам блока формирования частоты коррекции.

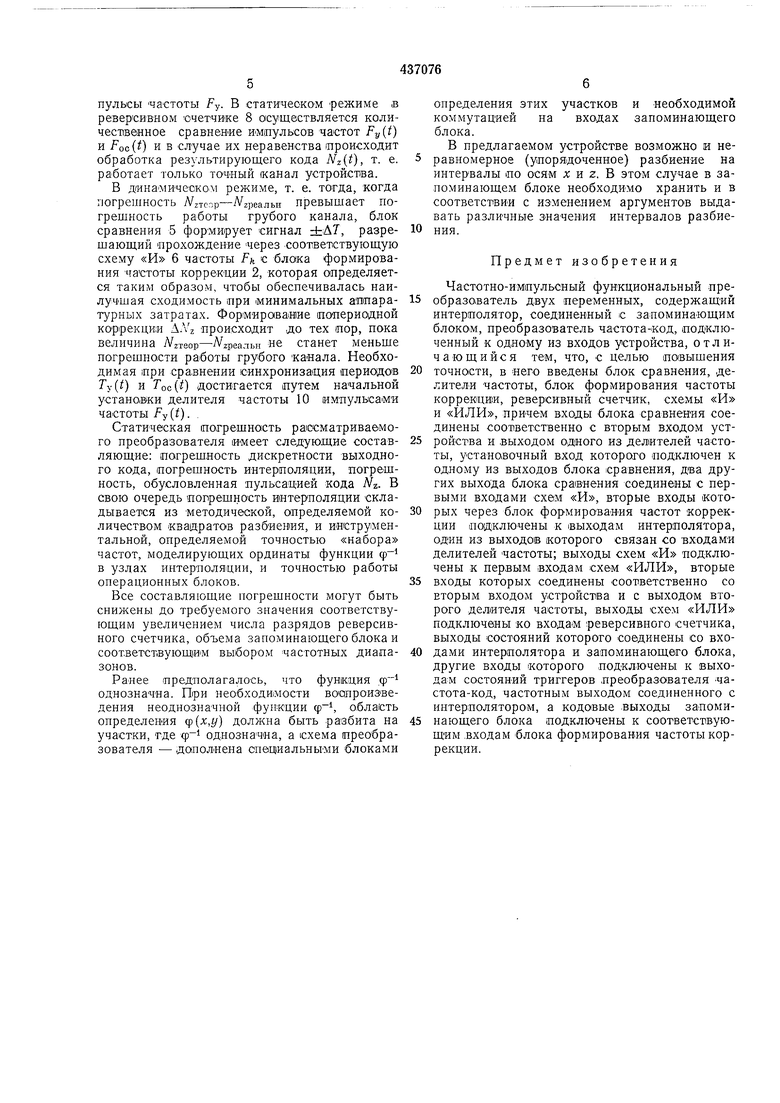

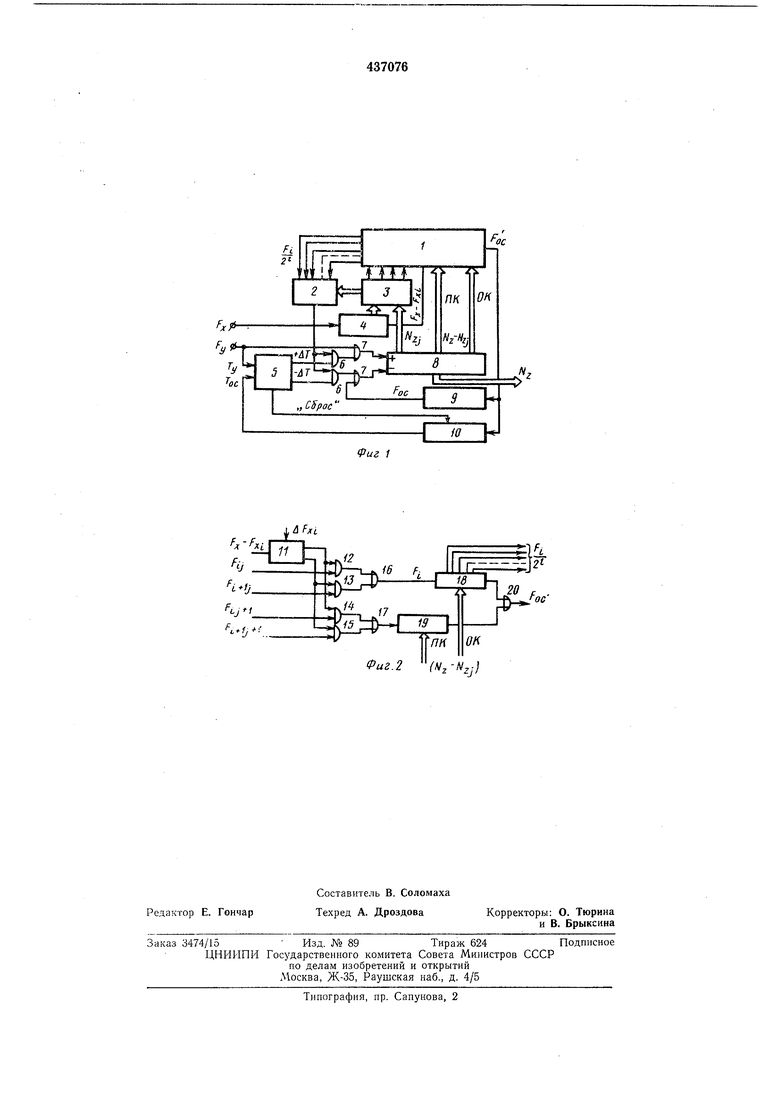

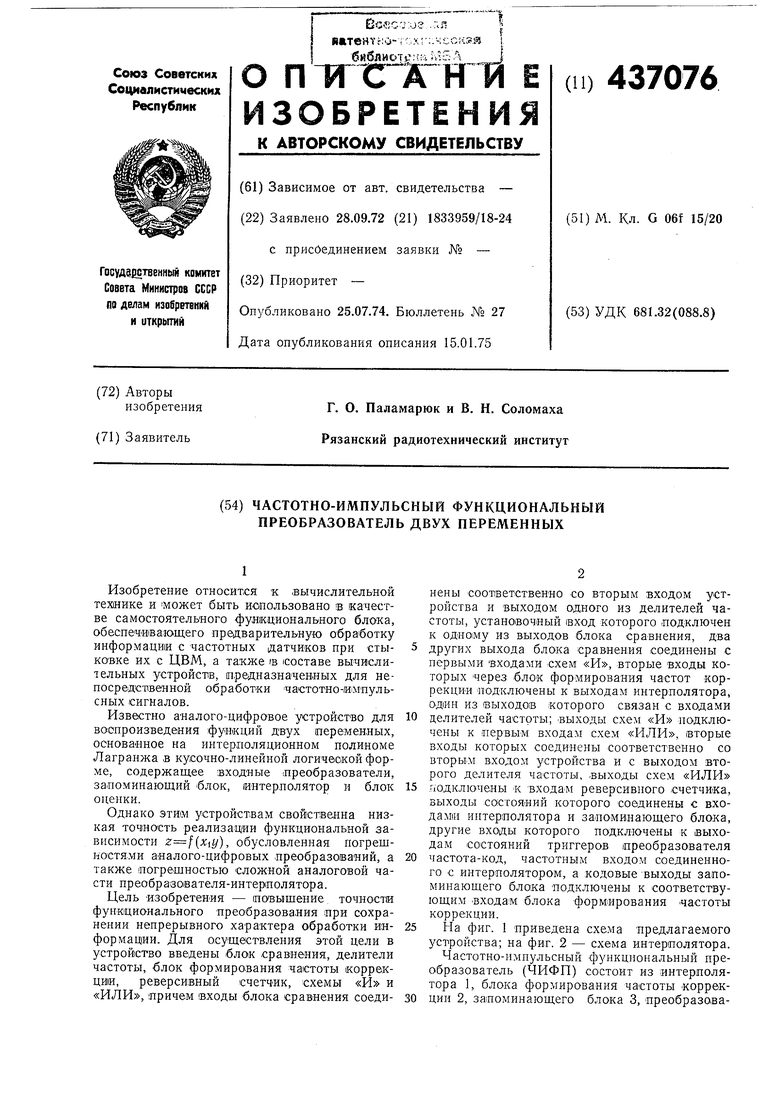

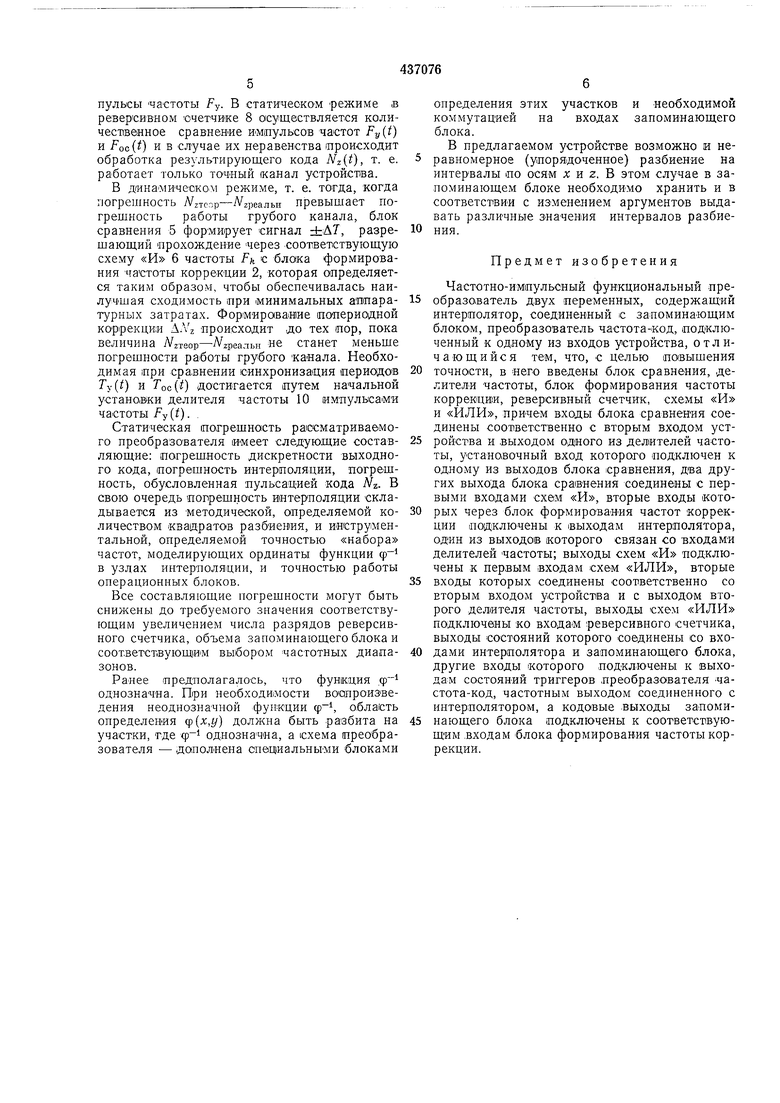

На фиг. 1 приведена схема предлагаемого устройства; на фиг. 2 - схема интерполятора.

Частотно-импульсный функциональный преобразователь (ЧИФП) состоит из интерполятора 1, блока формирования частоты коррекции 2, запоминающего блока 3, преобразователя частота-код 4, блока сравнения 5, схем «И 6 и «ИЛИ 7, реверюивного счетчика 8, делителей частоты 9 и 10.

В предлагаемом устройстве вход F соединен с входом блока сравнения 5, другим входом подключенного к выходу делителя .частоты 10, установочный вход которого соединен с выходом блока сравнения 5, а два других входа подключены к входам схем «И 6. Вторые входы этих схем .подключены к выходу блока формирования частоты коррекции 2, а выходы - к .входам соответствующих схем «ИЛИ 7. Второй вход одной из схем .«ИЛИ 7 соединен с входом устройства, а выход - с суммирующим входом реверсивного счетчика 8, -вычитающим входом подключенного к выходу другой схемы «ИЛИ 7, на второй вход которой .подключен выход делителя частоты 9. Выходы состояний реверсив.ного счетчика 8 соединены с входами интерполятора 1 и запоминающего блока 3, другими входами подключенного к выхо.дам состояний три.ггера преобразователя частота-код 4, частотным входом (FX-Fxi) соединенного с одним из входов интерполятора 1, а входом .- с входом FX устройства. Выходы запоминающего блока 3 подключены к соответствующим входам интерполятора 1, одним из выходов соединенного с входами делителей частоты 9 и 10, а .друга.ми - с входами блока формирования частоты коррекции 2, остальными «входами подключенного к кодовым выходам запоминающего .блока 3.

Частотно-им.пульсный функциональный преобразователь двух переменных реализует зависимость

N,{t) F,(i), F,(i)(1)

путем воспроизведения обратной функции

(2)

в цепи обратной связи частотно-.имоульсной системы следящего уравновешивания, составляющей основу схемы устройства.

Для повыщения быстродействия ЧИФП используется грубый канал, осуществляющий периодную отработ,ку результирующего кода NZ в динамическом режиме. Грубый канал (см. фиг. 1) состоит из схемы сравнения 5, схемы формирования частоты .коррекции 2, двух схем «И 6, делителя частоты 10.

Принцип действия грубого канала основан на сравнении .периодов входной частоты Гу(/) с периодом частоты обратной связи Гос(0случае их неравенства в течение времени (г)-Гос(0 формируется коррекция +AN,.

Работа схемы предлагаемого устройства происходит следующим образом. Импульсы входной частоты FX поступают на вход преобразователя частота-код 4, где формируется код номера .интервала. С .частотного выхода преобразователя частота-код 4 на интерполятор 1 подается разностный сигнал FX-Fxi, который участвует в формировании интерполирующего множителя. В соответствии с кодами преобразователя 4 и старщих разрядов реверсивного счетчика 8 запоминающий блок 3 подключает на вход интерполятора tl частоты Fij, Fi+i,j; Fij+i, / i+ij+i моделируюп ие ординаты функции ,в узлах интерполяции //-го .квадрата разбиения области определения Кроме того, на вход интерполятора подаются прямые и обратные коды .младших разрядов реверсивного счетчика S. Интерполятор, в соотвегствии с выражениями для последовательной линейной интерполяции по Лагранжу

/+l--g

г - zi

(3)

+ УГ

- г;

/4l

где

. У1 yijh У1+1 j

4 I

Xs (1

X -Xi

i l, 1+1 y. ,x.- у 1 + 1,1 + 1

- /--J

формирует частоту РОС, о.пределяющую значение функции ф-1 внутри найденного квадрата

5 разбиения (ij).

Выражения г/, и г/, (3) моделируются мноЖ1ительно-делительным устройствам (МДУ), реализованным на основе схемы триггерного кольца 11 ЛТК (см. фиг. 2), на выходах кото0 рой формируются прямоугольные импульсы с коэффициентами заполнения

РХ - FXI

и (4)

xi+l- xi

PKI+I - PXI

5 где F,.,t

опорная частота.

Сигналы ЛТК 11 управляют прохождением через схемы «И 12, 13, 14, 15 импульсов соответствующих частот , Fi+i,3, Рг,з+, i + l,j4-l

что равносильно умножению последних на

коэффициенты заиол.нения (4).

Схемы «ИЛИ 16, 17 осуществляют суммирование импульсных последовательностей, в результате чего на их выходах средние значения частот соответственно равны

г Г

FX-FXJ

р сX1 + 1 I г

1 1 -тъЬ fi+i,j

Fxi

,

xi + l x

. Г-,FX Fxi /г--.

Fj Fi,}+i

+ ./+i-Г -. (5) Fxi

F

XI

Окончательное выражение для у (3) моделирует1ся с помощью схем двоичных умножителей (ДУ) 18 и 19 и схемы «ИЛИ 20 (см. фиг. 2).

N,,.,j

, (6)

Pjг I N,j-, z,

где Nzi+i-N j соответствует младшей единице кода Л/zj, участвующего в определении квадрата разбиения о.бласти определения ф. С выхода интерполятора 1 - частота Foc, пройдя делитель частоты 9 и схему «ИЛИ 7, .поступает на вычитающий вход реверсивного счетчика 8, на суммирующий .вход которого

через другую схему «ИЛИ 7 поступают импульсы частоты Fy. В статическом режиме в реверсивном ючегчике 8 осуществляется количест1венное сравнеине Импульсов частот Fy(t) и /ос(О и в случае их неравенства (происходит обработка результирующего кода Nz(t), т. е. работает только точный канал у€тройст1ва.

В дина-мическом режиме, т. е. тогда, когда погрешность / гтспр-Л греальн прввышает погрешность работы грубого канала, блок сравнения 5 формирует сигнал гЬЛТ, разрещающий прохождение -через соответствующую схему «И 6 частоты Fh с блока формирования частоты коррекции 2, которая определяется таким образом, чтобы обеспечивалась наилучшая сходимость три минимальных ашпаратурных затратах. Формироваиив попериодной коррекции ДЛг происходит до тех пор, пока величина Л гтеор-Л греальн «в станет меньше погрещности работы грубого канала. Необходимая ери сравнении синхронизация периодов ГУ (О и Гос(0 достигается путем начальной установки делителя частоты 10 импулысами частоты Fj(t). .

Статическая погрешность рассматриваемого преобразователя имеет следующие составляющие: погрешность дискретности выходного кода, погрешность интерполяции, погрешность, обусловленная пульсацией кода . В свою очередь полрешность интерполяции складывается из методической, определяемой количеством «вадратов разбиения, и инструментальной, определяемой точностью «набора частот, моделирующих ординаты функции ф в узлах интерполяции, и точностью работы операционных блоков.

Все составляющие погрешности могут быть снижены до требуемого значения соответствующим увеличением числа разрядов реверсивного счетчика, объема запоминающего блока и соответствующим выборо.м частотных диапазонов.

Ранее предполагалось, что функция ф однозначна. При необходимости воспроизведения неоднозначной функции ф-, область определения (р(х,у) должна быть разбита на участки, где ф однозначна, а схема преобразователя - дополнена специальными блоками

определения этих участков и необходимой коммутацией на входах запоминающего блока.

В предлагаемом устройстве возможно и неравномерное (упорядоченное) разбиение на интервалы по осям А; и 2. В этом случае в запоминающе.м блоке необходимо хранить и в соответствии с изменением аргументов выдавать различные значения интервалов разбиения.

Предмет изобретения

Частотно-импульсный функциональный преобразО|Ватель двух переменных, содержащий интерполятор, соединенный с запоминающим блоком, преобразователь частота-код, подключенный к одному из входов устройства, отличающийся тем, что, с целью повышения

точности, в него введены блок сравнения, делители частоты, блок формирования частоты коррекци1И, реверсивный счетчик, схемы «И и «ИЛИ, причем входы блока сравнения соединены соответственно с вторым входом устройства и выходом одного из делителей частоты, установочный вход которого подключен к одному из выходов блока сравнения, два других выхода блока сра внения соединены с первыми входами схем «И, вторые входы «оторых через блок формирования частот коррекции подключены к 1выходам интерполятора, один из выходов которого связан со входами делителей частоты; выходы схем «И подключены к первым входам схем «ИЛИ, вторые

входы которых соединены соответственно со вторым входом устройства и с выходом второго делителя частоты, выходы схем «ИЛИ подключены ко входам реверсивного счетчика, выходы состояний которого соединены со входами интерполятора и запоминающего блока, другие входы которого подключены к выхода-м состояний триггеров преобразователя -частота-код, частотным выходом соединенного с интерполятором, а кодовые выходы запоминающего блока подключены к соответствующим входам блока формирования частоты коррекции.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1973 |

|

SU407317A1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Преобразователь частоты в код | 1975 |

|

SU553744A1 |

| Линейный интерполятор для систем интерактивной графики | 1988 |

|

SU1608691A1 |

| Измерительный преобразователь перемещений | 1991 |

|

SU1779921A1 |

| Цифровое устройство для обработки информации частотных датчиков | 1984 |

|

SU1239622A1 |

| Цифровой интерполятор | 1984 |

|

SU1238033A1 |

| Имитатор технологического объекта | 1980 |

|

SU924672A1 |

| Линейный интерполятор | 1979 |

|

SU842914A1 |

Фиг.2 4n,-N,j}

Авторы

Даты

1974-07-25—Публикация

1972-09-28—Подача