Изобретение относится к импульсной технике, может использоваться в станках с программным управлением.

Известен преобразователь унитарного кода в сдвиг фазы, содержащий первый и второй делители частоты, выходы которых соединены соответственно со входами блоков сложения и вычитания, в ключевных последовательно, причем другой вход блока сложения соединен с выходом генератора импульсов и входом третьего делителя частоты, выход которого через датчик обратной овязи соединен со следящей системой и входом дискриминатора, другой вход которого подключен через четвертый делитель частоты к выходу блока вычитания.

Цель изобретения - повышение частоты преобразования.

В предлагаемый преобразователь введены пятый делитель частоты, дополнительные блоки сложения, устройство запрета и блоки синхронизации, одни входы которых соединяются с выходами источника унитарного кода, другие через устройство запрета связаны с выходом генератора импульсов, а управляющий вход устройства запрета соединен через пятый делитель частоты с выходом генератора импульсов и непосредственно подключен к управляющим входам дополнительных блоков сложения, через которые выходы

бло-ков синхронизации подключены ко входам П рвого и второго делителей частоты.

С целью отработки каждого одиночного импульса унитарного кода третий, четвертый и лятый делители частоты выполнены с одинаковыми коэффициентами деления.

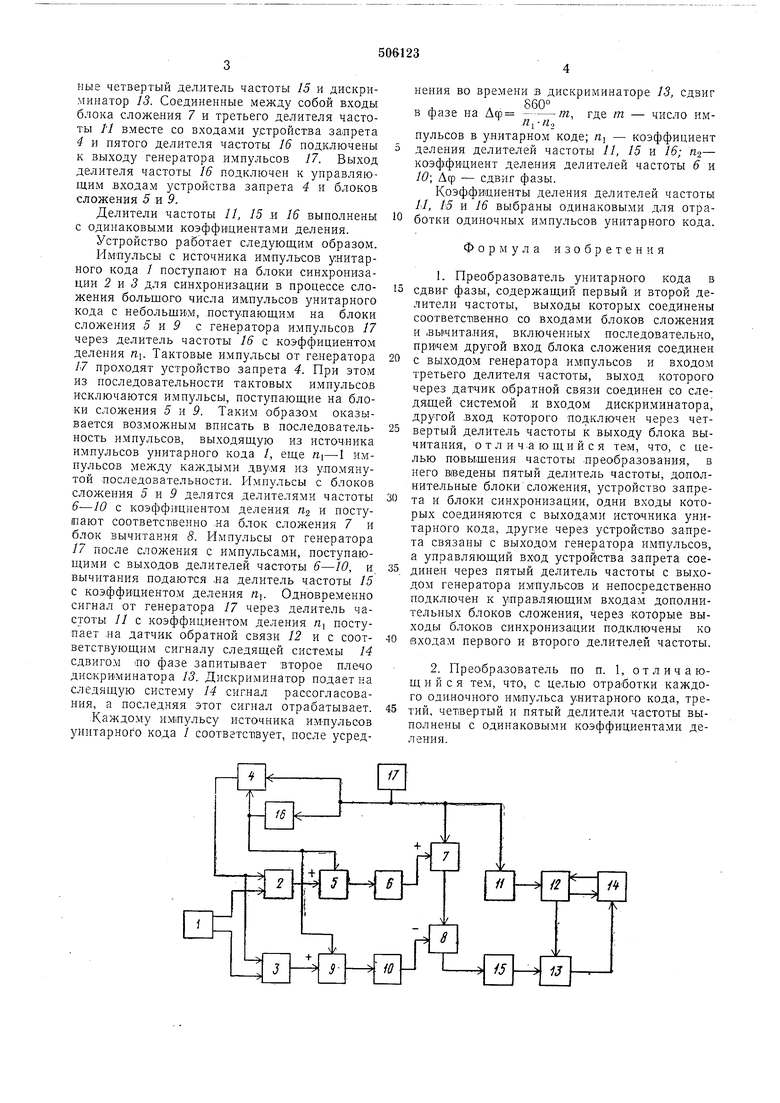

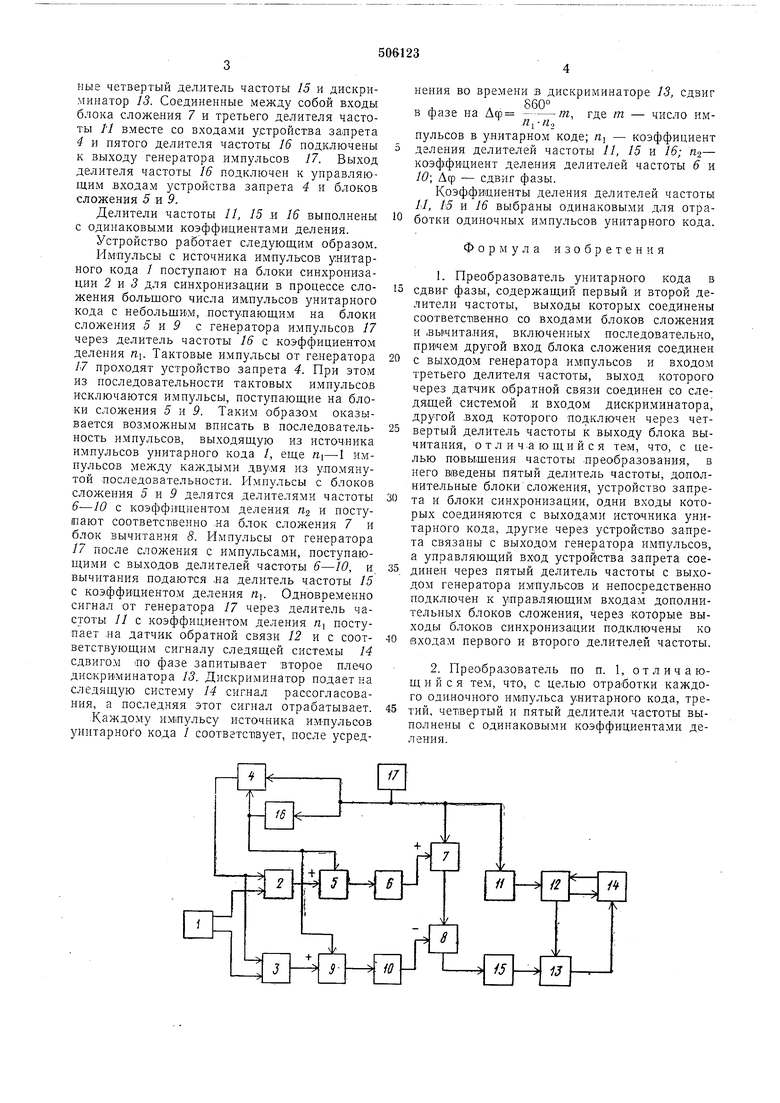

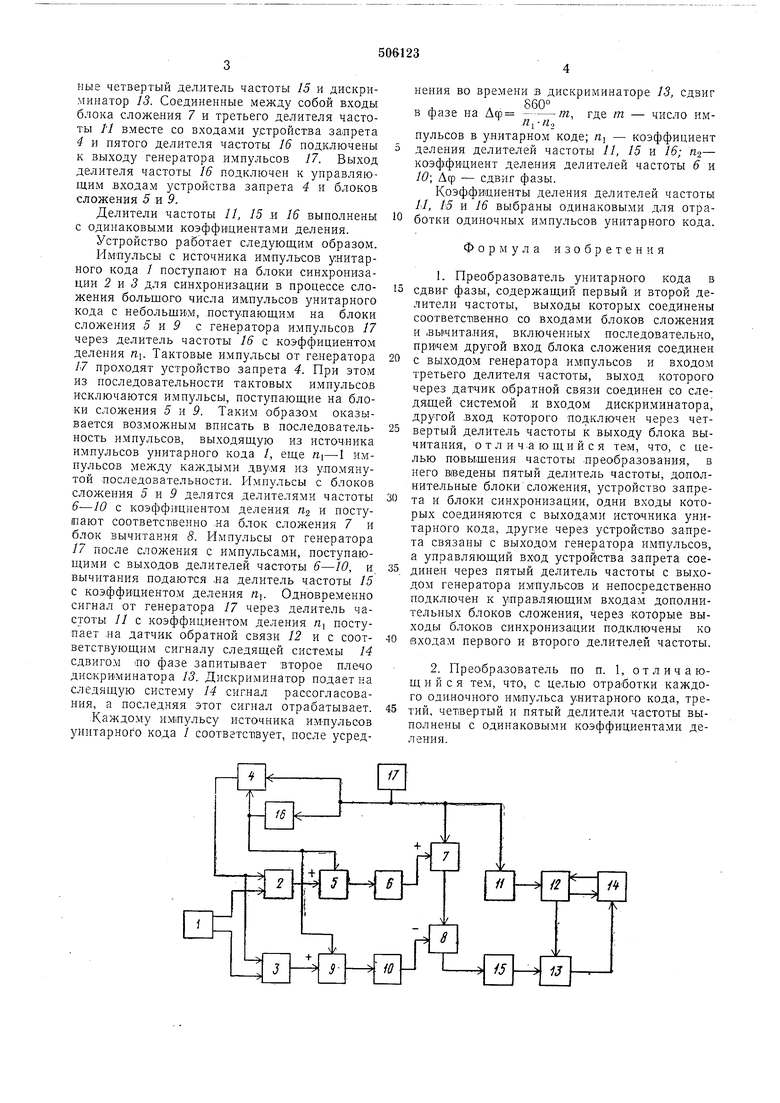

На чертеже приведена функциональная схема преобразователя.

Выходы источника унитарного кода / подключают к первым входам блоков синхронизации 2 и 3, другие входы которых соединены между собой и подключены к выходу устройства запрета 4. Выход блока синхронизации 2 через дополнительный блок сложения

5 и первый делитель частоты 6 подключен ко в.лоду блока сложения 7, выход Которого соединен с первым входом блока вычитания 8. Ко второму входу блока вычитания 8 подключен выход блока синхронизации 3 через

последовательно соединенные дополнительный блок сложения 9 и второй делитель частоты 10. Вход блока сложения 7 соединен со входом третьего делителя частоты 11, выход которого через датчик обратной овязи }2 подклЮЧен к первому входу дискриминатора 13 и первому входу следящей системы 14, выход которой подключен ко .второму входу датчи1ка обратной связи 12. Второй вход следящей системы 14 подключен к выходу блока нычитаиия 8 через последовательно соединен

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1980 |

|

SU903811A1 |

| Устройство для программного управления | 1979 |

|

SU938262A2 |

| Цифровая следящая система | 1980 |

|

SU962845A1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТНЫЙ ДИСКРИМИНАТОР | 1996 |

|

RU2143182C1 |

| Устройство синхронизации с дискретным управлением | 1974 |

|

SU562935A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1982 |

|

SU1048581A1 |

| Цифровая следящая система | 1976 |

|

SU809059A1 |

| Аналого-цифровой рентгеноспектральный анализатор | 1979 |

|

SU859892A1 |

| Устройство дискретной фазовой синхронизации | 1978 |

|

SU748894A1 |

| Контурная система программного управления | 1991 |

|

SU1800446A1 |

Авторы

Даты

1976-03-05—Публикация

1974-07-05—Подача