Изобретение относится к технике передачи сообщений дискретными сигналами и может использоваться в CHiCTieMax передачи коротких кодограм1М .и команд телеуправления.

Одно из известных устройств синхронизации с дискретным управлением содержит селектор фронтов импульсов, фазоБый дискриминатор, делитель частоты, задающий генератор и усредняющий блок .

Однако iB известном устройстве может и. 1место ложная синхроиизадия, когда расхожде1Н И е по фазе ме1Ж4Ц|у импульсами дрииимаемой информации и тактовыми .импульсами не обнаруживается и не устраняется.

Известно также устрой ство синхронизации с диакр-етлым упр авлением, соде|ржащее селактор фронтов имиульсов, выход которого подключен iKO входам дискримкнатара ложной синхроиизации и фазового, дискрймилатор-а, выходы которого -через усредняющий блок подключены к одному из входов делителя частоты, к другому входу которого подключен выход задающего генератора, а выход делителя частоты подключен к управляющим входам фазового дищриминатора и дискриминатора ложной синхронизации 2.

Однако это устрой1ство имеет малую скорость вхождения в синхронизм.

Цель изобретения - сокращение времени вхождения в синхронизм.

Для этого в устройство синхронизации с дискретным управлением, содержащее селектор фронтов импульсов, выход которого подключен ко входам дискрим.инатора ложной

синхронизации и фазового дискриминатора, выходы .которого через усред1няющий блок подключены К одному из входов делителя частоты, к другому 1входу которого -подключен выход задающего генератора, а выход делителя

частоты подключен к управляющим в.ходам фазового дискриминатора и дискриминатора ложной синхронизации, введены три элемента ИЛИ и ключ, при этом выходы фазового дискриминатора через первый элемент ИЛИ подключены к одному из входов Ключа, « другому входу которого подключен выход дискриминатора ложной синхронизации, а выход ключа подключен к дополнительному входу делителя частоты через второй элемент ИЛИ. ко второму входу которого подключен второй выход усредняющего блока, .первый и второй выходы которого через третий элемент ИЛИ подключены «ко «входу «запрет ключа.

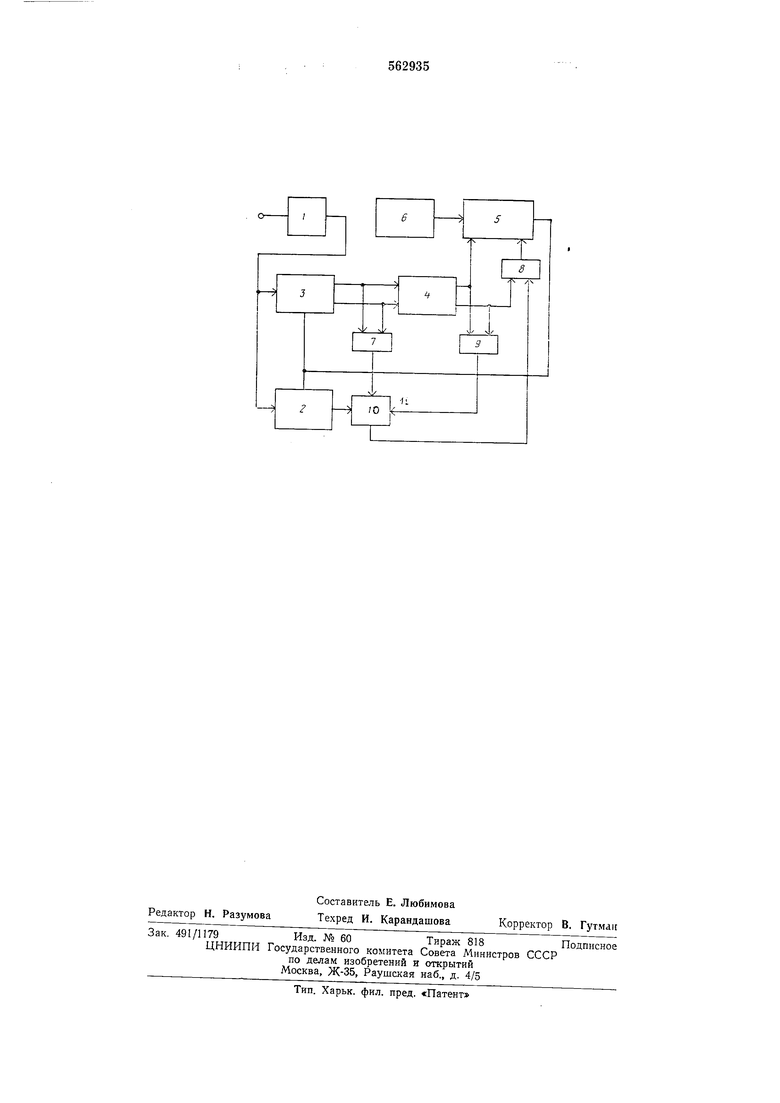

На чертеже представлена структурная

электрическая схема устройства.

Устройство синхронизации с дискретным управлением содержит селектор 1 фронтов импульсов, выход которого подключен ко входам дискриминатора 2 ложной синхронизаци)

и фазового дискриминатора 3, выходы которого через усред:Н|Яющ1ий блок 4 подключены к одному из входов делителя частоты 5, к другому входу которого подключен шыход задаюцего генератора 6, а выход делителя частоты 5 подключен к управляющим входам фазо-зого диокриминатора 3 и диакр.иминатора 2 ложной синхрон1таац,ии, три элемента ИЛИ 7, 8, 9 и ключ 10, при этом выходы фазового лискрйминатора 3 через первый элемент ИЛИ 7 подключены к одиаму из входов ключа 10, к друюму входу которого подключен выход д,и|ск риминатора 2 ложной синхронизации, а пыход ключа 10 подключен к дополнительному входу делителя частоты 5 черСз второй элемент ИЛИ 8, жо второму ;входу которого подключен второй выход усредняющего блока 4, лервый .и второй выходы жоторого через третий элемент ИЛИ 9 под-ключены ко входу // «запрет ключа 10.

Устройство работает следующим образом.

Во время приечма ннфор|Мации сигналы, соответст1вующ.ие значащим мом.ента-м, с выхода селектора / фронтов имиульсов поступают на фазовый дискриминатор 3 и дискриминатор 2 ложной синхрОЕизадии. При отсутствии ложпой .синхронизации фазовый дискриминатор 3 определяет знак рассогласования фазы, в зависимости от которого выдает либо импульсы добавления, л.Ибо вычитания на усредняющий блок 4. Сигналы на выходе уаредняюа1:его блока 4 появятся только в том случае, если количество импульсов добавления (вычита шя), поступающих с выхода фазового дис7-;рИМ1Иватора 3, устойчиво гьреобладает над количеством импульсов (вычитания (добавлег.ия) в течение периода усреднения. Сигнал с выхода усредняющего блока 4 поступает на делитель частоты 5, изменяя фазу тактовых

иМПУЛЬСОБ.

При возникновении ложной синхронизации дискри.минатор 2 ложной синхронизации тзыдает юи-гнал на ключ 10. Ключ 10 открывается, и импульсы добавления и вычитания, поочередно поступающие с выходов фазового дискри.минатора 3, через элемент ИЛИ 8, г,люч 10 и элемент ИЛИ 7, посту пают на дополнительный вход делителя частоты 5. При этом в силу поочередного поступления импуль ов Д0|ба1вления и вычитания с обоих выхо,-ов фазового дискриминатора 3 усредняющий блок 4 не -выдает управляющих сигналов на делитель частоты 5, и фаза тактовых импульсов изменяется только сигналами, поступаюЩ1ими с выхода «люча 10.

Ключ 10 остается открытым до появления управляющих сигналов с выхода усредняющего блока 4, что свидетельствует о выходе системы из состояния ложной синхронизации. Сиплалы с выхода усредняющего блока 4 через элемент ИЛИ 9 поступают на вход 11 «запрет ключа 10, ключ 10 закрывается, а

дальнейщая корректировка фазы, установка системы iB состояние нормальной синхронизаU .:i и последующее удержание ее в этол состоянии осуществляется управляющ,ими сигналами с выхода усредняющего блока 4.

1Предложе1нное устройство позволяет позыоить окорссть вхождеиия в синхранмзм.

Формула и 3 О б р е т е н и я

Устройство синхронизации с дискретным управлением, содержащее селектор фронтов импульсов, выход которого подключен ко входам дискрИ|Минатора ложной синхронизации и фазОВОго дискриминатора, выходы которого

через усредняющий блок подключены к одному из входов делителя частоты, к другол-ту входу которого подключен выход задающего генератора, а выход делителя частоты подключен -к управляющим входам фазового дискримииатора и дискриминатора ложной синхронизации, отличающееся тем, что, с целью сокращения времени вхождения в синхронизм, введены три элемента ИЛИ и ключ, при этом вы.ходы фазового дискриминатора через первый элемент ИЛИ подключены к одному из входов ключа, к другому входу которого подключен выход дискриминатора ложной синхронизации, а выход (ключа .подключен к дополнительноМу входу делителя частоты через

второй элемент ИЛИ, ко второму входу которого подключен второй выход усредняющего блока, первый и второй выходы которого через третий элемент ИЛИ подключены ко входу «запрет ключа.

Источники информации, принятые во внимание при экспертизе.

1. Гуров В. С. и др. Передача дискретной инфор-мации и телеграфия. М., «Связь, 1974г., с. 33-137.

2. Мартынов Е. М. Синхронизация в системах передачи дискретных сообщений. .М., «Связь, 1972 г, с. 112, рис. 6.20.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации с дискретным управлением | 1978 |

|

SU758547A2 |

| Устройство синхронизации с дискретным управлением | 1978 |

|

SU856028A2 |

| Устройство тактовой синхронизации | 1982 |

|

SU1059689A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство поэлементного фазирования | 1980 |

|

SU928665A1 |

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| Устройство тактовой синхронизации | 1976 |

|

SU585618A1 |

| Устройство синхронизации | 1981 |

|

SU1003376A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство компенсации сдвигачАСТОТ | 1979 |

|

SU843270A1 |

Авторы

Даты

1977-06-25—Публикация

1974-10-07—Подача