(54) ЦИФРОВАЯ СЛЕДЯЩАЯ СИСТЕМА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Цифровая динамическая следящая система | 1980 |

|

SU924667A2 |

| Устройство синхронизации сигналов | 1981 |

|

SU1021005A2 |

| Устройство фазирования бинарного сигнала | 1981 |

|

SU1075431A1 |

| Широтно-импульсное устройство для программного управления приводом | 1981 |

|

SU1020799A1 |

| Цифровой магнитовариационный преобразователь | 1978 |

|

SU802893A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1387198A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Электропривод | 1985 |

|

SU1275726A1 |

| Устройство синхронизации сигналов | 1975 |

|

SU552719A2 |

Предлагаемая цифровая следящая система относится к радиотехнике и предназначена для получения разностного отсчета при слежении за фазой сигналов в условиях помех.

Известна цифровая следящая система, содержащая линии задержки, генератор опорной частоты, делители, схемы запрета, счетчики результатов, вспомогательные счетчики, триггеры, временной дискриминатор и схемы перезаписи 1.

Однако данная схема не рещает вопросов фильтрации сигнало-в и получения разностного отсчета в условиях действия помех.

Известны следящие системы, содержащие опорный генератор, интегратор, реверсивный счетчик, делитель и дискриминатор знака рассогласования 2.

Недостатками данных следящих систем являются снижение надежности системы из-за необходимости введения устройств, - подстраивающих по частоте опорный генератор с тем, чтобы выходная частота системы, находящаяся в прямой зависимости от частоты опорного генератора, была равна частоте сигнала, ибо при расстройке частот

получение разностного отсчета становится невозможным,, и снижение быстродействия, а также надежности системы при работе со схемой совпадения кодов больщой разрядности или при работе на частоте, близкой к граничной, из-за задержки в цепях переноса делителя.i Цель изобретения - повышение быстродействия и надежности цифровой следящей системы.

Указанная цель достигается тем, что в

цифровую следящую систему, содержащую последовательно соединенные делитель частоты, дискриминатор знака рассогласования интегратор, реверсивный счетчик, а также генератор опорной частоты, введены блок перезаписи, последовательно соединенные

триггер и элемент И, блок задержки и элемент ИЛИ, выходы которых соединены со входами триггера, а входы - соответственно с первым входом блока перезаписи и выходом делителя частоты, входы которого

соединены с выходами элемента И и блока перезаписи, другие входы которого соединены с выходами реверсивного счетчика, а выход генератора опорной частоты соединен со вторым входом элемента И.

Система работает следующим образом. При поступлении импульсной последовательности одного сигнала на блок перезаписи в делителе частоты устанавливается код, обратный коду реверсивного счетчика (код реверсивного счетчика - начальное значение разности фаз), и на вход делителя частоты начинает поступать импульсная последовательность напряжения опор кого генератора. При переполнении делителя частоты, т. е. с задержкой, определяемой начальным значением разности фаз, на выходе появляется импульс напряжения, стопорящий делитель,. Фаза импульса -fg,,, сравнивается с фазой второго сигнала, в ре зультате чего меняется код в реверсивном счетчике, а следовательно и фаза импульса напряжения на выходе делителя частоты.

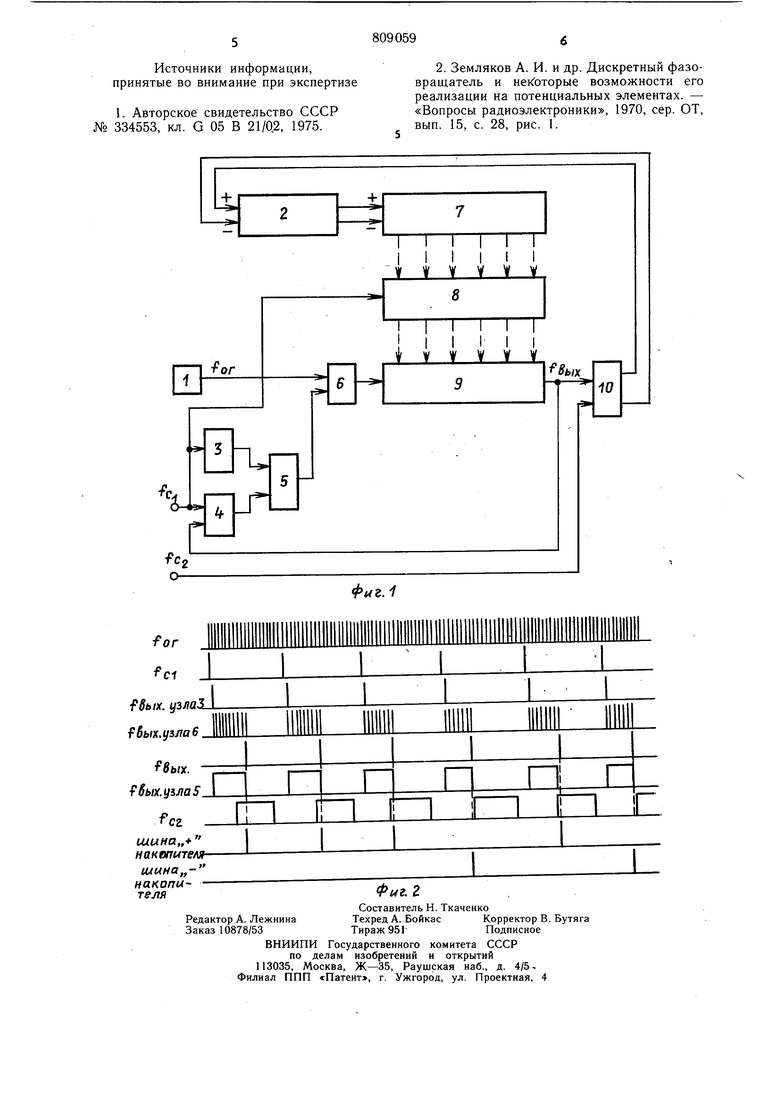

На фиг. 1 представлена блок-схема циф ровой следящей системы; на фиг. 2 - диаграммы напряжений.

Система содержит тэпорный генератор 1, интегратор 2, блок 3 задержки, схему ИЛИ 4, триггер 5, схему И 6, реверсивный счетчик 7, блок 8 перезаписи, делитель 9 частоты, дискриминатор 10 знака рассогласования.

Цифровая следящая система работает следующим образом.

Импульсная последовательность напряжения опорного генератора 1 подается на один из входов схемы И 6, сигнал fg подается на вход блока 3 задержки, блока 8 перезаписи и на один из входов схемы ИЛИ 4, сигнал ict подается на один из входов дис- криминатора 10 знака рассогласования. При поступлении импульса напряжения сигнала Iu4 на вход блока 8 перезаписи на делитель 9 частоты передается дополнительный код реверсивного счетчика 7. Этот же импульс через блок 3 задержки подается на триггер 5, опрокидывает его,- и импульсное напряжение for с опорного генератора 1 подается через схему И б на вход делителя 9 частоты. При переполнении делителя частоты 9, т. е. с з-адержкой, определяемой кодом реверсивного счетчика, на его выходе появляется импульс напряжения l,, который через схему ИЛИ 4 возвращает триггер 5 в исходное состояние и закрывает схему И 6., и на вход делителя частоты 9 прекращается поступление импульсного напряжения Где до момента появления очередного импульса напряжения сигнала f Следовательно, период выходной последовательности импульсов fgbix задается импульсной последовательностью напряжения сигнала f , т. е. независимо от расстройки опорного генератора (расстройка определяется заданной инструментальной точностью), частота выходного напряжения ,,, равна частоте сигнала

Х/

Импульсная последовательность наприжения fftbixH сигнал fcjj подаются на дискриминатор 10 знака рассогласования, где сравниваются между собой по фазе. В результате сравнения определяется знак рассогласования между ними, в зависимости от которого с соответствующего выхода дискриминатора импульс напряжения лг. поступает на соответствующий (щина сложения или щина вычитания) вход интегратора 2, предназначенного для фильтрации помех, а в конечном счете на вход реверсивного счетчика 7.

Таким образом, меняется код реверсивного счетчика 7, а следовательно и время появления импульсов напряжения Гвых (фазгимпульсов напряжения ). При поступлении очередного импульса напряжения сигнала работа схемы повторяется.

Очевидно, что код реверсивного счетчика 7 меняется до тех пор, пока временное положение переднего фронта импульсов напряжения f выи не совпадет с передним фронтом сигнала f(i, т.е. пока импульсы этих напряжений не совпадут по фазе. Наряду с этим каждый импульс выходного напряжения вых сдвигается по времени относительно соответствующих импульсов напряжения сигнала fcj на число периодов частоты , равное коду реверсивного счетчика 7. Следовательно, в реверсивном счетчике 7 записывается код, соответствующий разности фаз сигналов и W, т.е. разностный отсчет.

Использование изобретения позволяет синхронизироваться работе делителя частоты импульсами напряжения сигнала, вследствие чего отпадает необходимость в подстройке частоты опорного генератора, что значительно (примерно в 2 раза) упрощаех-схему устройства, и вследствие этого повышает его надежность (примерно в 2,5 раза), и вместо схемы совпадения использовать блок перезаписи, реализация которого более, чем в 1,5 раза проще схемы совпадения и обеспечивает надежную работу следящей системы больщой разрядности на частотах, близких к граничной частоте срабатывания элементов.

Формула изобретения

Цифровая следящая система, содержащая последовательно соединенные делитель частоты, дискриминатор знака рассогласования, интегратор, реверсивный счетчик, а также генератор опорной частоты, отличающаяся тем, что, с целью повышения быстродействия и йадежности системы, в нее введены блок перезаписи, последовательно соединенные триггер и элемент И, блок задержки и элемент ИЛИ, выходы которых соединены со входами триггера, а входы - соответственно с первым входом блока перезаписи и выходом делителя частоты, входы которого соединены с выходами элемента И и блока перезаписи, другие входы которого соединены с выходами реверсивного счетчика, а выход генератора опорной частоты соединен со вторым входом элемента И.

Авторы

Даты

1981-02-28—Публикация

1976-12-02—Подача