1

Изобретение отноеится к телеграфной связи.

Известно приемное устройство электронного телеграфного аппарата, содержаогее последовательно соединенные усилитель - ограничитель, распределитель, детектор, накопитель и выходной блок. Однако такое устройство имеет невысокую помехоустойчивость.

Для повышения помехоустойчивости в предлагаемом устройстве между усилителем - ограничителем и распределителем включена цепь из последовательно соединенных формирователя имиульсов, схемы «Запрет и элемента задержки, причем выход схемы «Запрет дополнительно подключен к управляющему входу детектора, выход которого подключен ко второму входу распределителя, а второй выход формирователя через вторую схему «Запрет подключен к управляющему входу накопителя, дополнительный выход которого через второй формирователь импульсов подключен к управляющим входам обеих схем «Запрет.

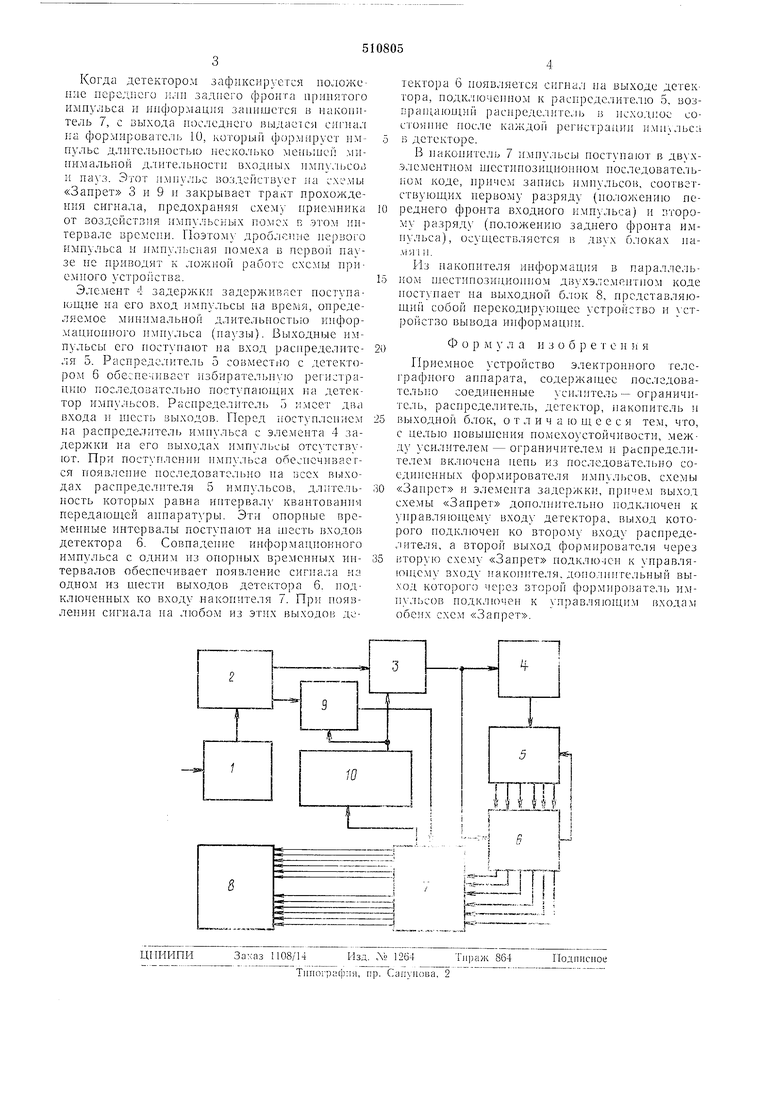

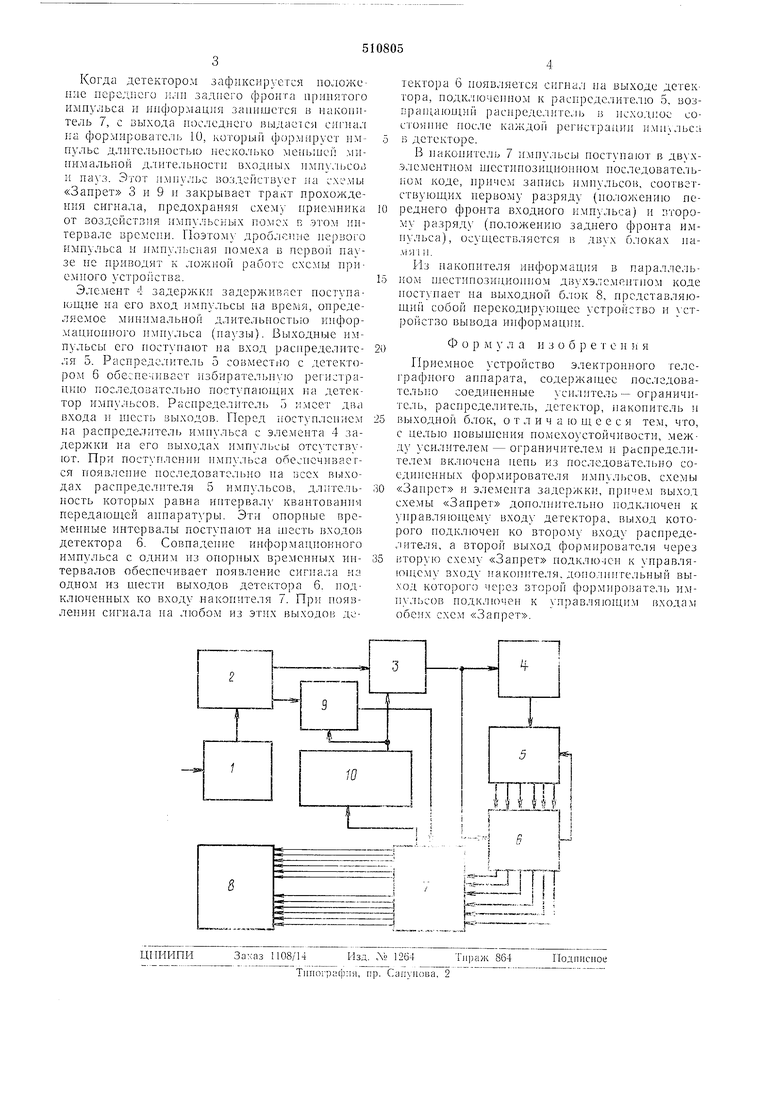

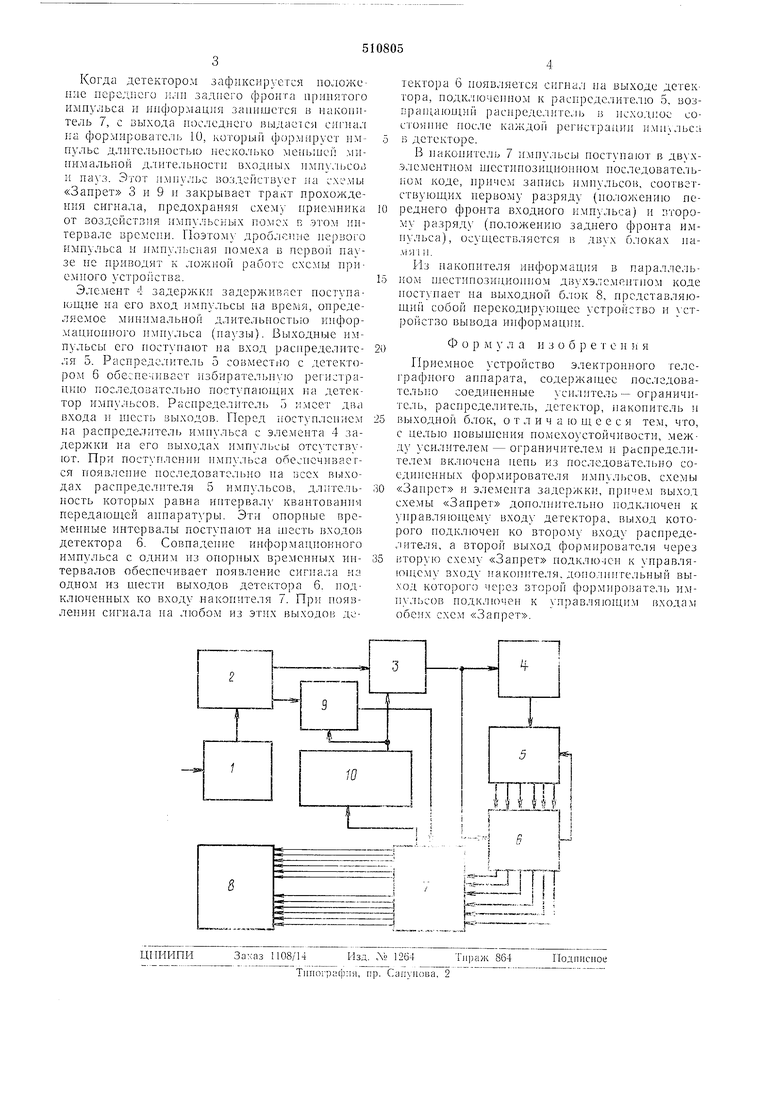

На чертеже дана блок-схема описываемого устройства.

Устройство содержит последовательно соединенные усилитель - ограничитель 1, формирователь 2 импульсов, схему «Запрет 3, элемент 4 задержки, распределитель 5, детектор 6, накопитель 7 и выходной блок 8. Выход схемы «Запрет 3 дополнительно подключен к управляющему входу детектора 6, выход которого подключен ко второму входу раснределителя 5, а второй выход формирователя 2 через вторую схему «Запрет 9 подключен к управляющему входу накопителя 7, дополнительный выход которого через второй формирователь 10 имиульсов подсоединен к управляющим входам обеих схем «Запрет 3 и 9.

Устройство работает следующим образом.

На вход усилителя - ограпичигеля 1 из канала связи непрерывно поступают манипулированные импульсы. С выхода усилителя - ограничителя 1 импульсы поступают на вход формирователя 2, в котором они дифференцируются и выпрямляются. Дифференцированные импульсы, соответствующие заднему фронту входных имнульсов, с выхода формирователя 2 через схему «Запрет 9 поступают на вход накопителя 7, синхрон1 зируя его работу и осуществляя сброс памяти после вывода ииформации. С другого выхода формирователя 2 выпрямленные импульсы через схему «Запрет 3 поступают на вход детектора 6 и вход элемента 4 задержки.

Схемы «Запрет 3 и 9 и формирователь 2 представляют собой блок защиты от имиульсиых помех, который 1аботает следующим образом.

Когда детектором зафиксируется положипне передпего или заднего фронта принятого нмпудьса и информация запишется в накопитель 7, с выхода последнего выдастся си|-иал па формнровател. 10, jvOTopbui формирует импульс длите,1ьпостыо несколько Menijinefi мипимальпой длительности входных имнульсов и пауз. Этот имиул с воздействует на схемы «Запрет 3 и 9 i закрывает тракт прохождения сюдгала, предохраняя схему приемника от воздействия импульсных помех в этом интервале времени. Поэтому дробление иервого импульса п пмпу.ть-еиая помеха в nepBoii паузе не приводят к ложной рабоге схемы прие.миого уетр01 етва.

Эле.мент 4 задержки задерживает поступаюгцне па его вход имиульеы на время, оиределяемое мннимальпой длительностью информацпопио1-о импульса (иаузы). Выходные импульеы его поступают иа вход распределителя 5. Распределитель 5 совместно е детектором 6 обеспечивает избирателыгсю регистрапию последовательно ноступающих на детектор импульсов. Раепределитель 5 имеет два входа и niecTb выходов. Перед ьостунлеиием на распределитель имн льса с элемента 4 задержки на его выходах импульсы отсутствуют. При постхпленпи имну.тьеа обеспечивается появление носледовате.мьно на всех выходах раснределителя 5 нмнульеов, длительность которых равна иптервалу квантовання передаюидей аппаратуры. Эти опорные временные интервалы поступают на шесть входов детектора 6. Совпадение ннформанпонного импульса с одним из опориых временных ннтервалов обеепечивает появление сигна.ча на одном нз HiecTH выходов детектора 6. подключенных ко входу накопителя 7. При ноявленип еигнала па любом из этггх выходов детектора 6 появляется еитнал на выходе детектора, нодк,чюченном к распределителю 5, возвран1,аюнин| распределитель в исходное состоянне ноеле каждой регистрации и. Б детекторе.

В накопитель 7 п: 1пульсы поступают в двухэлементном пюстипозиционном последовательliOM коде, причем запись импульсов, соответетвуюгцнх первому разряду (положению передпего фронта входного импульса) и г.торому разряду (положению задиего фронта имиульеа), осушествляетея в двух блоках иа.VI я i и.

Из накопителя информация в параллельком итестинозициоином двухэлеме1ггном коде ностунает на выходной б.ток 8, нредставляюший собой перекодирующее уетройство п устройство вывода ппформацпи.

Фор м у л а и 3 о б р е т е н и я

Прие.мпое уетройство электропного телеграфного аппарата, еодержашее последовательно соединенные уснлитель- ограничптель, распределитель, детектор, наконитель и выходной блок, о т л н ч а К) щ е е с я тем, что, с целью повышепия номехоуетойчнвостн, между усилителем - ограничителем и раснределителем включена иень из последовательно соединенных формирователя имнул15сов, схемы «Запрет н элемента задержки, прпче.м выход схемы «Запрет дополпительпо подключен к унравляюндему входу детектора, выход которого подключен ко второму входу распределителя, а второй выход (ормнрователя че)ез вторую схему «Запрет нодклю-1ен к управляюп ему входу накошггеля, доно.тпптельный выход которого через второй формировател импульсов иодключеи к уиравляюпгим входа.м обег-гх схем «Запрет.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения длительности фронтов импульсов | 1986 |

|

SU1357878A1 |

| Устройство для преобразования частоты гармонического сигнала в напряжение | 1974 |

|

SU574866A1 |

| Декодирующее устройство -позиционного временного кода | 1977 |

|

SU652724A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU919124A1 |

| Устройство для приема дискретной информации | 1976 |

|

SU642872A1 |

| Передающее стартстопное устройство | 1974 |

|

SU548937A1 |

| ГЁЛЕГРАФНЫЙ ПРИЕМНЫЙ АППАРАТ | 1972 |

|

SU343395A1 |

| Измеритель скорости звука | 1991 |

|

SU1796918A1 |

| Одноканальное устройство для управления многофазным вентильным преобразователем | 1977 |

|

SU731550A1 |

| Устройство управления узлами отбора игл кругловязальных машин | 1975 |

|

SU600224A1 |

Авторы

Даты

1976-04-15—Публикация

1973-12-17—Подача