(54) УСТРОЙСТВО ДЛЯ ИДЕНТИФИКАЦИИ ОДНОКРАТНЫХ

ВРЕМЕННЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля геометрических размеров грата электросварных труб | 1988 |

|

SU1623843A1 |

| Устройство для сверки шкал времени | 1986 |

|

SU1385118A1 |

| Система идентификации параметров многомерного нелинейного динамического объекта | 1986 |

|

SU1385122A1 |

| Устройство для сигнализации | 1986 |

|

SU1345226A1 |

| Устройство преобразования аналогового видеосигнала в двухуровневый | 1982 |

|

SU1107335A1 |

| Способ формирования сигнала управления экспонирования ПЗС-фотоприемника и устройство для его осуществления | 1989 |

|

SU1728982A1 |

| Устройство для сигнализации | 1985 |

|

SU1278913A1 |

| Вихретоковое устройство для неразрушающего контроля | 1989 |

|

SU1765763A2 |

| Цифровая система измерения и обработки | 1986 |

|

SU1352507A2 |

| Устройство управления несколькимиОдНОТипНыМи Об'ЕКТАМи C иНЕРциЕй | 1977 |

|

SU840793A1 |

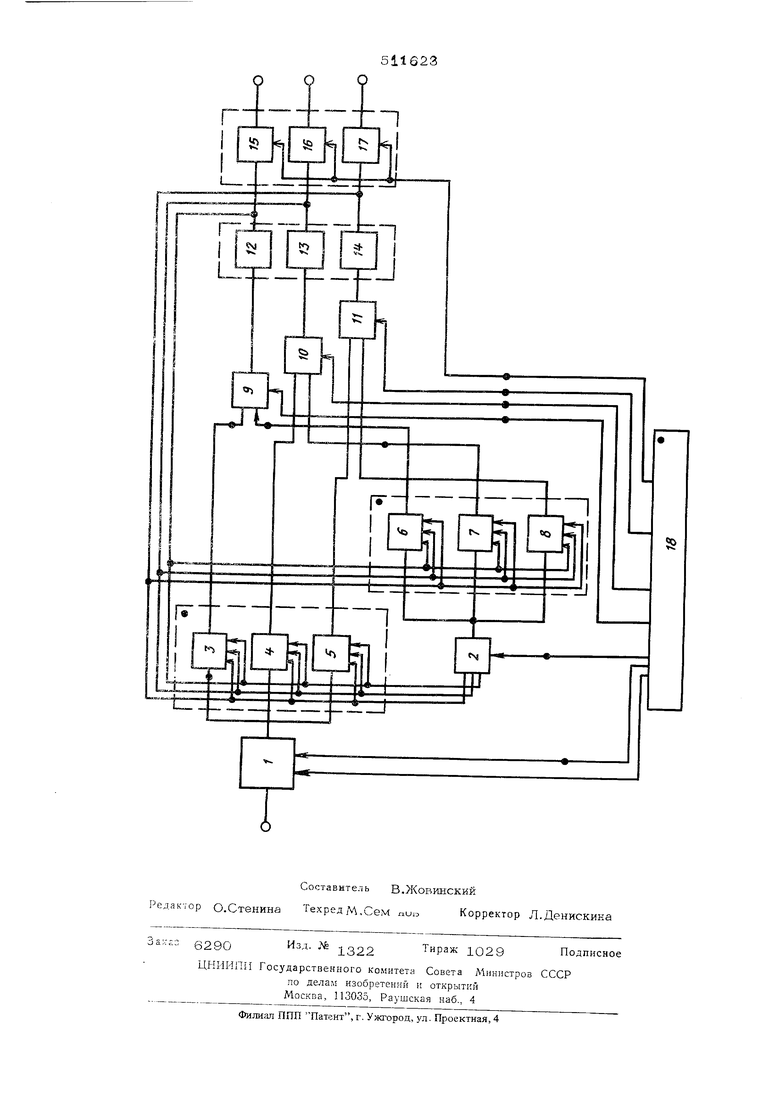

Изобретение относится к вычислительной технике и может применяться для быстрой идентификации однократных временных сигна лов, представляемых суммой небольшого чис ла компонент, и, в частности, для формант ног о анализа речи и ппя определения постоян ных времени распада компонент радиоактивных смесей. Известное устройство для идентификации однократных временных сигналов содержит оптимизаторы, синхрогенератор, блок запоминания сигнала, подключенный выходом соответственно к первым входам управляемых измерителей параметров сигнала блок модели сигнала, выходом соединенный соответственно с первыми входами управляе .ых измерителей параметров модели, первую и вторую группу запоминающих ячеек. Однако известное устройство требует бол шого числа пробных изменений настройки, что существенно снижает его быстродействи Цель изобретения - повышение быстродей ствия идентификатора сигналов, содержащих не ортогональные компоненты функции. Это достигается тем, что первые вхэдь) оптимизаторов подключены к выходам соответствующих управляемых измерителей параметров сигнала, а вторые входы соединены с выходами соответствующих управляемых измерителей параметров модели, выходы оптимизаторов через запоминающие ячейки первой группы подключены ко входам соответствую -. щих запоминающих ячеек второй группы, к соответствующим входам управляемых измерителей параметров сигнала, к соответствую щим входам управляемь;х измерителей параметров модели ц к информационным з.х.эдам блока модели сигнала, управляющий вход которого соединен с одним выходом синхроге- нератора, другие выходы которого подключены соответственно к управляющим входам блока запоминания сш-кала, оптимизаторов и запоминающих ячеек второй группы. На чертеже приведена блок-схема уст- р ойства. Предлагаемое устройство содержит блок 1 запоминания сигнала, блок 2 модели сигнала, управляемые измерители 3-8, оптимгтза™торы 9-11, запоминающие ячейки 12-14 первой группы, запоминающие ячейки 1517 второй группы и синхрогенератор 18, Первая группа управляемых измерителей 3 4 и 5 измеряет параметры сигнала, вторая 6, 7 и 8 измеряет параметры модели. Bxcvды измерителей первой группы присоединены к выходу блока 1 запоминания сигнала, управляющие входы этого блока соединены с выходами синхрогенератора, а информационный вход со входом устройства. Вторая -группа ущ)авлйемых измерителей состоит из измерителей 6, 7 и 8, входы которых присоединены к выходу блока 2 мо пели сигнала, входы которого присоединены к выходам запоминающих ячеек параметров модели 12, 13 и 14; к этим выходам под члючены также управляющие входы измерите лей 3-8 и входь ячеек 15, 16 и 17 второй группы. Выходы однотипных измерителей из разных групп присоединены попарно к входом оптимизаторов настройки модели; выходы измерителей 3 и 6 ко входам оптимизатора 9, выходы измерителей 4 и 7 ко входам оптимизатора 10, выходы измерите лей 5 и 8-ко входам оптимизатора 11, Вы. оптимизаторов 9, 10 и 11 с единены со входами ячеек первой группы 1, 13 и 14. Выходы запоминающих ячеек 15, 16 и 17 (запоминания параметров) подключены к выходу устройства, а управляюшие входы этих ячеек присоединены к выходу синхроген ратора 18. Второй сигнал запоминается в блоке 1 под воздействием управляющего сигнала с первого выхода синхрсгенератора 18, каж- дая посылка управляющего сигнала со второго выхода синхрогенератора вызывает вос произведение запомненного сигнала, причем время воспро-зведения может отличаться от длительности записи, и, в частности, воспро изведение может быть значительно ускорено по сравнению с записью. Одновременно с за пуском воопроизведения сетосрогенератор вкл чает блок модели сигнала 2, который генери рует сигнал, соотьетствующий значениям пар метров, отводимых с выходов ячеек 12, 13 и 14, соединенных с входами модели источ ника сигнала. Изменения параметров настройки блока 2 модели сигнала производятся поочередно, причем порядок осуществления этих изменений задан заранее и реализуется поочередным включением оптимизаторов 9, 10 и 11, посылками управляющих сш налов, отводимых от синхрогенератора. Каждый оптимизатор, когда он включен, настраивг ет отделытый параметр модели так, чтобы минимизировать различия сигналов, поступающих на его вход от управ-ляеглых измерителей. Входы каждого оптимизатора оединены с измерителями, обладающими повыщенной чувствительностью к изменениям параметра модели сигнала, управляем or с этим оптимизатором, и понижейной вительн остью к изменениям параметров, не управляемых оптимизатором. Это ослабляет влияние ошибок в настройке одних параметров на оптимизацию настройки других, что сокращает продо-лжи. тельность поиска и тем повыщает быстродействие устройства. Упрощение устройства достигнуто тем, что вместо сложного многомерного оптимизатора использованы более простые одномерные оптимизаторы, и тем, что благодаря ускорению процесса самонастройки модели генератора сигнала вывод результатов поиска производится после не большого числа циклов включений оптимиза-.-.торов с помощью последнего отправляющего сигнала, которым синхрогенератор включает ячейки выходного блока запоминания параметров. Формула изобретения Устройство для .-идентификации: о.окократ.ных временных сигналов, содержащее оптимизаторы, синхрогенератор, блок запоми нания сигнала, подключенный выходом CDQT. ветственно к первым входам управимемых измерителей параметров сигнала, блок модели сигнала, выходом соединенный соот« ветственно с первыми входами управляемых измерителей параметров модели, первую и вторую группу запоминающих ячеек, о т л и ч а ю щ е е с я тем, что, с целью поы.апения быстролейстьия, первые входы оптимизаторов подключены к выходам соответствующих управляемых измерителей параметров сигнала, а вторые входы соеди™ нены с выходами соответствующих управ- .тщемых измерителей параметров модели, выходы оптимизаторов через запоминающие, ячейки пфвой группы подключены ко вхо-. дам соответствующих запоминающих ячеек второй группы, к с о ответе-ТВ ующим входам управляемых измерителей параметров сигна ла, к соответствующим входам управляемых измерителей параметров модели и к инфор..-мационным входам блока модели сигнала, управляющий вход которого соединен с одним выходом синхрогенератора, другие выходы KDTOptJro подключены соответственно к управляющим входам блока запоминания сиг нала, оптимизаторов и запоминающих ячеек второй группы.

Авторы

Даты

1976-04-25—Публикация

1974-05-06—Подача