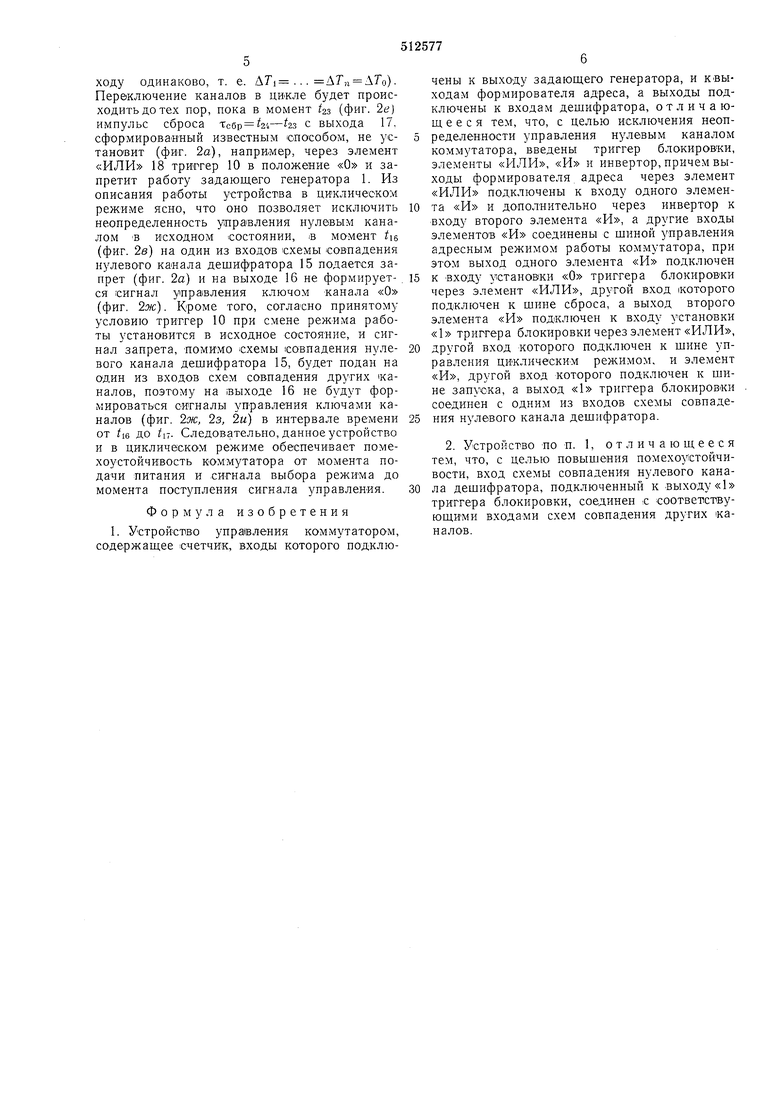

щими адресными входами триггеров счетчика 2, а также, включая и нулевой выход, через элемент «ИЛИ 5 - с входом инвертора 6 и с одним из входов элемента «И 7; элемент «И 8, у которого один из входов под.ключен к выходу инвертора 6, другой, соединенный с -вторым ВХОДОМ элемента «И 7, - -к выходу 9 сигнала управления адресны-м режимом работы коммутаторов, а выход сое динен с входам устаНОВ1ки «О триггера блокировки 10; элемент «ИЛИ 11, один из входов которого подключен .к выходу элемента «И 7, а другой, соединенный с одним из входов элемента «И 3, - к выходу 12 ситнала управления циклическим режимом работы коммутатора; элемент «И 13, у которого один из входов подключен к 1выходу элемента «ИЛИ И, другой, соединенный с вторым входом элемента «И 3, - К выходу 14 сигнала запуска, а выход соединен с входом установки «1 триггера блокировки 10; дешифратор 15, в котором один из входов схемы (совпадения нулевого канала подключен IK выходу «1 триггера блокиров1ки 10, другие входы всех схем совпадения соединены известным способом с выходом счетчика 2, а с выхода 16 поступают сигналы управления ключами соответствующих каналов.

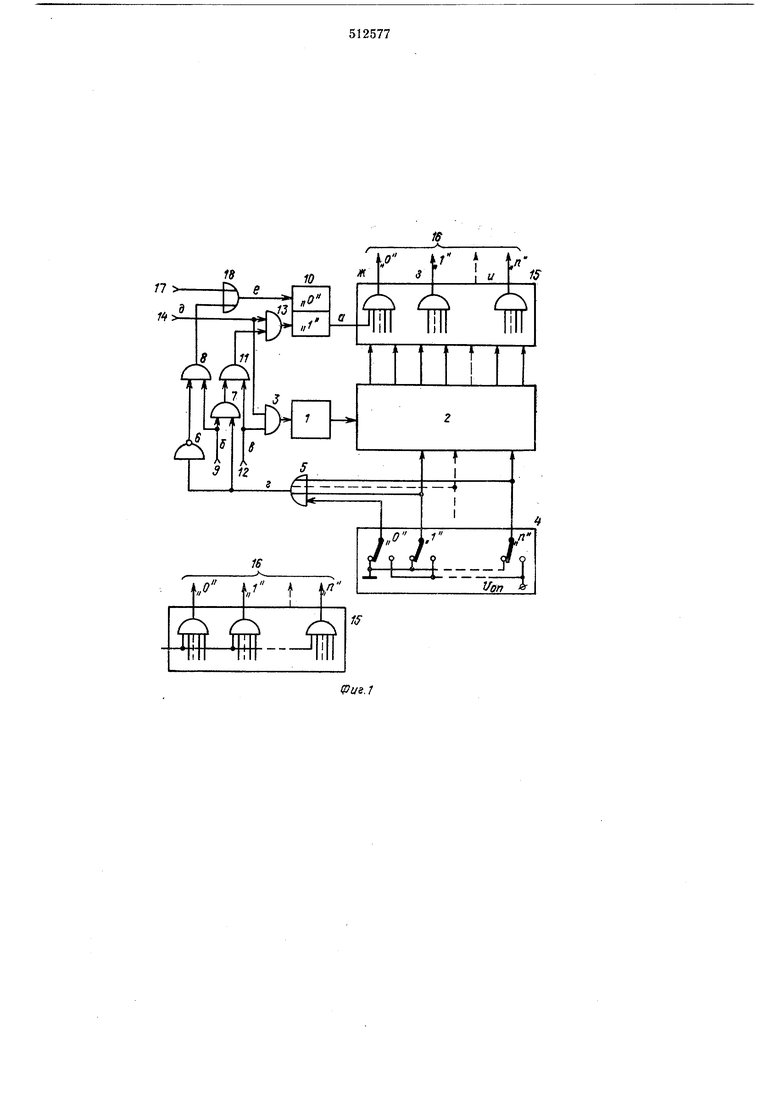

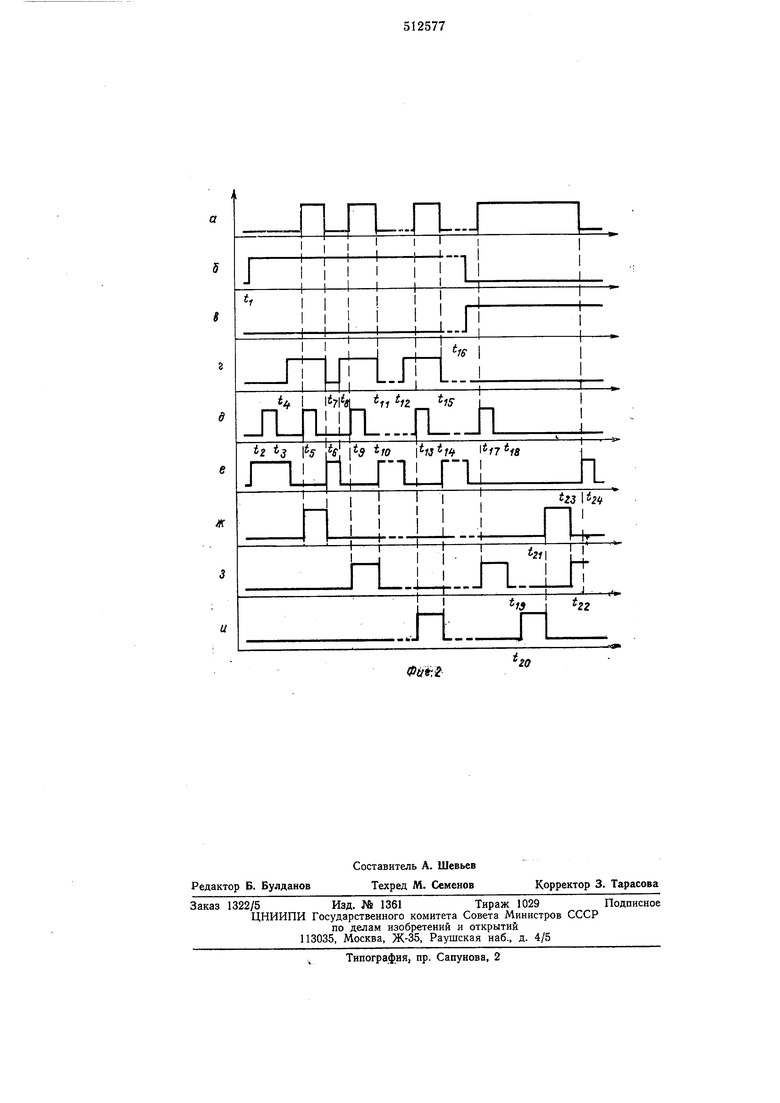

Работа коммутатора с устройством управления поясняется временной диаграммой на фиг. 2.

Условно считается, что после окончания работы в одном из выбранных режимов (когда снимается сигнал с выхода 9 или 12) формируется известным способом импульс сброса, который устанавливает триггер блокировки 10 в состояние «О (фиг. 2а).

При адресном режиме работы коммутатора сигнал управления с -выхода 9 поступит в момент ti (фиг. 26) на один из входов элемента «И 7 и элемента «И 8. Если адрес канала с формирователя адреса канала 4 не подается (фиг. 2г), то с выхода элемента «И 7 через элемент «ИЛИ 11 не будет поступать на элемент «И 13 сигнал совладения, разрешающий прОХождение с выхода 14 импульса запуска Тзап гз - 2 (фиг. 2г). Триггер 10 не изменит своего состояния «О (фиг. 2а) и на выходе 16 дешифратора 15 не будут, следовательно, формироваться сигналы управления ключом нулевого канала (фиг. 2ж). Не будут формироваться сигналы управлепия на выходе 16 и в том случае, если адрес, например, канала «О поступит с формирователя 4.в момент /4 (фиг. 2г), т. е. тогда, когда на элемент «И 13 уже не -поступает импульс запуска. Если же вслед за нодачей адреса канала «О с выхода 14 поступит в момент /5 (фит. 2(5) импульс запуска Тзап е - t, то триггер 10 перейдет в состояние «1 (фиг. 2а), и на выходе 16 дешифратора 15 сформируется (фиг. 2ж) сигнал управления ключом канала «О (как обусловлено, адрес канала «О с формирователя 4 не подается на счетчик 2, который, как известно, в исходном состоянии не

запреш,ает выход «О дешифратора 15). Когда же в момент tj (фиг. 2г) снимается адрес канала «О, то формируюп,ийся на выходе элемента «И 8 импульс своим фронтом

5 (фиг. 2е) установит триггер 10 в исходное состояние (фиг. 2а), и выход сигнала управления ключо.м 1канала «О будет запреи1,ен (фиг. 2ж). Из приведенного описания следует, что устройство в адресном режиме позволяет исключить неопределенность управления нулевым каналом (канал «О формируется в момент ty, когда поданы и сигнал адресного режима, и адрес канала «О, и сигнал запуска - фиг. 26, 2г, 2д - работы .коммутатора).

5 Кроме тото, в исходном состоянии (после подачи питания) коммутатор защищен от помех, так как в момент ti (фиг. 2е) на выходе элемента «И 8 формируется импульс, который своим фронтом установит триггер 10 в

0 положение «О (фиг. 2а), на один из входов всех схем совпадения дешифратора 15 поступит сигнал запрета, и на выходе 16 не будут формироваться сигналы управления ключами каналов коммутатора (фиг. 2ж, 2з и 2и). В

5 момент /8 может быть подан адрес канала «1 (фиг. 2г), который установит триггеры счетчика 2 в соответствующее положение и разрешит прохождение через элемент «И 13 в момент tg (фиг. 2д) импульса запуска Тзап

0 Триггер Ш перейдет в состояние «1 (фит. 2а) и снимет запрет на формирование сигналов упраВления ключами каналов, в том числе и ключом капала «1 (фиг. 2з) до момента /и, когда прекратится подача адреса канала «1 (фиг. 2г). Наконец, в момент /12 будет сформирован адрес канала «п, а в момент /13, когда поступит импульс запуска Тзап /14-/13 (фиг. 2д), на выходе 16 дешифратора 15 сигнал управления ключом

0 канала «п (фиг. 2м). В дальнейшем после снятия адреса канала «п в момент /15 (фиг. 2г) управление ключами каналов может быть продолжено в последовательпости, определяемой оператором или заданной прог5 раммой.

При работе коммутатора в циклическом режиме сигнал упра-вления с выхода 12 поступит в момент /16 (фиг. 2в) на один из в.ходов элементов «И 3 и (через элемент «ИЛИ 11)

0 «И 13. В момент tn (фиг. 2д) импульс Тзап /18 - /17 с выхода 14 установит триггер 10 в положение «1 (фиг. 2а) и запустит задающий генератор 1, с выхода которого тактовые импульсы начнут поступать на счетный

5 вход запуска счетчика 2. На выходе 16 дешифратора 15 будут формпроваться последовательно во времени сигналы управления ключами каналов коммутатора. К общему выходу в момент /17 (фиг. 2а) подключится первый канал на время .ДГ1 /|9-/п, в момепт /аи (фиг. 2и) -«я, канал на время Д7„ /21- - - /20, в момент /21 (фиг. 2ж) - нулевой канал на время АГо /22 - /2i и т. д. (при постоянной частоте тактовых импульсов время

5 подключения каждото канала к общему выходу одинаково, т. е. A7i ... Д7,1 АГо). Переключение каналов в цикле будет происходить до тех пор, пока в момент 4з (фиг. 2е) импульс сброса Тсбр 44-tza с выхода 17. сформирова-нный известным способом, не установит (фиг. 2а), например, через элемент «ИЛИ 18 триггер 10 в положение «О и запретит работу задающего генератора 1. Из описания работы устройства в циклическом режиме ясно, что оно позволяет исключить неопределенность управления нулевым каналом В исходном состоянии, в момент tif, (фиг. 2в) на один из входов схемы совпадения нулевого каиала дешифратора 15 подается запрет (фиг. 2а) и на выходе 16 не формируется сигнал управления ключом канала «О (фиг. 2ж). Кроме того, согласно принятому условию триггер 10 при смене режима работы установится в исходное состояние, и сигнал запрета, ломимо схемы совпадения нулевого канала дешифратора 15, будет подан на один из входов схем совпадения других каналов, поэтому на ;выходе 16 не будут формироваться сигналы управления ключами каналов (фиг. 2ж, 2з, 2и) в интервале времени от 16 до /17. Следовательно, данное устройство и в циклическом режиме обеспечивает помехоустойчивость коммутатора от момента подачи питания и сигнала выбора режима до момента поступления сигнала управления.

Формула изобретения

1. Устройство управления коммутатором, содержаш;ее Счетчик, входы которого подключены к выходу задающего генератора, и квыходам формирователя адреса, а выходы подключены к входам дешифратора, отличающееся тем, что, с целью исключения неоиределенности управления нулевым каналом коммутатора, введены триггер блокировки, элементы «ИЛИ, «И и инвертор, причем выходы формирователя адреса через элемент «ИЛИ подключены к входу одного элемента «И и дополнительно через инвертор к входу второго элемента «И, а другие входы элементов «И соединены с шиной управления адресным режимом работы коммутатора, при этом выход одного элемента «И подключен

к входу установ1ки «О триггера блокировки через элемент «ИЛИ, другой вход (которого подключен к шипе сброса, а выход второго элемента «И подключен к входу установки «1 триггера блокировки через элемент «ИЛИ,

другой вход которого подключен к щине управления циклическим режимом, и элемент «И, другой вход которого подключен к шине запуска, а выход «1 триггера блокировки соединен с одним из входов схемы совпадеПИЯ нулевого канала дешифратора.

2. Устройство по п. 1, отличающееся тем, что, с целью повышения помехоустойчивости, вход схемы совпадения нулевого канала дешифратора, подключенный к выходу «1 триггера блокировки, соединен с соответствующими входами схем совпадения других каналов.

f8

/7 5

mi-rLJ

а

I

I I I

I I г

.J

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Коммутатор | 1980 |

|

SU884138A1 |

| Устройство для считывания графической информации | 1988 |

|

SU1536413A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Цифровые вторичные часы | 1988 |

|

SU1511733A1 |

| Устройство контролируемого пункта системы телемеханики | 1986 |

|

SU1374266A1 |

| Коммутатор | 1981 |

|

SU976499A1 |

| Цифровой генератор периодической функции | 1987 |

|

SU1432491A1 |

4 I rr 1Z 1S 1

Jum.-(i-.Ji

j i.j Lii-t tj. j,-1

г j fs. w

/ иЖггии-

iK

tZ3 Zt

EL

J-L.LL..n.UT

«W

гг

Авторы

Даты

1976-04-30—Публикация

1973-07-16—Подача