соединен с прямым входом элемеи-та И-НЕ каждого канала приема и анализа контрольной информации, вход вьгаачи группы адресных входов устройства соединен с вторым входом второг элемента ИЛИ и прямым управляюищм входом первого дешифратора каждого канала приема и анализа контрольной информации, выходы которого соединены с входами синхронизации соответствующего регистра контроля, п выходов первого дешифратора соединены с соответствующими входамтя третьего элемента ИЛИ, инверсный выход которого соед,инен с управляющими входами шинных формирователей первой группы, выходы шинных формирователей первой группы соединены с информационными входами соответствующих регистров контроля, выходы которых соединены с первыми входами соответствуюш1их блоков поразрядного сравнения, группа информационных входов устройства соединена с вторыми входами соответствующих N блоков поразрядного сравнения m каналов приема и анализа контрольной информации, выходы которых соединены с информационными входами шинных формирователей, второй - (т+1)-и групп соответственно, И первых инверсных выходов второго дешифратора соединены с управляющими входами 1Ш1нных формирователей второй (п+1)-й групп соотвстственпо, выходы j -X и1иннь х формирователей второй (j+1)H групп (где j 1,8) соединены с информационным входом j -го шинного формирователя первой группы и i -м входом-выходом группы входов-выходов данных устройства, выходы К-го блока поразрядного сравнения каждого канала приема и анализа контрольной информации соединены с входами К-го элемента ИЛИ группы (где К 1,W ), выход каждого элемента .ИЛИ группы соединен с соответствующем входом шифратора и входом первого элемента 1-ШИ соответствующего канала приема и анализа контрольной информации, выход первого элемента НЕ соединен с первыми входами первого и второгО элементов И-КЕ, выход которого соединен с первыми

829

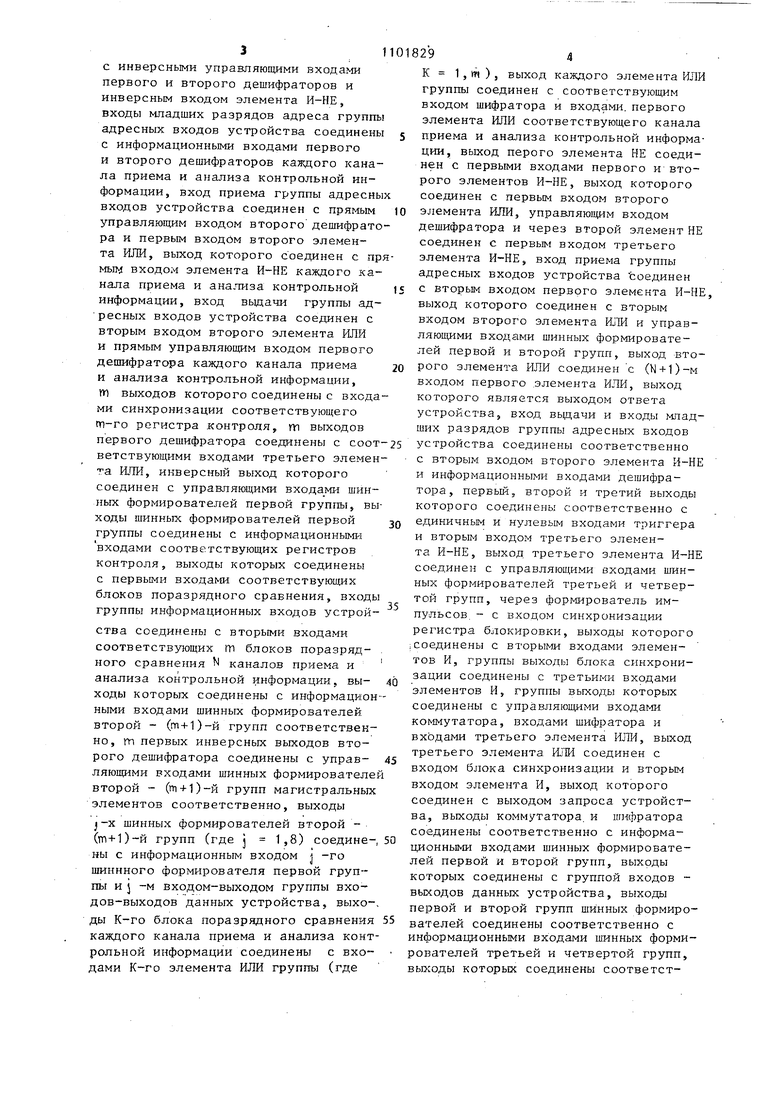

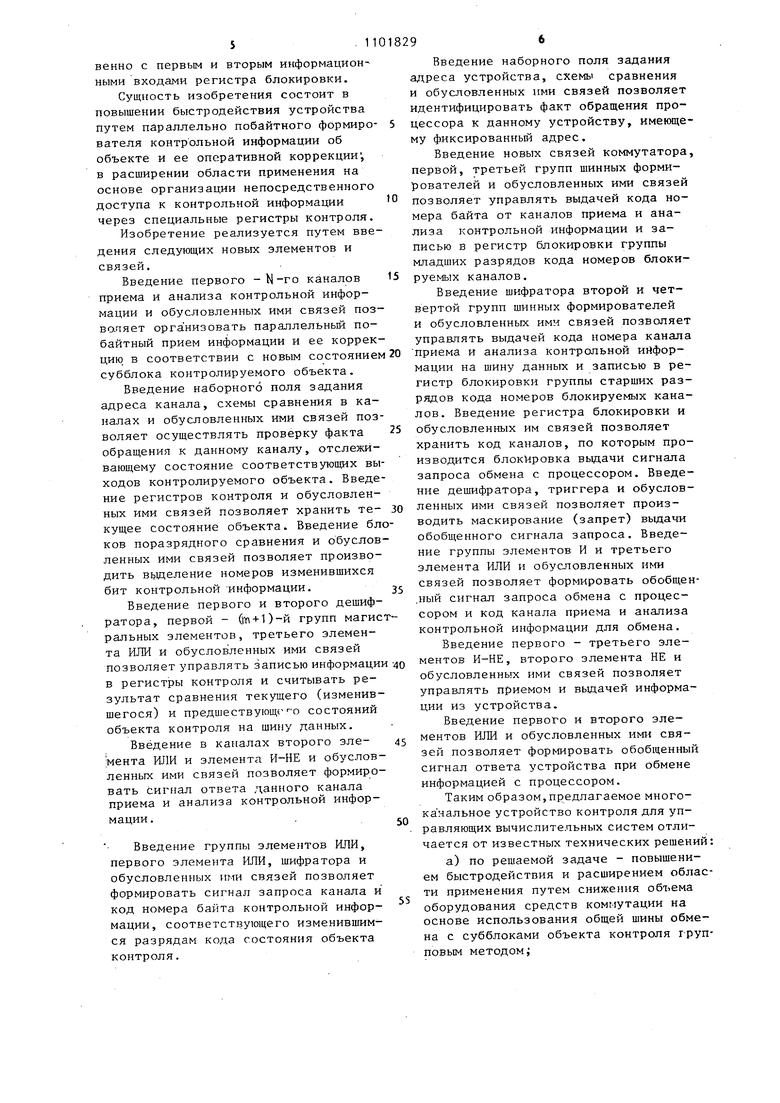

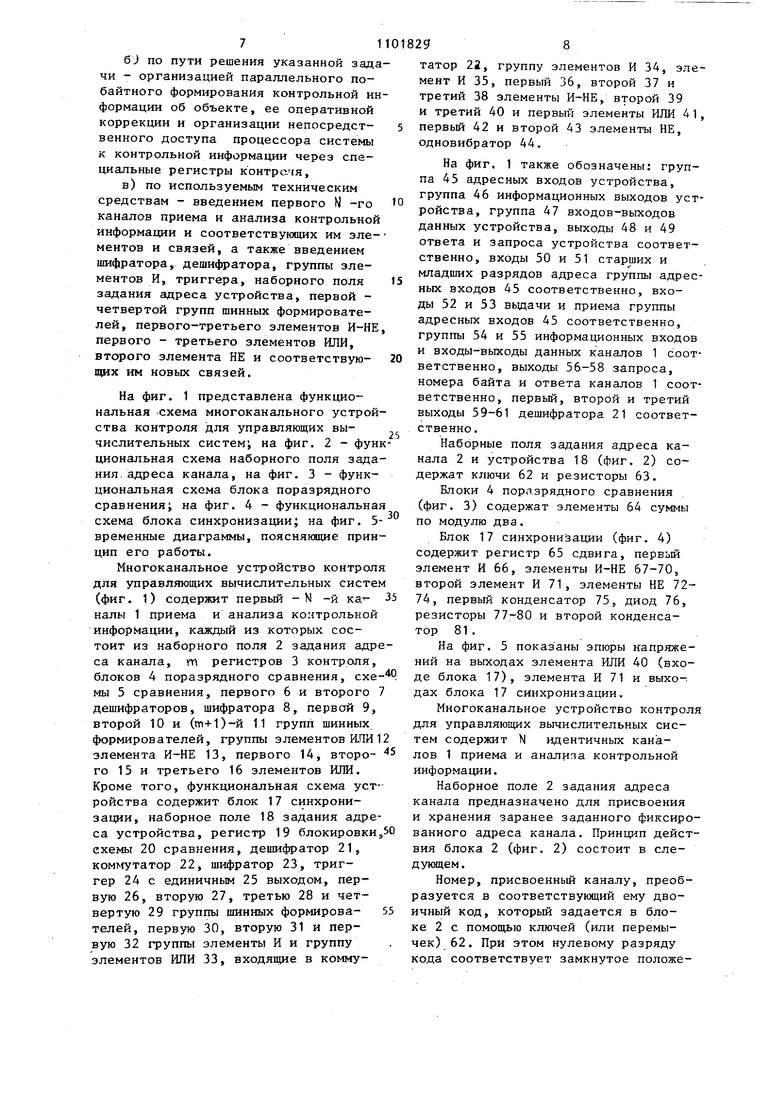

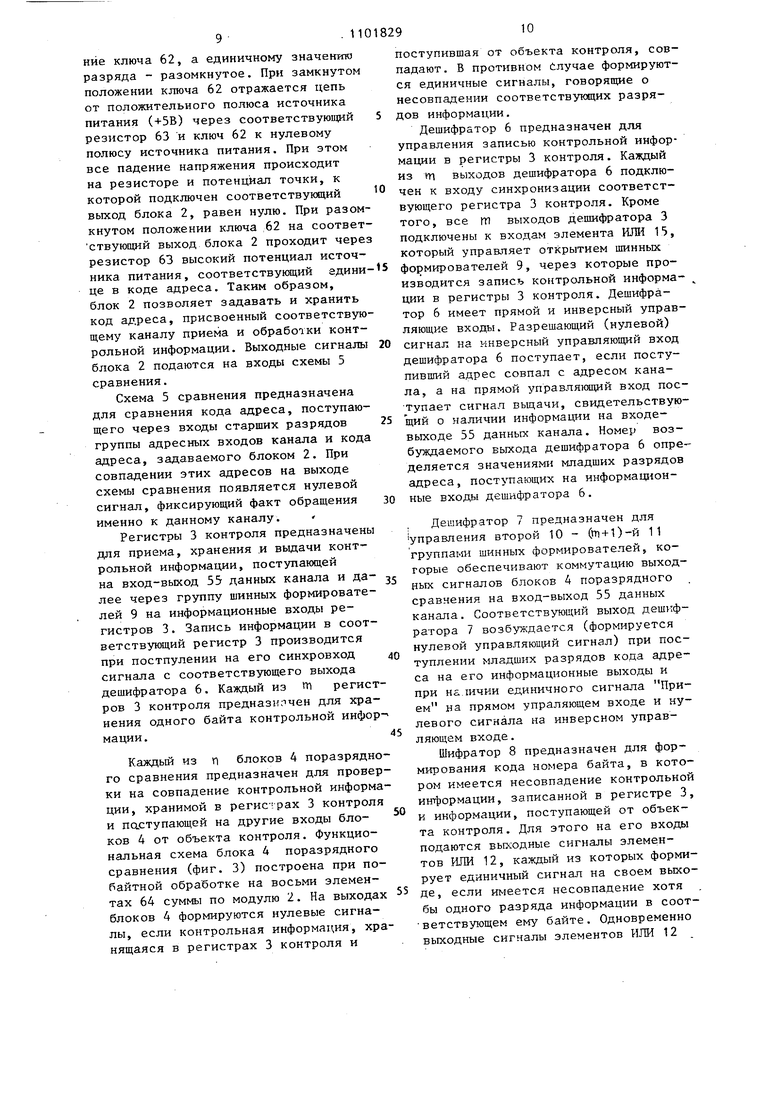

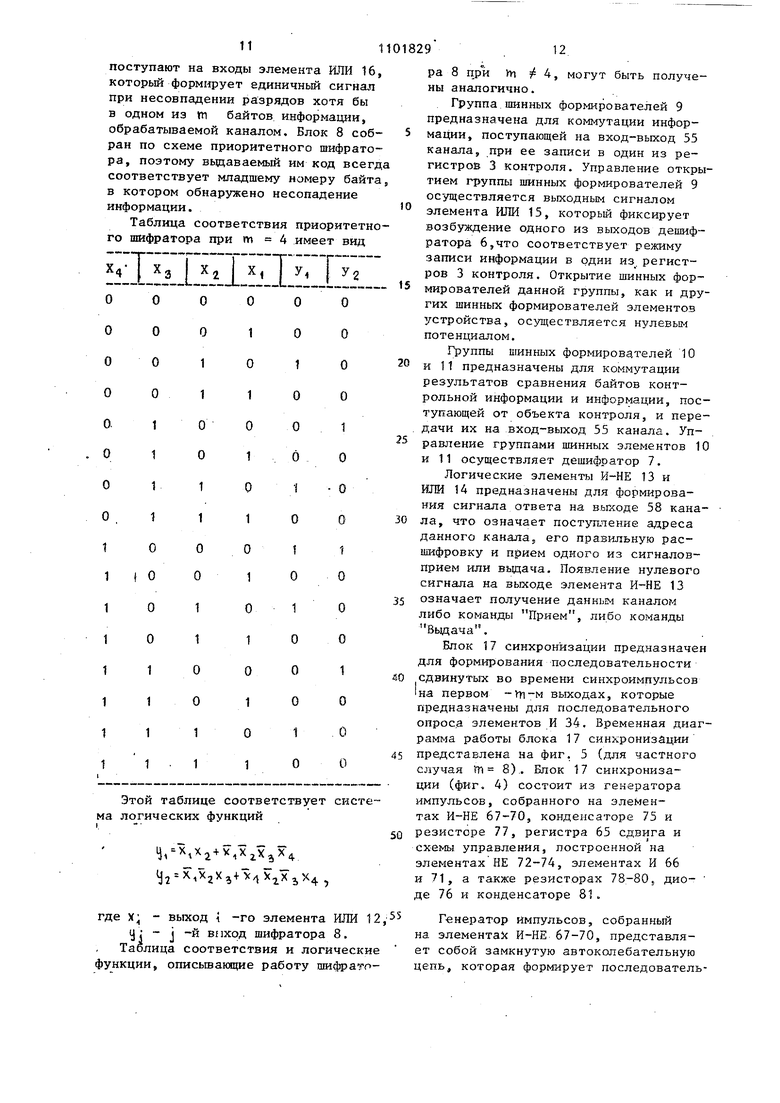

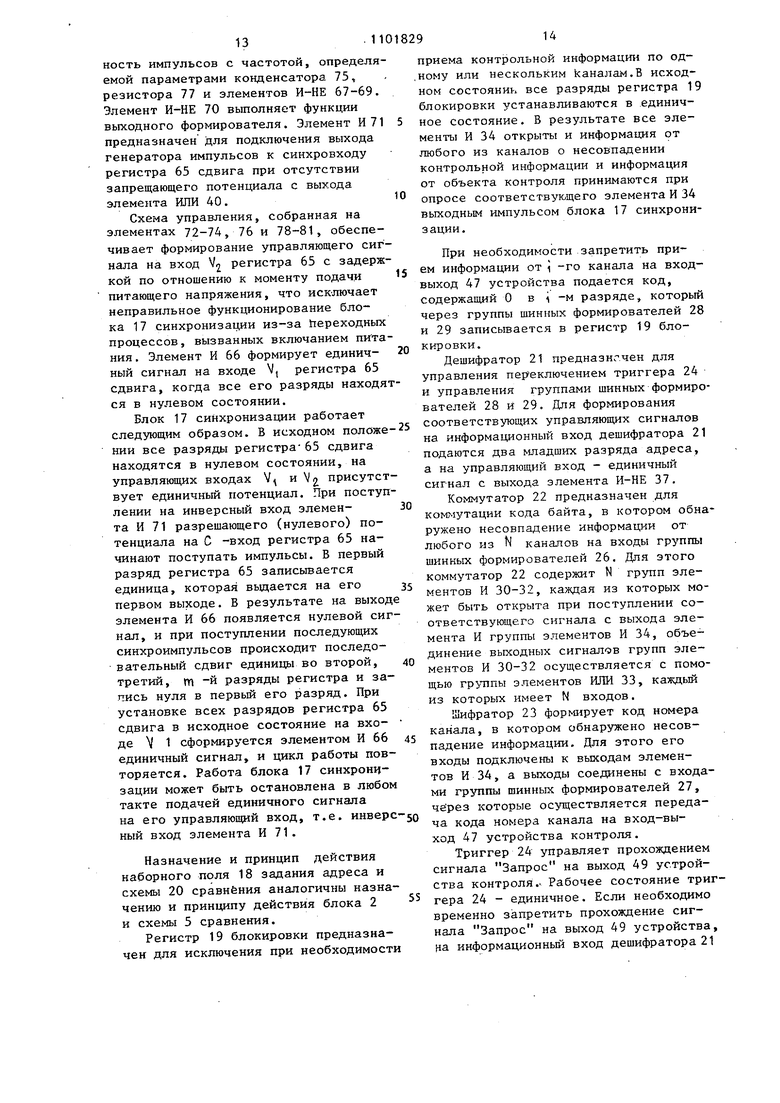

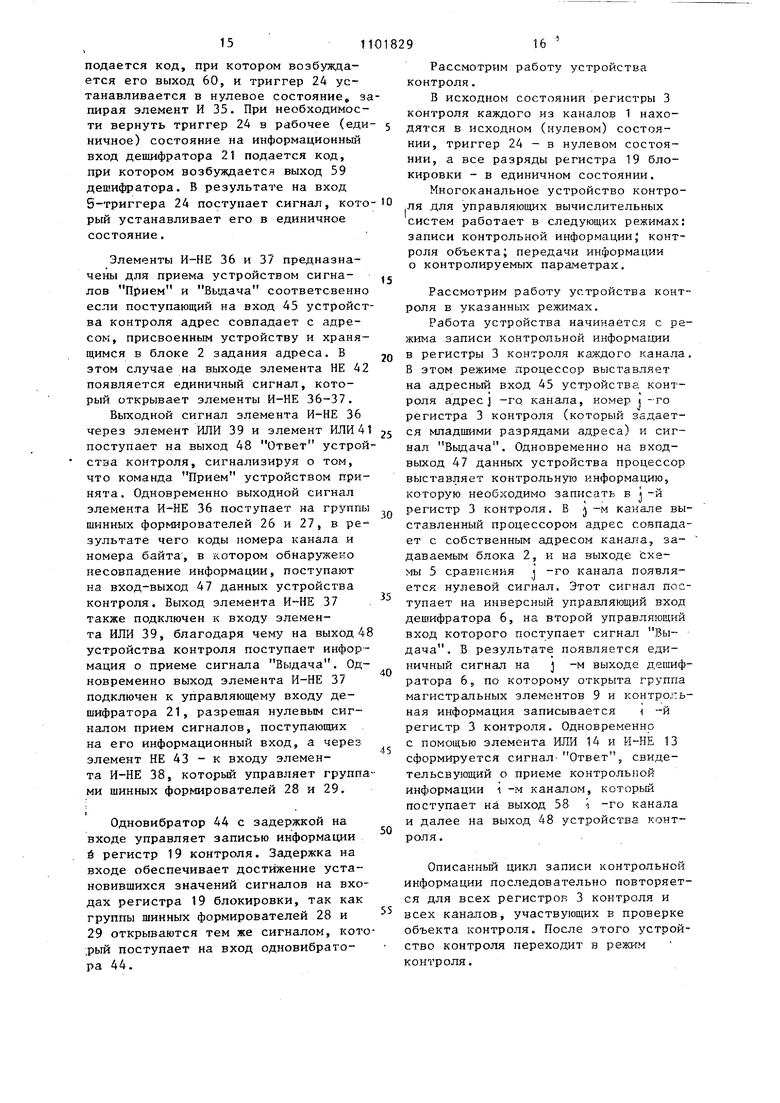

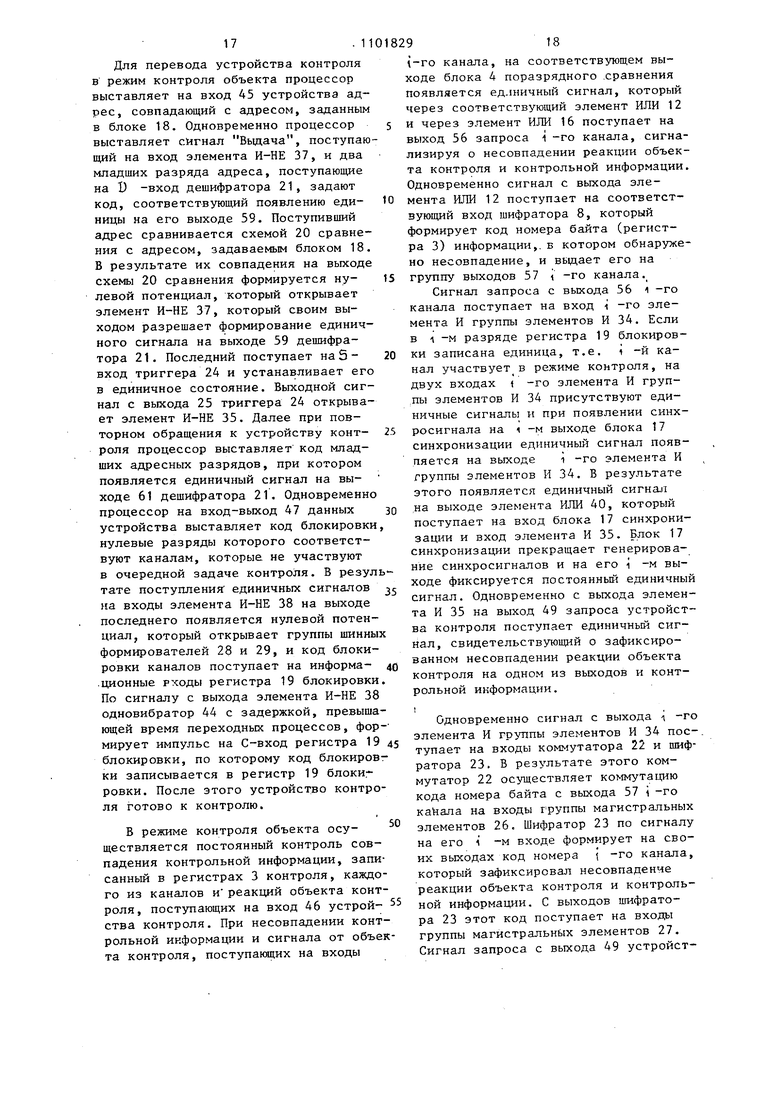

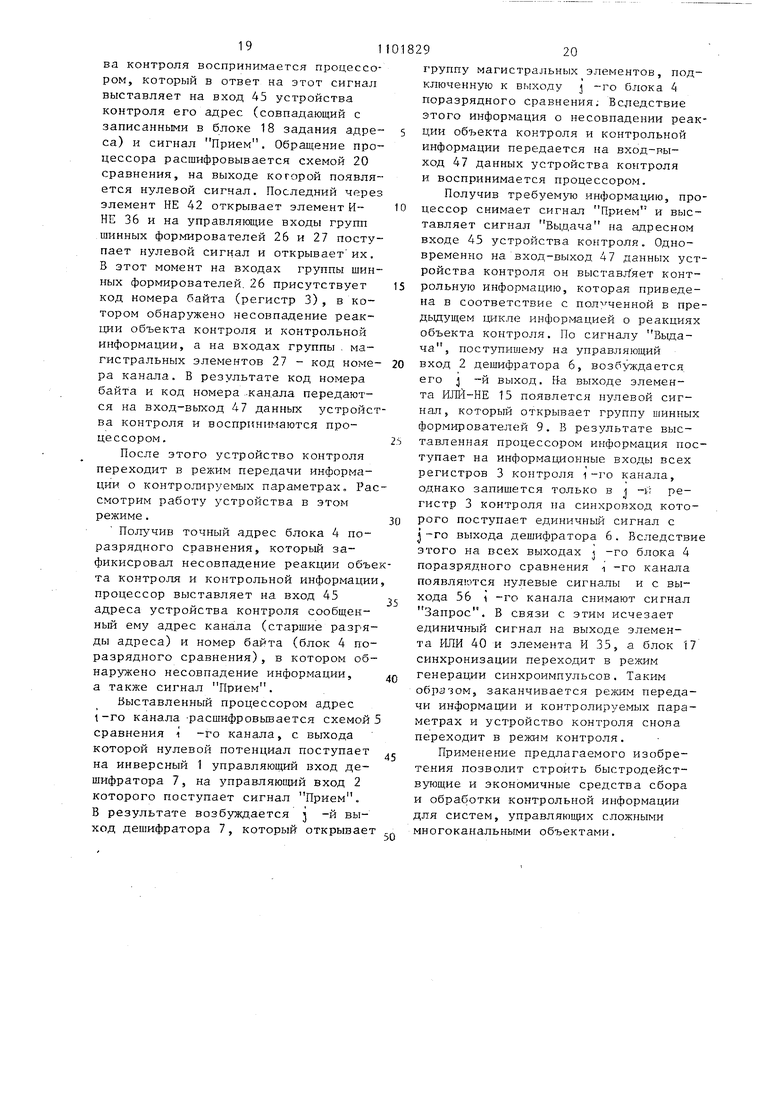

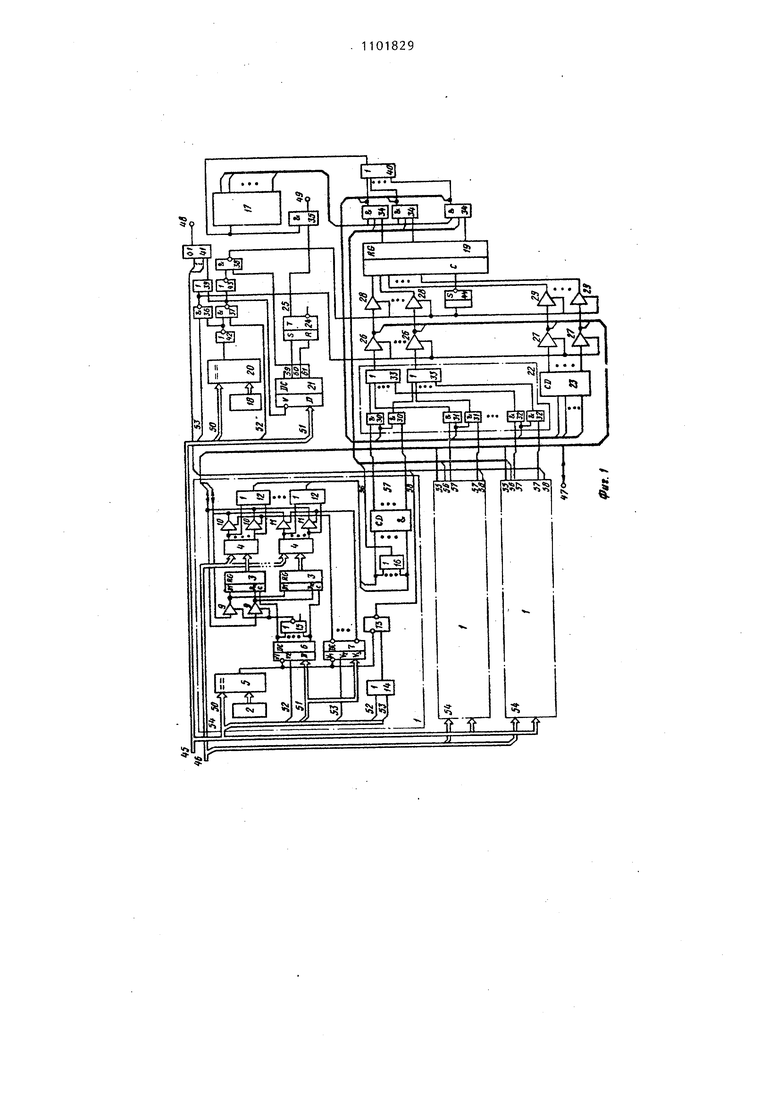

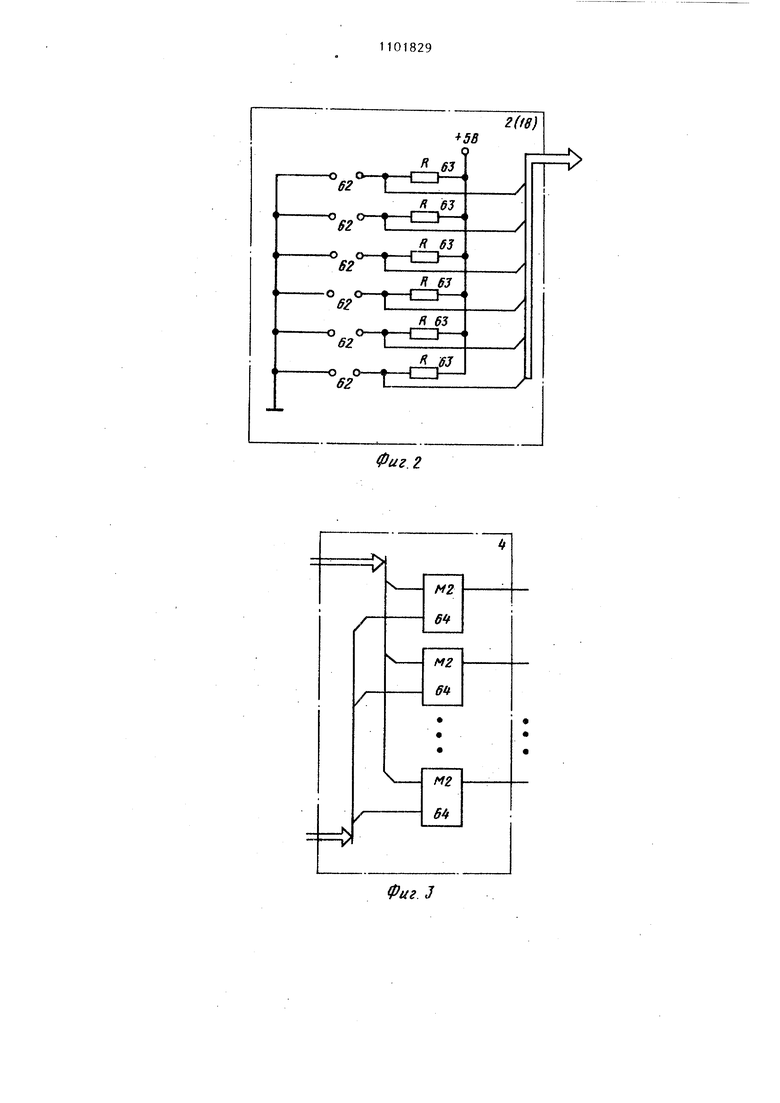

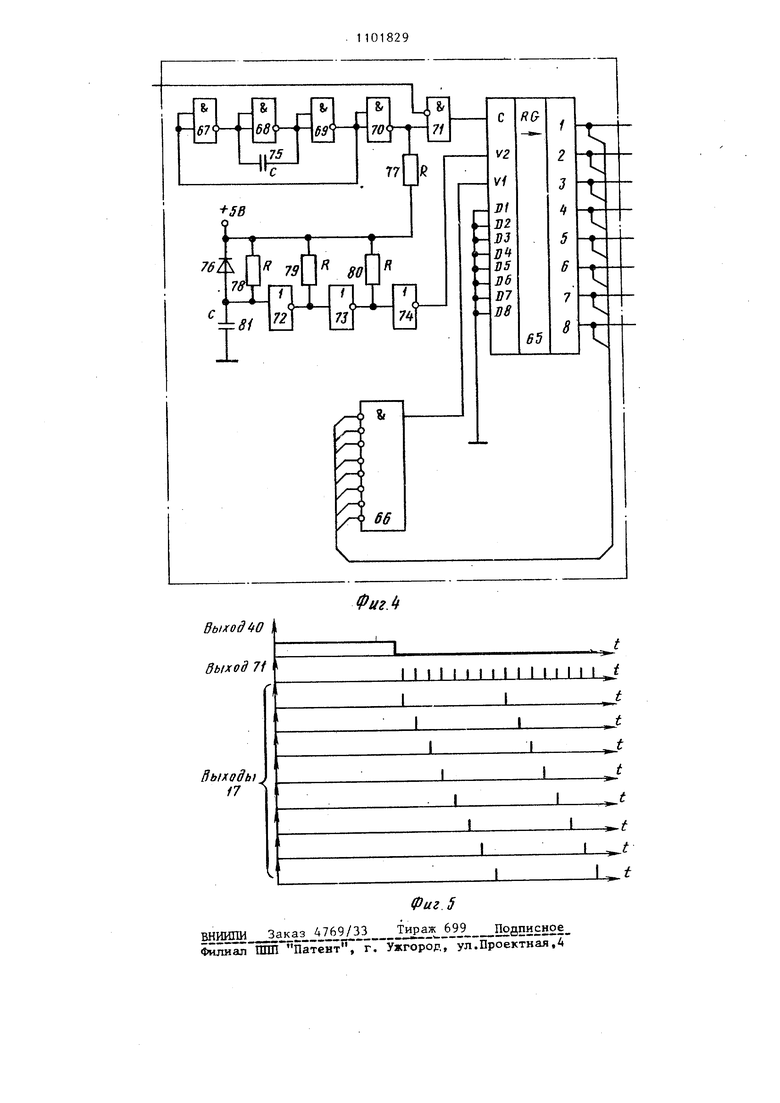

входами; второго элемента ИЛИ, управляющим входом дешифратора и через второй элемент НЕ - с первым входом третьего элемента , вход приема группы адресных входов устройства соединен с вторым входом первого элемента И-НЕ, выход которого соединен с вторы входом второго элемента ИЛИ и управляющими входами шинных формирователей первой и второй групп, выход второго элемента ИЛИ соединен с (гп+1)-м входом первого элемента ИЛИ, выход которого является выходом ответа устройства, вход вьгдачт и входы младших разрядов группы адресных входов устройства соединены соответственно с вторь&1 входом второго элемента И-НЕ и инфомационными входами дешифратора, первьш, второй и третий выходы которого соединены соответственно с единичным и нулевым входами триггера и вторым входом третьего элемента И-НЕ, выход третьего элемента И-НЕ соединен с управляющими входами шинных формирователей третьей и четвертой группы и через формирователь импульсов - с входом синхронизации регистра блокировки, выходы которого соединены с вторыми входами элементов И группы, выходы блока синхронизации соединены с третьими входами элементов И группь, выходы которь х соединены с управляющими входами коммутатора, входами шифратора и входами третьего элемента ИЛИ, выход третьего элемента ИЛИ соединен с входом блока синхронизации и вторым входом элемента И, выход которого соединен с выходом запроса устройства, выходы коммутатора и шифратора соединены соответственно с информационными входами шинных формирователей первой и второй групп, выходы которых соединены с группой входов-выходов данных устройства, выходы первой и второй групп шинных формирователей соединены соответственно с информационными входами шинных формирователей третьей и четвертой групп, выходы KOTopbDC соединены соответственно с первым и вторым информационными входами регистра блокировки. 1. 1 Изобретение относится к автоматика и вычислительной технике и может быть использовано при разработке уст ройств и подсистем тестового и функционального диагностирования управляющих вычислительных систем, предназначенных для управления сложными распределенными объектами. Известно устройство контроля, содержащее коммутатор, регистр, схем сравнения и элемент ИЛИ lj . Недостатком этого устройства явется большой объем оборудования при его использовании для контроля сложных многовыходных систем. Известно также устройство контро ля сложных программных автоматов, содержащее коммутаторы, регистры, элементы И 2j . Недостатком указанного устройства является узкая область применения, обусловленная тем, что при группировании выходов объекта по функциональному признаку число таких групп а следовательно, и объем оборудования обработки контрольной информаци весьма велико. Наиболее близким к предлагаемому изобретению по технической сущности и достигаемому положительному эффекту является устройство контроля, содержащее блок синхронизации, коммута тор, схему сравнения, регистр, счетчик, триггер, элемент И, элемент НЕ причем выход блока синхронизации и единичный выход триггера соединены с первым и вторым входами элемента И соответственно, выход которого соеди нен со счетным входом счетчика, вход запуска устройства соединен с единичным входом триггера, управляю щим входом коммутатора установочным входом счетчика, выход которого является выходом устройства, информ ционне входы устройства соединены с информационными входами коммутатора первый - h-й выходы которого соединены соответственно с первым информационным входом регистра и первым (т1--1)-м входами схемы сравнения, - (2п-2)-й входы схемы сравнени соединены с первым - (п-1)-м выхода ми регистра, первый - (п-1)-й выход схемы сравнения соединены с вторым п-м информационными входами регистр соответственно, И-ii выход которого соединен с входом элемента НЕ, вы9ход которого соединен с нулевым входом триггера з . Недостатками известного устройства являются низкое быстродействие и узкая область применения. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в многоканальное устройство контроля для управляклцих вычислительных систем, содержащее блок синхронизации, схему сравнения, регистр блокировки, триггер, элемент И, первый элемент НЕ и коммутатор, причем единичный выход триггера соединен с первым входом элемента И, введены наборное поле задания адреса устройства, дешифратор, шифратор, группа элементов И, четыре группы шинных формирователей, первый, второй и третий элементы И-НЕ, первый, второй и третий элементы ИЛИ, формирователь импульсов, второй элемент НЕ, N каналов приема и анализа контрольной информации, каждый из которых содержит In регистров контроля, наборное поле задания адреса канала, m блоков поразрядного сравнения, схему сравнения, первый и второй дешифраторы, шифратор, группу элементов ИЛИ, (т+1) группу шинных формирователей, первьй, второй и третий элементы ИЛИ и элемент И-НЕ, причем входы старших разрядов адреса группы адресных входов устройства и выходы наборного поля задания адреса устройства соединены соответственно с первой и второй группами входов схемы сравнения, выход которой соединен с входом первого элемента НЕ, выход первого элемента ШИ i -го канала приема и анали за контрольной информации (где 1 ,N) соединен с первым входом -го элемента И группы, выход элемента И-НЕ, канала приема и анализа контрольной информа1Ц1и соединен с i -м входом первого элемента-ИЛИ, группа выходов шифратора i -го канала приема и -анализа контрольной информации соединена с i -и группой информационных входов коммутатора, входы старших разрядов группы адресных входов устройства и выходы наборного поля задания адреса канала соединены соответственно с первым и вторым входами схемы сравнения соответг,твуюш,его канала приема и анализа контрольной информации, выход которой соединен с инверсными управляющими входами первого и второго дешифраторов и инверсным входом элемента И-НЕ, входы младших разрядов адреса группы адресных входов устройства соединены с информационными входами первого и второго дешифраторов каждого канала приема и анализа контрольной информации, вход приема группы адресны входов устройства соединен с прямым управляющим входом второго дешифрато ра и первым входим второго элемента ИЛИ, выход которого соединен с пр мым входом элемента И-НЕ каждого канала приема и анализа контрольной информации, вход вьщачи группы адресных входов устройства соединен с вторым входом второго элемента ИЛИ и прямым управляющим входом первого дешифратора каждого канала приема и анализа контрольной информации, W выходов которого соединены с входа ми синхронизации соответствующего т-го регистра контроля, пп выходов первого дешифратора соединены с соот ветствующими входами третьего элемен та ИЛИ, инверсный выход которого соединен с управляющими входами шинных формирователей первой группы, вы ходы шинных формирователей первой группы соединены с информационными входами соответствующих регистров контроля, выходы которых соединены с первыми входами соответствующих блоков поразрядного сравнения, входы группы информационных входов устройства соединены с вторыми входами соответствующих m блоков поразрядного сравнения N каналов приема и анализа контрольной информации, выходы которых соединены с информацион ными входами шинных формирователей второй - (т+1)-й групп соответственно, гп первых инверсных выходов второго дешифратора соединены с управляющими входами шинных формирователе второй - ()-й групп магистральных элементов соответственно, выходы J-X шинных формирователей второй (пп+1)-й групп (где 3 1,8) соединены с информационным входом j -го щиннного формирователя первой группы и j -м входом-выходом группы входов-выходов данных устройства, выходы К-го блока поразрядного сравнения каждого канала приема и анализа конт рольной информации соединены с входами К-го элемента ИЛИ группы (где К 1,W ), выход каждого элемента ИЛИ группы соединен с соответствующим входом шифратора и входами, первого элемента ИЛИ соответствующего канала приема и анализа контрольной информации, выход перого элемента НЕ соединен с первыми входами первого и второго элементов И-НЕ, выход которого соединен с первьм входом второго элемента ИЛИ, управляющим входом дешифратора и через второй элемент НЕ соединен с первьм входом третьего элемента И-НЕ, вход приема группы адресных входов устройства соединен с вторым входом первого элемента И-НЕ, выход которого соединен с вторым входом второго элемента ИЛИ и управляющими входами шинных формирователей первой и второй групп, выход второго элемента ИЛИ соединен с (W-fl)-M входом первого .элемента ИЛИ, выход которого является выходом ответа устройства, вход выдачи и входь; младших разрядов группы адресных входов устройства соединены соответственно с вторым входом второго элемента И-НЕ и информационными входами дешифратора, первый, второй и третий выходы которого соединены соответственно с единичным и нулевым входами триггера и вторым входом третьего элемента И-НЕ, выход третьего элемента И-НЕ соединен с управляющими входами шинных формирователей третьей и четвертой групп, через формирователь импульсов. - с входом синхронизации регистра блокировки, выходы которого соединены с вторыми входами элементов И, группы выходы блока синхронизации соединены с третьими входами элементов И, группы выходы которых соединены с управляющими входами коммутатора, входами шифратора и входами третьего элемента ИЛИ, выход третьего элемента ИЛИ соединен с входом блока синхронизации и вторым входом элемента И, выход которого соединен с выходом запроса устройства, выходы коммутатора, и шифратора соединены соответственно с информационными входами шинных формирователей первой и второй групп, выходы которых соединены с группой входов выходов данных устройства, выходы первой и второй групп шинных формирователей соединены соответственно с информационными входами шинных формирователей третьей и четвертой групп, вькоды которых соединены соответственно с первым и вторым информацион ными входами регистра блокировки. Сущность изобретения состоит в повышении быстродействия устройства путем параллельно побайтного формиро вателя контрольной информации об объекте и ее оперативной коррекции, в расширении области применения на основе организации непосредственного доступа к контрольной информации через специальные регистры контроля. Изобретение реализуется путем вве дения следующих новых элементов и связей. Введение первого -М-го каналов приема и анализа контрольной информации и обусловленных ими связей поз воляет орга низовать параллельный побайтный прием информации и ее коррек цию в соответствии с новым состояние субблока контролируемого объекта. Введение наборного поля задания адреса канала, схемы сравнения в каналах и обусловленных ими связей поз воляет осуществлять проверку факта обращения к данному каналу, отслеживающему состояние соответствующих вы ходов контролируемого объекта. Введе ние регистров контроля и обусловленных ими связей позволяет хранить текущее состояние объекта. Введение бл ков поразрядного сравнения и обуслов ленных ими связей позволяет производить вьщеление номеров изменившихся бит контрольной информации. Введение первого и второго дешифратора, первой - (т + 1)-й групп магис ральных элементов, третьего элемента ИЛИ и обусловленных ими связей позволяет управлять записью информаци в регистры контроля и считывать результат сравнения текущего (изменившегося) и предшествующео состояний объекта контроля на шину данных. Введение в каналах второго элемента ИЛИ и элемента И-НЕ и обусловленных ими связей позволяет формировать сигнал ответа данного канала приема и анализа контрольной информации . Введение группы элементов ИЛИ, первого элемента ШИ, шифратора и обусловленных ими связей позволяет формировать сигнал запроса канала и код номера байта контрольной информации, соответствующего изменившимся разрядам кода состояния объекта контроля. 1 96 Введение наборного поля задания адреса устройства, схемы сравнения и обусловленных ими связей позволяет идентифицировать факт обращения процессора к данному устройству, имеющему фиксированный адрес. Введение новых связей коммутатора, первой, третьей групп шинных формирователей и обусловленных ими связей позволяет управлять выдачей кода номера байта от каналов приема и анализа контрольной информации и записью в регистр блок11ровки группы младших разрядов кода номеров блокируемых каналов. Введение шифратора второй и четвертой групп шинных формирователей и обусловленных ими связей позволяет упраштять выдачей кода номера канала приема и анализа контрольной информации на шину данных и записью в регистр блокировки группы старших разрядов кода номеров блокируемых каналов. Введение регистра блокировки и обусловленных им связей позволяет хранить код каналов, по которым производится блокировка выдачи сигнала запроса обмена с процессором. Введение дешифратора, триггера и обусловленных ими связей позволяет производить маскирование (запрет) выдачи обобщенного сигнала запроса. Введение группы элементов И и третьего элемента ИЛИ и обусловленных ими связей позволяет формировать обобщен,ный сигнал запроса обмена с процессором и код канала приема и анализа контрольной информации для обмена. Введение первого - третьего элементов И-НЕ, второго элемента НЕ и обусловленных ими связей позволяет управлять приемом и выдачей информации из устройства. Введение первого и второго элементов ИЛИ и обусловленных ими связей позволяет формировать обобщенный сигнал ответа устройства при обмене информацией с процессором. Таким образом,предлагаемое многоканальное устройство контроля для управляющих вычислительных систем отличается от известных технических решений: а) по решаемой задаче - повышением быстродействия и расширением области применения путем снижения объема оборудования средств коммутации на основе использования общей шины обмена с субблоками объекта контроля групповым методом; б)ПО пути решения указанной зада чи - организацией параллельного побайтного формирования контрольной ин формации об объекте, ее оперативной коррекции и организации непосредственного доступа процессора системы к контрольной информации через специальные регистры контрачя, в)по используемым техническим средствам - введением первого N -го каналов приема и анализа контрольной информации и соответствующих им элементов и связей, а также введением шифратора, дешифратора, группы злементов И, триггера, наборного поля задания адреса устройства, первой четвертой групп шинных формирователей, первого-третьего элементов И-НЕ первого - третьего элементов ИЛИ, второго элемента НЕ и соответствующих им новых связей. На фиг. 1 представлена функциональная Схема многоканального устрой ства контроля для управляющих вычислительных систему на фиг. 2 - фун циональная схема наборного поля зада ния, адреса канала, на фиг. 3 - функциональная схема блока поразрядного сравнения на фиг. 4 - функциональна схема блока синхронизации; на фиг. 5 временные диаграммы, поясняющие прин цип его работы. Многоканальное устройство контрол для управляющих вычислительных систе (фиг. 1) содержит первый - N -и каналы 1 приема и анализа контрольной информации, каждый из которых состоит из наборного поля 2 задания адр са канала, т регистров 3 контроля, блоков 4 поразрядного сравнения, схе мы 5 сравнения, первого 6 и второго дешифраторов, шифратора 8, первой 9, второй 10 и (т+1)-й 11 групп шинных формирователей, группы элементов ИЛИ элемента И-НЕ 13, первого 14, второго 15 и третьего 16 элементов ИЛИ. Кроме того, функциональная схема уст ройства содержит блок 17 синхронизащ1и, наборное поле 18 задания адре са устройства, регистр 19 блокировки схемы 20 сравнения, дешифратор 21, кoм ryтaтop 22, шифратор 23, триггер 24 с единичным 25 выходом, первую 26, вторую 27, третью 28 и четвертую 29 группы шинных формирователей, первую 30, вторую 31 и первую 32 группы элементы И и группу элементов ИЛИ 33, входящие в коммутатор 22, группу элементов И 34, элемент И 35, первый 36, второй 37 и третий 38 элементы И-НЕ, второй 39 и третий 40 и первый элементы ИЛИ 41, первый 42 и второй 43 элементы НЕ, одновибратор 44. На фиг. 1 также обозначены: группа 45 адресных входов устройства, группа 46 информационных выходов устройства, группа 47 входов-выходов данных устройства, выходы 48 и 49 ответа и запроса устройства соответственно, входы 50 и 51 старших и младших разрядов адреса группы адресных входов 45 соответственно, входы 52 и 53 вьщачи и приема группы адресных входов 45 соответственно, группы 54 и 55 информационных входов и входы-выходы данных каналов 1 соответственно, выходы 56-58 запроса, номера байта и ответа каналов 1 соответственно, первый, второй и третий выходы 59-61 дешифратора 21 соответственно. Наборные поля задания адреса канала 2 и устройства 18 (фиг. 2) содержат ключи 62 и резисторы 63. Блоки 4 поразрядного сравнения (фиг. 3) содержат элементы 64 суммы по модулю два. Блок 17 синхронизации (фиг. 4) содержит регистр 65 сдвига, первый элемент И 66, элементы И-НЕ 67-70, второй элемент И 71, элементы НЕ 7274, первый конденсатор 75, диод 76, резисторы 77-80 и второй конденсатор 81 . На фиг. 5 показаны эпюры напряжений на выходах элемента ИЛИ 40 (входе блока 17), элемента И 71 и выходах блока 17 синхронизации. Многоканальное устройство контроля для управляю1цих вычислительных систем содержит N идентичных каналов 1 приема и анализа контрольной информации. Наборное поле 2 задания адреса канала предназначено для присвоения и хранения заранее заданного фиксированного адреса канала. Принцип действия блока 2 (фиг. 2) состоит в следующем. Номер, присвоенный каналу, преобразуется в соответствующий ему двоичный код, который задается в блоке 2 с помощью ключей (или перемычек) 62. При этом нулевому разряду кода соответствует замкнутое положа9.1 нйе ключа 62, а единичному значениго разряда - разомкнутое. При замкнутом положении ключа 62 отражается цепь от положительного полюса источника питания (+5В) через соответствующий резистор 63 и ключ 62 к нулевому полюсу источника питания. При этом все падение напряжения происходит на резисторе и потенциал точки, к которой подключен соответствующий выход блока 2, равен нулю. При разом кнутом положении ключа 62 на соответ ствующий выход блока 2 проходит чере резистор 63 высокий потенциал источника питания, соответствукхций едини це в коде адреса. Таким образом, блок 2 позволяет задавать и хранить код адреса, присвоенный соответствую щему каналу приема и обработки контрольной информации. Выходные сигналы блока 2 подаются на входы схемы 5 сравнения. Схема 5 сравнения предназначена для сравнения кода адреса, поступающего через входы старших разрядов группы адресных входов канала и кода адреса, задаваемого блоком 2. При совпадении этих адресов на выходе схемы сравнения появляется нулевой сигнал, фиксирующий факт обращения именно к данному каналу. Регистры 3 контроля предназначены для приема, хранения ,и выдачи контрольной информации, поступающей на вход-выход 55 данных канала и далее через группу шинных формирователей 9 на информационные входы регистров 3. Запись информации в соответствующий регистр 3 производится при постпулении на его синхровход сигнала с соответствующего выхода дешифратора 6. Каждый из Ш регист ров 3 контроля предназначен для хранения одного байта контрольной инфор мации. Каждьш из л блоков 4 поразрядно го сравнения предназначен для провер ки на совпадение контрольной информа ции, хранимой в регистрах 3 контроля и паступающей на другие входы блоков 4 от объекта контроля. Функциональная схема блока 4 поразрядного сравнения (фиг. 3) построена при побайтной обработке на восьми элементах 64 суммы по модулю 2. На выходах блоков 4 формируются нулевые сигналы, если контрольная информация, хра нящаяся в регистрах 3 контроля и 9 поступившая от объекта контроля, совпадают . В противном Случае формируются единичные сигналы, говорящие о несовпадении соответствующих разрядов информации. Дешифратор 6 предназначен для управления записью контрольной информации в регистры 3 контроля. Каждый из m выходов дешифратора 6 подключен к входу синхронизации соответствующего регистра 3 контроля. Кроме того, все m выходов дешифратора 3 подключены к входам элемента HJli 15, который управляет открытием шинных формирователей 9, через которые производится запись контрольной информации в регистры 3 контроля. Дешифратор 6 имеет прямой и инверсный управляющие входы. Разрешающий (нулевой) сигнал на инверсный управляющий вход дешифратора 6 поступает, если поступивший адрес совпал с адресом канала, а на прямой управлякхций вход поступает сигнал выдачи, свидетельствующий о наличии информации на входевыходе 55 данных канала. Номер возбуждаемого выхода дешифратора 6 определяется значениями младших разрядов адреса, поступающих на информационные входы дешифратора 6. Дешифратор 7 предназначен для управления второй 10 - ((Т| + 1)-й 11 группами шинных формирователей, которые обеспечивают коммутацию выходHbix сигналов блоков 4 поразрядного сравнения на вход-выход 55 данных канала. Соответствующий выход дешифратора 7 возбуждается (формируется нулевой управляющий сигнал) при поступлении младших разрядов кода адреса на его информационные выходы и при наличии единичного сигнала Прием на прямом упраляющем входе и нулевого сигнала на инверсном управляющем входе. Шифратор 8 предназначен для формирования кода номера байта, в котором имеется несовпадение контрольной инт)ормации, записанной в регистре 3, к информации, поступающей от объекта контроля. Для этого на его входы подаются выходные сигналы элеме;нтов ИЛИ 12, каждый из которых формирует единичный сигнал на своем выходе, если имеется несовпадение хотя бы одного разряда информации в соответствующем ему байте. Одновременно выходные сигналы элементов Р1ЛИ 12 поступают на входы элемента который формирует единичньй при несовпадении разрядов хо в одном из tn байтов информ обрабатываемой каналом. Блок ран по схеме приоритетного ш ра, поэтому вьщаваемый им ко соответствует младшему номер в котором обнаружено несопад информации. Таблица соответствия прио го шифратора при m 4 имее Этой таблице соответствуе ма логических функций I. 1, Х,,(2 . где Х; - выход ( -го элемента ИЛИ 12,5S ц; - j -и впход шифратора 8. Таолица соответствия и логические функции, описьшающие работу шифратг ра 8 при Hi 7 4, могут быть получены аналогично. Группа шинных формирователей 9 предназначена для коммутации информации, поступающей на вход-выход 55 канала, при ее записи в один из регистров 3 контроля. Управление открытием группы шинных формирователей 9 осуществляется выходным сигналом элемента ИЛИ 15, который фиксирует возбуждение одного из выходов дешифратора 6,что соответствует режиму записи информации в одни из регистров 3 контроля. Открытие шинных формирователей данной группы, как и других шинных формирователей элементов устройства, осуществляется нулевым потенциалом. Группы шинных формирователей 10 и 11 предназначены для коммутации результатов сравнения байтов контрольной информации и информации, поступающей от объекта контроля, и передачи их на вход-выход 55 канала. Управление группами шинных элементов 10 и 11 осуществляет дешифратор 7. Логические элементы И-НЕ 13 и ИЛИ 14 предназначены для формирования сигнала ответа на выходе 58 канала, что означает поступление адреса данного канала, его правильную расшифровку и прием одного из сигналовприем или вьщача. Появление нулевого сигнала на выходе элемента И-НЕ 13 означает получение данньм каналом либо команды Прием, либо команды Выдача. Блок 17 синхронизации предназначен для формирования последовательности сдвинутых во времени синхроимпульсов на первом -м выходах, которые гфедназкачены для последовательного опроса элементов И 34, Временная диаграмма работы блока 17 синхронизации представлена на фиг. 5 (для частного случая т 8). Блок 17 синхронизации (фиг. 4) состоит из генератора импульсов, собранного на элементах И-НЕ 67-70, конденсаторе 75 и резисторе 77, регистра 65 сдвига и схемы управления, построенной на элементахНЕ 72-74, элементах И 66 и 71, а также резисторах 78-80; диоде 76 и конденсаторе 81. Генератор импульсов, собранный на элементах И-НЕ 67-70, представляет собой замкнутую автоколебательную цепь, которая формирует последовательность импульсов с частотой, определя емой параметрами конденсатора 75, резистора 77 и элементов И-НЕ 67-69. Элемент И-НЕ 70 выполняет функции вьгходного формирователя. Элемент И 7 предназначен для подключения выхода генератора импульсов к синхровходу регистра 65 сдвига при отсутствии запрещающего потенциала с выхода элемента ИЛИ 40. Схема управления, собранная на элементах 72-74, 76 и 78-81, обеспечивает формирование управляющего сиг нала на вход Vj регистра 65 с задерж кой по отношению к моменту подачи питающего напряжения, что исключает неправильное функционирование блока 17 синхронизации из-за Шереходных процессов, вызванных включанием пита ния. Элемент И 66 формирует единичный сигнал на входе V, регистра 65 сдвига, когда все его разряды находя ся в нулевом состоянии. Блок 17 синхронизации работает следующим образом. В исходном положе НИИ все разряды регистра-65 сдвига находятся в нулевом состоянии, на управляющих входах V 2. присутст вует единичный потенциал. При поступ лении на инверсный вход элемента И 71 разрешающего (нулевого) потенциала на С -вход регистра 65 начинают поступать импульсы. В первый разряд регистра 65 записывается единица, которая вьщается на его первом выходе. В результате на выход элемента И 66 появляется нулевой си нал, и при поступлении последующих синхроимпульсов происходит последовательный сдвиг единицы во второй, третий, fn й разряды регистра и за пись нуля в первый его разряд. При установке всех разрядов регистра 65 сдвига в исходное состояние на входе V 1 сформируется элементом И 66 единичный сигнал, и цикл работы пов торяется. Работа блока 17 синхронизации может быть остановлена в любо такте подачей единичного сигнала на его управляющий вход, т.е. инвер ный вход элемента И 71. Назначение и принцип действия наборного поля 18 задания адреса и схемы 20 сравнения аналогичны назна чению и принципу действия блока 2 и схемы 5 сравнения. Регистр 19 блокировки предназначен для исключения при необходимост приема контрольной информации по од.ному или нескольким kaHajiaM.B исходном состояник все разряды регистра 19 блокировки устанавливаются в единичное состояние. В результате все элементы И 34 открыты и информация от любого из каналов о несовпадении контрольной информации и информация от объекта контроля принимаются при опросе соответствующего элемента И 34 выходным импульсом блока 17 синхронизации. При необходимости запретить прием информации от i -го канала на входвыход 47 устройства подается код, содержащий О в i -м разряде, который через группы шинных формирователей 28 и 29 записывается в регистр 19 блокировки. Дешифратор 21 предназначен для управления переключением триггера 24 и управления группами шинных формирователей 28 и 29. Для формирования соответствующих управляющих сигналов на информационный вход дешифратора 21 подаются два младших разряда адреса, а на управляющий вход - единичный сигнал с выхода элемента И-НЕ 37. Коммутатор 22 предназначен для коммутации кода байта, в котором обнаружено несовпадение информации от любого из N каналов на входы группы шинных формирователей 26. Для этого коммутатор 22 содержит N групп элементов И 30-32, каждая из которых может быть открыта при поступлении соответствующего сигнала с выхода элемента И группы элементов И 34, объединение выходных сигналов групп эле ментов И 30-32 осуществляется с помощью группы элементов ИЛИ 33, каждьш из которых имеет N входов. Шифратор 23 формирует код номера канала, в котором обнаружено несовпадение информации. Для этого его входы подключены к выходам элементов И 34, а выходы соединены с входами группы шинных формирователей 27, через которые осуществляется передача кода номера канала на вход-выход 47 устройства контроля. Триггер 24 управляет прохождением сигнала Запрос на выход 49 устройства контроля. Рабочее состояние триггера 24 - единичное. Если необходимо временно запретить прохождение сигнала Запрос на выход 49 устройства, на информационный вход дешифратора 21 подается код, при котором возбуждается его выход 60, и триггер 24 устанавливается в нулевое состояние, пирая элемент И 35. При необходимос ти вернуть триггер 24 в рабочее (ед ничное) состояние на информационный вход дешифратора 21 подается код, при котором возбуждается выход 59 дешифратора. В результате на вход S-триггера 24 поступает сигнал, кот рый устанавливает его в единичное состояние, Элементы И-НЕ 36 и 37 предназначены для приема устройством сигналов Прием и Выдача соответсвенн если поступающий на вход 45 устройс ва контроля адрес совпадает с адресом, присвоенным устройству и храня щимся в блоке 2 задания адреса. В этом случае на выходе элемента НЕ 4 появляется единичный сигнал, который открывает элементы И-НЕ 36-37. Выходной сигнал элемента И-НЕ 36 через элемент ИЛИ 39 и элемент ИЛИ 4 поступает на выход 48 Ответ устро ства контроля, сигнализируя о том, что команда Прием устройством при нята. Одновременно выходной сигнал элемента И-НЕ 36 поступает на групп шинных формирователей 26 и 27, в ре зультате чего коды номера канала и номера байта, в котором обнаружено несовпадение информации, поступают на вход-выход 47 данных устройства контроля. Выход элемента И-НЕ 37 также подключен к входу элемента ИЛИ 39, благодаря чему на выход 4 устройства контроля поступает инфор мация о приеме сигнала Выдача. Од новременно выход элемента И-НЕ 37 подключен к управляющему входу дешифратора 21, разрешая нулевым сигналом прием сигналов, поступающих на его информационный вход, а через элемент НЕ 43 - к входу элемента И-НЕ 38, который управляет групп ми шинных формирователей 28 и 29. Одновибратор 44 с задержкой на входе управляет записью информации и регистр 19 контроля. Задержка на входе обеспечивает достижение установившихся значений сигналов на вхо дах регистра 19 блокировки, так как группы шинных формирователей 28 и 29 открываются тем же сигналом, кот рый поступает на вход одновибратора 44. Рассмотрим работу устройства контроля. В исходном состоянии регистры 3 контроля каждого из каналов 1 находятся в исходном (нулевом) состоянии, триггер 24 - в нулевом состоянии, а все разряды регистра 19 блокировки - в единичном состоянии. Многоканальное устройство контро,ля для управляющих вычислительных систем работает в следующих режимах: записи контрольной информации; контроля объекта; передачи информации о контролируемых параметрах. Рассмотрим работу устройства контроля в указанных режимах. Работа устройства начинается с режима записи контрольной информации в регистры 3 контроля каждого канала. В этом режиме процессор выставляет на адресный вход 45 уст1эойства контроля адрес J -го. канала, номер « -го регистра 3 контроля (который задается младшими разрядами адреса) и сигнал Вьщача. Одновременно на входвыход 47 данных устройства процессор выставляет контрольную информацию, которую необходимо записать в -и t V регистр 3 контроля.В J -м канале выставленный процессором адрес совпадает с собственным адресом канала, задаваемым блока 2, и на выходе txeмы 5 сравтгения j -го канала появляется нулевой сигнал. Этот сигнал поступает на инверсный управляющий вход дешифратора 6, на второй управляющий вход которого поступает сигнал Выдача, В результате появляется единичный сигнал на J -м выходе дешифратора 6, по которому открыта группа магистральных элементов 9 и контрольная информация записывается -и регистр 3 контроля. Одновременно с помощью элемента ИЛИ 14 и И-НЕ 13 сформируется сигнал- Ответ 5 свидетельсвующий о приеме контрольной информации 1 -м каналом, который поступает на выход 58 i -го канала и далее на выход 48 устройства контроля . Описанный цикл записи контрольной информации последовательно повторяется для всех регистров 3 контроля и всех каналов, участвующих в проверке объекта контроля. После этого устройство контроля переходит в режим контроля. 17. 11 Для перевода устройства контроля в режим контроля объекта процессор выставляет на вход 45 устройства адрес, совпадающий с адресом, заданным в блоке 18. Одновременно процессор выставляет сигнал Выдача, поступаю щий на вход элемента И-НЕ 37, и два младших разряда адреса, поступающие на I) -вход дешифратора 21, задают код, соответствующий появлению единицы на его выходе 59. Поступивший адрес сравнивается схемой 20 сравнения с адресом, задаваемым блоком 18. В результате их совпадения на выходе схемы 20 сравнения формируется нулевой потенциал, который открывает элемент И-НЕ 37, который своим выходом разрешает формирование единичного сигнала на выходе 59 дешифратора 21. Последний поступает на 5 вход триггера 24 и устанавливает его в единичное состояние. Выходной сигнал с выхода 25 триггера 24 открывает элемент И-НЕ 35. Далее при повторном обращения к устройству контроля процессор выставляет код младших адресных разрядов, при котором появляется единичный сигнал на выходе 61 дешифратора 21. Одновременно процессор на вход-выход 47 данных устройства выставляет код блокировки нулевые разряды которого соответствуют каналам, которые не участвуют в очередной задаче контроля. В резул тате поступления единичных сигналов на входы элемента И-НЕ 38 на выходе последнего появляется нулевой потенциал, который открывает группы шинны формирователей 28 и 29, и код блокировки каналов поступает на информа- .ционные рходы регистра 19 блокировки По сигналу с выхода элемента И-НЕ 38 одновибратор 44 с задержкой, превыша ющей время переходных процессов, фор мирует импульс на С-вход регистра 19 блокировки, по которому код блокиров ки записывается в регистр 19 блокировки. После этого устройство контро ля готово к контролю. В режиме контроля объекта осуществляется постоянный контроль совпадения контрольной информации, запи санный в регистрах 3 контроля, каждо го из каналов и реакций объекта конт роля, поступающих на вход 46 устройства контроля. При несовпадении конт рольной информации и сигнала от объе та контроля, поступаклцих на входы 9 -го канала, на соответствующем выходе блока 4 поразрядного .сравнения появляется едлничный сигнал, который через соответствующий элемент ИЛИ 12 и через элемент ИЛИ 16 поступает на выход 56 запроса i -го канала, сигнализируя о несовпадении реакции объекта контроля и контрольной информации. Одновременно сигнал с выхода элемента ИЛИ 12 поступает на соответствующий вход шифратора 8, который формирует код номера байта (регистра 3) информации,, в котором обнаружено несовпадение, и выдает его на группу выходов 57 i -го канала. Сигнал запроса с выхода 56 i -го канала поступает на вход i -го элемента И группы элементов И 34. Если в л -м разряде регистра 19 блокировки записана единица, т.е. i -и канал участвует в режиме контроля, на двух входах -го элемента И группы элементов И 34 присутствуют единичные сигналы и при появлении синхросигнала на -м выходе блока 17 синхронизации единичный сигнал появляется на выходе 1 -го элемента И группы элементов И 34. В результате этого появляется единичный сигнал на выходе элемента ИЛИ 40, который поступает на вход блока 17 синхронизации и вход элемента И 35. Блок 17 синхронизации прекращает генерирование синхросигналов и на его i -м выходе фиксируется постоянньш единичный сигнал. Одновременно с выхода элемента И 35 на выход 49 запроса устройства контроля поступает единичный сигнал, свидетельствующий о зафиксированном несовпадении реакции объекта контроля на одном из выходов и контрольной информации. Одновременно сигнал с выхода д -го элемента И группы элементов И 34 пос-. тупает на входы коммутатора 22 и шифратора 23. В результате этого коммутатор 22 осуществляет коммутацию кода номера байта с выхода 57 -го канала на входы группы магистральных элементов 26, Шифратор 23 по сигналу на его -м входе формирует на своих выходах код номера ; -го канала, который зафиксировал несовпадение реакции объекта контроля и контрольной информации. С выходов шифратора 23 этот код поступает на входы группы магистральных элементов 27. Сигнал запроса с выхода 49 устройства контроля воспринимается процессо ром, который в ответ на этот сигнал выставляет на вход 45 устройства контроля его адрес (совпадающий с записанными в блоке 18 задания адре са) и сигнал Прием. Обращение процессора расшифровывается схемой 20 сравнения, на выходе которой появля ется нулевой сигнал. Последний через элемент НЕ 42 открывает элемент ИНЕ 36 и на управляющие входы групп шинных формирователей 26 и 27 посту пает нулевой сигнал и открываетих. В этот момент на входах группы шин ных формирователей. 26 присутствует код номера байта (регистр 3), в котором обнаружено несовпадение реакции объекта контроля и контрольной информации, а на входах группы . магистральных элементов 27 - код номера канала. В результате код номера байта и код номера .канала передаются на вход-выход 47 данных устройст ва контроля и воспринимаются процессором . После этого устройство контроля переходит в режим передачи информации о контролируемых параметрах о Рас смотрим работу устройства в этом режиме. Получив точный адрес блока 4 поразрядного сравнения, которьй зафикисровал несовпадение реакции объе та контроля и контрольной информации процессор выставляет на вход 45 адреса устройства контроля сообщенный ему адрес канала (старшие разряды адреса) и номер байта (блок 4 поразрядного сравнения), в котором обнаружено несовпадение информации, а также сигнал Прием. Выставленный процессором адрес 1-го канала -расшифровьшается схемой сравнения i -го канала, с выхода которой нулевой потенциал поступает на инверсный 1 управляющий вход дещифратора 7, на управляющий вход 2 которого поступает сигнал Прием. В результате возбуждается j -и выход дешифратора 7, который открывает группу магистральных элементов, подключенную к выходу J -го блока 4 поразрядного сравнения; Вследствие этого информация о несовпадении реакции объекта контроля и контрольной информации передается на вход-выход 47 данных устройства контроля и воспринимается процессором. Получив требуемую информацию, процессор снимает сигнал Прием и выставляет сигнал Выдача на адресном входе 45 устройства контроля. Одновременно на вход-выход 47 данных устройства контроля он выставляет контрольную информацию, которая приведена в соответствие с пол ченной в предыдущем цикле информацией о реакциях обьекта контроля. По сигналу Вьщача, пocтyпишe fy на управляющий вход 2 дешифратора 6, возб ткдается его J -и выход. Н-а выходе элемента ИЛЙ-НЕ 15 появлется нулевой сигнал, который открывает группу шинных формирователей 9. В результате выставленная процессором информация поступает на информационные входы всех регистров 3 контроля 1-го канала, однако запишется только в j -i; регистр 3 контроля на синхровход которого поступает единичньш сигнал с ( -го выхода дешифратора 6. Вследствие этого на всех выходах -го блока 4 поразрядного сравнения -го канала появляются нулевые сигналы и с выхода 56 i -го канала снимают сигнал Запрос, В связи с этим исчезает единичный сигнал на выходе элемента ИЛИ 40 и элемента И 35, а блок 17 синхронизации переходит в режим генерации синхроимпульсов. Таким образом, заканчивается режим передачи информации и контролируемых параметрах и устройство контроля снова переходит в режим контроля. Применение предлагаемого изобретения позволит строить быстродействующие и экономичные средства сбора и обработки контрольной информации для систем, управляюш х сложными многоканальными объектами.

с

ЕЗЕЛ 3

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1129599A1 |

| Устройство для контроля управляющих сигналов микропроцессора | 1989 |

|

SU1656536A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для обслуживания сообщений | 1986 |

|

SU1341638A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

МНОГОКАНАЛЬНОЕ УСТРОЙСТВО КОНТРОЛЯ ДЛЯ УПРАВЛЯЮЩИХ ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ, содержащее блок синхронизации, схему сравнения, регистр блокировки, триггер, элемент И, первый элемент НЕ и коммутатор, причем единичный выход триггера соединен с первым входом элемента ,i, о т л ичающееся тем, что, с целью повышения быстродействия, в устройство введены наборное поле задания адреса устройства, дешифратор, шифратор, группа элементов И, четыре группы шинных формирователей, первый, второй и третий элементы И-НЕ, первый, второй и третий элементы ИЛИ, формирователь импульсов, второй элемент НЕ, И каналов приема и анализа контрольной информации, каждый из которых содержит гп регистров контроля, наборное поле задания адреса канала, m блоков поразрядногосравнения, схему сравнения, первый и второй дешифраторы, шифратор, группу элементов ИЛИ, (гц+1) группу шинных формирователей, первый, второй и третий элементы ИЛИ и элемент И-НЕ, . причем входы старших разрядов адреса группы адресных входов устройства соединены соответственно с первой и второй группами входов сравнения, выход которой соединен с входом первого элемента НЕ, выход первого элемента ИЛИ 1 -го канала приема и анализа контрольной информации (где1 1,N ) соединен с гкрвым входом i -го элемента И группы, выходы элемента И-НЕ -то канала примера и анализа контрольной информации соединен с i -м входом первого элемента ИЛИ, (Л группа выходов шифратора i -го канала приема и анализа контрольной С информации соединена с i -и группой информационных входов коммутатора, входы старших разрядов группы адресных входов устройства и выходы наборного поля задания адреса канала соединены соответственно с первым и вторым входами схемы сравнения соответствующего канала приема и анализа контрольной информации, выход которой соединен с инверсными управляюш ми входами первого и второго дешифраторов и инверсным входом элемента- И-НЕ, входы младших разрядов адреса группы адресных входов устройства соединены с информационными входами первого и второго дешифраторов каждого канала приема и анализа контрольной информации, вход приема группы адресных входов устройства соединен с прямым управляющим входом второго дешифратора и первым входом второго элемента ИЛИ, выход которого

Фиг.З

Выходов выход 7f

Фиг. it

I м I I I I I I I I I I м

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальное устройство для тестового контроля | 1974 |

|

SU516039A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ автоматического контроля микропрограммного автомата | |||

| Сб | |||

| связи и дискретные устройства управления | |||

| М., Наука, 1976, с | |||

| Ударно-вращательная врубовая машина | 1922 |

|

SU126A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-07—Публикация

1983-04-07—Подача