СО N9

li

Изобрете1ше относится к вычислительной технике, предназначено для генерации кодов цифровых значений периодической функции в дискретные рав- ноотстоядие моменты времени, может быть использовано для снятия амплитудно-частотной характеристики (АЧХ) и прове15ки работы цифровых фильтров с двумя квадратурными каналами.

Цель изобретения ,расширение класса решаемых задач генератора за счет формирования периодической последовательности по двум каналам,

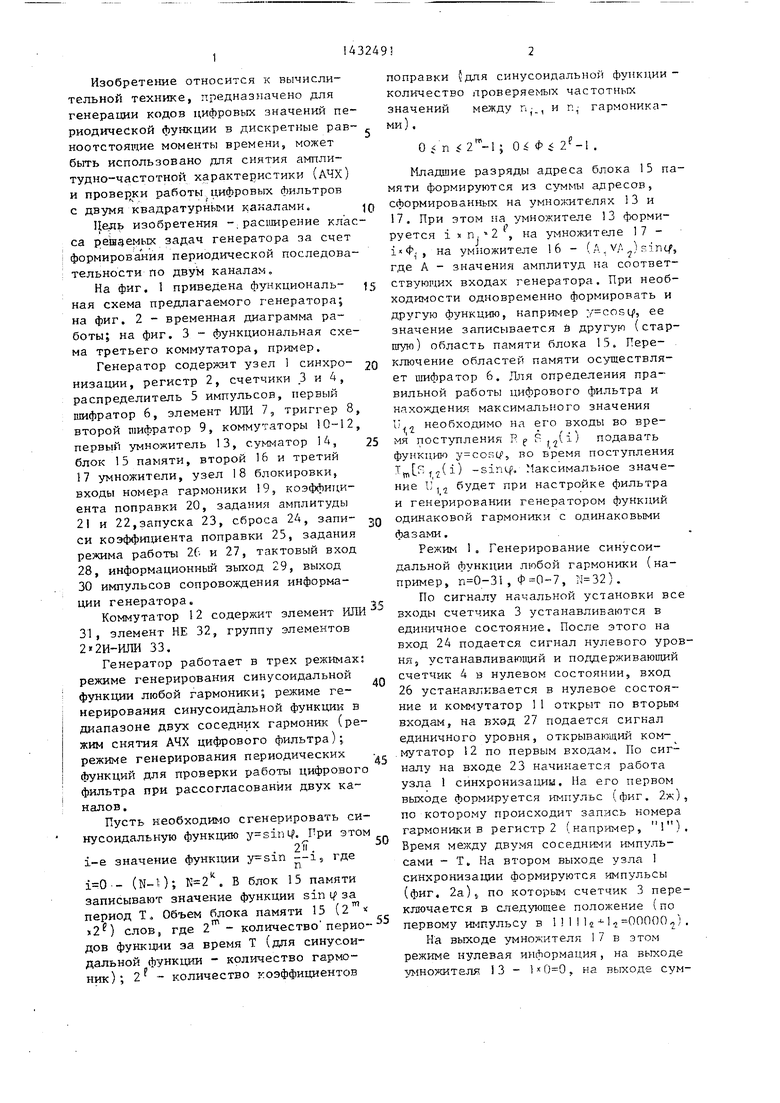

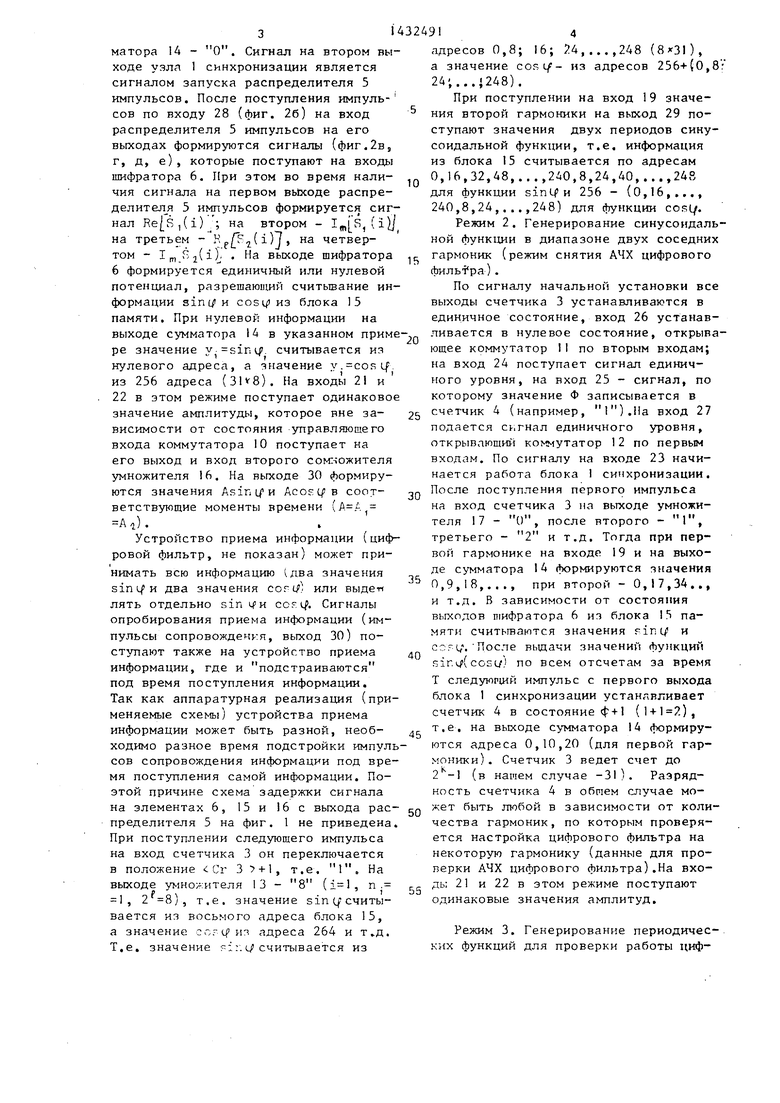

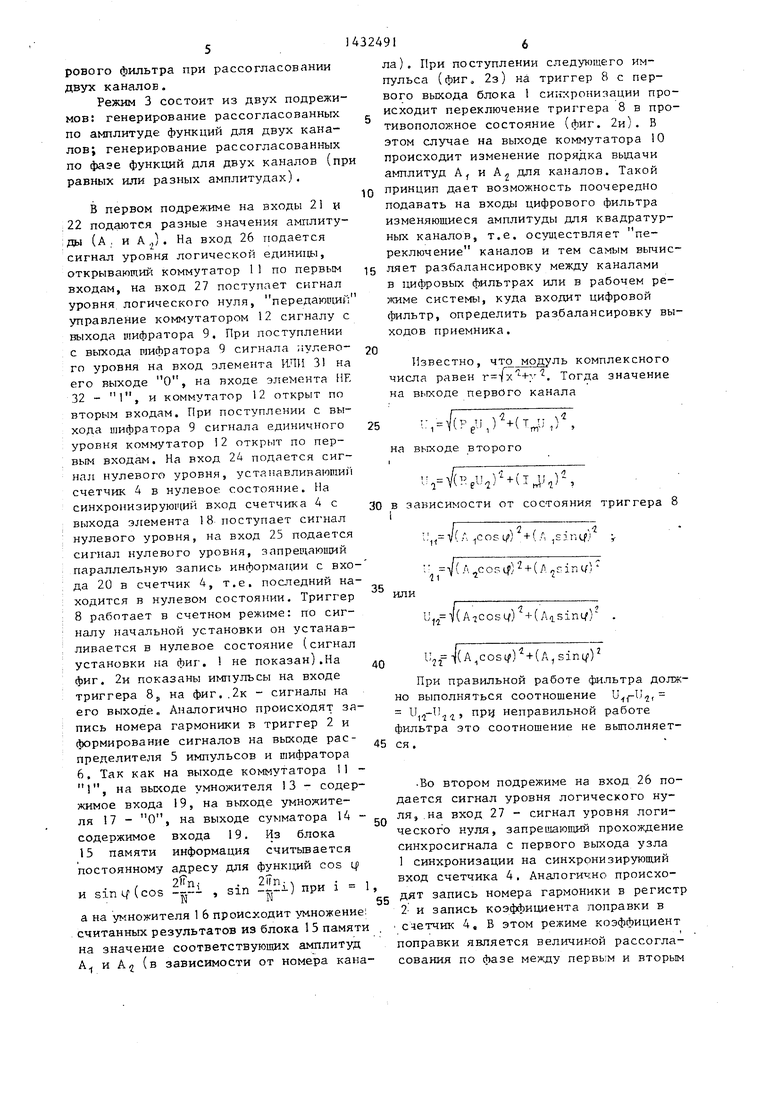

На фиг, 1 приведена функциональ- ная схема предлагаемого генератора; на фиг. 2 - временная диаграмма работы; на фиг. 3 - функциональная схема третьего коммутатора, пример.

Генератор содержит узел 1 синхро- низации, регистр 2, счетчики .3 и 4, распределитель 5 импульсов, первый шифратор 6, элемент ИЛИ 7, триггер 8, второй шифратор 9, коммутаторы 10-12, первый умножитель 13, сумматор 14, блок 15 памяти, второй 15 и третий 17 умножители, узел 18 блокировки, входы номера гармоники 9, коэффициента поправки 20, задания амплитуды 21 и 22,запуска 23, сброса 24, запи- си коэффициента поправки 25, задания режима работы 26 и 27, тактовый вход 28, информационньй выход 29, выход 30 импульсов сопровождения информации генератора.

Коммутатор 12 содержит элемент ИЛИ 31, элемент НЕ 32, группу элементов 2 2И-ИЛИ 33.

Генератор работает в трех режимах: режиме генерирования синусоидальной функции любой гармоники; режиме генерирования синусоидальной функции в диапазоне двух соседних гармоник (режим снятия АЧХ цифрового фильтра);, режиме генерирования периодических функций для проверки работы цифрового фильтра при рассогласовании двух каналов .

Пусть необходимо сгенерировать синусоидальную функцию y sinM . При этом

. 2п. i-e значение функции -i, где

(N- i); . В блок 15 памяти записывают значение функции sin if за период Т,, Объем блока памяти 15 (2 2П слов, где количество периодоз функисии за время Т (для синусоидальной функции - количество гармоник); 2 - количество коэффициентов

поправки дпя синусоидальной функции - количество проверяемых частотньгк

Q

и r.j гармоника5

0

5

0

значений между г ми).

О п : ; 0 Ф .

Младшие разряды адреса блока 15 памяти формируются из суммы ад:ресов, сформированных на умногкителях 13 и 17. При этом на умножителе 13 формируется i X п- 2 , на умножит€ше 17 - 1«Ф|, на умножителе 16 - (, si nif где А - значения амплитуд на соответствующих входах генератора. При необходимости одновременно формировать и другую функцию, например y-costf, ее значение записывается и другую (старшую) область памяти блока 15. Пере- , ключение областей памяти осуществляет шифратор 6. Япя определения правильной работы цифрового фильтра и нахождения максимального значения необходимо на его входы, во время поступления Rf (,(1) подавать функцию ,(f, во в ремя поступления ) -sinef. Максимальное значение L , будет при настройке фильтра и генерировании генератором функций одинаковой гармоники с одинаковыми фа 3 ами.

Режим 1. Генерирование синусоидальной функции любой гармоники (например, , , ).

По сигналу начальной установки все входы счетчика 3 устанавливаются в единичное состояние. После этого на вход 24 подается сигнал нулевого уровня, устанавливаюпщй и поддерживаюишй счетчик 4 в нулевом состоянии, вход 26 устанавливается в нулевое состояние и коммутатор 11 открыт по вторым входам, на вхэд 27 подается сигнал единичного уровня, открывающий ком- .мутатор 12 по первым входам. По сигналу на входе 23 начинается работа узла 1 синхронизации. На его первом выходе формируется импульс (фиг. 2ж), по которому происходит запись номера гармоники в регистр 2 (напр:имер, ). Время между двумя соседними импульсами - Т, На втором узла 1 синхронизации формируются импульсы (фиг, 2а)., по которым счетчик 3 переключается в следующее положение (по первому Н -1пульсу в П 1 I .2 00000) .

На выходе умножителя 17 в этом режиме нулевая информация, на выходе у шо чителя 1 3 - ,, на выходе сум314324914

матора 14 - О. Сигнал на втором вы- адресов 0,8; 16; 24,...,248 (8x31), ходе узла I синхронизации является сигналом запуска распределителя 5 импульсов. После поступления импуль- сов по входу 28 (фиг. 26) на вход распределителя 5 импульсов на его выходах формируются сигналы (фиг.2в5 г, д, е), которые поступают на входы шифратора 6. При этом во время наличия сигнала на первом выходе распре- делител 5 импульсов формируется сигнал ,(i) ; на втором - , (i) на третьем - К „,,(1)7, на четвертом - I m (i}. , На выходе шифратора гармоник (режим снятия АЧХ цифрового 6 формируется единичный или нулевой фильтра). потенциал, разрешающий считывание информации sint/H cos 1 из блока 15

10

а значение cosi/- из адресов (0, 24;...-248).

При поступлении на вход 19 значения второй гармоники на выход 29 поступают значения двух периодов сину соидальной функции, т.е. информация из блока 15 считывается по адресам

0,16,32,48240,8,24,40,...,248

для функции sinM H 256 - (0,16,..., 240,8,24,... ,248) для функции CORL/.

Режим 2. Генерирование синусоидал ной функ1щи в диапазоне двух соседних

По сигналу начальной установки вс выходы счетчика 3 устанавливаются в единичное состояние, вход 26 устанав ливается в нулевое состояние, открыв ющее коммутатор 11 по вторым входам; на вход 24 поступает сигнал единичного уровня, на вход 25 - сигнал, по которому значение Ф записывается в счетчик 4 (например, 1).На вход 27 подается ct.rHan единичного уровня, открывающий коммутатор 12 по первым входам. По сигналу на входе 23 начинается работа блока 1 синхронизации. После поступления первого импульса на вход счетчика 3 на выходе умножителя 17 - О, после второго - 1, третьего - 2 и т.д. Тогда при первой гармонике на входе 19 и на выходе сумматора 14 формируются значения

памяти. При нулевой информации на выходе сумматора 14 в указанном примере значение . считывается из нулевого адреса, а значение y.cos(. из 256 адреса (ЗиЗ). На входы 21 и 22 в этом режиме поступает одинаковое значение амплитуды, которое вне зависимости от состояния управляющего входа коммутатора 10 поступает на его выход и вход второго сом:тожителя умножителя 16. На выходе 30 формируются значения AsinL/ и АСОЕС/В соответствующие моменты времени (. А -i) .

Устройство приема информации (цифровой фильтр, не показан) может принимать всю информацию (.два значения sin ц и два значения или выдеп лять отдельно sin COF. ij. Сигналы опробирования приема информации (импульсы сопровождения, выход 30) поступают также на устройство приема информации, где и подстраиваются под время поступления информации. Так как аппаратурная реализация (при- меняеьяые схемы) устройства приема информации может быть разной, необходимо разное время подстройки импульсов сопровождения информации под время поступления самой информации. По- этой причине схема задержки сигнала

адресов 0,8; 16; 24,...,248 (8x31), гармоник (режим снятия АЧХ цифрового фильтра).

0

а значение cosi/- из адресов (0,8: 24;...-248).

При поступлении на вход 19 значения второй гармоники на выход 29 поступают значения двух периодов синусоидальной функции, т.е. информация из блока 15 считывается по адресам

0,16,32,48240,8,24,40,...,248

для функции sinM H 256 - (0,16,..., 240,8,24,... ,248) для функции CORL/.

Режим 2. Генерирование синусоидальной функ1щи в диапазоне двух соседних

адресов 0,8; 16; 24,...,248 (8x31), гармоник (режим снятия АЧХ цифрового фильтра).

По сигналу начальной установки все выходы счетчика 3 устанавливаются в единичное состояние, вход 26 устанавливается в нулевое состояние, открывающее коммутатор 11 по вторым входам; на вход 24 поступает сигнал единичного уровня, на вход 25 - сигнал, по которому значение Ф записывается в счетчик 4 (например, 1).На вход 27 подается ct.rHan единичного уровня, открывающий коммутатор 12 по первым входам. По сигналу на входе 23 начинается работа блока 1 синхронизации. После поступления первого импульса на вход счетчика 3 на выходе умножителя 17 - О, после второго - 1, третьего - 2 и т.д. Тогда при первой гармонике на входе 19 и на выходе сумматора 14 формируются значения

П,9,18 при второй - 0,17,34..,

и т.д. в зависимости от состояния выходов шифратора 6 из блока 15 памяти считываются значения rint/ и ссг1г осле выдачи значений функций sir. 1( cost/) по всем отсчетам за время Т следуюп1ий импульс с первого выхода блока 1 синхронизации устанг1нливает счетчик 4 в состояние ф + 1 (1 + 1.), т.е. на выходе сумматора 14 формируются адреса 0,10,20 (для первой гармоники). Счетчик 3 ведет С чет до 2 -1 (в нашем случае -31). Разрядность счетчика 4 в обр1ем случае мо

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор периодической функции | 1985 |

|

SU1275412A1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| Устройство для цифровой обработки сигналов | 1988 |

|

SU1575203A1 |

| Анализатор гармоник | 1988 |

|

SU1663571A1 |

| Аналого-цифровой анализатор сигналов | 2024 |

|

RU2826857C1 |

| УНИВЕРСАЛЬНЫЙ ГЕНЕРАТОР СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 1994 |

|

RU2060536C1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Цифровой фильтр | 1988 |

|

SU1566469A1 |

| Устройство для вычисления спектра сигналов | 1990 |

|

SU1803920A1 |

Изобретение относится к вычислительной технике и предназначено для генерации кодов цифровых значений периодической функции в дискретные равноотстоящие моменты времени, может быть использовано, для снятия амплитудно-частотной характеристики (АЧХ) и проверки работы цифровых фильтров с двумя квадратурными каналами. Цель изобретения - расширение класса решаемых задач за счет формирования периодической последовательности по двум каналам. Генератор содержит узел 1 синхронизации, регистр 2, счетчики 3 и 4, распределитель 5 импульсов, первый шифратор 6, элемент ИЛИ 7, триггер 8, второй шифратор 9, коммутаторы 10-12, первый умножитель 13, сумматор 14, блок 15 памяти, второй 16, третий.17 умножители, узел 18 блокировки, вход 19 номера гармоники, вход 20 коэффициента поправки, входы 21 и 22 задания амплитуды, вход 23 запуска, вход 24 сброса, вход 25 записи коэффициента поправки, входы 26 и 27 задания режима работы, такто-G вьй вход 28 информационный выход 29, выход 30 импульсов сопровождения ин- /Л формации генератора. Коммутатор 12 содержит элемент ИЛИ 31, элемент НЕ 32, группу элементов 2И-ИЛИ 33 с соответствующими связями. 3 ил.

на злементах 6, 15 и 16 с выхода рас- ел т быть любой в зависимости от колипределителя 5 на фиг. 1 не приведена. При поступлении следующего импульса на вход счетчика 3 он переключается в положение iСг 3 +1, т.е. 1. На выходе умно :ителя 13 - 8 (, п . 1, 2 8), т.е. значение sin с считывается из восьмого адреса блока 15, а значение согс из адреса 264 и т..д. Т.е. значение я1:. L/ считывается из

55

чества гармоник, по которым проверяется настройка цифрового фильтра на некоторую гармонику (данные для проверки АЧХ цифрового фильтра).На входы 21 и 22 в этом режиме поступают одинаковые значения амплитуд.

Режим 3. Генерирование периодических функций для проверки работы циф

чества гармоник, по которым проверяется настройка цифрового фильтра на некоторую гармонику (данные для проверки АЧХ цифрового фильтра).На входы 21 и 22 в этом режиме поступают одинаковые значения амплитуд.

Режим 3. Генерирование периодических функций для проверки работы цифрового фильтра при рассогласовании двух каналов.

Режим 3 состоит из двух подрежимов: генерирование рассогласованных по амплитуде функций для двух каналов; генерирование рассогласованных по фазе функций для двух каналов (при равных или разных амплитудах).

В первом подрежиме на входы 21 и 22 подаются разные значения амплиту- :ды (А; и А ,} . На вход 26 подается сигнал уровня логической единипя,

ла). При поступлении следующего импульса (фиг, 2з) на триггер 8 с первого выхода блока 1 син: ронизации происходит переключение триггера 8 в противоположное состояние (фиг. 2и). В этом случае на выходе коммутатора 10 происходит изменение порядка выдачи амплитуд А и А для каналов. Такой -|Q принцип дает возможность поочередно подавать на входы цифрового фильтра изменяющиеся амплитуды для квадратурных каналов, т.е. осуществляет переключение каналов и тем самым вычисв цифровых фильтрах или в рабочем режиме системы, куда входит цифровой фильтр, определить разбалансировку выходов приемника.

Известно, что модуль комплексного числа равен г т|х -+у . Тогда значение на выходе первого канала

; «f Р и - 1 U- е-|, I

(т)

открывающий коммутатор 11 по первым 15 ляет разбалансировку между каналами входам, на вход 27 поступает сигнал уровня, логического нуля, передающий управление коммутатором 12 сигналу с выхода щифратора 9. При поступлении с выхода шифратора 9 сигнала г.упево- 20 го уровня на вход элемента ЯПИ 31 на его выходе О, на входе элемента НЕ 32 - 1, и коммутатор 12 открыт по вторым входам. При поступлении с выхода шифратора 9 сигнала единичного 25 уровня коммутатор 2 открыт по первым входам. На вход 24 подается сигнал нулевого уровня, устаиавливаюпшй счетчик 4 в нулевое состояние. На синхронизирующий вход счетчика 4 с выхода элемента 18 поступает сигнал нулевого уровня, на вход 25 подается сигнал нулевого уровня, запрещаюишй параллельную запись информации с входа 20 в счетчик 4, т.е. последний находится в нулевом состоянии. Триггер В работает в счетном режиме: по сигналу начальной установки он устанавливается в нулевое состояние (сигнал установки на фиг, не показан).На Q фиг. 2и показаны импульсы на входе триггера 8, на фиг..2к - сигналы на его выходе,, Аналогично происходят запись номера гармоники в триггер 2 и

на выходе второго

1 ; -.Н 15 т I J. | т п l U - VV - - гЛ- 1

30 в зависимости от состояния триггера 8

1

1:,т/(Л cosg) +(Д ,Einqi) ;.

35

или

I /, f V ,cos q) 2 + (А , in v)

U,i(A7Cos4) + (/4sini/) () + (А,з1п1)

При правильной работе фильтра должно выполняться соотношение , прц неправильной работе фильтра это соотношение не выполняет- формирование сигналов на выходе рас. - -45 ся.

пределителя 5 импульсов и шифратора

211 П( . 211П;

-Во втором подрежиме на вход 26 подается сигнал уровня логического нуля, .на вход 27 - сигнал уровня логического нуля, запрещающий прохождение синхросигнала с первого выхода узла 1 синхронизации на синхронизирующий вход счетчика 4, Аналогично происхои sin Ч (cos , sin запись номера гармоники в регистр

а на -умножителя 1 6 происходит умножение:2- и запись коэффициента поправки в

. считанных результатов из блока 15 памяти , сметчик 4. В этом режиме коэффициент

на значение соответствующих амплитудпоправки является величиной рассоглаА и Ал (в зависимости от номера кана-сования по фазе между первым и вторым

ла). При поступлении следующего импульса (фиг, 2з) на триггер 8 с первого выхода блока 1 син: ронизации происходит переключение триггера 8 в противоположное состояние (фиг. 2и). В этом случае на выходе коммутатора 10 происходит изменение порядка выдачи амплитуд А и А для каналов. Такой принцип дает возможность поочередно подавать на входы цифрового фильтра изменяющиеся амплитуды для квадратурных каналов, т.е. осуществляет переключение каналов и тем самым вычисв цифровых фильтрах или в рабочем режиме системы, куда входит цифровой фильтр, определить разбалансировку выходов приемника.

Известно, что модуль комплексного числа равен г т|х -+у . Тогда значение на выходе первого канала

ляет разбалансировку между каналами

; «f Р и - 1 U- е-|, I

(т)

разбалансировку ме

5 ляет разбалансировку между каналами 20 25 Q

на выходе второго

1 ; -.Н 15 т I J. | т п l U - VV - - гЛ- 1

30 в зависимости от состояния триггера

1

1:,т/(Л cosg) +(Д ,Einqi) ;.

5 ляет разбалансировку между к 0 25 Q

35

или

I /, f V ,cos q) 2 + (А , in v)

U,i(A7Cos4) + (/4sini/) () + (А,з1п1)

-Во втором подрежиме на вход 26 подается сигнал уровня логического нуля, .на вход 27 - сигнал уровня логического нуля, запрещающий прохождение синхросигнала с первого выхода узла 1 синхронизации на синхронизирующий вход счетчика 4, Аналогично происходд запись номера гармоники в регистр

каналами. Амплитуда на входах .2 и 22 может быть равной или разной (для проверки фильтра только на реакцию при рассогласовании фаз между канала- с ми ). Аналогично происходит формирование сигналов, показанных на фиг. 2а, б, в , г, д, е, ж, з, и, к, на выходе умножителя 13 происходит умножение номера гармоники на номер 10 отсчета. Шифратор 9, управляя работой коммутатора 12, поочередно вьщает на его выход содержимое первого или второго (он подсоединен к уровню логического нуля) входа, т.е. на выходе 15 множителя 17 поочередно формируются значения j «i и . Эти значения оступают на входы суммирования суматора 14 и с блоков памяти считыватся поочередно значения cosd/ ,+0), 20 sin(t;.+0) для первого канала H COS(C/ + ), sin( 1/,.) для второго канала, оторые умножаются на значение амлитуды на умножителе 16 (t/ rixi, г 1)о 25

При переключении триггера 8 в противоположное состояние меняется фаза первого и второго каналов. Такая частотная последовательность дает воз- 30 можность проверить реакцию квадратурных каналов цифрового фильтра или по результатам проверки цифрового фильтра определить расстройку фаз каналов приемника.25

Формула изобретения

Цифровой генератор периодической функции, содержащий два счетчика, три 40 умножителя, сумматор, узел синхронизации, регистр, блок памяти, причем вход номера гармоники генератора подключен к информа11 1онному входу регистра, выход которого подключен к пер- 45 вому входу первого умножителя, вход синхронизации регистра подключен к первому выходу узла синхронизации, второй выход которого подключен к счетному входу первого счетчика, ин- gg формационный выход генератора подключен к выходу второго умножителя, первый вход которого подключен к выходу блока памяти, младшие (п-1) разряды адресного входа которого подключены gg к выходу сумматора, первый вход кото рого подключен к выходу первого умножителя, второй вход сумматора подключен к выходу третьего умножителя,

первьй вход которого подключен к выходу первого счетчика, входы коэффициента поправки, сброса и записи генератора подключены соответственно к информационному входу сброса и входу записи коэффициента поправки второго счетчика, вход запуска генератора подключен к входу пуска узла синхронизации, отличающийся тем, что, с целью расширения класса решаемых задач генератора за счет формирования периодической последовательности по двум каналам, в него ввдены .распределитель импульсов, два шифратора, три коммутатора, элемент ИЛИ, узел блокировки и триггер, причем первьп выход узла синхронизации подключен к первому входу узла блокировки и входу триггера, тактовый вход генератора подключен к тактовому входу распределителя импульсов, управляюищй вход которого подключен к второму выходу узла синхронизации, выходы распределителя импульсов подключены к выходу импульсов сопровождения генератора и входу первого шифратора, выход которого подключен к входу старшего разряда адресного входа блока памяти, первый вход задания режима генератора подключен к управляющему входу первого коммутатора, первый информационньи вход которого подключен к выходу первого счетчика, младшие разряды второго информационного входа первого коммутатора подключены к входу логической единицы генератора, а старшие разряды - к входу логического нуля генератора, выход первого коммутатора подключен к второму входу первого умножителя, второй вход задания режима генератора под- ключен к первому управляющему входу второго коммутатора и второму входу узла блокировки, выход которого подключен к входу синхронизации второго счетчика, выход которого подключен к первому информационному входу второго коммутатора, второй информационный вход которого подключен к входу логического нуля, выход триггера подключен к первому входу второго шифратора, второй вход которого подключен к выходу элемента ИШ1, первьп и второй входы которого подключены к первому и второму выходам узла распределения импульсов, выход второго коммутатора подключен к второму входу третьего умно ителя, второй вход второго умножителя подключен к выходу третьего коммутатора, первый и второй информационные входы которого подключены к первому и второму входам задания амплитуды генератора, выход второго шифратора подключен к управляющему входу третьего коммутатора и второму управ- . ляющему входу второго коммутатора.

9 27

51

.

d3i

Lp

52

ri

55(М

(i-t-)p

(Pue.5

| Цифровой генератор синусоидальной функции | 1982 |

|

SU1043615A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой генератор периодической функции | 1985 |

|

SU1275412A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| (прототип). | |||

Авторы

Даты

1988-10-23—Публикация

1987-03-25—Подача