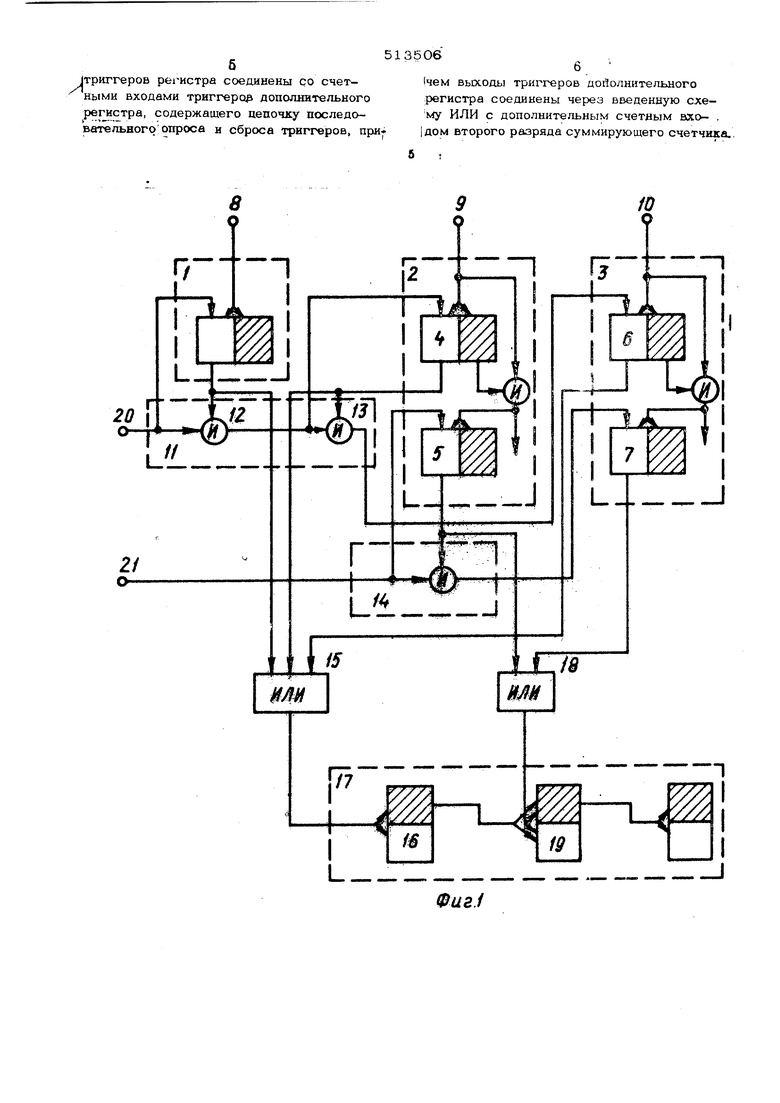

(54) МНОГОВХОДОВЫЙ СЧЕТЧИК ИМПУЛЬСОВ

3

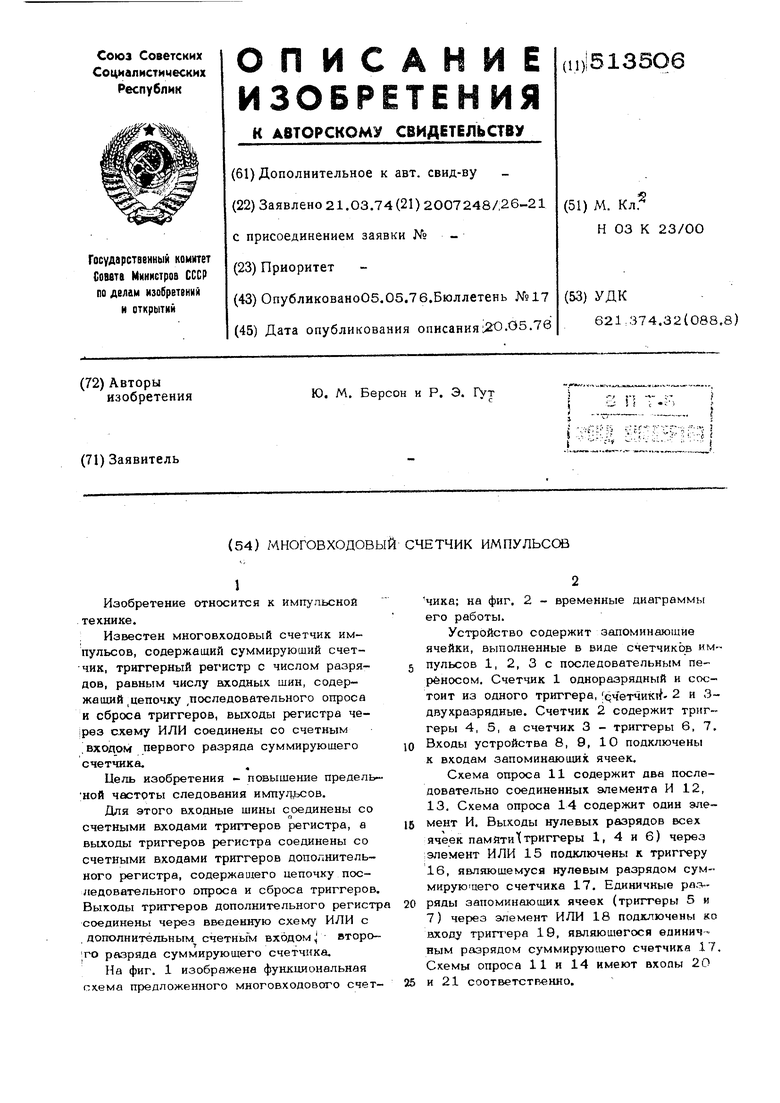

.Чноговходовый счетчих работает следу ШИЛ4 оораэом.

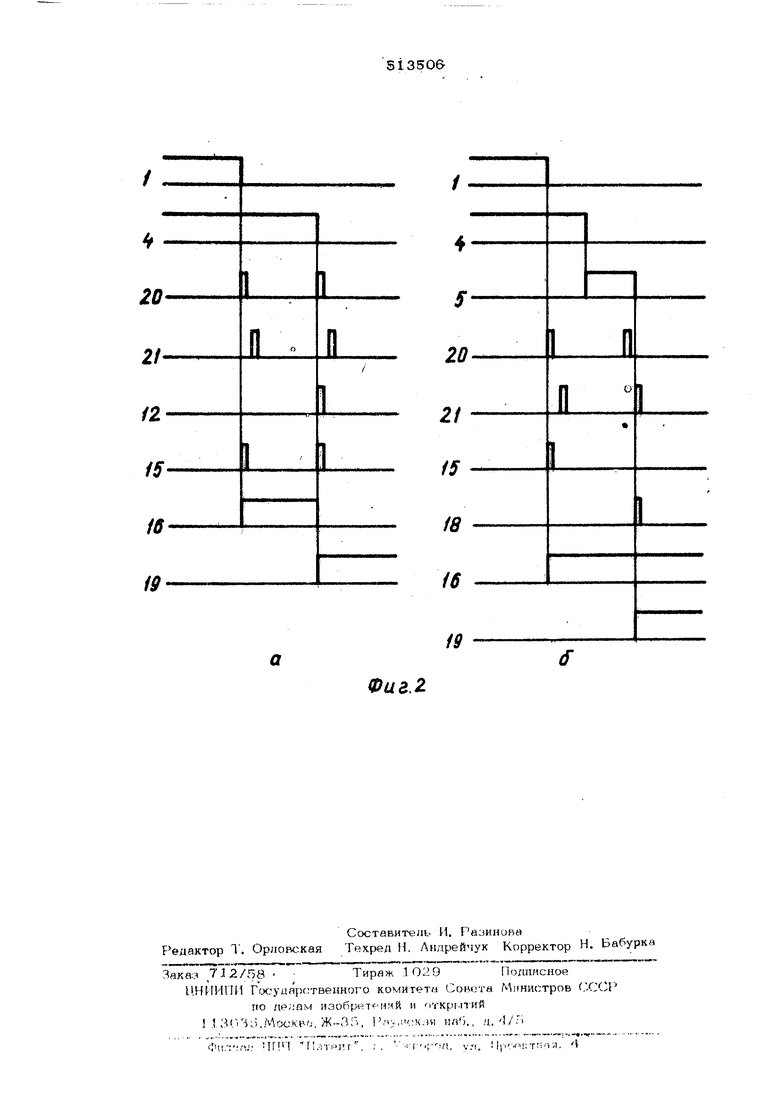

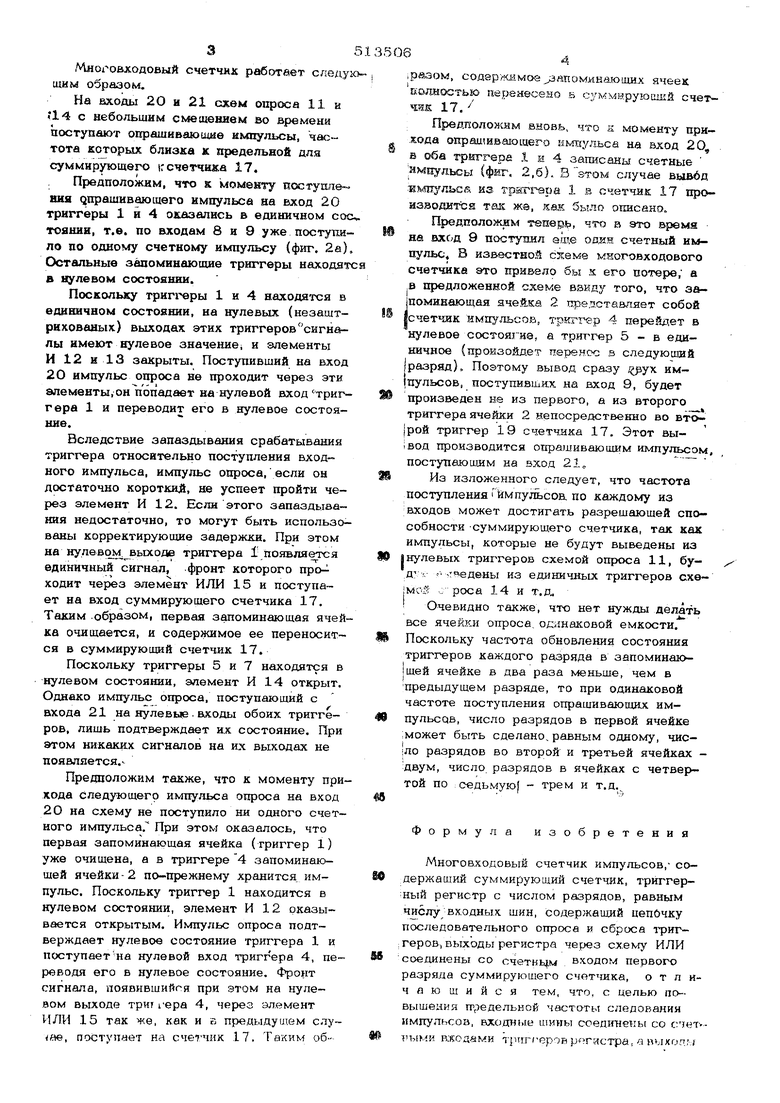

На входы 20 и 21 схем опроса 11 и 14 с небольшим смещением во времени поступают опрашивающие импульсы, частота которых близка к предельной для суммирующего гсчетчика 17. . Предположим, что к моменту поступления упрашивающего импульса на вход 20 триггеры 1 и 4 оказались в единичном сос тоании, т.е. по входам 8 и 9 уже поступило по одному счетному импульсу (фиг. 2а) Остальные запоминающие триггеры находят в нулевом состоянии.

Поскольку трип- ры 1 и 4 находятся в единичном состоянии, на нулевых (незаштрихованых) выходах этих триггеров сигналы имеют нулевое значение; и элементы И 12 и 13 закрыты. Поступивший на вход 20 импульс опроса не проходит через эти элементы,он попадает на нулевой входтриггера 1 и переводит его в нулевое состояние.

Вследствие запаздывания срабатывания триггера относительно поступления вход ного импульса, импульс опроса, если он достаточно короткий, не успеет пройти через элемент И 12. Если этого запаздывания недостаточно, то могут быть использованы корректирующие задержки. При этом на нулевом, вьиоде триггера i появляется единичный сигнал, фронт которого проходит через элемент ИЛИ 15 и поступает на вход суммирующего счетчика 17, Таким -образом, первая запоминающая ячейка очищается, и содержимое ее переносится в суммирующий счетчик 17.

Поскольку триггеры 5 и 7 находятся в нулевом состоянии, элемент И 14 открыт. Однако импульс опроса, поступающий с входа 21 на нулевые . входы обоих триггеров, лишь подтверждает их состояние. При этом никаких сигналов на их выходах не появляется.

Предположим также, что к моменту прихода следующего импульса опроса на вход 20 на схему не поступило ни одного счетного импульса, При этом оказалось, что первая запоминающая ячейка (триггер 1) уже очищена, а в триггере 4 запоминающей ячейки - 2 по-прежнему хранится импульс. Поскольку триггер 1 находится в нулевом состоянии, элемент И 12 оказывается открытым. Импульс опроса подтверждает нулевое состояние триггера 1 и поступает на нулевой вход триггера 4, переводя его в нулевое состояние. Фронт сигнала, появившийся при этом на нулевом выходе триггера 4, черюз элемент ИЛИ 15 так же, как и Б предыдущем , поступает на счетчик 17, Таким обл

ipaaoM, содерж15.мо а йпоминающих ячеек солнсетью пер8не ;ено ь сум « ируюшдй счетчнк 17.

Предполоншм вновь, что к моменту прихода опраишвающего импульса на вход 20 в оба триггере 1 и 4 затесаны счетные импульсы (фиг, 2,6). В этом случае вывбд кш15льса из третч ра 1 в счетчик 17 проиаводитсй таи же, жаж было окисано.

Предположим теперь, что в это время на вход 9 поступил еще оалн счетный импульс, В известной многовходового счетчика это привело бы к его потере; а в предложенной схеме ввиду того, что за- 1поминающая ячейка 2 представляет собой |счетчик ймяульсой, триггеф 4 перейдет в нулевое состоягиа, а триггчэр 5 - в единичное (произойдет перенес в следующий )разряд). Поэтому вывод сразу /jpyx имшульсов, поступивших на вход 9, будет произведен не из первого, а из второго триггера ячейки 2 непосредственно во вт |рой триггер 19 счетчика 17. Этот выiBOA Производится опрашивающим импульсом, поступающим на вход 21,

Из изложенного следует, что частота поступления f ймпульсоа по каждому из входов может достигать разрешающей способности -суммирующего счетчика, так как импульсы, которые не будут выведены из I нулевых триггеров схемой опроса 11, бу- дг г. .-т гедены из единичных триггеров схемой .; роса 14 и т.д,

Очевидно также, что нет нужды делать все ячейки опроса, одинаковой емкости. S Поскольку частота обновления состояния триггеров каждого разряда в запоминак щей ячейке в два раза меньше, чем в предыдущем разряде, то при одинаковой частоте поступления опрашивающих импульсов, число разрядов в первой ячейке ;может быть сделано, равным одному, чис- |ло разрядов во второй и третьей ячейках :двум, число разрядов в ячейках с четвертой по : седьмую трем и т,д.

Формула изобретения

Многовходовый счетчик импульсов,- со- держащий суммирующий счетчик, трйггер:ный регистр с числом разрядов, равным ч 1блу;входных щин, Содвржащий цепочку последовательного опроса и сброса триггеров, выходы регистра через схему ИЛИ соединены со счетнь4м входом первого

разряда суммирующего , отличающийся тем, что, с целью повышения предельнсй частоты следования импульсов, Бхо.цные шииы соед1гаекы со сштvbn-iK вжояами триггеров регистра, а выхоам

1триггеров регистра соединены со счетными входами триггероэ дополнительного , соаержашего цепочку последовательногоопроса и сброса триггеров, при

(чем выходы триггеров дойолнительного регистра соединены через введенную схему ИЛИ с дополнительным счетным вхо|дом второго разряда суммирующего счетчика..

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОВХОДОВЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1973 |

|

SU375797A1 |

| МНОГОВХОДОВОЙ СЧЕТЧИК ИМПУЛЬСОВ* | 1971 |

|

SU316197A1 |

| МНОГОВХОДОВОЙ СЧЕТЧИК ИМПУЛЬСОВ | 1970 |

|

SU266392A1 |

| Устройство переменного приоритета | 1988 |

|

SU1585797A1 |

| Устройство для моделирования графов | 1983 |

|

SU1124318A1 |

| УСТРОЙСТВО для СЧИТЫВАНИЯ ОСЦИЛЛОГРАММ | 1968 |

|

SU218546A1 |

| Устройство для регистрации временных и информационных процессов | 1986 |

|

SU1363258A1 |

| Устройство для опроса информационных каналов | 1980 |

|

SU955067A1 |

| Устройство для временного программного управления | 1985 |

|

SU1290259A1 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

Фиг. 2

Авторы

Даты

1976-05-05—Публикация

1974-03-21—Подача