(54) УСТРОЙСТВО для ОПРОСА ИНФОРМАЦИОННЫХ КАНАЛОВ

1

Изобретение относится к телемеханике и вычислительной технике и предназначено для использования в устройствах программного опроса информационных каналов .с автоматическим выбором порядка опроса.

Известно устройство для опроса инфор- 5 мационных каналов, содержащее счетчики кадра и сканирования, блок анализа, регистр команд, запоминающее устройство, дешифратор, сумматор и операционный регистр 1.

Недостаток данного устройства - тре- Q бование к совпадению адресов ячеек памяти, в которых записаны коды частот опроса каналов с номерами этих каналов, что ограничивает возможность оперативного вмешательства в процесс работы устройства.

Наиболее близким к предлагаемому яв- 15 ляется устройство для опроса телеметрических каналов, содержащее последовательно соединенные счетчик, запоминающее устройство, блок анализа, мультиплексор, два регистра, блок ключей, элемент И, триггер, о два сумматора, второе запоминающее устройство, а также тактовую и входную шины 2.

Недостатком известного устройства является жесткая зависимость частоты опроса

какого-либо из каналов от высших частот опроса, что сужает базовый набор частот и затрудняет возможность оперативного изменения очередности и частот опроса каналов в процессе работы устройства.

Цель изобретения - расширение области применения устройства.

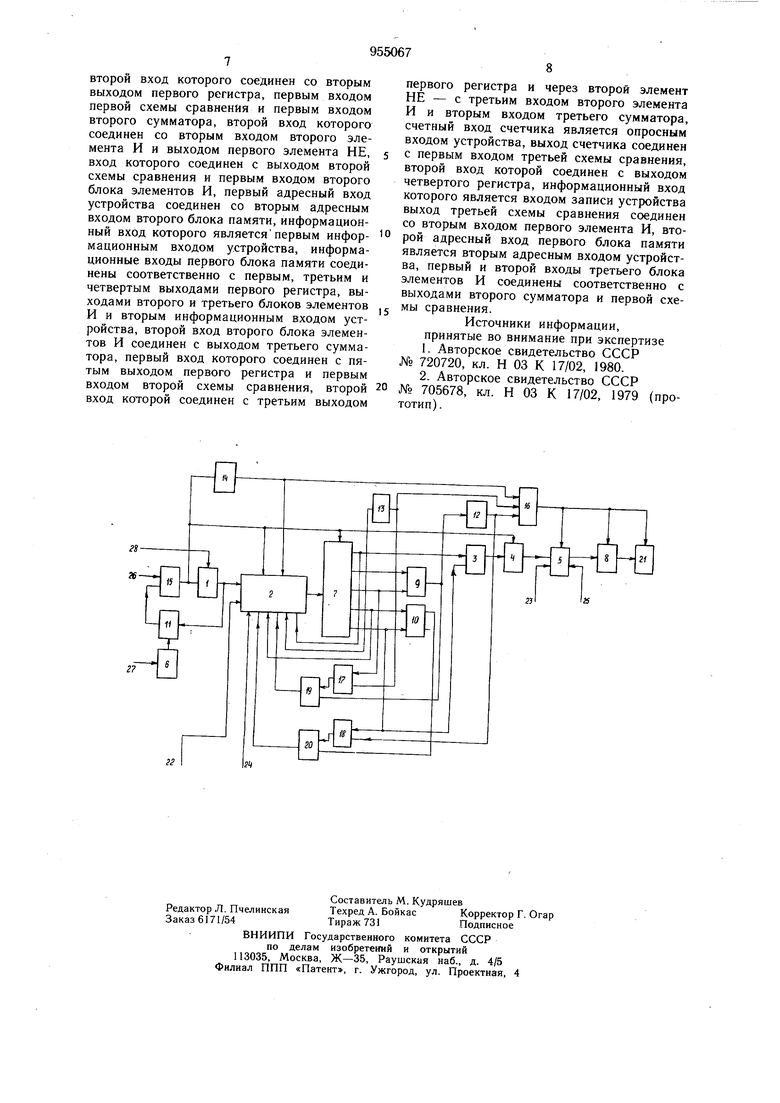

Поставленная цель достигается тем, что в устройство для опроса информационных каналов, содержащее два блока памяти, счетчик, два регистра, первый элемент И, два сумматора и первый блок элементов И, причем выход первого элемента И соединен с тактовым входом счетчика, выход которого соединен с первым адресным входом первого блока памяти, первый выход первого регистра соединен с первым входом первого сумматора, первый вход первого элемента И является тактовым входом устройства, введены два элемента НЕ, второй элемент И, третий и четвертый регистры, второй и третий блоки элементов И, третий сумматор, три схемы сравнения и элемент задержки, причем выход первого элемента И соединен с тактовыми входами первого блока памяти, первого и второго регистров и через элемент задержки - со входом считывания первого блока памяти и первым входом второго элемента И, выход которого соединен с тактовыми входами второго блока памяти, и третьего регистра и первым входом первого блока элементов И, второй вход которого соединен с Выходом третьего регистра, вход которого соединен с выходом второго блока памяти, первый адресный вход которого соединен с выходом второго регистра, вход которого соединен с выходом первого сумматора, второй вход которого соединен со вторым выходом первого регистра, первым входом первой схемы сравнения и первым входом второго сумматора, второй вход которого соединен со вторым входом второго элемента И и выходом первого элемента НЕ, вход которого соединен с выходом второй схемы сравнения и первым входом второго блока элементов И, первый адресный вход устройства соединен со вторым адресным входом второго блока памяти, информационный вход которого является первым информационным входом устройства, информационные входы первого блока памяти соединены соответственно с первым, третьим и четвертым выходами первого регистра, выходами второго и третьего блоков элементов И и вторым информационным входом устройства, второй вход второго блока элементов И соединен с выходом третьего сумматора, первый вход которого соединен с пятым выходом первого регистра и первым входом второй схемы сравнения, второй вход которой соединен, с третьим выходом первого регистра и через второй элемент НЕ - с третьим входом второго элемента И и вторым входом третьего сумматора, счетный вход счетчика является опросным входом устройства, выход счетчика соединен с первым входом третьей схемы сравнения, второй вход которой соединен с выходом четвертого регистра, информационный вход которого является входом записи устройства выход третьей схемы сравнения соединен со вторым входом первого элемента И, второй адресный вход первого блока памяти является вторым адресным входом устройства, первый и второй входы третьего блока элементов И соединены соответственно с выходами второго сумматора и первой схемы сравнения. На чертеже представлена структурная схема устройства для опроса информационных каналов. Устройство содержит счетчик 1, блок 2 памяти, сумматор 3, регистр 4, блок 5 памяти, регистры 6-8, схемы сравнения 9-11, элементы НЕ 12 и 13, элемент 14 задержки, элементы И 15 и 16, сумматоры 17 и 18, блоки элементов И 19-21, адресные входы 22 и 23, информационные входы 24 и 25, тактовый вход 26, вход 27 записи и опросный 28 вход устройства. Предлагаемое устройство работает следующим образом. Устройство осуществляет опрос информационных каналов с любой из частот в целое число раз меньших базовой частоты опроса. Частота опроса каждого из каналов не зависит ни от номера этого канала, ни от частот опроса других каналов и может оперативно изменяться во время работы устройства. Перед началом работы (при необходимости и во время работы) в каждую из ячеек запоминающего устройства 5 по входу 25 записывается номер канала, подлежащего опросу по адресу со входа 23 (адресация начинается с нулевой ячейки), причем номера каналов, опрашиваемых с одинаковой частотой, заносятся в последовательно расположенные ячейки, т. е. объединяются в группы. В каждую из ячеек запоминающего устройства 2 по входу 24 записывается информация об одной из групп каналов (адресация начинается с первой ячейки), опрашиваемых с одинаковой частотой. Каждая ячейка запоминающего устройства 2 условно разделена на пять групп по несколько разрядов Е каждой. Группа младших разрядов используется для организации счетчика опрашиваемых каналов (в исходном состоянии записываются нули), в следуюп1ей группе записывается число, на единицу меньшее количества каналов, опрашиваемых с данной частотой, последующая группа разрядов отводится под организацию счетчика опроса (исходное состояние - нулевое), далее записывается число, на единицу меньшее коэффициента деления базовой частоты опроса nj, а в старшие разряды заносится адрес группы каналов, опрашиваемых с данной частотой. В регистр 6 записывается число, на единицу большее количества групп каналов ш, опрашиваемых с одинаковой частотой. На вход 26 поступает тактовая частота, которая в m или более раз выше базовой частоты опроса. Импульс опроса по входу 28 устанавливает счетчик 1 в нулевое состояние в результате чего на выходе схемы 11 сравнения устанавливается уровень, разрешающий прохождение тактовых импульсов через элемент И 15 на вход счетчика I. В течение периода между импульсами опроса тактовые импульсы поочередно выбирают из блока 2 информацию о группах каналов, используемую для определения номеров каналов, которые необходимо опросить в данный интервал времени. Тактовые импульсы поступают на счетный вход работающего по переднему фронту счетчика 1, поочередно устанавливая тем самым адреса ячеек, подлежащих выборке из блока 2. Передним фронтом каждого тактового импульса осуществляется считывание содержимого очередной ячейки блока 2 и их запись в регистр 7. В сумматоре 3 суммируются начальный адpec группы каналов, опрашиваемых с одинаковой частотой, со значением счетчика опрашиваемых каналов (исходное состояние счетчика - нуль). Сформированный таким образом адрес ячейки с номером опрашиваемого канала записывается в регистр 4 передним фронтом тактового импульса, а оттуда поступает на адресный вход йлока 5. Разрешающий считывание сигнал формируется на выходе схемы 9 сравнения. Если значение счетчика опрора (третий выход регистра 7) более чем на единицу отличается от коэффициента деления базовой частоты опроса (не совпадает с четвертым выходом регистра 7), то на выходе схемы 9 сравнения устанавливается уровень «1, разрешающий прохождение через блок 19 неизмененного или увеличенного на единицу в сумматоре 17 значения счетчика опроса для дальнейшей перезаписи его в соответствующие разряды ячейки блока 2. Перезапись значения счетчика опроса без изменений происходит тогда, когда данная группа каналов должна быть исключена из опроса, т. е. во всех его разрядах записаны значения «1, что вызывает появление на выходе элемента НЕ 13 запрещающего уровня «О. Таким образом, после поступления п импульсов опроса на выходе схемы 9 устанавливается значение «О. В этом случае на выходе элемента НЕ 12 устанавливается уровень, разрешающий прохождение задержанного элементом задержки 15 тактового импульса через элемент И 16. Этот импульс задним фронтом считывает из блока 5 но.мер опрашиваемого канала, записывает его в регистр 8 и разрешает блоку 31 опрос канала. В то же время на выходе блока 19 устанавливаются нулевой уровень, т. е. происходит установка счётчика опроса в исходное состояние, и происходит подготовка для выборки содержимого следующей ячейки блока 5, т. е. для опроса через nj импульсов опроса следующего канала. Для этого значение счетчика опрашиваемых каналов в сумматоре 18 увеличивается на единицу. Схема 10 сравнения определяет, опрошены ли все каналы данной группы. Если нет, то на ее выходе устанавливается потенциал, разрешающий прохождение через блок 20 нового значения счетчика опрашиваемых каналов на один из входов блока 2 с целью дальнейщей его перезаписи в соответствующие разряды ячейки. Б противном случае сигнал с выхода схемы 10 устанавливает на выходе блока 20 нулевой уровень, приводя тем самым счетчик опрашиваемых каналов в исходное состояние для того, чтобы вновь начать опрос каналов данной группы. Значения второй, четвертой и пятой, а также измененные значения первой и третьей групп разрядов регистр 7 задним фронтом задержанного тактового импульса записываются в ячейку блока 2. С приходом следующего тактового импульса значение счетчика 1 увеличивается на единицу, происходит выборка содержимого следующей ячейки блока 2 и все последующие операции. Этот процесс происходит, пока значение счетчика 1 не совпадает с содержимым регистра 6, т. е. не прочитаны все ячейки блока 2. В этом случае сигнал, поступающий с выхода схемы 11, блокирует прохождение тактовых импульсов через элемент И 15. Следующий импульс опроса устанавливает счетчик 1 в исходное состояние и весь процесс повторяется. Таким образом, в течение времени между двумя импульсами опроса поочередно анализируются все ячейки блока 2 и опрашиваются необходимые каналы. Если возникает необходимость изменения порядка опроса каналов, их номеров или частот опроса (что определяется внешними устройствами), то это легко осуществляется коррекцией исходных данных в блоках 2 и 5 и регистре 7 по входам 22-25 и 27. Таким образом, предлагаемое устройство позволяет производить опрос каналов с автоматической настройкой на любые независимые друг от друга частоты опроса и легко изменять режимы опроса в процессе работы устройства, что позволяет ему найти широкое применение в телеметрических и вычислительных системах. Формула изобретения Устройство для опроса информационных каналов, содержащее два блока памяти, счетчик, два регистра, первый элемент И, два сумматора и первый блок элементов И, причем выход первого элемента И соединен с тактовы.м входом счетчика,- вь1ход которого соединен с первым адресным входом первого блока памяти, первый выход первого регистра соединен с первым входом первого сумматора, первый вход первого элемента И является тактовым входом устройства, отличающееся тем, что, с целью расширения области применения, оно содержит два элемента НЕ, второй элемент И, третий и четвертый регистры, второй и третий блоки элементов И, третий сумматор, три схемы сравнения и элемент задержки, причем выход первого элемента И соединен с тактовыми входами первого блока памяти, первого и второго регистров и через элемент задержки со входом считывания первого блока памяти и первым входом второго элемента И, выход которого соединен с тактовыми входами второго блока памяти и третьего регистра и первым входом первого блока элементов И, второй вход которого соединен с выходом третьего регистра, вход которого соединен с выходом второго блока памяти, первый адресный вход которого соединен с выходом второго регистра, вход которого соединен с выходом первого сумматора. второй вход которого соединен со вторым выходом первого регистра, первым входом первой схемы сравнения и первым входом второго сумматора, второй вход которого соединен со вторым входом второго эле мента И и выходом первого элемента НЕ, вход которого соединен с выходом второй схемы сравнения и первым входом второго блока элементов И, первый адресный вход устройства соединен со вторым адресным входом второго блока памяти, информационный вход которого являетсяпервым информационным входом устройства, информационные входы первого блока памяти соединены соответственно с первым, третьим и четвертым выходами первого регистра, выходами второго и третьего блоков элементов И и вторым информационным входом устройства, второй вход второго блока элементов И соединен с выходом третьего сумматора, первый вход которого соединен с пятым выходом первого регистра и первым входом второй схемы сравнения, второй вход которой соединен с третьим выходом первого регистра и через второй элемент НЕ - с третьим входом второго элемента И и вторым входом третьего сумматора, счетный вход счетчика является опросным входом устройства, выход счетчика соединен с первым входом третьей схемы сравнения. второй вход которой соединен с выходом четвертого регистра, информационный вход которого является входом записи устройства выход третьей схемы сравнения соединен со вторым входом первого элемента И, второй адресный вход первого блока памяти является вторым адресным входом устройства, первый и второй входы третьего блока элементов И соединены соответственно с выходами второго сумматора и первой схемы сравнения. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 720720, кл. Н 03 К 17/02, 1980. 2. Авторское свидетельство СССР jvb 705678, кл. Н 03 К 17/02, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Устройство для опроса информационных датчиков | 1983 |

|

SU1172085A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Многоканальное устройство для сравнения кодов | 1990 |

|

SU1795446A1 |

| Устройство для управления обменом информацией | 1990 |

|

SU1783525A1 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| Устройство для ввода и вывода информации | 1990 |

|

SU1709295A1 |

| Многоканальное измерительное устройство для цифровой фильтрации | 1985 |

|

SU1252919A1 |

Авторы

Даты

1982-08-30—Публикация

1980-11-17—Подача