памяти, блок 3 управления, счетчик 4 времени, сумматор 5, группу 6 первых элементов И, блок 7 оперативной памяти, регистр 8, группу 9 элементов ЭКВИВАЛЕНТНОСТЬ, две группы 10, 16 элементов НЕ, элементы 13, 19 НЕ, элементы 11, 12, 15, 17, 20, 21, 23 И, блок передачи ,информации, блок 27 сбора информации, блок 26 исполнительных элементов, элементы ИЛИ

1

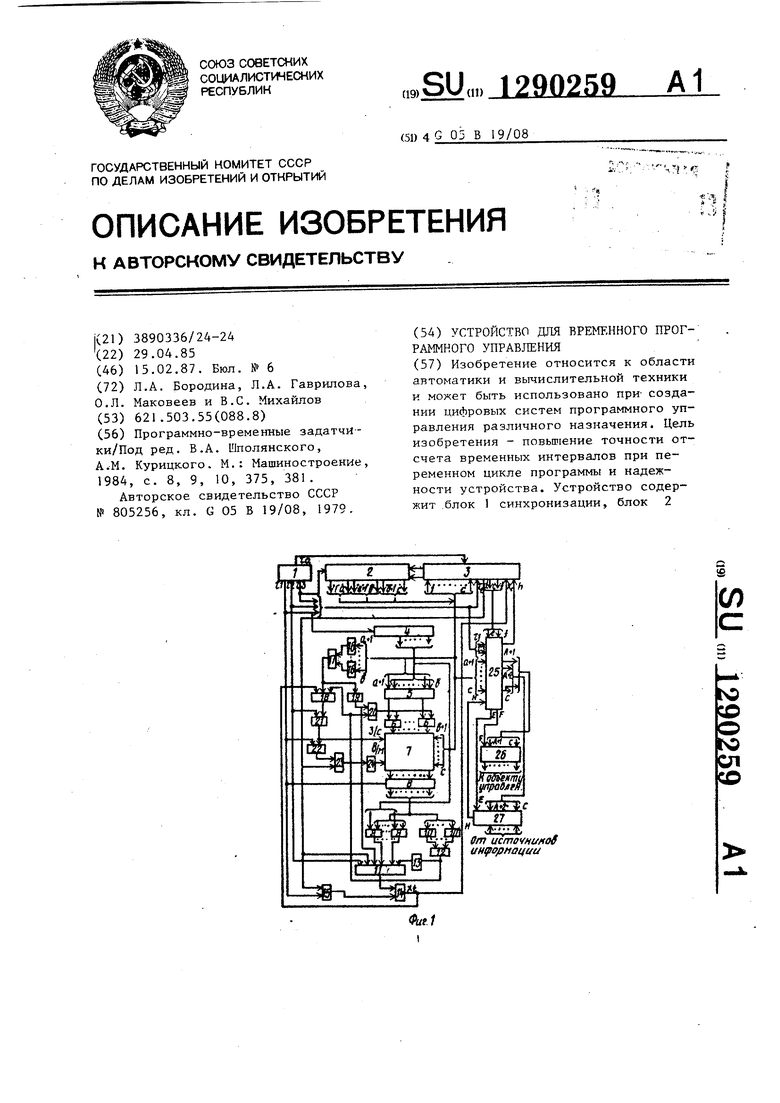

Изобретение относится к автоматике и вычислительной технике и может быть использовано при создании цифровых систем программного управления различного назначения.

Целью изобретения является повышение точности отсчета временных интервалов при переменном цикле программы и надежности устройства.

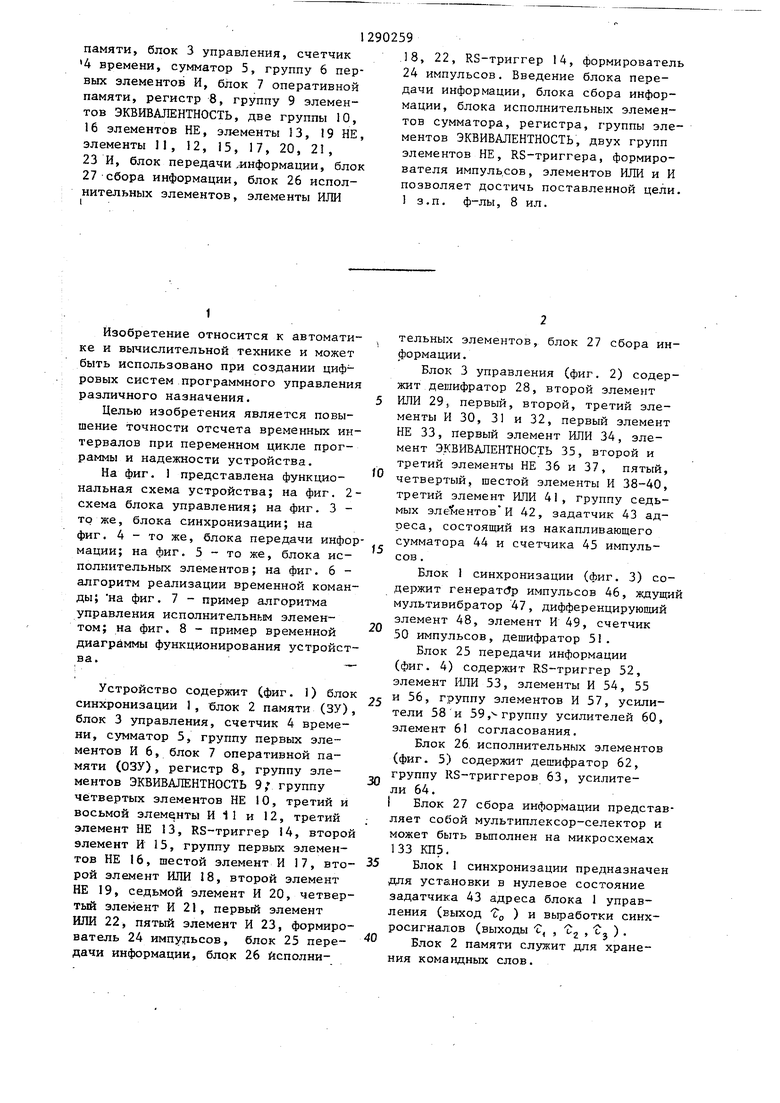

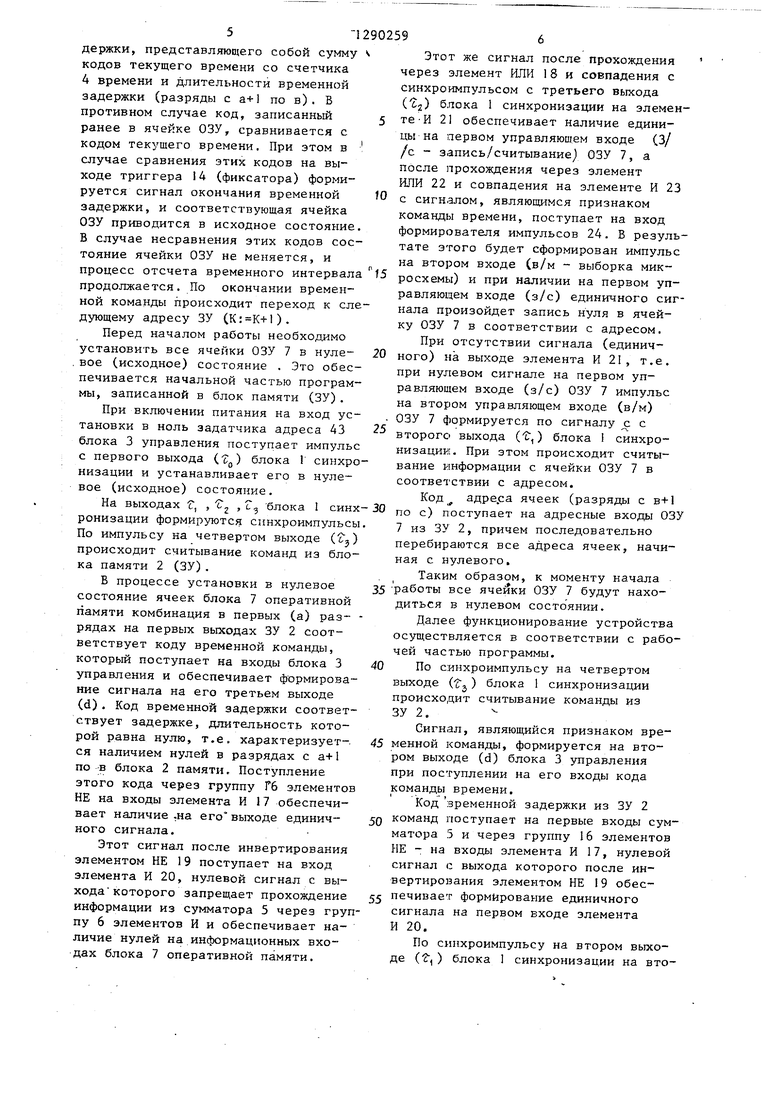

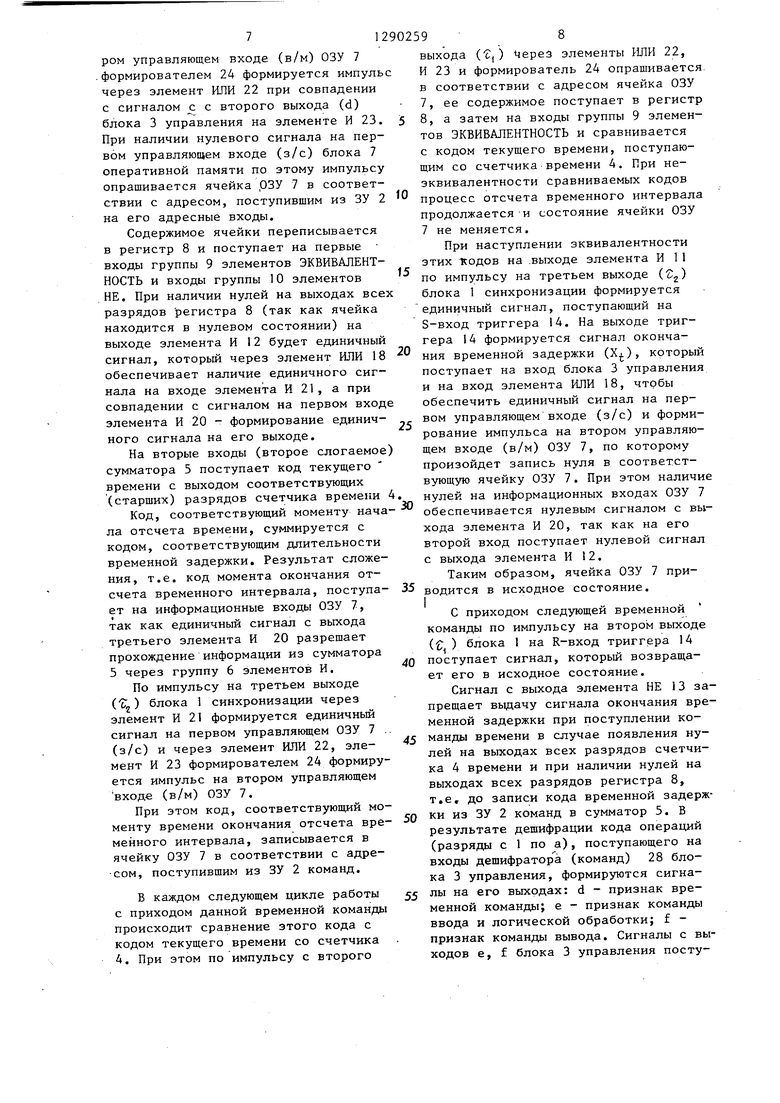

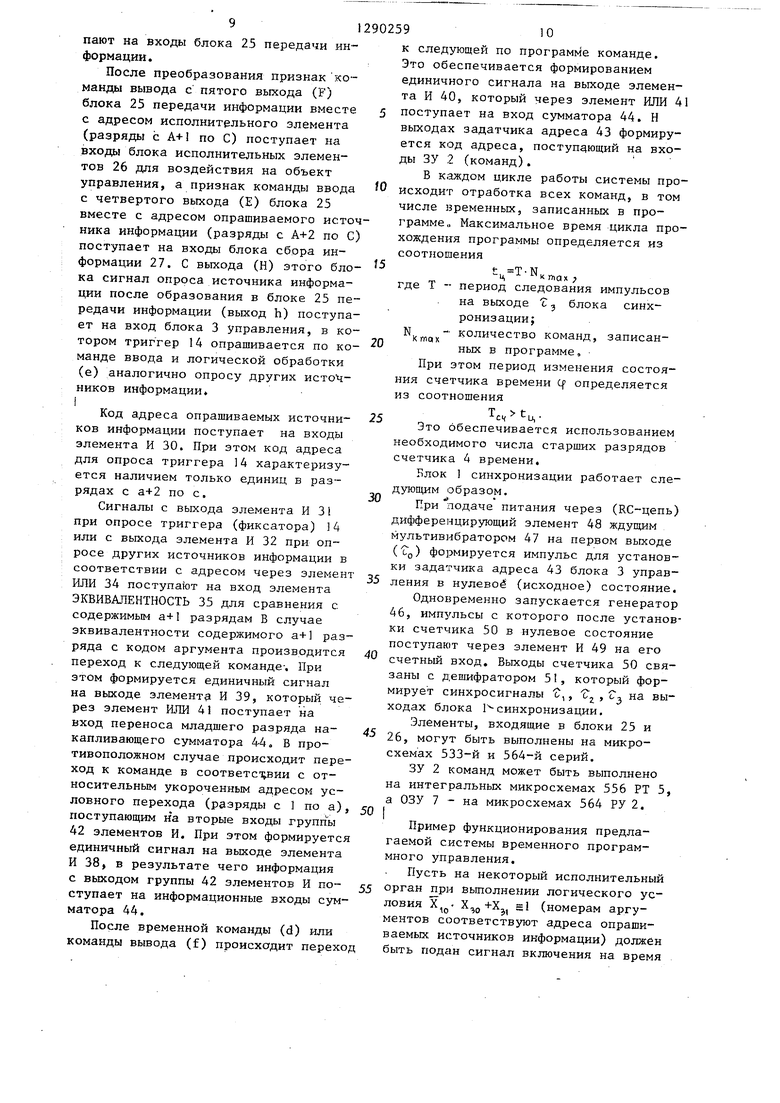

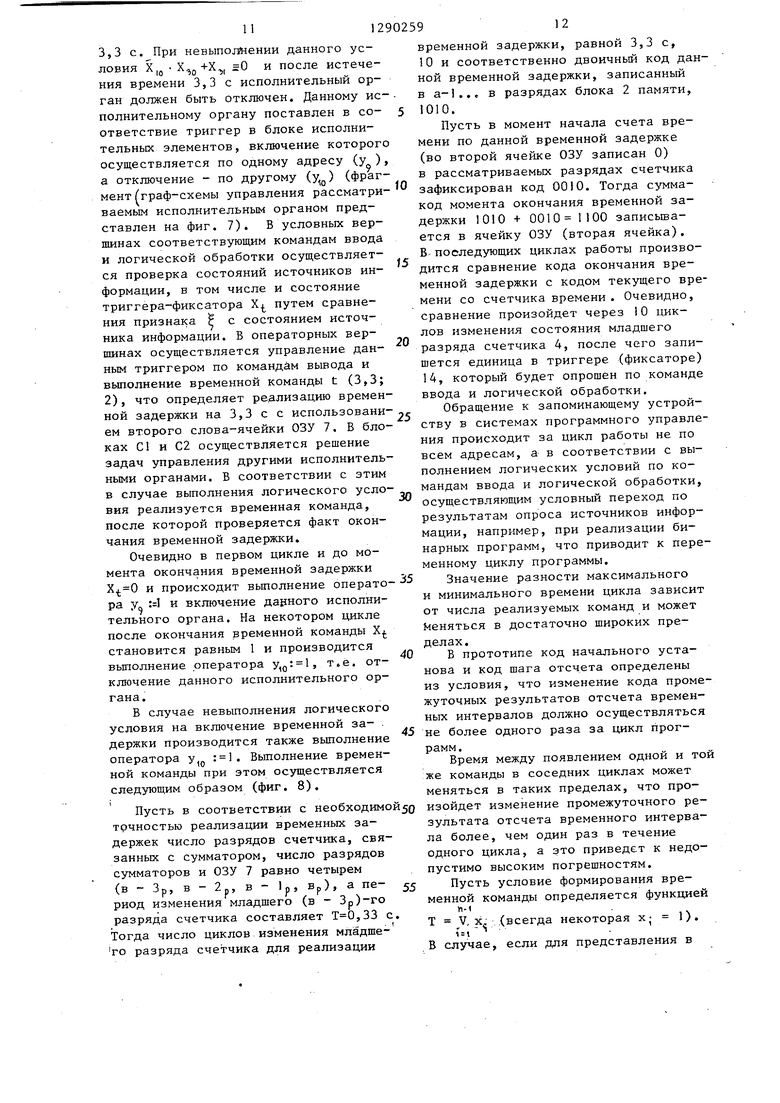

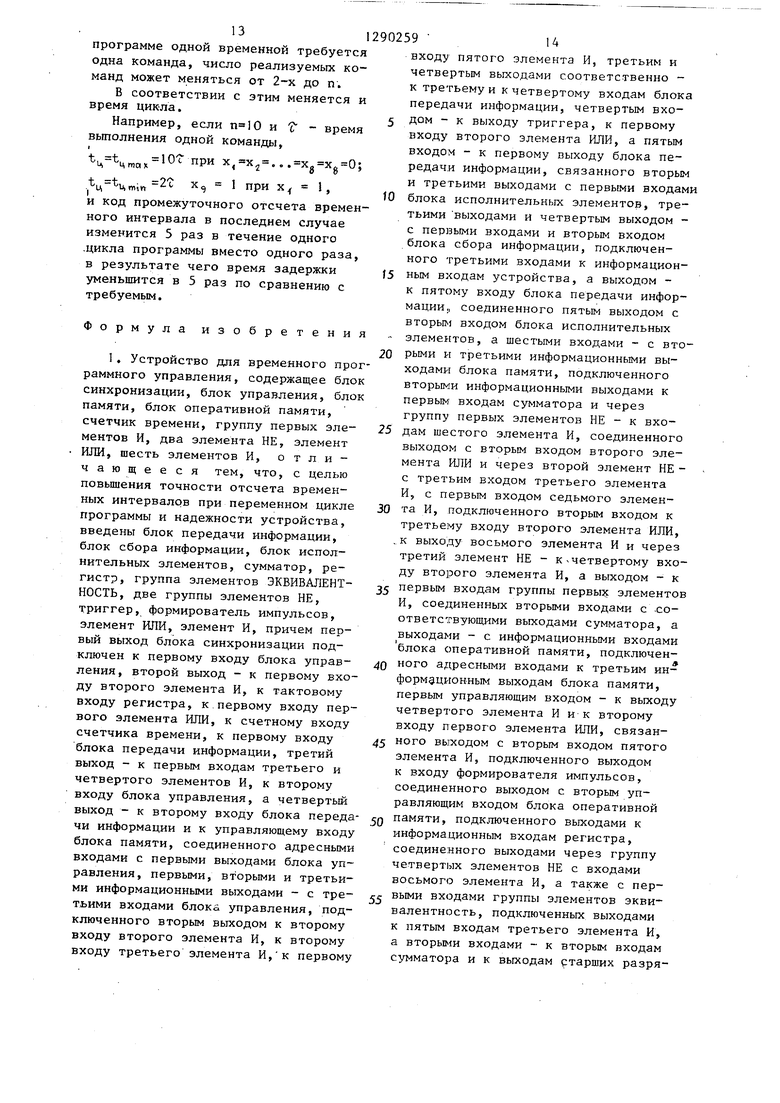

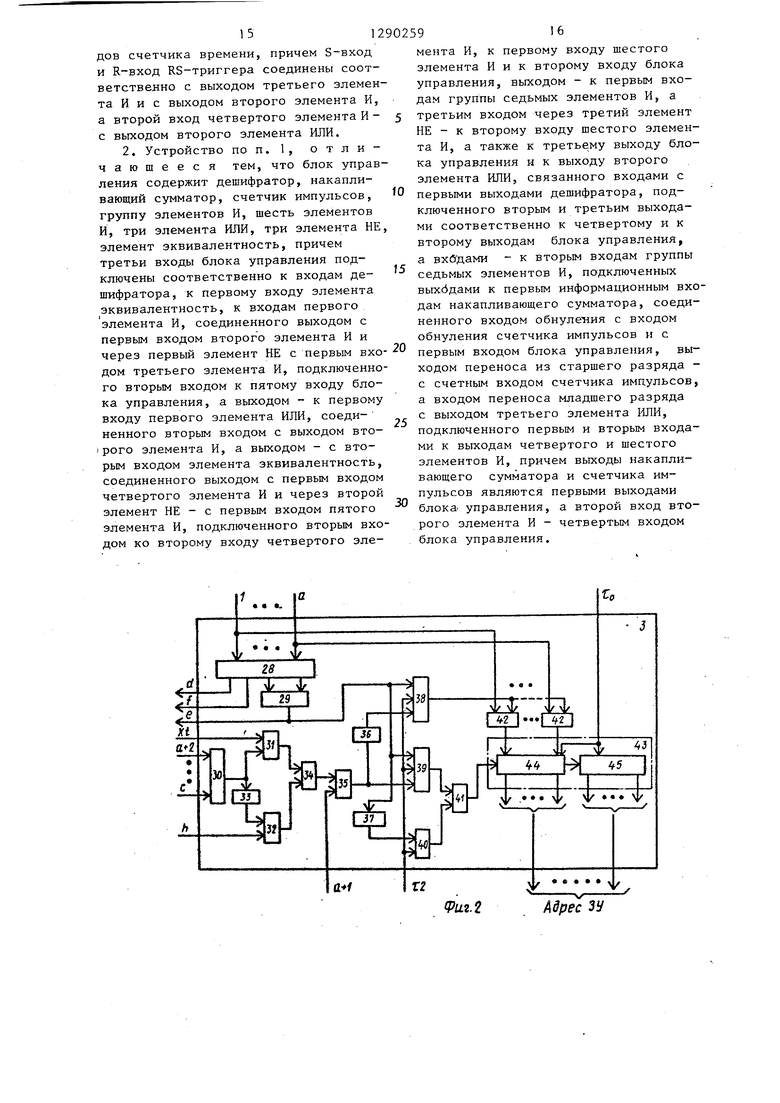

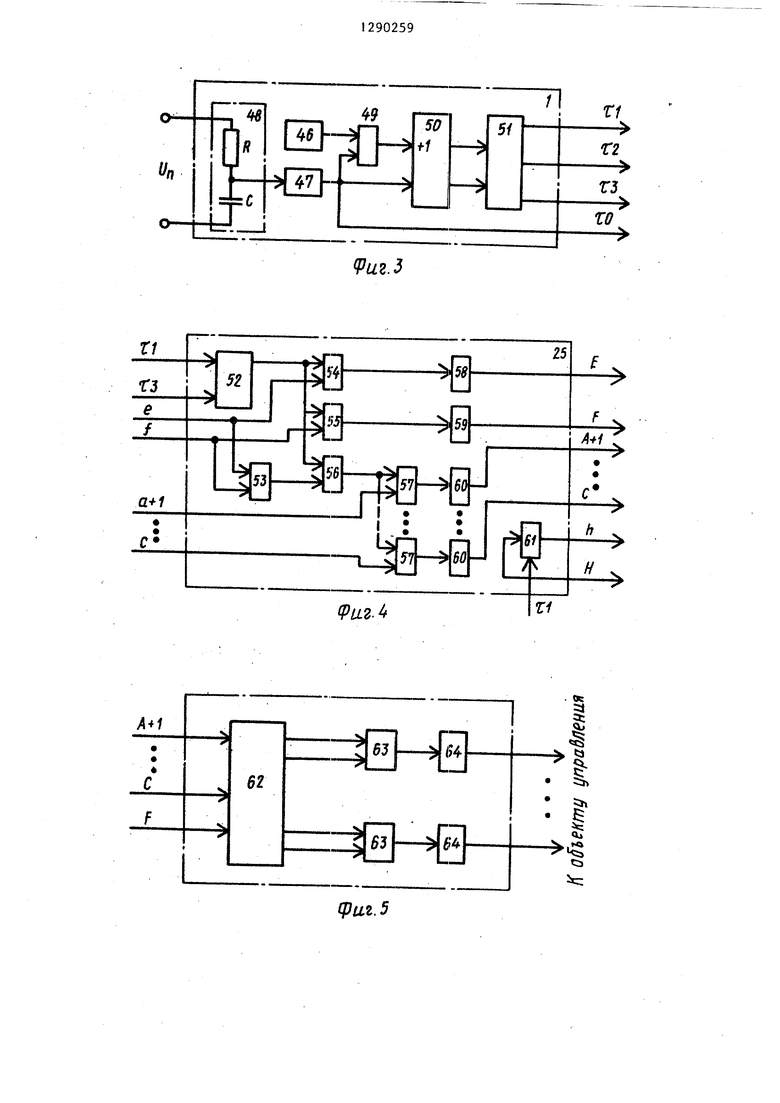

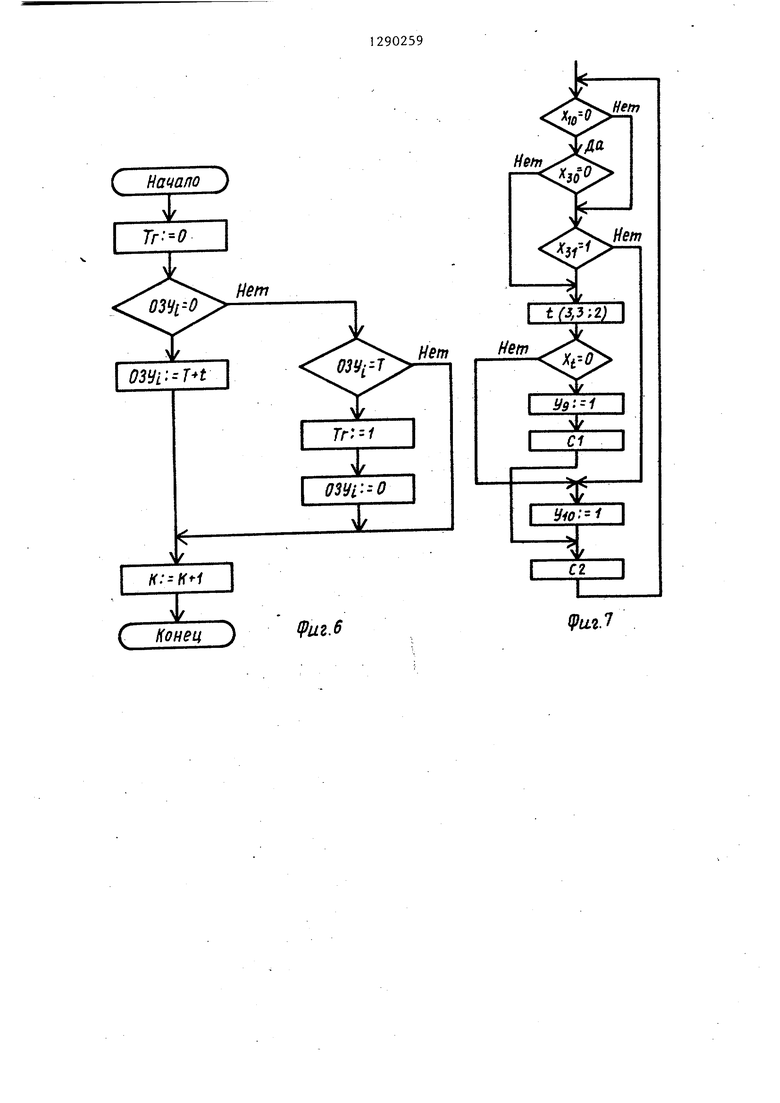

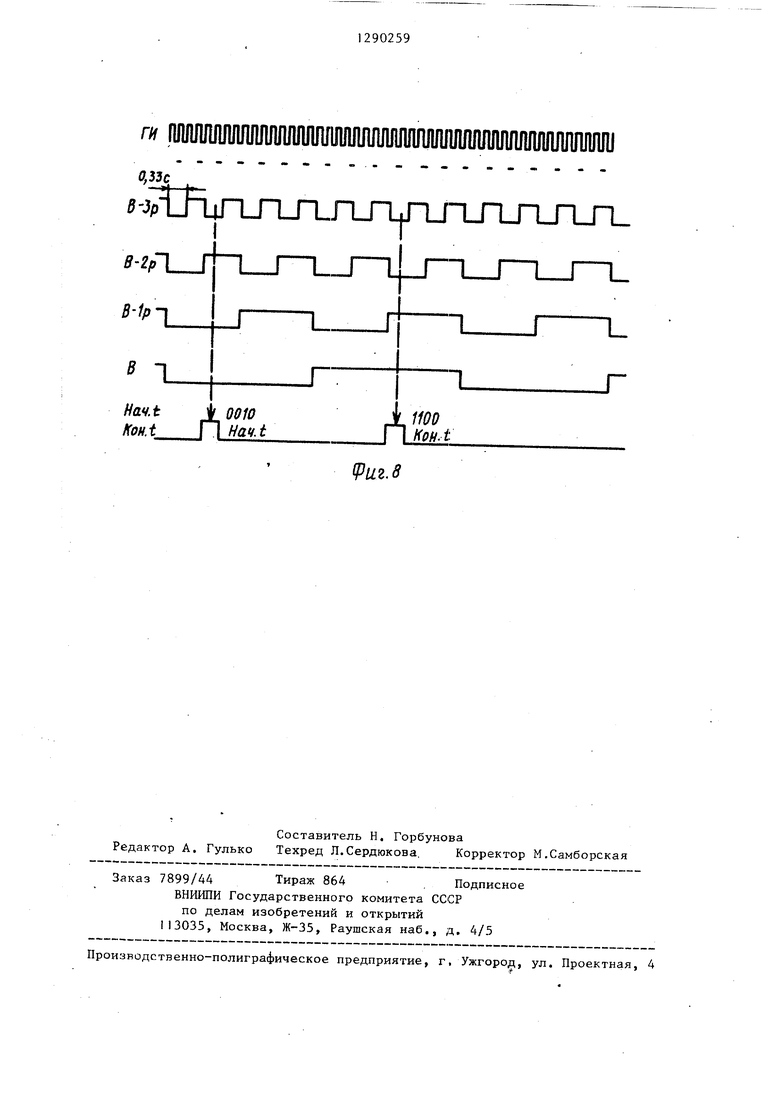

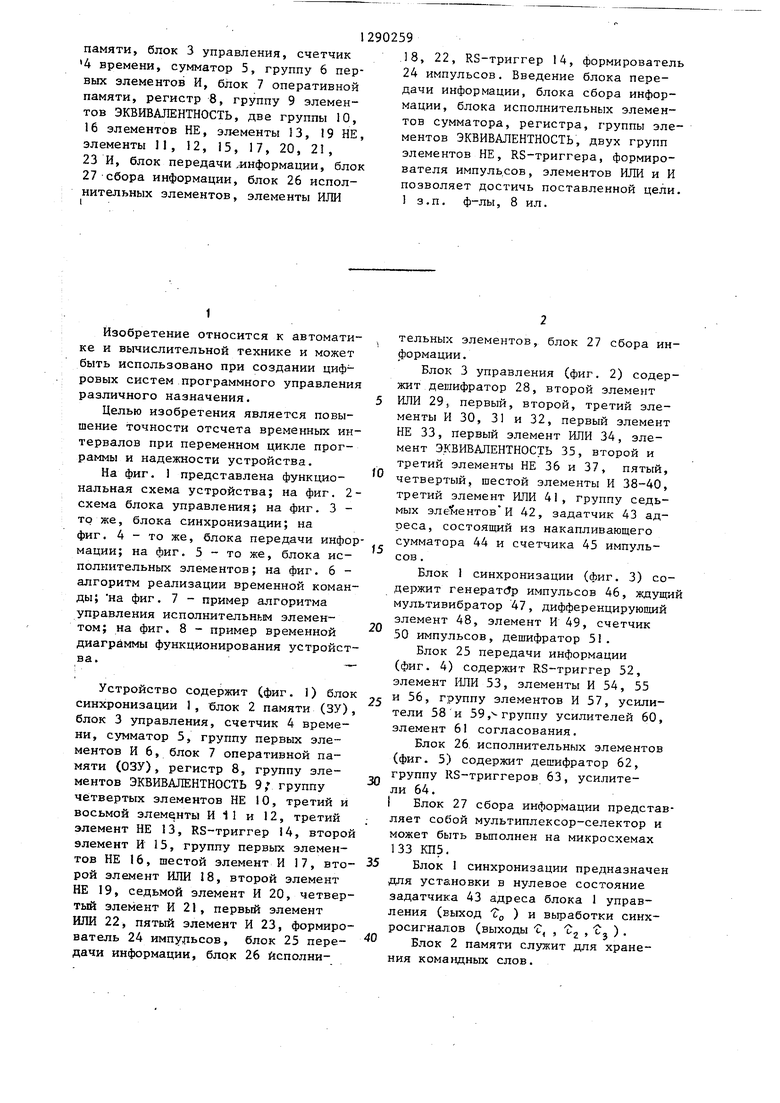

На фиг. 1 представлена функциональная схема устройства; на фиг. 2- схема блока управления; на фиг. 3 - то же, блока синхронизации; на фиг. 4 - то же, блока передачи информации; на фиг. 5 - то же, блока исполнительных элементов; на фиг. 6 - алгоритм реализации временной команды; на фиг. 7 - пример алгоритма управления исполнительным элементом; на фиг. 8 - пример временной диаграммы функционирования устройства.-

Устройство содержит (фиг. 1) блок синхронизации 1, блок 2 памяти (ЗУ), блок 3 управления, счетчик 4 времени, сумматор 5, группу первых элементов И 6, блок 7 оперативной памяти (ОЗУ), регистр 8, группу элементов ЭКВИВАЛЕНТНОСТЬ 9; группу че:твертых элементов НЕ 10, третий и восьмой элементы И 11 и 12, третий элемент НЕ 13, RS-триггер 14, второй элемент И 15, группу первых элементов НЕ 16, шестой элемент И 17, второй элемент ИЛИ 18, второй элемент НЕ 19, седьмой элемент И 20, четвертый элемент И 21, первый элемент ИЛИ 22, пятый элемент И 23, формирователь 24 импульсов, блок 25 передачи информации, блок 26 йсполни18, 22, RS-триггер 14, формирователь 24 импульсов. Введение блока передачи информации, блока сбора информации, блока исполнительных элементов сумматора, регистра, группы элементов ЭКВИВАЛЕНТНОСТЬ, двух групп элементов НЕ, RS-триггера, формирователя импуль сов, элементов ИЛИ и И позволяет достичь поставленной цели. 1 3.п, ф-лы, 8 ил.

5

0

5

0

5

0

тельных элементов, блок 27 сбора информации.

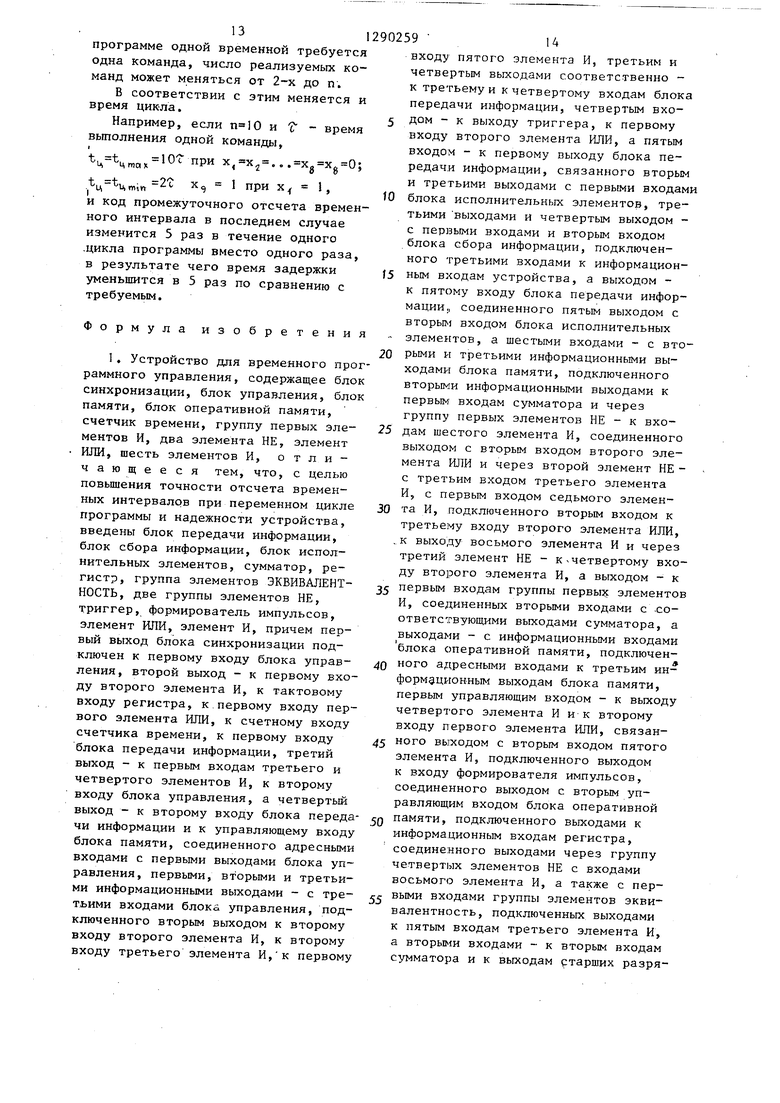

Блок 3 управления (фиг. 2) содержит дешифратор 28, второй элемент ИЛИ 29, первый, второй, третий элементы И 30, 31 и 32, первый элемент НЕ 33, первый элемент ИЛИ 34, элемент ЭКВИВАЛЕНТНОСТЬ 35, второй и третий элементы НЕ 36 и 37, пятый, четвертый, шестой элементы И 38-40, третий элемент ИЛИ 41, группу седьмых эле мантов И 42, задатчик 43 адреса, состоящий из накапливающего сумматора 44 и счетчика 45 импульсов .

Блок 1 синхронизации (фиг. 3) содержит генератор импульсов 46, ждущий мультивибратор 47, дифференцирующий элемент 48, элемент И 49, счетчик 50 импульсов, дешифратор 51.

Блок 25 передачи информации (фиг. 4) содержит RS-триггер 52, элемент ИЛИ 53, элементы И 54, 55 и 56, группу элементов И 57, усилители 58 и 59 , группу усилителей 60, элемент 61 согласования.

Блок 26 исполнительных элементов (фиг. 5) содержит дешифратор 62, группу RS-триггеров 63, усилители 64 .

I Блок 27 сбора информации представляет собой мультиплексор-селектор и может быть вьшолнен на микросхемах 133 КП5,

Блок I синхронизации предназначен для установки в нулевое состояние задатчика 43 адреса блока 1 управления (выход сГд ) и выработки синхросигналов (выходы С, , , L J ) .

Блок 2 памяти служит для хранения командных слов.

Блок 7 оперативной памяти служит для записи кодов моментов окончания временных интервалов (задержек), работает в режимах считывания и записи информации.

Блок 3 управления обеспечивает управление хадом программы за счет изменения состояния задатчика адреса команд в зависимости от кодов операций, состояния входной информации и значения истинности.

Формирователь 24 осуществляет выработку, импульсов выборки микросхемы с временным сдвигом относительно адресных и информационных входов, необ ходимым для устойчивого срабатывания блока 7 оперативной памяти выбранного типа.

Блок 25 передачи информации предназначен для выдачи кода адреса исполнительного элемента (вторые входы, разряды с А+1 по С) при наличии признака команды вывода (четвертый вход f) или кода адреса источника информации - датчика (третьи выходы, разряды с А + 2 по С) при наличии признака команды ввода (третий вход ё) и согласования параметров этих сигналов с входными сигналами (Р, F, А+1,о..,С) блоков 26 исполнительных /элементов и сбора информации 27 соответственно, а также согласования параметров сигнала опроса с выхода (Н) блока 27 сбора информации с входным сигналом (пятый вход h) блока 3 (по времени и уровню).

Блок исполните{1ьньгх элементов 26 предназначен для выдачи управ/хяющих воздействий на объект управления в соответствии с адресом исполнительного элемента при наличии признака команды вьшода (F),

Блок сбора информации 27 предназначен для опроса источников информации (датчиков) в соответствии с адресом при наличии признака команды ввода (Е) и выдачи сигнала результата опроса (Н).

Работа системы временного прог- раммного управления осуществляется по командам, записанным в блоке 2 памяти (ЗУ). Используются следующие типы команд: команда вьшода, команда ввода и логической обработ- ки, временная команда.

Число выходов блока 2 памяти соответствует .количеству разрядов командного слова.

5

0

. 5

0 5

0

5

Каждое командное слово может быть разбито на информационные поля.

Комбинации в первых разрядах : (первые выходы) на выходе блока 2 памяти соответствуют кодам операций ;. (команд).

Нулевая комбинация в разрядах с 1 по а представляет собой код команды вывода f, по которой происходит подача управляющего воздействия на исполнительные элементы (ИЭ). После выполнения этой команды происходит переход к следующей по программе команде, при этом разряды с а+1 по с представляют собой код адреса ИЭ.

Наличие хотя бы одной единицы в разрядах с 1 по а-1 определяет код команды ввода и логической обработки е, по которой происходит опрос источников информации (ИИ), анализ полученной информации .и переход по программе в соответствии с результатом опроса. Эти же разряды (с 1 по а, первые выходы блока 2) представляют собой код относительного укороченного адреса условного перехода, разряд а+1 определяет признак сравнения с состоянием источника информации h, а разряды с а+2 по с представляют собой код адреса опрашиваемого источника информации.

Наличие единицы в разряде а и нулей в разрядах с 1 по а-1 определяет код временной команды d, которая позволяет реализовать временные задержки. При этом разряды с а+ 1 по в (вторые выходы блока 2) определяют код длительности временной задержки, а разряды с в+1 по с - код адреса ячейки оперативного блока 4 памяти, в которую производится запись, хранение и считывание кода момента времени окончания отсчета временного интервала.

Принцип реализации временной команды заключается в следующем (фиг.6),

С приходом временной команды, зафиксированной, например, по адресу (к) блока 2 памяти, триггер 14 устанавливается в нулевое состояние и Б соответствии с адресом (разряды с в+1 по с) опрашивается ячейка блока 7 .

При этом, если данная ячейка ОЗУ находится в нулевом (исходном) состоянии, в нее производится запись кода момента окончания временной заш

5-1290259

держки, представляющего собой сумму v кодов текущего времени со счетчика А времени и длительности временной задержки (разряды с а-«-1 по в) . В противном случае код, записанный ранее в ячейке ОЗУ, сравнивается с кодом текущего времени. При этом в случае сравнения этих кодов на выходе триггера 14 (фиксатора) формируется сигнал окончания временной задержки, и соответствующая ячейка ОЗУ приводится в исходное состояние. В случае несравнения этих кодов состояние ячейки ОЗУ не меняется, и процесс отсчета временного интервала продолжается. По окончании временной команды происходит переход к следующему адресу ЗУ ().

Перед началом работы необходимо установить все ячейки ОЗУ 7 в нуле- . вое (исходное) состояние . Это обеспечивается начальной частью программы, записанной в блок памяти (ЗУ).

При включении питания на вход установки в ноль задатчика адреса A3 блока 3 управления поступает импульс

20

25

с первого выхода (f) блока 1 синхронизации и устанавливает его в нулевое (исходное) состояние.

На выходах f, , блока 1 ронизации формируются синхроимпульсы. По импульсу на четвертом выходе (j) происходит считывание команд из блока памяти 2 (ЗУ).

В процессе установки в нулевое состояние ячеек блока 7 оперативной памяти комбинация в первых (а) раз- - рядах на первых выходах ЗУ 2 соответствует коду временной команды, который поступает на входы блока 3 управления и обеспечивает формирование сигнала на его третьем выходе (d). Код временной задержки соответствует задержке, длительность которой равна нулю, т.е. характеризует-. ся наличием нулей в разрядах с а+1 по ;в блока 2 памяти. Поступление этого кода через группу Г6 элементов НЕ на входы элемента И 17 обеспечивает наличие-на его выходе единичного сигнала.

Этот сигнал после инвертирования элементом НЕ 19 поступает на вход элемента И 20, нулевой сигнал с выхода которого запрещает прохождение информации из сумматора 5 через группу 6 элементов И и обеспечивает наличие нулей на информационных входах блока 7 оперативной памяти.

Этот же сигнал после прохождения через элемент ИЛИ 18 и совпадения с синхро:импульсом с третьего выхода (t) блока 1 синхронизации на элементе-И 21 обеспечивает наличие единицы на первом управляющем входе (3/ /с - запись/считывание ОЗУ 7, а после прохождения через элемент ИЛИ 22 и совпадения на элементе И 23 с СИГН.ЗЛОМ, являющимся признаком команды времени, поступает на вход формирователя импульсов 2А. В результате этого будет сформирован импульс на втором входе (в/м - выборка мик росхемы) и при наличии на первом управляющем входе (з/с) единичного сигнала произойдет запись нуля в ячейку ОЗУ 7 в соответствии с адресом. При отсутствии сигнала (единичного) на выходе элемента И 21, т.е. при нулевом сигнале на первом управляющем входе (з/с) ОЗУ 7 импульс на втором управляющем входе (в/м) ОЗУ 7 формируется по сигналу jc с второго выхода (,) блока 1 синхронизации. При этом происходит считывание информации с ячейки ОЗУ 7 в соответствии с адресом.

Код адрера ячеек (разряды с в+1 синх- 30 по с) поступает на адресные входы ОЗУ 7 из ЗУ 2, причем последовательно перебираются все адреса ячеек, начиная с нулевого.

Таким образом, к моменту начала

35 работы все ячейки ОЗУ 7 будут находиться в нулевом состоянии.

Далее функционирование устройства осуществляется в соответствии с рабочей частью программы.

По синхроимпульсу на четвертом выходе (f, ) блока 1 синхронизации происходит считывание команды из ЗУ 2.

Сигнал, являющийся признаком вре45 менной команды, формируется на втором выходе (d) блока 3 управления при поступлении на его входы кода команды времени.

Код временной задержки из ЗУ 2

Q команд поступает на первые входы сумматора 5 и через группу 16 элементов НЕ - на входы элемента И 17, нулевой сигнал с выхода которого после инвертирования элементом НЕ I9 обес55 печивает формирование единичного сигнала на первом входе элемента И 20.

По с1П1хроимпульсу на втором выходе (б, ) блока 1 синхронизации на вто

ром управляющем входе (в/м) ОЗУ 7 .формирователем 24 формируется импуль через элемент ИЛИ 22 при совпадении с сигналом с с второго выхода (d) блока 3 управления на элементе И 23. При наличии нулевого сигнала на первом управляющем входе (з/с) блока 7 оперативной памяти по этому импульсу опрашивается ячейка РЗУ 7 в соответствии с адресом, поступившим из ЗУ 2 на его адресные входы.

Содержимое ячейки переписывается в регистр 8 и поступает на первые входы группы 9 элементов ЭКВИВАЛЕНТНОСТЬ и входы группы 10 элементов НЕ. При наличии нулей на выходах все разрядов регистра 8 (так как ячейка находится в нулевом состоянии) на выходе элемента И 12 будет единичный сигнал, который через элемент ИЛИ 18 обеспечивает наличие единичного сигнала на входе элемента И 21, а при совпадении с сигналом на первом вход элемента И 20 - формирование единичного сигнала на его выходе.

На вторые входы (второе слогаемое сумматора 5 поступает код текущего времени с выходом соответствующих (старших) разрядов счетчика времени

Код, соответствующий моменту нача ла отсчета времени, суммируется с кодом, соответствующим длительности временной задержки. Результат сложения, т.е. код момента окончания отсчета временного интервала, поступа- ет на информационные входы ОЗУ 7, так как единичный сигнал с выхода третьего элемента И 20 разрешает прохождение информации из сумматора 5 через группу 6 Элементов И.

По импульсу на третьем выходе СсГ.) блока 1 синхронизации через элемент И 21 формируется единичный сигнал на первом управлякнцем ОЗУ 7 .. (з/с) и через элемент ИЛИ 22, эле- мент И 23 формирователем 24 формируется импульс на втором управляющем входе (в/м) ОЗУ 7.

При этом код, соответствующий моменту времени окончания отсчета вре- менного интервала, записывается в ячейку ОЗУ 7 в соответствии с адресом, поступившим из ЗУ 2 команд.

В каждом следующем цикле работы с приходом данной временной команды происходит сравнение этого кода с кодом текущего времени со счетчика 4. При этом по импульсу с второго

5

О

5

выхода ( с, ) Через элементы 1-1ПИ 22, И 23 и формирователь 24 опрашивается в соответствии с адресом ячейка ОЗУ

7,ее содержимое поступает в регистр

8,а затем на входы группы 9 элементов ЭКВИВАЛЕНТНОСТЬ и сравнивается

с кодом текущего времени, поступающим со счетчика времени 4. При неэквивалентности сравниваемых кодов процесс отсчета временного интервала продолжается и состояние ячейки ОЗУ 7 не меняется.

При наступлении эквивалентности этих Кодов на .выходе элемента И 11 по импульсу на третьем выходе () блока 1 синхронизации формируется единичный сигнал, поступающий на S-вход триггера 14. На выходе триггера 14 формируется сигнал окончания временной задержки (Х), который поступает на вход блока 3 управления и на вход элемента ИЛИ 18, чтобы обеспечить единичный сигнал на первом управляющем входе (з/с) и формирование импульса на втором управляющем входе (в/м) ОЗУ 7, по которому произойдет запись нуля в соответствующую ячейку ОЗУ 7. При этом наличие нулей на информационных входах ОЗУ 7 обеспечивается нулевым сигналом с выхода элемента И 20, так как на его второй вход поступает нулевой сигнал с выхода элемента И 12.

Таким образом, ячейка ОЗУ 7 приводится в исходное состояние.

С приходом следующей временной команды по импульсу на втором выходе (Г ) блока 1 на R-вход триггера 14 поступает сигнал, который возвращает его в исходное состояние.

Сигнал с выхода элемента НЕ 13 запрещает выдачу сигнала окончания временной задержки при поступлении команды времени в случае появления нулей на выходах всех разрядов счетчика 4 времени и при наличии нулей на выходах всех разрядов регистра 8, т.е, до записи кода временной задержки из ЗУ 2 команд в сумматор 5. В результате дешифрации кода операций (разряды с 1 по а), поступающего на входы дешифратора (команд) 28 блока 3 управления, формируются сигналы на его выходах: d - признак временной команды; е - признак команды ввода и логической обработки; f - признак команды вывода. Сигналы с выходов е, f блока 3 управления поступают на входы блока 25 передачи информации.

После преобразования признак команды вывода с пятого выхода (F) блока 25 передачи информации вместе с адресом исполнительного элемента (разряды с А+1 по С) поступает на входы блока исполнительных элементов 26 для воздействия на объект управления, а признак команды ввода с четвертого выхода (Е) блока 25 вместе с адресом опрашиваемого источника информации (разряды с А+2 по С) поступает на входы блока сбора информации 27. С выхода (Н) этого бло- ка сигнал опроса источника информации после образования в блоке 25 передачи информации (выход h) поступает на вход блока 3 управления, в котором триггер 14 опрашивается по ко- манде ввода и логической обработки (е) аналогично опросу других исто11- ников информации

Код адреса опрашиваемых источни- ков информации поступает на входы элемента И 30. При этом код адреса для опроса триггера 14 характеризуется наличием только единиц в разрядах с а+2 по с.

Сигналы с выхода элемента И 31 при опросе триггера (фиксатора) 14 или с выхода элемента И 32 при опросе других источников информации в соответствии с адресом через элемент ИЛИ 34 поступают на вход элемента ЭКВИВАЛЕНТНОСТЬ 35 для сравнения с содержимым а+1 разрядам В случае эквивалентности содержимого а+ разряда с кодом аргумента производится переход к следующей команде-. При этом формируется единичный сигнал на выходе элемента И 39, который через элемент ИЛИ 41 поступает на вход переноса младшего разряда на- капливающего сумматора 44. В противоположном случае происходит переход к команде в соответст вии с относительным укороченным адресом условного перехода (разряды с 1 по а) поступающим н а вторые входы групп ы 42 элементов И. При этом формируетс единичный сигнал на выходе элемента И 38, в результате чего информация с выходом группы 42 элементов И по- ступает на информационные входы сумматора 44.

После временной команды (d) или команды вывода (f) происходит перех

к следующей по программе команде. Это обеспечивается формированием единичного сигнала на выходе элемента И 40, который через элемент ИЛИ 4 поступает на вход сумматора 44. Н выходах задатчика адреса 43 формируется код адреса, поступающий на входы ЗУ 2 (команд).

В к;аждом цикле работы системы происходит отработка всех команд, в том числе ззременньк, записанных в программе,. Максимальное время цикла прохождения программы определяется из соотношения

«- T-N

-ц - к шах ;

где Т -- период следования импульсов

на вькоде ронизации;

блока синхN - количество команд, записанК moi X

ных в программе.

При этом период изменения состояния счетчика времени Cf определяется из соотношения

T,,t.

Это обеспечивается использованием необходимого числа старших разрядов счетчика 4 времени.

Блок 1 синхронизации работает следующим образом.

При подаче питания через (RC-цепь) дифференцирующий элемент 48 ждущим мультивибратором 47 на первом выходе (Сд) формируется импульс для установки задатчика адреса 43 блока 3 управления в нулевое (исходное) состояние

Одновременно запускается генератор 46, импульсы с которого после установки счетчика 50 в нулевое состояние поступают через элемент И 49 на его счетный вход. Выходы счетчика 50 связаны с дешифратором 5I, который формирует синхросигналы о,, Г , С на выходах блока 1 синхронизации.

Элементы, входящие в блоки 25 и 26, могут быть выполнены на микросхемах 533-й и 564-й серий.

ЗУ 2 команд может быть выполнено на интегральных микросхемах 556 РТ 5, а ОЗУ 7 - на микросхемах 564 РУ 2.

Пример функционирования предлагаемой системы временного программного управления.

Пусть на некоторый исполнительный орган при вьшолнении логического условия . X Q+Xj| 1 (номерам аргументов соответствуют адреса опрашиваемых источников информации) должен быть подан сигнал включения на время

3,3 с. При невыполнении данного условия X,

Х,„+Х,, 0

15

20

и после истечения времени 3,3 с исполнительный орган должен быть отключен. Данному ис- полнительному органу поставлен в со- 5 ответствие триггер в блоке исполнительных элементов , включение которого осуществляется по одному адресу (у ), а отключение - по другому (у ) (фрагмент (граф-схемы управления рассматри- ваемым исполнительным органом представлен на фиг, 7). В условных вершинах соответствующим командам ввода и логической обработки осуществляется проверка состояний источников информации, в том числе и состояние триггера-фиксатора Х путем сравнения признака с состоянием источника информации. В операторных вершинах осуществляется управление данным триггером по командам вывода и выполнение временной команды t (3,3; 2), что определяет реализацию временной задержки на 3,3 с с использовани-j, ем второго слова-ячейки ОЗУ 7. Б блоках С1 и С2 осуществляется решение задач управления другими исполнительными органами. В соответствии с этим в случае выполнения логического условия реализуется временная команда, после которой проверяется факт окончания временной задержки.

Очевидно в первом цикле и до момента окончания временной задержки и происходит выполнение операто- - ра у. и включение дарного исполнительного органа. На некотором цикле после окончания временной команды Х становится равным 1 и производится выполнение оператора у,д: 1, т.е. отключение данного исполнительного органа.

В случае невыполнения логического условия на включение временной за- держки производится также выполнение оператора у : 1. Вьшолнение временной команды при этом осуществляется следующим образом (фиг. 8).

30

40

45

временной задержки, равной 3,3 с, 10 и соответственно двоичный код дан ной временной задержки, записанный в а-1.., в разрядах блока 2 памяти, 1010.

Пусть в момент начала счета времени по данной временной задержке (во второй ячейке ОЗУ записан 0) в рассматриваемых разрядах счетчика зафиксирован код 0010. Тогда сумма- код момента окончания временной задержки 1010 + 0010 1100 записьша- ется в ячейку ОЗУ (вторая ячейка). В-последующих циклах работы производится сравнение кода окончания временной задержки с кодом текущего вре мени со счетчика времени. Очевидно, сравнение произойдет через 10 циклов изменения состояния младшего разряда счетчика 4, после чего запишется единица в триггере (фиксаторе) 14, который будет опрошен по команде ввода и логической обработки.

Обращение к запоминающему устройству в системах программного управления происходит за цикл работы не по всем адресам, а в соответствии с выполнением логических условий по командам ввода и логической обработки, осуществляющим условный переход по результатам опроса источников информации, например, при реализации бинарных программ, что приводит к переменному циклу программы.

Значение разности максимального и минимального времени цикла зависит от числа реализуемых команд и может Меняться в достаточно широких пределах.

В прототипе код начального уста- нова и код шага отсчета определены из условия, что изменение кода промежуточных результатов отсчета временных интервалов должно осуществляться не более одного раза за цикл программ.

Время между появлением одной и той же команды в соседних циклах может

меняться в таких пределах, что про- Пусть в соответствии с необходимой о изойдет изменение промежуточного результата отсчета временного интервала более, чем один раз в течение одного цикла, а это приведет к недопустимо высоким погрешностям. 55 Пусть условие формирования временной команды определяется функцией

пи Т V, .(всегда некоторая х; 1).

точностью реализации временных задержек число разрядов счетчика, связанных с сумматором, число разрядов сумматоров и ОЗУ 7 равно четырем (в - Зр, в - 2р, в - 1р, Вр), а период изменения младшего (в - Зр)-го разряда счетчика составляет ,33 с Тогда число циклов изменения младще- го разряда счетчика для реализации

V, X, .(всегда некоторая х;

В случае, если для представления в

15

0

5 ,

0

0

5

временной задержки, равной 3,3 с, 10 и соответственно двоичный код данной временной задержки, записанный в а-1.., в разрядах блока 2 памяти, 1010.

Пусть в момент начала счета времени по данной временной задержке (во второй ячейке ОЗУ записан 0) в рассматриваемых разрядах счетчика зафиксирован код 0010. Тогда сумма- код момента окончания временной задержки 1010 + 0010 1100 записьша- ется в ячейку ОЗУ (вторая ячейка). В-последующих циклах работы производится сравнение кода окончания временной задержки с кодом текущего времени со счетчика времени. Очевидно, сравнение произойдет через 10 циклов изменения состояния младшего разряда счетчика 4, после чего запишется единица в триггере (фиксаторе) 14, который будет опрошен по команде ввода и логической обработки.

Обращение к запоминающему устройству в системах программного управления происходит за цикл работы не по всем адресам, а в соответствии с выполнением логических условий по командам ввода и логической обработки, осуществляющим условный переход по результатам опроса источников информации, например, при реализации бинарных программ, что приводит к переменному циклу программы.

Значение разности максимального и минимального времени цикла зависит от числа реализуемых команд и может Меняться в достаточно широких пределах.

В прототипе код начального уста- нова и код шага отсчета определены из условия, что изменение кода промежуточных результатов отсчета временных интервалов должно осуществляться не более одного раза за цикл программ.

Время между появлением одной и той же команды в соседних циклах может

пи V, .(всегда некоторая х; 1).

V, X, .(всегда некоторая х;

случае, если для представления в

программе одной временной требуется одна команда, число реализуемых команд может меняться от 2-х до п.

В соответствии с этим меняется и время цикла.

Например, если и t - время выполнения одной команды,

, ПР X,X2 ...

, tu,4mm-2 J

у. I при X ,

и код промежуточного отсчета временного интервала в последнем случае изменится 5 раз в течение одного .цикла программы вместо одного раза, в результате чего время задержки уменьшится в 5 раз по сравнению с требуемым.

Формула изобретения

1, Устройство для временного программного управления, содержащее блок синхронизации, блок управления, блок памяти, блок оперативной памяти, счетчик времени, группу первых элементов И, два элемента НЕ, элемент ИЛИ, шесть элементов И, отличающееся тем, что, с целью повышения точности отсчета временных интервалов при переменном цикле программы и надежности устройства, введены блок передачи информации, блок сбора информации, блок исполнительных элементов, сумматор, регистр, группа элементов ЭКВИВАЛЕНТНОСТЬ, две группы элементов НЕ, триггер, формирователь импульсов, элемент ИЛИ, элемент И, причем первый выход блока синхронизации подключен к первому входу блока управления, второй выход - к первому входу второго элемента И, к тактовому входу регистра, к первому входу первого элемента ИЛИ, к счетному входу счетчика времени, к первому входу блока передачи информации, третий выход - к первым входам третьего и четвертого элементов И, к второму входу блока управления, а четвертый выход - к второму входу блока передачи информации и к управляющему входу блока памяти, соединенного адресными входами с первыми выходами блока управления, первыми, вторыми и третьими информационными выходами - с третьими входами блока управления, подключенного вторым выходом к второму входу второго элемента И, к второму входу третьего элемента И, к первому

входу пятого элемента И, третьим и четвертым выходами соответственно - к третьему и к четвертому входам блока передачи информации, четвертым входом - к выходу триггера, к первому входу второго элемента ИЛИ, а пятым входом - к первому выходу блока передачи информации, связанного вторым и третьими выходами с первьми входами

блока исполнительных элементов, третьими выходами и четвертым выходом - с первыми входами и вторым входом блока сбора информации, подключенного третьими входами к информационным входам устройства, а выходом - к пятому входу блока передачи информации,, соединенного пятым выходом с вторым входом блока исполнительных элементов, а шестыми входами - с вторыми и третьими информационными выходами блока памяти, подключенного вторы : и информационньти выходами к первым входам сумматора и через группу первых элементов НЕ - к входам шестого элемента И, соединенного выходом с вторым входом второго элемента ИЛИ и через второй элемент НЕ - с третьим входом третьего элемента И, с первым входом седьмого элемента И, подключенного вторым входом к третьему входу второго элемента ИЛИ, „к выходу восьмого элемента И и через третий элемент НЕ - к четвертому входу второго элемента И, а выходом - к

первым входам группы первы: с элементов И, соединенных вторыми входами с .соответствующими выходами сумматора, а выходами - с информационными входами блока оперативной памяти, подключенного адресными входами к третьим ин- форм ционным выходам блока памяти, первым управляющим входом - к выходу четвертого элемента И и к второму входу первого элемента ИЛИ, связанного выходом с вторым входом пятого элемента И, подключенного выходом к входу формирователя импульсов, соединенного выходом с вторым управляющим входом блока оперативной

памяти, подключенного выходами к информационным входам регистра, соединенного выходами через группу четвертых элементов НЕ с входами восьмого элемента И, а также с первыми входами группы элементов эквивалентность, подключенных выходами к пятым входам третьего элемента И, а вторыми входами - к вторым входам сумматора и к выходам ртарших разрядов счетчика времени, причем S-вход и R-вход RS-триггера соединены соответственно с выходом третьего элемен та И и с выходом второго элемента И, а второй вход четвертого элемента И - с выходом второго элемента ИЛИ.

2. Устройство по п. 1, отличающееся тем, что блок управ ления содержит дешифратор, накапливающий сумматор, счетчик импульсов, группу элементов И, шесть элементов И, три элемента ИЛИ, три элемента НЕ элемент эквивалентность, причем третьи входы блока управления подключены соответственно к входам дешифратора, к первому входу элемента эквивалентность, к входам первого элемента И, соединенного выходом с первым входом второго элемента И и через первый элемент НЕ с первым вхо дом третьего элемента И, подключенно го вторым входом к пятому входу блока управления, а выходом - к первому входу первого элемента ИЛИ, соеди- ненного вторым входом с выходом вто- iрого элемента И, а выходом - с вторым входом элемента эквивалентность, соединенного выходом с первым входом четвертого элемента И и через второй элемент НЕ - с первым входом пятого элемента И, подключенного вторым вхо дом ко второму входу четвертого эле10

J5

20

25

30

мента И, к первому входу шестого элемента И и к второму входу блока управления, выходом - к первым входам группы седьмых элементов И, а третьим входом через третий элемент НЕ - к второму входу шестого элемента И, а также к третьему выходу блока управления и к выходу второго элемента ИЛИ, связанного входами с первыми выходами дешифратора, подключенного вторым и третьим выходами соответственно к четвертому и к второму выходам блока управления, а вхС дами - к вторью входам группы седьмых элементов И, подключенных вьгхбдами к первым информационным входам накапливаюш;его сумматора, соединенного входом обнуле ния с входом обнуления счетчика импульсов и с первым входом блока управления, выходом переноса из старшего разряда - с счетным входом счетчика имцульсов, а входом переноса младшего разряда с выходом третьего элемента ИЛИ, подключенного первым и вторым входами к выходам четвертого и шестого элементов И, причем выходы накапливающего сумматора и счетчика импульсов являются первыми выходами блока управления, а второй вход второго элемента И - четвертым входом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программное временное устройство | 1990 |

|

SU1762298A1 |

| Устройство для контроля информационного тракта "запоминающее устройство команд-процессор | 1980 |

|

SU1005060A2 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для приема и передачи информации | 1991 |

|

SU1833871A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1246103A2 |

| Генератор псевдослучайных сигналов | 1986 |

|

SU1347166A1 |

| УСТРОЙСТВО ОБМЕНА ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1991 |

|

RU2020571C1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при- создании цифровых систем программного управления различного назначения. Цель изобретения - повьшшние точности отсчета временных интервалов при переменном цикле программы и надежности устройства. Устройство содержит блок 1 синхронизации, блок 2 (Л С .ф- - ф: Л77 источников индгорноциа

ik

43

5 1

Т2

с

/

(PU2.2

Адрес ЗУ

fPU2.3

Я

52

J-4

rf

25

ь

7йидI .

с

iig.г/

фаг. 5

С Начало J I Гг-О

С Конец J

(Риг.б

t(2,2) 1

(Ри,г.7

г/гпшшшишшшллшишшиишшишшшшшшлшш

5-J DVlJTJl-nJlJTJlJlJnJ l rL

IPui.S

| Программно-временные задатчики/Под ред | |||

| В.А | |||

| Шполянского, A.M | |||

| Курицкого | |||

| М.: Машиностроение, 1984, с | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для программного управления | 1979 |

|

SU805256A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-02-15—Публикация

1985-04-29—Подача