1

Изобретение относится к запоминающим устройствам и (МОжет быть использовано нри изготовлении и испытании матриц оиеративкой памяти.

Известны устройства для контроля матриц иaiмяти 1, 2, 3.

Одно из них, содержащее двухкоординатный самописец в качестве регистрирующего прибора, позволяет получить лищь траницу работоспособности, не давая никаких сведеНИИ об участках области неработоспособности, непосредствепно прилегающих IK границе области работоспособности 1.

Другое известное устройство для контроля матриц памяти, содержащее электроуправляемую пищущую мащинку, имеет сравнительное малое быстродействие. Кроме того, его недостатком являются и неиопользованные функциональные воз-можиости блока печати 2.

Известно та-кже устройство для контроля матриц намяти, содержащее генераторы ступенчатых напряжений, выходы одного из iOTOрых соединены соответственно с входами другого тенератора и блока управления печатью, а входы общих генераторов - с выходом злемента «И, к иервому входу которого подключен -выход триггера, входом связаниого с выходом блока управления, и блок выявления сбоев 3.

Однако у такого устройства невысокая степень автоматизации процесса контроля, которая обусловливает необходимость постоянного контроля со стороны оператора за окончанием печатания области работоспособности, что снижает надежность работы устройства.

Цель изобретения - повышение надежности работы устройства для контроля матриц памяти.

Это достигается тем, что В устройСтво введены дополнительный элемент «И, элемент задержки и два дополнительных триггера, первые входы которых подключены к выход}- элемента «НЕ, вторые входы-соответственно к выходам блока управления и элемента задержки, а выходы-к первому и второму входам дополнительного элемента «И, третий вход которого соединен с выходом элемента «И и входом элемента задержки, а выход-с входом блока упра вления печатью.

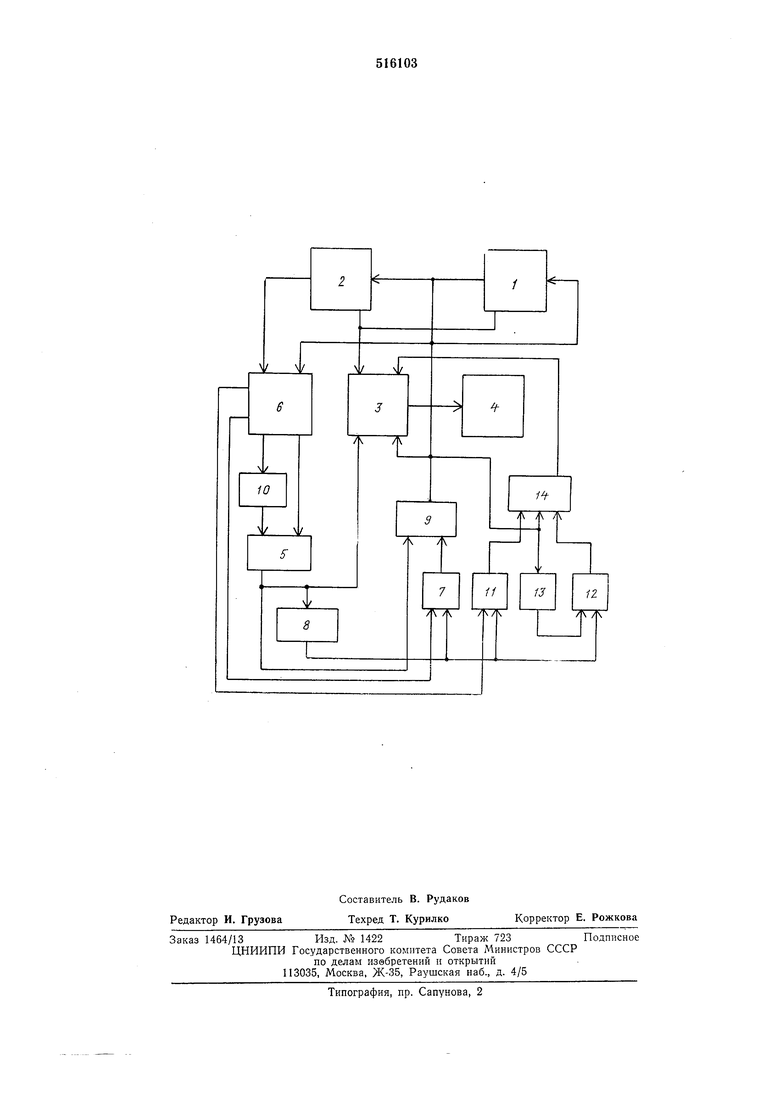

На чертел-се представлена блок-схема устройства для контроля матриц памяти.

Устройство содержит генераторы 1 и 2 CTVненчатых напряжений (генератор 1-генератор падающего ступенчатого напряжения), блок 3 управления печатью, блок 4 печатл, блок 5 выявления сбоев, блок 6 управления, триггер 7, элемент «НЕ 8, элемент «Н 9 на два входа, контролируемую матрицу 10. дополнптельпые триггеры И и 12, элемент 13 задержки и дополиительиый элемент «И 14 на три входа. Вход генератора 2 нодключен ,к выходу генератора 1, выходы генераторов 1 и 2 соединены через блок 6 унравления н контролируе.мую Матрицу 10 с входом блока 5 выявления сбоев, другие выходы генераторов объединены и через блок 3 унравления нечатью подключены к входу блока 4 печати. Выход блока 5 выявления сбоев соединен с входом блока 3 унравления нечатью и одним входом элемента «И 9 неносредственно, а через элемент «НЕ 8 - с нервыми входами триггеров 7, 11 и 12, вторые входы триггеров 7 и 11-с блоком 6 унравления. Второй вход триггера 12 подключен к выходу элемента 13 задержки, выход триггера 7 - к другому входу элемента «И 9, выход которого соединен с входами блока 3 унравления нечатью и генератора 1, третьим входом элемента «И 14 и входом элемента 13 задержки. Выходы триггеров 11 и 12 связаны с первым и вторым входами элемента «И 14, выход которой подключен к входу бло1ка управления печатью. Устройство работает следующим образо.м. Блок 6 унравления выдает по программе один или несколько циклов «запись - считывание информации по всем адресам контролируемой матрицы 10. Записываемая и считываемая информация сравнивается в блоке 5 выявления сбоев. При совнадении заннсанной и .считанной информации на выходе блока выявления сбоев появляется один сигнал, например низкий уровень, он подается па блок 3 унравления нечатью и блок 4 печати, печатает Знак, нанример «, онределяющий область работоснособности нроверяемой матрицы 10. В случае несовпадения занисанной и считанной информации на выходе блока выявления сбоев образуется другой сигнал, например высокий уровень, в результате чего блок нечати отнечатывает другой знак, нанример «-j-, определяющий неработоспособность нроверяемой матрицы. Когда сигнал несовпадения занисанной и считанной информации в контролируемом обходе всех адресов нроверяемой матрицы следует хотя бы носле одного сигнала совнадения 1Сравниваемой информации, триггеры 7 н И через элемент «НЕ 8 устанавливаются в общем случае первым сигналом совнадения в единичное состояние и на элементы «И 9 .ч 14 подаются разрешающие уровни (в данном случае высокие). После этого первый сигнал несовнадения в TOiM же обходе адресов с выхода блока выявления сбоев воздействует на вход «установка в нуль генератора 1 падающего стуненчатого напряжения, устанавливает его в исходное нулевое состоянне, действуя на вход блока 6 унравления нечатью, осуществляет возврат каретки блока 4 нечати в исходное ноложение следующей строки и нереводит триггер 12 в единичное состояние. В результате этого отпечатывается область работоспособности, ограниченная в Конде каждой .строки только одним знаком области неработоспособности проверяемой матрицы 10. Остальные siHaKH, определяющие неработоспособность проверяемой матрицы, не выводятся на .печать. В случае, когда после строки, содержащей хоть один знак работоспособности, идет строка со всеми знаками, которые определяют область неработоснособности матрицы, триггер 12 остается в единичном состоянии, так как он устанавливается в нулевое состояние сигналом знака, который соответствует совпадению записанной и считанной информации. Разрещающий уровень (в данном 1случае, высокий) с выхода триггера 12 поступает на элемент «И 14, где уже присутствует разрешающий (высокий) уровень с выхода триггера 11, н нрн поступлении на третий вход элемента «И 14 сигнала возврата каретки с выхода элемента «И 9 управляющий сигнал с выхода элемента «И 14 подается в блок 3 унравления печатью на останов блока 4 печати. Устройство, таким образом, обеспечивает автоматический останов после нанечатания области работоспособности. Участие оператора в нроцессе контроля матриц памяти сведена к минимуму и состоит лищь IB том, что оператор осуществляет только подготовку и пуск устройства для контроля. Процесс контроля матриц и останов устройства по окончанию контроля происходит автоматически. Это сунгественно повыщает надежность работы устройства. Формула изобретения Устройство для контроля матриц памяти но авт. св. N° 464019, отличающееся тем, что, с целью увеличения быстродействия и новыщения надежности работы устройства, оно содержит дополнителыный элемент «И, элемент задержки и два донолнительных триггера, нервые входы 1которых подключены к выходу элемента «НЕ, вторые входы-соответственно к выходам блока унравления и элемента задержки, а выходы - к первому и второму входам дополнительного элемента «И, третий вход которого соединен с выходом элемента «И и входом элемента задержки, а выход с входом блока унравления нечатью. Источники информации, принятые во внимание при экснертизе: 1.Электроника, 1966, № 45, стр. 41. 2.Авт. св. № 242969, М. Кл. GI1C 29/00, 1966. 3.Авт. св. № 464019, М. Кл. G НС 29/00, 1972.

/ /

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля матриц памяти | 1975 |

|

SU524227A1 |

| Устройство для контроля матриц памяти | 1972 |

|

SU464019A1 |

| Устройство для контроля запоминающих матриц | 1976 |

|

SU639024A1 |

| Устройство для контроля матриц памяти | 1975 |

|

SU597010A2 |

| Устройство для вывода информации | 1986 |

|

SU1403058A1 |

| Устройство контроля и регистрации параметров химических источников тока | 1977 |

|

SU731501A1 |

| Устройство для контроля памяти | 1978 |

|

SU706882A1 |

| Устройство для контроля блоков памяти | 1983 |

|

SU1234884A1 |

| Устройство для контроля запоминающих матриц на магнитных пленках | 1979 |

|

SU773736A1 |

| Устройство для контроля оперативных накопителей | 1983 |

|

SU1103292A1 |

Авторы

Даты

1976-05-30—Публикация

1975-03-10—Подача