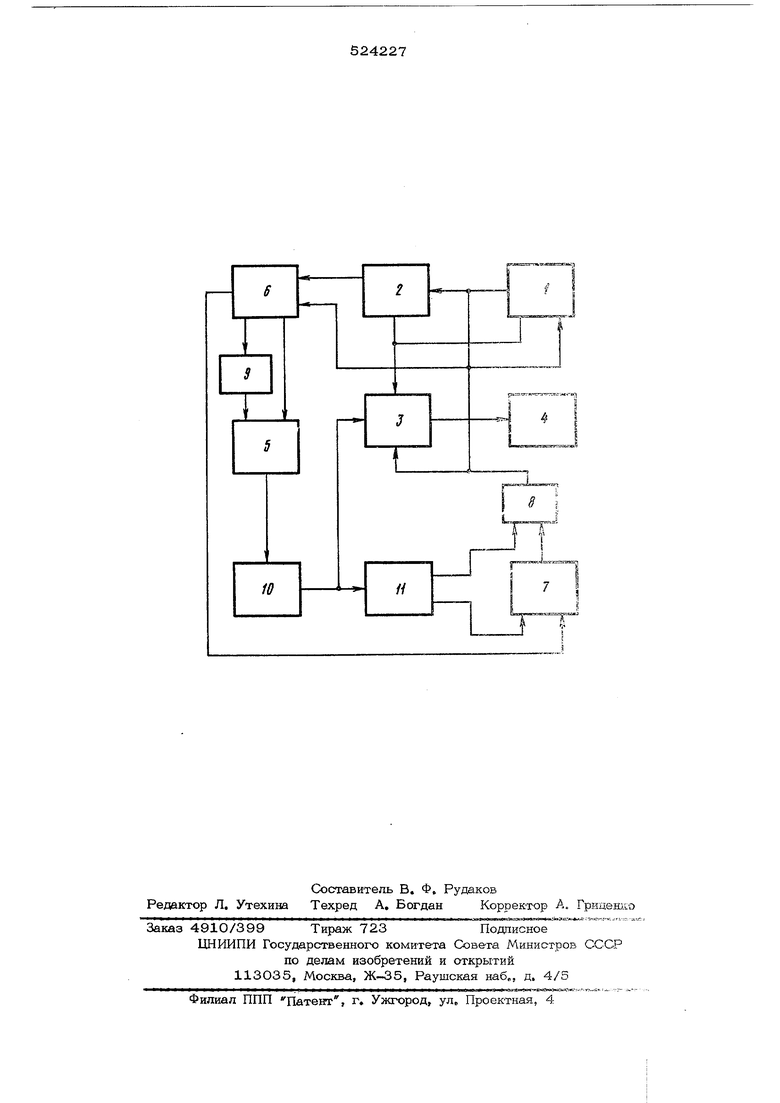

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МАТРИЦ ПАМЯТИ матрицы и осущесгвлять возврат каретки блока печати каждый раз, когда в обласги нерабогоспособносгк число сбоев, возрастая превышает число запоминающих элементов, подлежащих возможной замене. На чертеже изображена структурная схема устройства. Устройство содержит генераторы ступенчатых напряжений 1 и 2, блок 3 управления печатью, блок печати 4, блок 5 еыявле ния сбоев, блок управления 6, триггер 7, элемент И 8, контролируемую матрицу 9, счетчик 10 для подсчета числа сбоев и де- щифратор 11. Выход генератора 1 подключен ко входу ге нератора 2, Одни выходы генераторов соединены через, блок управления со вхо,аа,ми блока выявления сбоев непосредсгвенно и через контролируемую матрицу, другие через блок управления печатью - со входом блока печати. Другой выход блока управления соединен с первым входом триггера, выход которого поддлючен к первому входу элемента И, а его выход соединен с блоком управления печатью и входом генерато- ра 1, Выход блока выявления сбоев через счетчик связан с блоком управления печатью и дешифратором, один выход которого соединен со вторым входом триггера, а дру гой - со Вторым входом элемента И. Устройство работает следующим образом Блок управления б выдает по программе один или несколько циклов запись-считывание информации по всем адресам конгро- лируемой матрицы 9, Записываемая и считы ваемая информации сравниваются в блоке выявления сбоев 5. При совпадении записанной и считанной информации на выходе блока выявления сбоов появляется сигнал, который подается через счетчик на блок управления печатью, и блок печати отпечатает знак, например, , определяющий работоспособность проверяемой матрицы. Этот сигнал через де- щифратор поступает и на триггер 7, который устанавливается з единичное состояние При несовпадении записанной и считанной информации на выходе блока выявления сбоев появляются сигналы, которые подсчитываются счетчиком и поступают на вход дешифратора и в блок управления печатью, а оттуда на блок печати, В случае,когда на вход дешифратора поступает сигнал знака, определяющий число сбоев, большее чем числ элементов, подлежащих возможной замене в этой матрице, сигнал с выхода дешифратора поступает через элемент И, где на входе уже присутствует разрешающий Уровень с выхода триггера, на вход установка в нуль генератора 1 и устанавливает его в исходное (нулевое) состояние. Поступая также на вход генератора 2, этот сигнал изменяет его состояние на +1. Кроме того, поступая на вход блока управления печатью, этот сигнал осуществляет возврат каретки блока печати в исходное положение следующей строки. В результате отпечать - вается область работоспособности с прилегающей зоной неидентичности, ограниченная знаками, которые определяются числом сбоев, больщим чем число элементов, подлежащих замене. Остальные знаки, определяющие неработоспособность проверяемой матрицы, на печать не выводятся. По сравнению с известным устройством: 3 в предложенном устройстве теоретически вдвое повышено быстродействие в случае, когда один или несколько запоминающих элементов, число которых не превышает числа элементов, подлежащих возможной замене, полностью неисправны, и на ЗО-40% повышено быстродействие в случае, когда один или несколько запоминающих элементов, число которых не превышает числа элементов, подлежащих возможной замене, неидентичны, Тое. обладают худшими параметрами по сравнению с параметрами основной массы запоминающих элементов матрицы. Формула изобретения Устройство для контроля матриц памя-ти, содержащее генераторы ступенчатых напряжений, выходы одного из которых соединены соответственно со входами другого генератора и блока управления печатью, а входы обоих генераторов соединены с выходом элемента И, к первому входу которого подключен выход триггера, первый вход которого соединен с выходом блока управления, и блок выявления сбоев, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит счетчик и дешифратор, выходы которого по/ ключены ко вторым входам элемента И и риггера, а вход - ко входу блока управлеиг печатью и выходу счетчика, вход котоого поддлючен к выходу блока выявления боев. Источники, принятые во внимание при кспертизе: 1.Электроника, 1966, № 45, стр. 41. 2.Авт.св. № 242969, М кл. G 11 С 29/00, 1968. 3.Авт.св. № 464019, М. кл. G 11 С 29/ОО, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля запоминающих матриц | 1976 |

|

SU639024A1 |

| Устройство для контроля матриц памяти | 1975 |

|

SU597010A2 |

| Устройство для контроля матриц памяти | 1975 |

|

SU516103A2 |

| Устройство для контроля запоминающих матриц на магнитных пленках | 1979 |

|

SU773736A1 |

| Устройство для контроля матриц памяти | 1972 |

|

SU464019A1 |

| Устройство для редактирования информации на экране электронно-лучевой трубки | 1983 |

|

SU1091153A1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Многоканальное измерительно-регистрирующее устройство (его варианты) | 1982 |

|

SU1038807A1 |

| Устройство управления обменом | 1977 |

|

SU732842A1 |

Авторы

Даты

1976-08-05—Публикация

1975-03-11—Подача