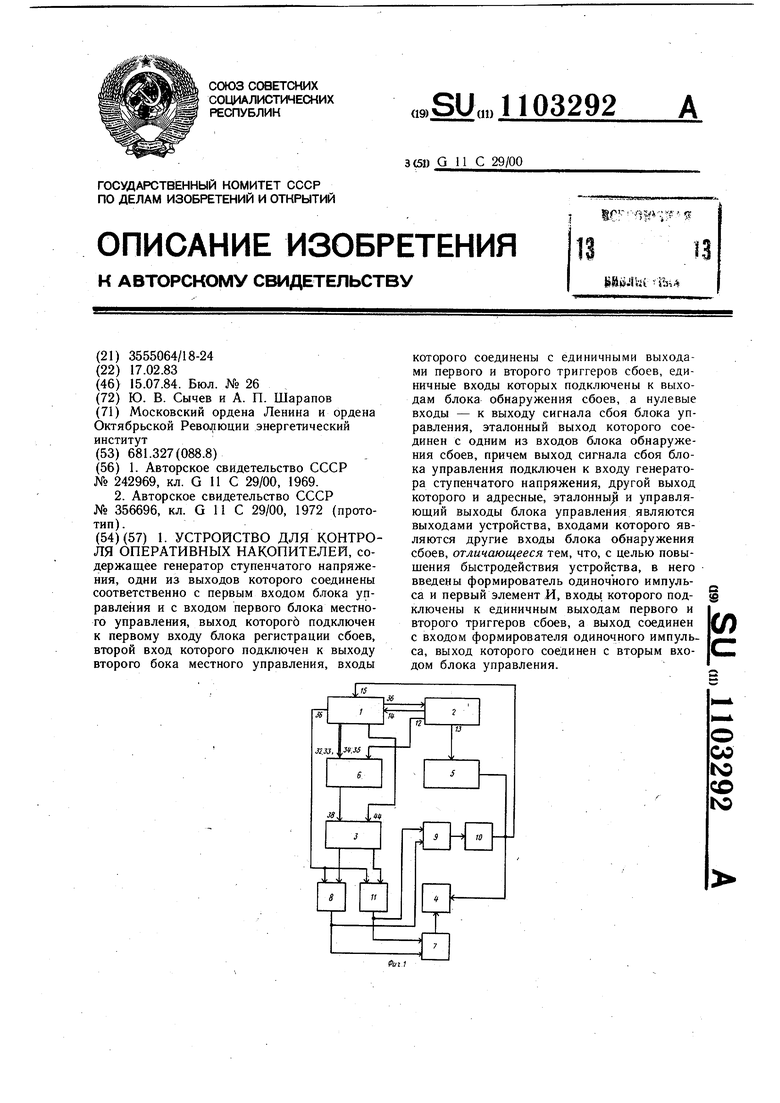

2. Устройство по п. 1, отличающееся тем, что блок управления содержит генератор тактовых импульсов, счетчики, триггеры, компаратор, элемент ИИ, элементы И НЕ и элементы И с второго по четвертый, причем первый вход второго элемента И подключен к выходу генератора тактовых импульсов, а выход - к счетному входу первого счетчика, выходы которого соединены с одним из входов компаратора, другие входы которого подключены к выходам второго счетчика, счетный вход которого соединен с выходом третьего элемента И, а выход переполнения - с первым входом четвертого элемента И и счетным входом первого триггера, выход которого подключен к второму входу четвертого элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого подкючен к счетному входу второго триггера, инверсный выход которого соединен с вторым входом первого элемента И, а вход сброса - с входами сброса счетчиков, третьего и четвертого триггеров, счетный вход третьего триггера подключен к выходу переполнения первого счетчика и первому входу тр(етьего элемента И, второй вход которого соединен с инверсным выходрм третьего триггера, выход первого элемента И-НЕ подключен к первому входу второго элемента И-НЕ, второй вход которого соединен с прямым выходом четверг того триггера, инверсный выход которого подключен к первому входу третьего элемента И-НЕ, второй вход которого и входы Первого элемента И-НЕ соединены с выходами компаратора, счетный вход четвертого триггера подключен к выходу переполнения второго счетчика, выходы второго и третьего элементов И-НЕ соединены с входами четвертого элемента И-НЕ, вход сброса первого триггера и второй вход элемента ИЛИ являются первым н вторым входами блока, выходом сигнала сбоя которого является инверсный выход второго триггера, выходы первого счетчика являются адресными выходами блока, управляющим и эталонным выходами которого являются соответственно прямой выход третьего триггера и выход четвертого элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1987 |

|

SU1540025A1 |

| Устройство для контроля аналогового сигнала | 1990 |

|

SU1797097A1 |

| Устройство для опроса датчиков | 1984 |

|

SU1238089A2 |

| Устройство для контроля блока памяти | 1981 |

|

SU1043753A2 |

| Вычислительное устройство для термографического анализа кислорода в жидкой стали | 1980 |

|

SU883919A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Устройство приоритета | 1979 |

|

SU805313A1 |

| Устройство для контроля времени выполнения программ | 1982 |

|

SU1059575A1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛОВ ПРЕРЫВАНИЯ ПРИ ОТЛАДКЕ ПРОГРАММ | 1992 |

|

RU2042192C1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОПЕРАТИВНЫХ НАКОПИТЕЛЕЙ, содержащее генератор ступенчатого напряжения, одни из выходов которого соединены соответственно с первым входом блока управления и с входом первого блока местного управления, выход которогй подключен к первому входу блока регистрации сбоев, второй вход которого подключен к выходу второго бока местного управления, входы которого соединены с единичными выходами первого и второго триггеров сбоев, единичные входы которых подключены к выходам блока обнаружения сбоев, а нулевые входы - к выходу сигнала сбоя блока управления, эталонный выход которого соединен с одним из входов блока обнаружения сбоев, причем выход сигнала сбоя блока управления подключен к входу генератора ступенчатого напряжения, другой выход которого и адресные, эталонны и управляющий выходы блока управления являются выходами устройства, входами которого являются другие входы блока обнаружения сбоев, отличающееся тем, что, с целью повыщения быстродействия устройства, в него введены формирователь одиночного импульса и первый элемент И, входы, которого подключены к единичным выходам первого и (Л второго триггеров сбоев, а выход соединен с входом формирователя одиночного импульса, выход которого соединен с вторым входом блока управления. СО 1C ;о to

1

Изобретение относится к вычислительной технике и может быть использовано при исследовании оперативных накопителей,для ускорения определения области устойчивой работы оперативного накопителя.Известно устройство для контроля ореративных накопителей, содержащее блок управления оперативным накопителем, генератор ступенчатых напряжений, печатающее устройство, устройство, управления печатью 1.

Однако данное устройство не позволяет регистрировать в областях неработоспособности числа сбоев типа «Ложная единица и «Ложный нуль.

Наиболее близким к изобретению является устройство для контроля оперативных накопителей, содержащее генератор ступечатных напряжений, блок управления блок выявления сбоев, блок печати (как минимум с двухцветной печатью), блок управления печатью, счетчик числа сбоев, блок управления цветом печати, элемент ИЛИ и триггеры, один выход генератора ступен11атых напряжений соединен с блоком управления, другой - с исследуемым оперативным накопителем, а третий - с блоком управления печатью, выход которого соединен с одним входом блока печати, к другому входу которого подключен выход блока управления символами, к двум входам которого подключены единичные выходы триггеров сбоев, единичные входы которых соединены с выходами блока выявления сбоев, а нулевые входы триггеров объединены и соединены с одним выходом блока управления, другой выход которого соединен с одним из входов исследуемого оперативного накопителя, выход которого соединен-с одним из входов блока выявления сбоев, к второму входу которого подключен третий выход блока управления, четвертый выход которого подключен к входу генератора ступенчатых напряжений./Это устройство позволяет регистрировать в областях иеработоспособности число-сбоев типа «Ложная единица и «Ложный нуль, что повышает точность контроля и позволяет более полно исследовать накопитель 2.

Недостатком данного устройства является невысокая, скорость определения области неработоспособности из-за того, что при возникновении сбоев разного типа не осуществляется переход к следующим значениям (или значению) питающих напряжений, а при возникновении такой ситуации не имеет смысла продолжать испытания при данных сочетаниях питающих напряжений.

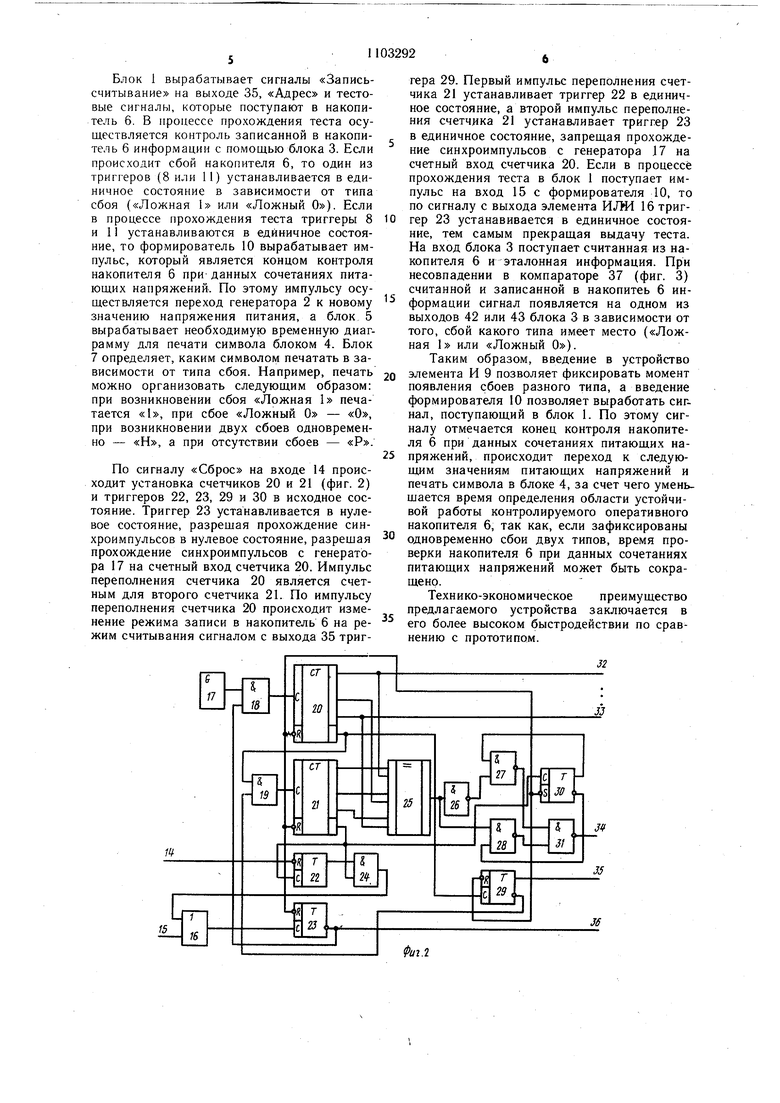

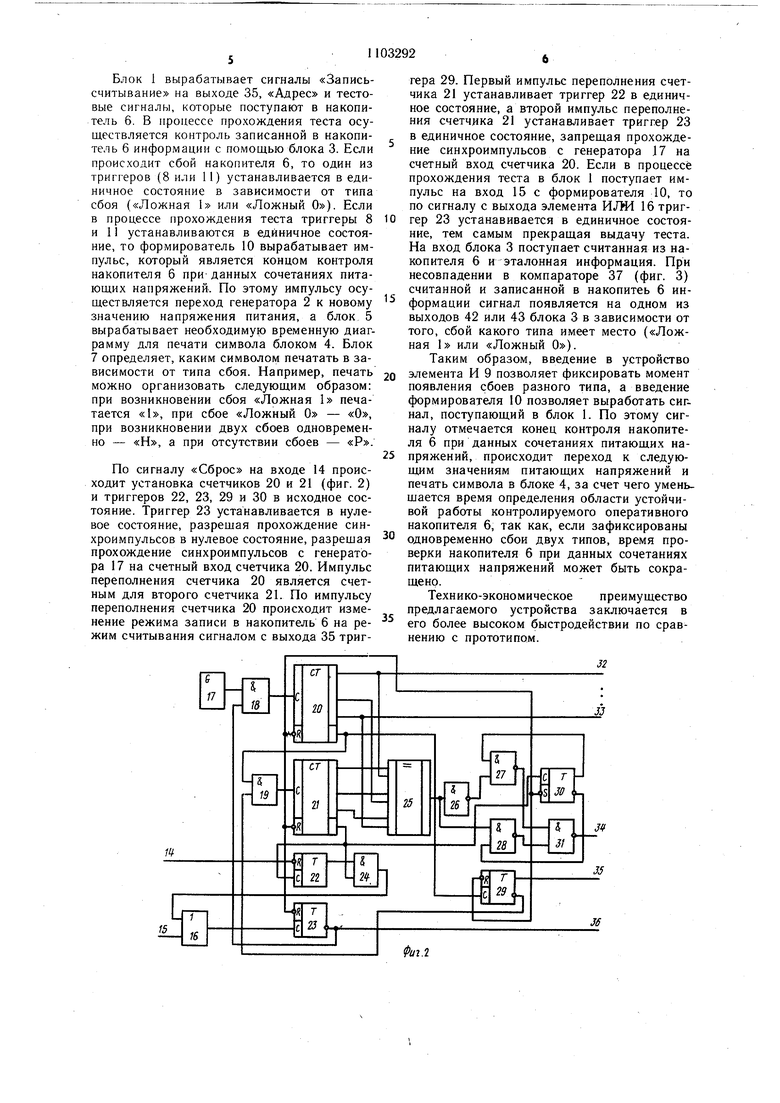

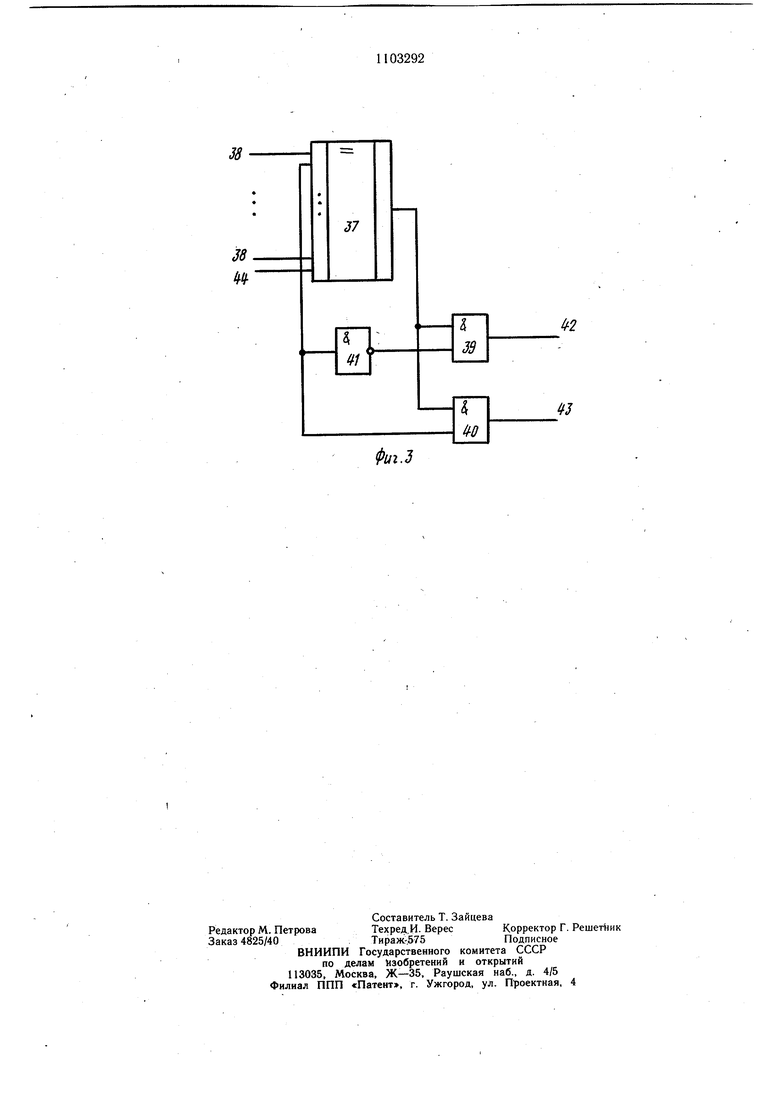

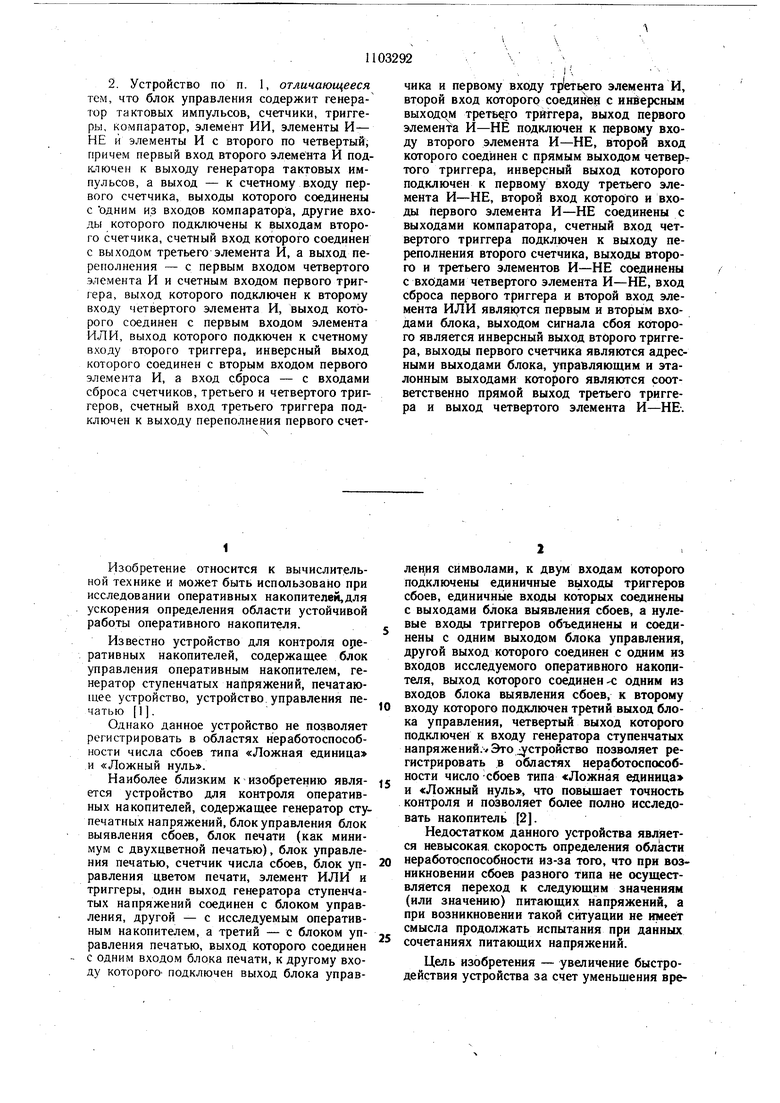

Цель изобретения - увеличение быстродействия устройства за счет уменьщения времени определения области устойчивой работы при исследовании оперативного накопителя. Поставленная цель достигается тем, что в устройство для контроля оперативных накопителей, содержащее генератор ступенчатого напряжения, одни из выходов которого соединены соответственно с первым входом блока управления и с входом первого блока местного управления, выход которого подключен к первому входу блока регистрации сбоев, второй вход которого подключен к выходу второго блока местного управления, входы которого соединены с единичными выходами первого и второго триггеров сбоев, единичные входы которых подключены к выходам блока обнаружения сбоев, а нулевые входы - к выходу сигнала сбоя блока управления, эталонный вход которого соединен с одним из входов блока обнаружения сбоев, причем выход сигналу сбоя блока управления подключен к входу генератора ступенчатого напряжения, другой выход которого и адресные, эталонный и управляющий выходы блока управления являются выходами устройства, входами которого являются другие входы блока обнаружения сбоев, введены формирователь одиночного импульса и первый элемент И, входы которого подключены к единичным выходам первого и второго триггеров сбоев, а выход соединен с входом формирователя одиночного импульса, выход которого соедивен с вторым входом бока управления. Блок управления содержит генератор тактовых импульсов, счетчики, триггеры, компаратор, элемент ИЛИ, элементы И-НЕ и элементы И с второго по четвертый, причем первый вход второго элемента И подключен к выходу генератора тактовых импульсов, а выход - к счетному входу первого счетчика, выходы которого соединены с одним из входов компаратора, другие входы которого подключены к выходам второго счетчика, счетный вход которого соединен с выходом третьего элемента И, а выход переполнения - с первым входом четвертого элемента И и счетным входом первого триггера, выход которого подключен к второму входу четвертого элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого подключен к счетному вхоДу второго триггера, инверсный выход которого соединен с вторым входом первого элемента И, авход сброса - с входами сброса счетчиков, третьего и четвертого триггеров, счетный вход третьего триггера подключен к выходу переполнения первого счетчика и первому входу третьего элемента И, второй вход которого соединен с инверсным выходом третьего триггера, выход первого эл«йента И-НЕ подключен к первому входу второго элемента И-НЕ, второй вход кагорого соединен с прямым выходом четвертого триггера, инверсный выход которого, подключен к первому входу третьего элемента И-НЕ, второй вход которого и входы первого элемента И-НЕ соединены с выходами компаратора, счетный вход четвертого триггера подключен к выходу переполнения второго счетчика, выходы второго и третьего элементов И-НЕ соединены с входами четвертого элемента И-НЕ, вход сброса первого триггера и второй вход элемента ИЛИ являются первым и вторым входами блока, выходом сигнала сбоя которого явяется инверсный выход второго триггера, выходы первого счетчика являются адресными выходами блока, управляющим и эталонным выходами которого являются соответственно прямой выход третьего триггера и выход четвертого элемента И-НЕ. На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - функциональная схема блока обнаружения сбоев, Устройство содержит (фиг., 1) блок 1 управления, генератор 2 ступенчатого напряжения, блок 3 обнаружения сбоев, блок 4 регистрации сбоев, реализованный на устройстве печати символов, первый блок 5 местного управления, предназначенный для управления печатью, контролируемый оперативный накопитель 6. Устройство содержит также второй блок 7 местного управления, предназначенный для управления выбором символов, первый триггер 8 сбоев, первый элемент И 9, формирователе 10 одиночного импульса и второй триггер 11 сбоев. На фиг. 1 обозначены выходы 12 и 13генератора 2 ступенчатого напряжения, первый 14 и второй 15 входы блока 1 управления. Блок I управления содержит (фиг. 2) элемент ИЛИ 16, генератор 17 тактовых импульсов, второй 18 и третий 19 элементы И, первый 20 и второй 21 счетчики, первый 22 и второй 23 триггеры, четвертый элемент И 24, компаратор 25, элементы И-НЕ 26- 28 с первого по третий, третий 29 и четвертый 30 триггеры и четвертый элемент И-НЕ 31. На фиг. 2 обозначены адресные 32 и 33, эталонный 34, управляющий 35 выходы и выход 36 сигнала сбоя с блока управления. Блок 3 обнаружения ощибок содержит ((})иг. 3) компаратор 37 с информационными входами 38, элементы И 39 и 40 и элемент И-НЕ 41. На фиг. 3 обозначены выходы 42 и 43 блока 3 обнаружения ощибок, информационный вход 44. Устройство работает следующим образом. Генератор 2 (фиг. 1) изменяет значения напряжения питания, подаваемого на контролируемый накопитель 6. Для каждого значения напряжения питания с помощью теста, например «бегающая 1 и О, вырабатываемого блоком 1, оценивается работоспособность накопителя 6.

Блок 1 вырабатывает сигналы «Записьсчитывание на выходе 35, «Адрес и тестовые сигналы, которые поступают в накопитель 6. В процессе прохождения теста осуществляется контроль записанной в накопитель 6 информации с помощью блока 3. Если происходит сбой накопителя б, то один из триггеров (8 или 11) устанавливается в единичное состояние в зависимости от типа сбоя («Ложная 1 или «Ложный О). Если в процессе прохождения теста триггеры 8 и 11 устанавливаются в единичное состояние, то формирователь 10 вырабатывает импульс, который является концом контроля накопителя 6 при данных сочетаниях питающих напряжений. По этому импульсу осуществляется переход генератора 2 к новому значению напряжения питания, а блок 5 вырабатывает необходимую временную диаграмму для печати символа блоком 4. Блок 7 определяет, каким символом печатать в зависимости от типа сбоя. Например, печать можно организовать следующим образом: при возникновении сбоя «Ложная 1 печатается «1, при сбое «Ложный О - «О, при возникновении двух сбоев одновременно - «Н, а при отсутствии сбоев - «Р.

По сигналу «Сброс на входе 14 происходит установка счетчиков 20 и 21 (фиг. 2) и триггеров 22, 23, 29 и 30 в исходное состояние. Триггер 23 устанавливается в нулевое состояние, разрещая прохождение синхроимпульсов в нулевое состояние, разрешая прохождение синхроимпульсов с генератора 17 на счетный вход счетчика 20. Импульс переполнения счетчика 20 является счетным для второго счетчика 21. По импульсу переполнения счетчика 20 происходит изменение режима записи в накопитель 6 на режим считывания сигналом с выхода 35 триггера 29. Первый импульс переполнения счетчика 21 устанавливает триггер 22 в единичное состояние, а второй импульс переполнения счетчика 21 устанавливает триггер 23 в единичное состояние, запрещая прохождение синхроимпульсов с генератора 7 на счетный вход счетчика 20. Если в процессе прохождения теста в блок 1 поступает импульс на вход 15с формирователя 10, то по сигналу с выхода элемента ИЛИ 16 триггер 23 устанавивается в единичное состояние, тем самым прекращая выдачу теста. На вход блока 3 поступает считанная из накопителя 6 и эталонная информация. При несовпадении в компараторе 37 (фиг. 3) считанной и записанной в накопитеь 6 информации сигнал появляется на одном из выходов 42 или 43 блока 3 в зависимости от того, сбой какого типа имеет место («Ложная 1 или «Ложный О).

Таким образом, введение в устройство элемента И 9 позволяет фиксировать момент появления сбоев разного типа, а введение формирователя 10 позволяет выработать сигнал, поступающий в блок 1. По этому сигналу отмечается конец контроля накопителя 6 при данных сочетаниях питающи.х напряжений, происходит переход к следующим значениям питающих напряжений и печать символа в блоке 4, за счет чего уменьшается время определения области устойчивой работы контролируемого оперативного накопителя 6, так как, если зафиксированы одновременно сбои двух типов, время проверки накопителя 6 при данных сочетаниях питающих напряжений может быть сокращено.

Технико-экономическое преимущество предлагаемого устройства заключается в его более высоком быстродействии по сравнению с прототипом.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для РЕГИСТРАЦИИ ОБЛАСТЕЙ УСТОЙЧИВОЙ РАБОТЫ ФЕРРИТОВЫХ МАТРИЦ | 0 |

|

SU242969A1 |

| Солесос | 1922 |

|

SU29A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УСТРОЙСТВО для КОНТРОЛЯ ЗАПОМИНАЮЩИХ МАТРИЦ | 0 |

|

SU356696A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1984-07-15—Публикация

1983-02-17—Подача