1

Изобретение относиягсй к измерительной технике и может быть использовано при преобразованиях активной мощности Б код, а также при измерениях мощности.

, Известен преобразователь активной мош- ностн в код с двухтактным интегрированием, состоящий из множительного устройства, клк

MeftjHHTerparopa, устройства сравнени$1, опредепителя периода, генератора счетных им- Ю пульсов, счетчика результата и источника опорного напряжения, в котором входы по напрвжению и току соединены с соответствук 1 шнмн входами множительного устройства, выход которого п6дклю 1ен к входу ключа, |5 Другой вход которого соединен с выходом источника опорного напряжения; вход управления подключен к выходу определителя периода, а выход ключа связан с ьходом интегратора, выход которого соединен с входом 20 устройства сравнения, которое по вькоду-- подключено к входу второго ключа, другой вход которого соединен с выходом определителя периода, а третий - с выходом генератора счетньк импульсов,i 25

Недостаток известного устройства - невысокая точность преобразования активной мсшшости в код.

Цель изобретения - устранение этого не 6 достатка,

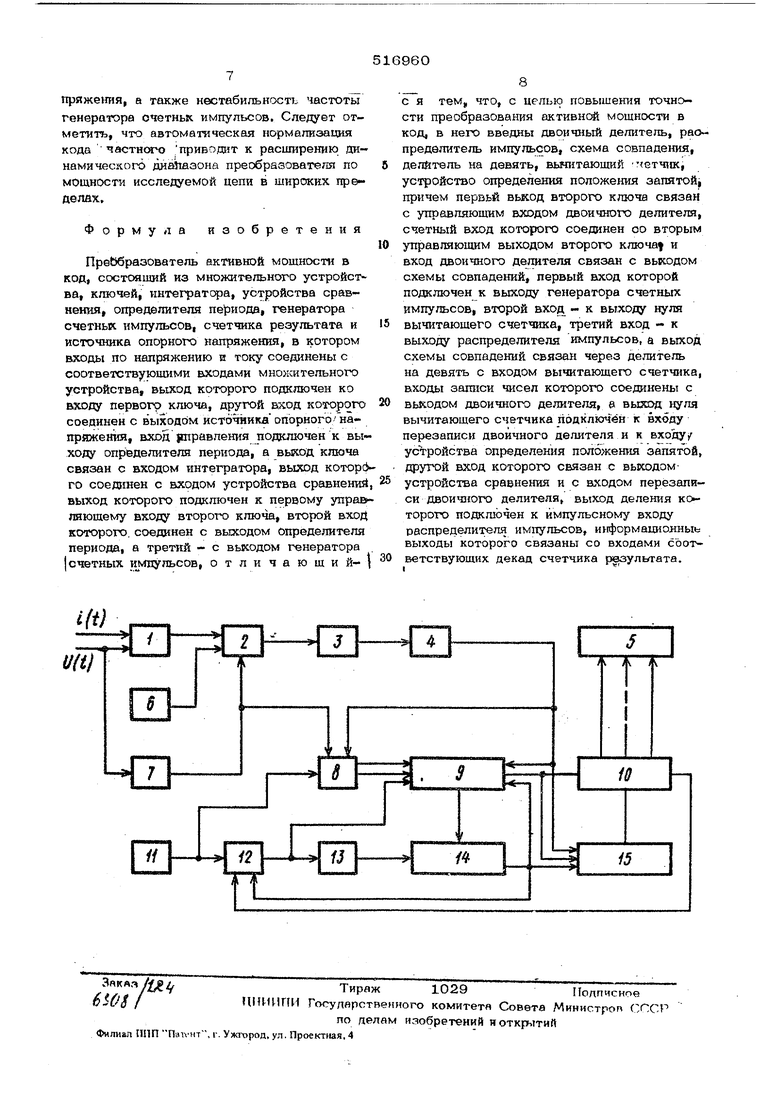

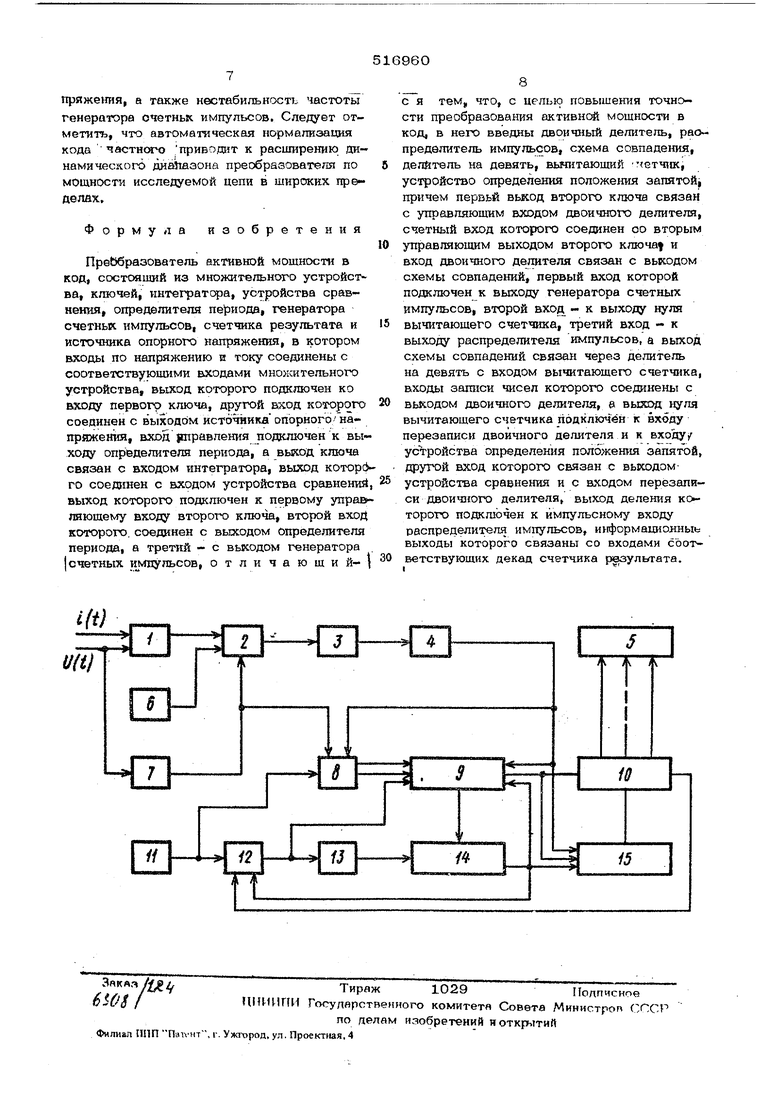

Поставленная цель достигается тем что в преобразователь введены двоичньй делитель, рвспрвде-«нтель импульсов, схема совпадения, делитель на девять, вычитающий счетчик, устройство определения положения запятой, причем выход ключа связац с упра&ляющим входом двоичного делителя, счетный вход которого соединен со вторьм выходом второго ключа и с выходом схемы совпадений, первый вход которой подключен к аько ду генератора счетных импульсов, второй вход - к выюду нуля вычитающего счетчика, третий вход - к выходу распределителя импульса, а выход схемы совпадения связан через делитель на девять с входом вычитаю.щего счетчика, входы записи числа которого соединены с выходом двоичного детштеля, а вькод нуля вычитаюгаего счетчика подклочен к входу перезаписи двоичного делителя и к входу устройства определения положения аяпТОЙ, другой вход которого связан с выходом устройства сравнения и с входом перезапис двоичного делителя, выход делентш которого подключен к импульсному входу распредели теля импульсов,-информационные выходы которого связаны с входами сост)вётствующих декад счетчика результата. На чертеже представлена блок- хема пре обраэователя активной мощности в код. Устройство состоит из множительного уст ройства 1, двухполюсного ключа 2, интеграт ра 3, устройства сравнения 4, счетчика речзультата 5, источника 6 опорного напряжения, определителя периода 7, ключа 8, двоичного делителя 9, распределителя импульЬов 10, генератора счетных импульсов 11, схемы совпадения 12, делителя на девять 13 вычитающего счетчика 14, устройства определения положения запятой 15. ВходньЕ цепи по току и напряжению подключены к входу множительного устройства 1, вькод которого подключен к входу двухполюсного ключа 2, вход управления которого соеш1нен с вьходом определителя периода 7 и входом управления ключа 8, а другой вход ключа 2 соединен с вьосодом источника опорного напряжетгя 6,,Вход определителя периода 7 соединен с входом по напряжению множительного устройства 1, Вькод двухполюсного ключа 2 соединен с входом интегратора 3, выход которого связан с входом устройства сравнения 4, Вьгход последнего соединен с вторьм. управляю щим входом ключа 8, с входом двоичного делителя 9 и с входом устройства определения положе1гая запятой 15. Сигнальньй вход, ключа 8 соединен с вькодом генераторасчетных импульсов 11 и сигнальным {перBbw) входом схемы совпадения 12, Второй управляющий вход схемы совпадения 12 соединен с выходом нуля вычитающего счетчика 14 и с входами двоичного делителя 9 и устройства 15. а третий управляющий вход соединен с выходом распределителя 1О, Выход схемы 12 соединен с входами двоичного делителя 9 и через делитель на девять 13 с входом счетчика 14, другой вход которого соединен с выходом перезаписи двоичного делителя 9. Выход двоичного делителя 9 соединен с входами устройства 15 и распределителя импульсов Ю выходы которого соединены с входами счетчика 5. Цифровой эквивалент ак-ивчой мощности НС сле;1уемой цепи определяется по выражению.V. 1х U(t )1 (t )dt гед К - коэффициент аналого-цифрового преобразователя мощности} Т - период основной гармоники тока L ( t ) и напряжения и (t ). Преобразователь работает следующим обом. Б первом такте интегрирования пряжение с выхода перемножителя подаетчерез ключ 2 на вход интегратора 3, К нцу первого такта напряжение на выходе тегратора вых -..пт ,п ;; 1р И - число периодов интerpиpoвaния Т - постоянная времени интегратора; и , Л - действующие значения напряжения и тока к-ой гармоники} Ф - угол сдвига между ними} Р - активная мощность. Число счетньк импульсов, пQcтyпaющиk вход счетчика управления двоичного делия 9 от генератора 11 в течение первого та интегрирования пТ N. (ш) где T - период следования счетньпс импульсов. Во втором такте интегрирования сигнал ыхода определителя 7 разрешает подачу ицательного напряжения источника 6 ез ключ 2 на вход интегратора 3. Прос интегрировании продолжается до моменравенства выходного напряжения интеграа нулю, который фиксируется устройством внения 4, При этом вьшолняется равенство Т, 2 т о Число импульсов, поступивших с выхода ча 8 на вход приемного счетчика двоичо делителя 9, равно (V ) N -S 1ц з (IV) с учетом (П, Ш, V ) получим и. N { const з (VI) видно, что цифровой эквивалент ности пропорционален члстному деле-J и не зависит эт ста511;т1,нсх:ги частоты с«1етньк импульсов, необходима лишь кратковременная стабильность на время преобразования. По истечении второго такта интетрирования на выходе двоичного делителя 9 nonyHa ем число импульсов К, , равное целочислен которые ному значению отношения через распределитель 10 поступают на вход первой декады счетчика резуттьтата 5. Величина образцового напряжения и и бирается из условия обеспечения целочисленного значения отношения Q 2 Q при коэ фициенте мощности исследуемой цепи, равном единице. В приемном счетчике фиксируется остаток Aj Депения . Сигналом с выхода устройства срав нения 4 остаток Aj записьвается в вычитающий (Летчик 14. Если ), то схема 12 открывается сигналом разрешения с выхода нудя счетчика. Сигнал с вькода устрой ства 4 поступае- также на вход устройства 15, которое поделзт импульс на вход управЛенин распределителя 10 при К i О, подготавливая его к передаче импульсов с вы хода делителя 9 на вход второй декады (летчика результата. Импульсы с выхода генератора 11 через открытую схему 12 проходят на вход приемного счетчика двоичного делителя 9 и через делитель на девять 13 - на вход вычитающего счетчика 14. К. моменту обнулеьшя счетчика 14 на вход приемного счетчика двоичного делителя 9 поступает девять А импульсов, которьЕ суммируются с Д импульсов в двоичном делителе 9. Во второй декаде i счетчика 5 фтсс1фуется целочисленное знагче1ше отношения а в приемном счетчике двоичного делителя получа)г емкод остатка А 10A.j - , , который сигналом с вы:;ода нуля вычитающего счетчика 14 переписывается в этот же счетчик 14. Если А 0 то схема 12 закрывается и на этом процесс вычисления прекращается. Если А„ О, то устройство 15 по сигналу с выхода нуля счетчика 14 подает на вход управления распределителя 10 второй HMiiyjTbc, который подготавливает его к передаче импульсов с вькода дешгтедя 9 в третью декаду ; счетчика 5. Дальше процесс вычисления протекает аналогично вышеописанному. При заполнении всех разрядов счетчика 5 сигнал с выхода распределителя 10 закрывает схему 12 совпамО}гая. В счетчике результатов 5 оказывается зафиксированным код числа, пропорционального значению активной мощности. Если коэффициент мощности исследуемой цепи не равен единице, то отношение уменьшается во столько раз, во сколько раз коэффициент мощности отличается от единицы При этом возможно появление ошибок- вследствие того, что старшие разрйды счеч чика 5 не принимают участия в представлении результата отношения. Для обеспечения представления результата отношения ,.2 всеми разрядами реализован алгоритм деления с плавающей запятой. Если, например, коэффициент мошлости равен 0,01, то с окончанием второго такта интегрирования на выходе двоичного 9 получаем К- О импульсов. В этом случае сигнал с выхода устройства сравнения 4 запоминается в устройстве 15, что приводит к сдвигу запятой в счетчике 5 на один десятьй разряд в сторону старших разрядов. Состояние распределителя 10 при этом не изменяется Этим же сигналом и с приемного счетчика двоичного делители19 в вычитающий счетчшс 14 записывается код -шсла N. С умножением N на 9 величина целочис- , 10-N., ленного значения отношепил К -fT игнал с выхода нуля вычитающего счетчика 14 переписьтает из двоичнэго делителя 9 код числа 10 No в счетчик 14. Дальше N „ умножается на 9 it заноситчисло 10 ся в делитель 9, При этом ип его выходе получается целочисленное значение отношения К„ ЛОО N J которое через распреде- литель Ю заносится в старшую декаду счетчика 5. Дальше процесс вычисления от ощ&Ш1Я происходит аналогично описанному при коэффициенте мошиэсти, равном едитще. ри представлении результата частного семи декада;чга в счетчике 5 процесс вычисления прекращается. Таким образом, путем автоматической обеспе- орма71изашп1 кода частного ено устранение потери точности в младих разрядах при liSMciiemiH коэ|)4|нииснта ошности исследуемой цепи в широких преелах. На результат преэбразэв.ишя но влият погрешность формиропатояя опорного ип

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1978 |

|

SU746511A1 |

| Автоматический цифровой измеритель коэффициента гармоник | 1980 |

|

SU911363A1 |

| Одноканальное устройство для управленияВЕНТильНыМ пРЕОбРАзОВАТЕлЕМ | 1979 |

|

SU839007A1 |

| Цифровой фазометр | 1975 |

|

SU653579A1 |

| Цифровой низкочастотный частотомер | 1975 |

|

SU636553A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧАСТОТЫ | 1970 |

|

SU264457A1 |

| Устройство импульсного регулирования мощности переменного тока | 1983 |

|

SU1100693A1 |

| Устройство для записи параметров движения | 1984 |

|

SU1273811A1 |

| Цифроаналоговый измеритель средней частоты | 1991 |

|

SU1775678A1 |

| Устройство для измерения амплитудно- фАзОВыХ чАСТОТНыХ ХАРАКТЕРиСТиК | 1979 |

|

SU849151A1 |

Авторы

Даты

1976-06-05—Публикация

1974-08-19—Подача