1

Изобретение относится к области импульсной техники, в частности к формирователям импульсов с подазлеиисм кратковременных помех, и может быть испо..ьзовано в вычислительной технике и автомати се.

Известно устройство, содержащее два триггера и вырабатывающее вы.чодной импульс с заданной задержкой при длительности управляющего сигнала большей заданного значения

1.

Однако такое устройство имеет сложную конструкцию, а его триггеры после включения или кратковременного пропадания напряжения могут устанавливаться в произвольное состояние, что приводит к выдаче ложного выходного импульса.

Известно устройство для подавления помех, содержащее два триггера, каждый из которых имеет входы нулевой, единичный, синхронизации и раздельной установки в «О и выходы единичный и инверсный, причем входы раздельной установки в «О обоих триггеров объединены, вход синхронизации первого триггера является входом устройства, единичный выход второго триггера - выходом устройства, а единичный выход первого триггера соединен с единичным входом второго триггера 2.

Однако это устройство отличается конструктивной сложностью и невысокой надежностью.

Цель изобретения - повышение надежности и упрощение устройства.

Для этого единичный вход второго триггера объединен с его входом синхронизации, нулевой его вход зазем„тен, а инверсный выход соединен с единичны.: входом первого триггера, причем объединенные входы раздельной уст;;новки в «О обоих триггеров являются управляю-щим входом устройства.

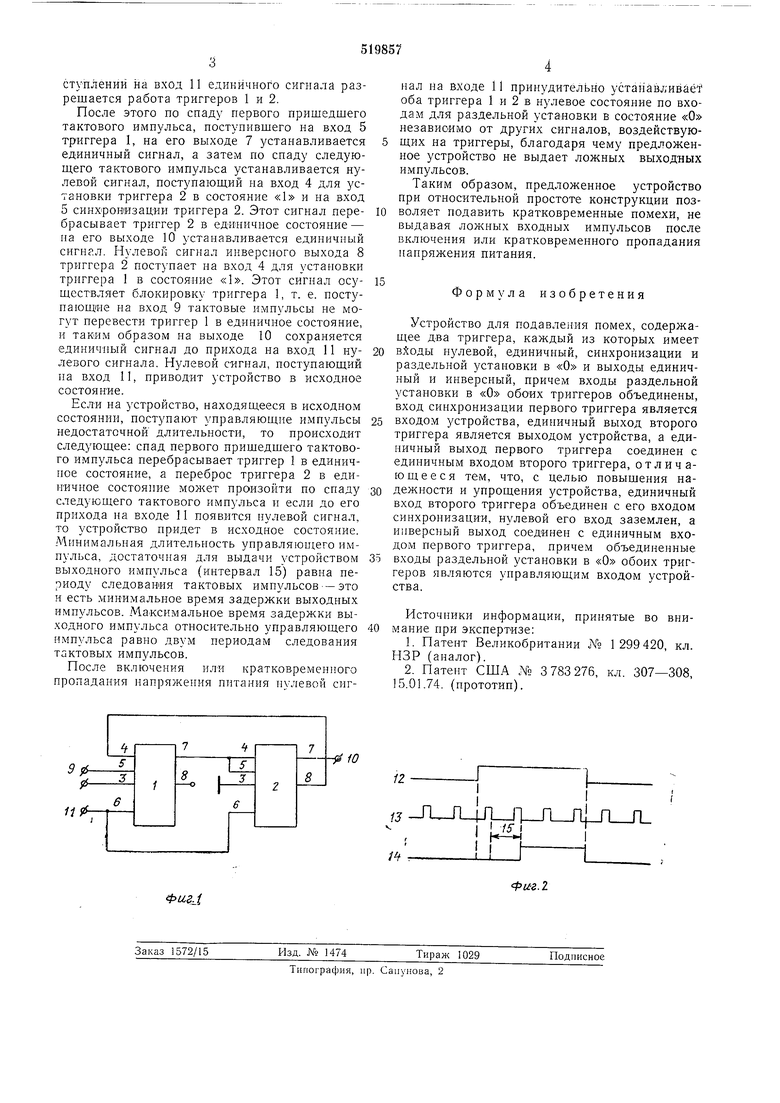

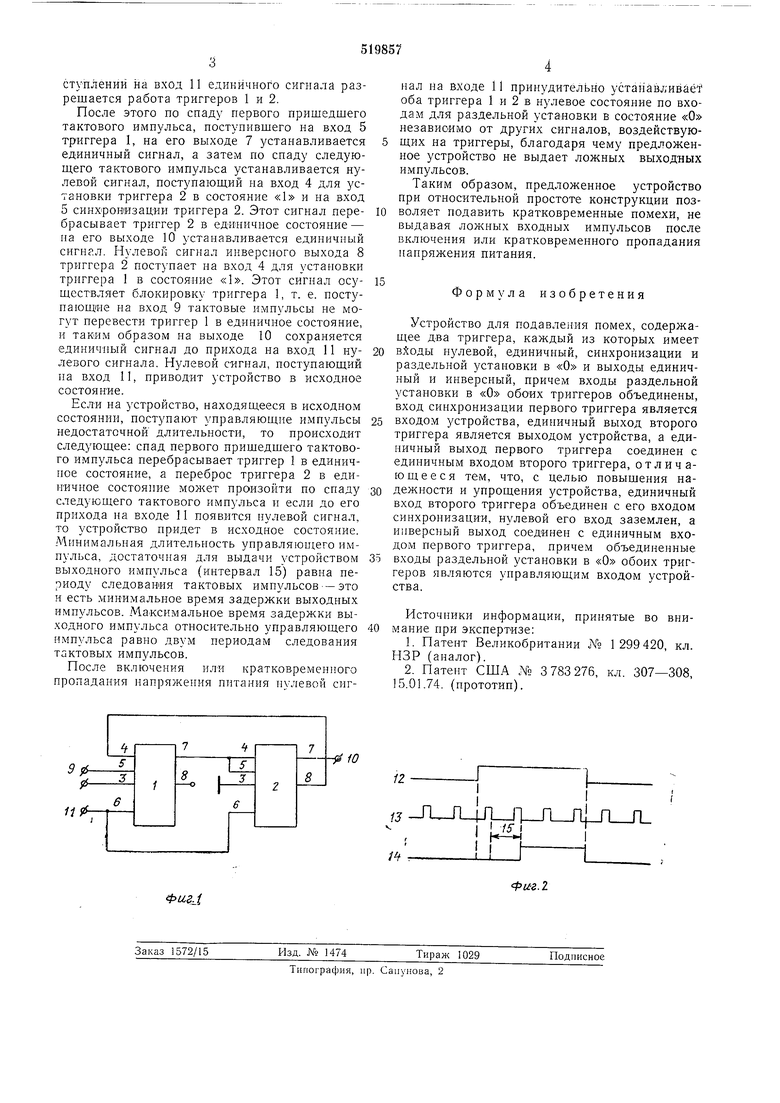

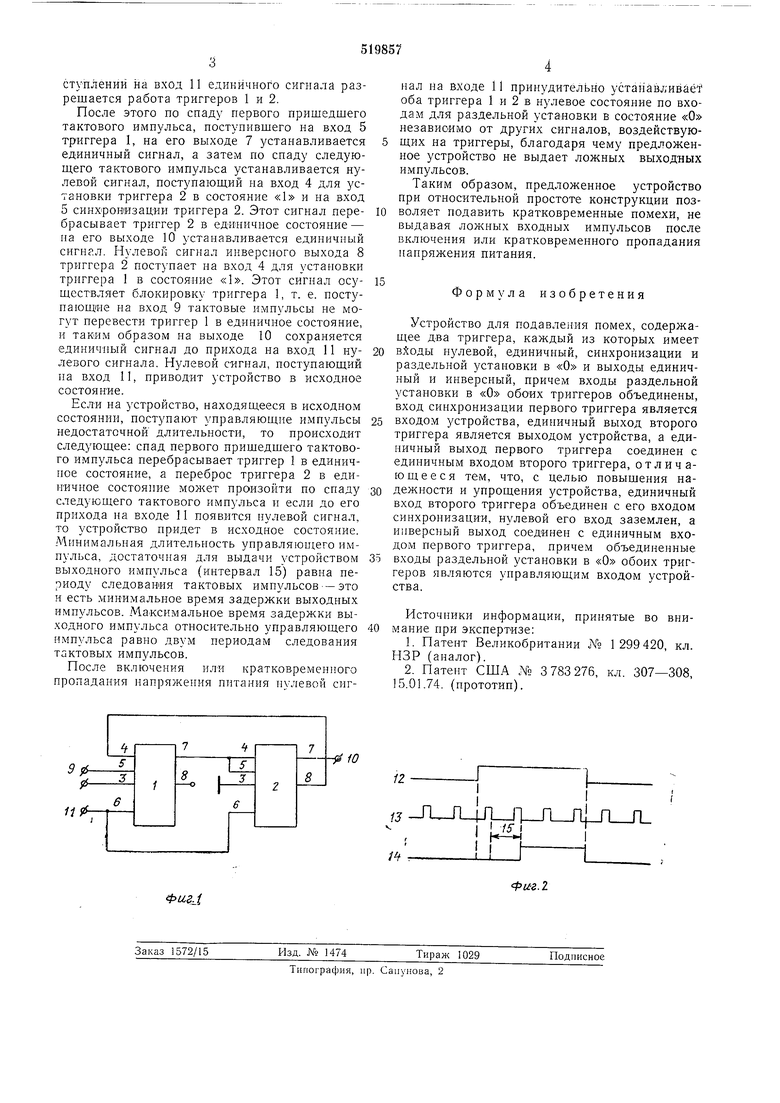

На фиг. 1 представлена принципиальна, электрическая схема предложенного устройства; на фиг. 2 - временная диаграмма его работы.

Устройство содержит триггеры 1, 2, каждый из которых имеет входы 3-6 нулевой, единичный, синхронизации и раздельной установки в

«О и выходы 7, 8 единичный и инверсный соответственно. Вход 5 синхронизации триггера 1 является входом 9, а единичный выход 7 триггера 2 - выходом 10 устройства. Объединенные в.ходы 6 раздельной установки в «О

триггеров 1 и 2 являются управляющим входом 11 устройства.

На временной диаграмме показаны импульсы 12-14, которые появляются на входах 11, 9 и выходе 10 соответственно, а интервал 15, равный минимальной длительности управляющего импульса, достаточной для выдачи устройством выходного сигнала. В исходном с:остоянии на входе И нулевой сигнал, который поступает на входы 6 триггеров 1 и 2,

принудительно устанавливая на их выходах 7 и выходе устройства нулевой сигнал. При поступлении на вход 11 единичного сигнала разрешается работа триггеров 1 и 2.

После этого по спаду первого пришедшего тактового импульса, поступившего на вход 5 триггера 1, на его выходе 7 устанавливается единичный сигнал, а затем по спаду следуюш.его тактового импульса устанавливается нулевой сигнал, поступаюший на вход 4 для установки триггера 2 в состояние «1 и на вход 5 синхронизации триггера 2. Этот сигнал перебрасывает триггер 2 в единичное состояние - на его выходе 10 устанавливается единичный сигнал. Нулевой сигнал инверсного выхода 8 триггера 2 поступает на вход 4 для установки триггера 1 в состояние «1. Этот сигнал осундествляет блокировку триггера 1, т. е. поступающие на вход 9 тактовые импульсы не могут перевести триггер 1 в единичное состояние, и таким образом на выходе 10 сохраняется единичный сигнал до прихода на вход 11 нулевого сигпала. Нулевой сигпал, поступающий на вход 11, приводит устройство в исходное состояние.

Если на устройство, находящееся в исходном состоянии, поступают управляющие импульсы недостаточной длительности, то происходит следующее: спад первого пришедшего тактового импульса перебрасывает триггер 1 в единичное состояние, а переброс триггера 2 в единичное состояние может произойти по спаду следующего тактового импульса и если до его прихода на входе 11 появится нулевой сигнал, то устройство придет в исходное состояние. Минимальная длительность управляюи1его импульса, достаточная для выдачи устройством выходного импульса (интервал 15) равна периоду следования тактовых импульсов - это и есть мииимальпое время задержки выходных импульсов. Максимальное время задержки выходного импульса относительно управляющего импульса равно двум периодам следования тактовых импульсов.

После включения или кратковременного пропадания напряжения питания нулевой сигнал На входе 11 принудительно устанавливае1 оба триггера 1 и 2 в нулевое состояние по входам для раздельной установки в состояние «О независимо от других сигналов, воздействующих на триггеры, благодаря чему предложенное устройство не выдает ложных выходных импульсов.

Таким образом, предложенное устройство при относительной простоте конструкции позволяет подавить кратковременные помехи, не выдавая ложных входных импульсов после включения или кратковременного пропадания напряжения питания.

Формула изобретения

Устройство для подавления помех, содержащее д-ва триггера, каждый из которых имеет в.оды пулевой, единичный, синхронизации и раздельной установки в «О и выходы единичный и инверсный, причем входы раздельной установки в «О обоих триггеров объединены, вход синхронизации первого триггера является входом устройства, единичный выход второго триггера является выходом устройства, а единичный выход первого триггера соединен с единичным входом второго триггера, отличающееся тем, что, с целью повышения надежности н упрощения устройства, единичный вход второго триггера объединен с его входом синхронизации, нулевой его вход заземлен, а инверсный выход соединен с единичным входом первого триггера, причем объединенные входы раздельной установки в «О обоих триггеров являются унравляющим входом устройства.

Источники информации, принятые во внимание при экспертизе:

1.Патент Великобритании N° 1299420, кл. НЗР (аналог).

2.Патент США № 3783276, кл. 307-308, 15.01.74. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1978 |

|

SU744943A1 |

| Устройство для подавления помех | 1984 |

|

SU1203692A2 |

| Селектор интервалов между импульсами | 1979 |

|

SU822341A1 |

| Цифровой фильтр | 1978 |

|

SU748803A1 |

| Формирователь импульсов | 1979 |

|

SU839034A1 |

| Аналого-цифровой преобразователь | 1977 |

|

SU684735A1 |

| Устройство для подавления помех | 1978 |

|

SU698128A2 |

| Устройство для подавления помехпРи цифРОВОй пЕРЕдАчЕ иМпульСНОйпОСлЕдОВАТЕльНОСТи | 1977 |

|

SU840745A1 |

| Расширитель импульсов | 1976 |

|

SU603109A1 |

| Формирователь импульсов по фронту и спаду | 1977 |

|

SU711671A1 |

Авторы

Даты

1976-06-30—Публикация

1974-11-10—Подача