. i

Изобретение относится к области автомаг(тики и вычислительной техники, предназнаj чено для реализации всех самодвойственных функций четырех переменных и может быть использовано при построении ЦВМ и САУ, I Известны устройства, предназначенные |для выполнения логическихфункций tl, 2. I Известен элемент вычислительной Ъреды , сод жащий триггеры, инверторы и элементы И, причем один логический полю элемента подключен к выходам / первого и второго элементов И, соединенных с вхо i дом инвертора, другой логический полюс - {к выходу третьего элемента Т1, к выходу I второго элеменат И и входу другого давертора. I Однако такой элемент вычисляет погичес I кие функции только двух переменных,.

Наиболее близким техническим решением к данному и обретен1ж является логическая {ячейка, содержащая элементы НЕ , И,

.

/-

, Однако такая ячейка не реализует всех

I само действенных функций четырех перемен|ных..

Целью изобретения является расширение функциональных возможностей путем реализации всех; самодвойственных функций четырех переменных.

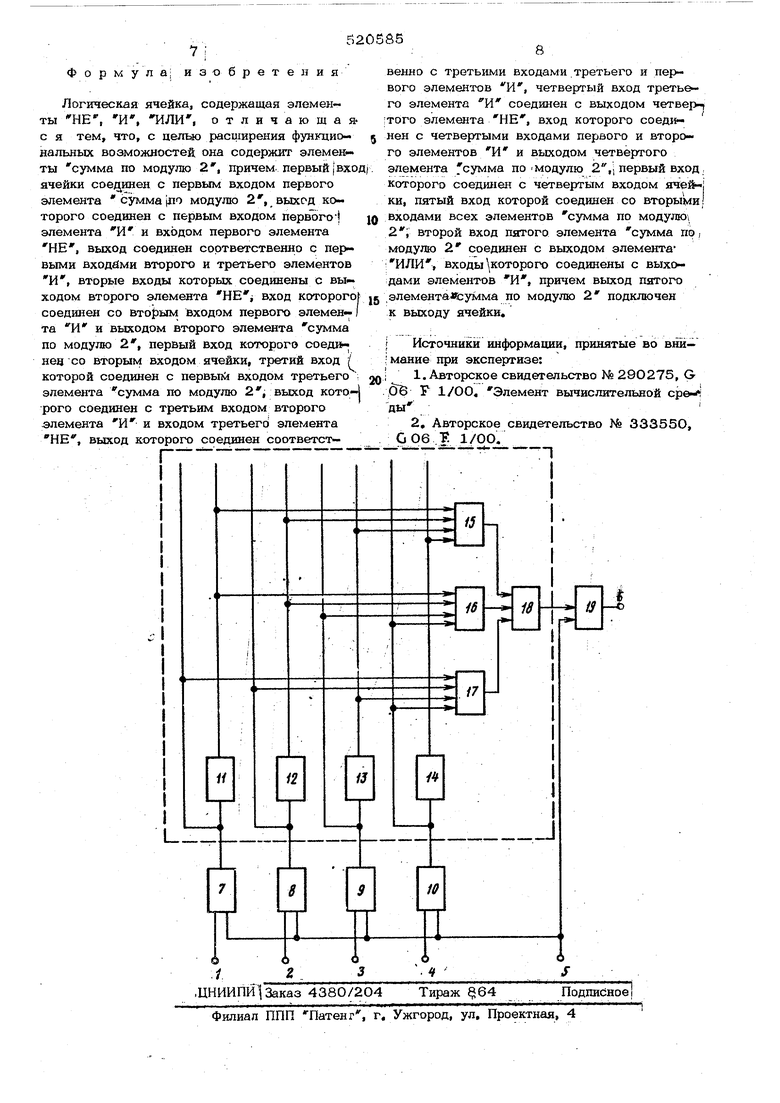

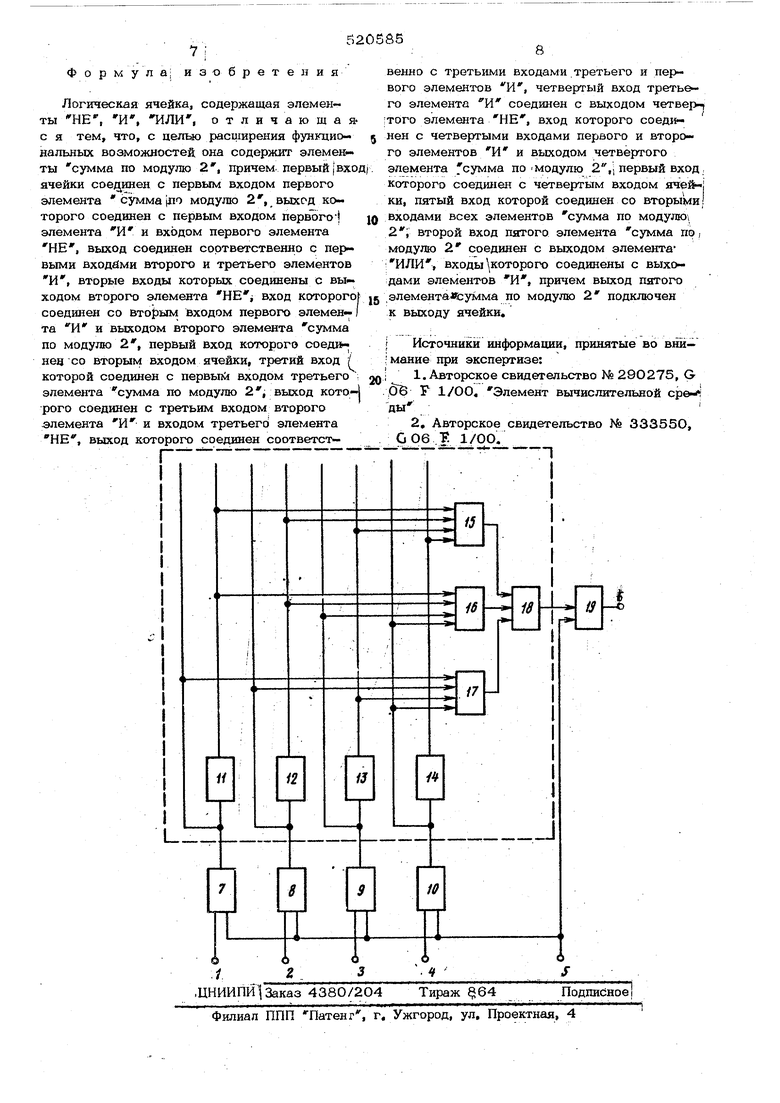

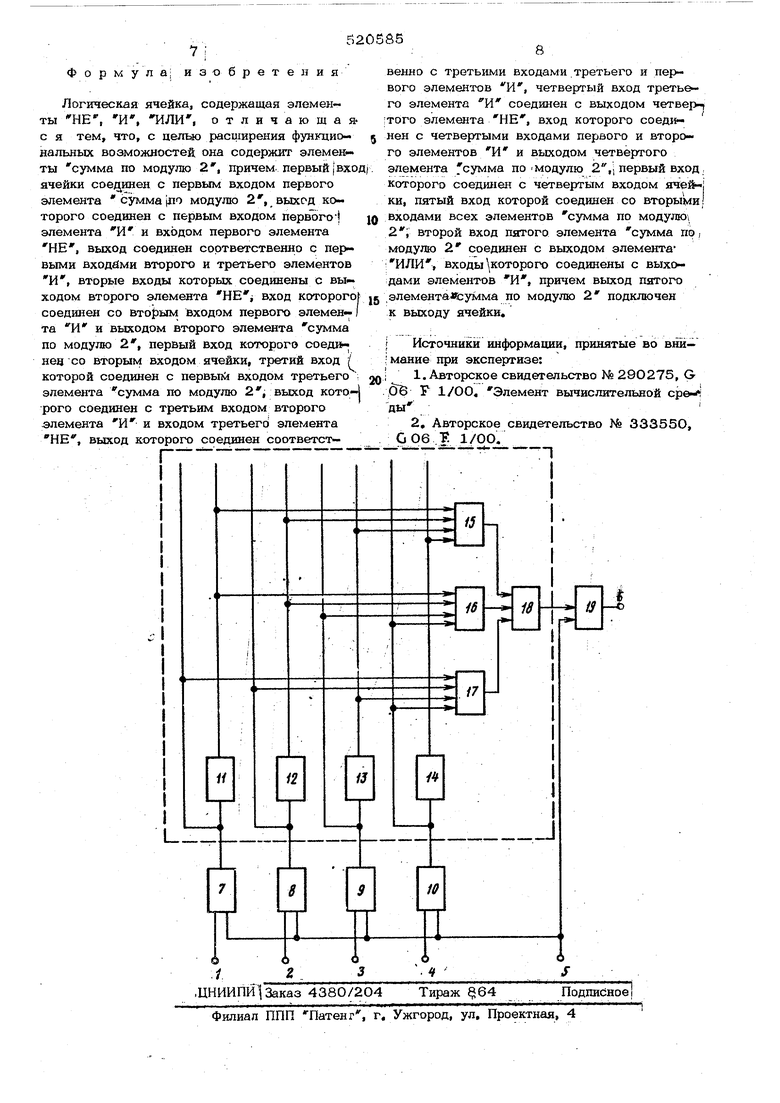

С аач)й целью предложенная ячейка содержит элементы сумма по модулю 2, первый вход ячейки соединен с первым входом первого элемента сумма по модулю 2, выход которого соединен с первым входом первого элемента И и входом первого элемента НЕ, выход которого соединен соответственно с первыми входами второго и третьего элементов И , вторые входы которых соединены с выходом второго эл&мента НЕ, вход которого соединен со вторым входом первого элемента И и выходом второго элемента сумма по модулю 2/, первый вход которого соединен со вторым входом ячейки, третий вХод которой соединен с первым входом j тЬвтъёго элеметта сумма по модулю 2/выход которого соединен с третьим входом второго элемента Щ я входом третьего элементаНЕ, вь) хйд.которого соединен соответственно с . третьими входами третьего и первого элемента И. Четверггый вход второго элемента И соединен с выходом четвертого элемента НЕ вход которого соединен с четвертыми входами первого и второго элементов И к выходом четвертого элемента сумма по модулю 2, первый вход которого соединен с чет-вертым входом ячейки, пятый вход которой соединен со вторыми входами всех элементов сумма по модулю 2. Второй вход пятого элемента сумма по модулю 2 соединен с выходом элемента ИЛИ, входы которого соединены с выходами элементов И , Выход пятого элемента сумма по модулю 2 подключен к выходу ячейки. Структурная схема логической ячейки представлена на чертеже. Логическая ячейка содержит входы 1-5, выход 6, четыре элемента 7-10 сумма по модулю 2, четыре элемента НЕ 11-14, три элемента И 15-17, один элемент ИЛИ 18 и (пятый) элемент сумма по модулю 2 19. Первый вход 1 ячейки соединен с первым входом первого элемента сумма по модулю 2 7, выход которого непосредственно соединен элементом И 17 и через первый элемент НЕ 11 с элементами И 15, 16 Второй вход 2 ячейки соединен с первым входом второго элемента по модулю 2 8, выход которого непосредствелшо соединен элементом И 17 и через второй элемент НЕ 12 с элементами И 15, 16. Третий вход 3 ячейки соединен с первым входом третьего элемента сумма по модулю 2 9, выход которого непосредственно соединен со вторым элементом И 16 и через третий элемент НЕ 13 с элементами И 15,17. Четвертый вход 4 ячейки соединен с первым входом четвертого элемента сумма по модулю 2 10, выход которого непосредственно соединен с элементами И 16, 17 и через четвертый элемент НЕ 14 с элементом И 15, Выходы элементов И 15, 16, 17 соединены со входами элемента ИЛИ 18, вььход которого соединен с одним входом пятого элемента сумма по модулю 2 19, Пятый вход 5 ячейки соединен со вторыми входами всех элементов сумма по модулю 2 - 7-10 и 19, а выход элемента 19 служит выходом 6 устройства. На выходе 6 реализуется логическая функция F {Lca@e)(t©eHc@e)td©e)v(a©e)(t)0e) c@e)Cd+e)v (a©e.)(t)©eHc®e(.d0e)3@eb где а, в, с, d j е - сигналы на входах 1-5 соответственно. Работа интегрального модуля описывается таблицами 1, 2 и 3,

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический модуль | 1984 |

|

SU1242929A1 |

| Логическое устройство | 1976 |

|

SU657432A1 |

| Многофункциональный логический модуль | 1974 |

|

SU500525A1 |

| Устройство для вычисления булевых дифференциалов | 1989 |

|

SU1777132A1 |

| Универсальный логический модуль | 1987 |

|

SU1536370A1 |

| ТРОИЧНЫЙ Т-ТРИГГЕР И ТРОИЧНЫЙ РЕВЕРСИВНЫЙ СЧЕТЧИК НА ЕГО ОСНОВЕ | 2014 |

|

RU2562370C2 |

| Четырехвходовый одноразрядный сумматор | 1986 |

|

SU1417012A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Система для выполнения команд десятичной арифметики табличным способом | 1981 |

|

SU1027731A1 |

| Устройство для полиномиального разложения логических функций | 1988 |

|

SU1550507A1 |

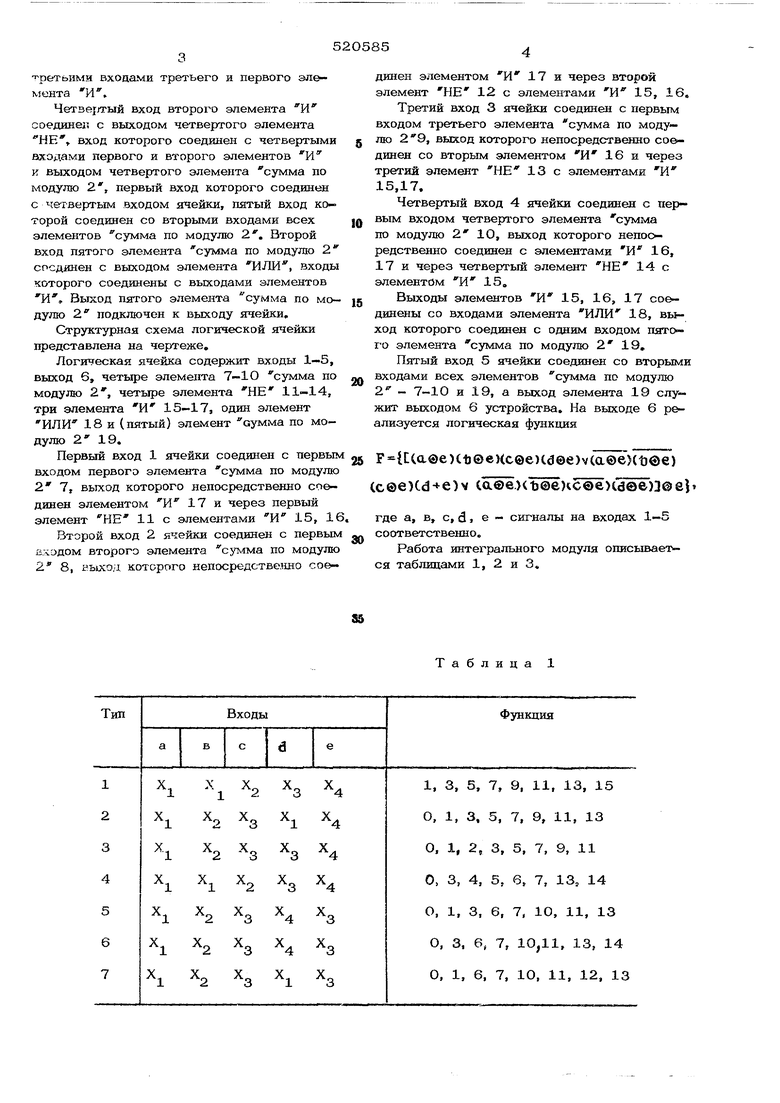

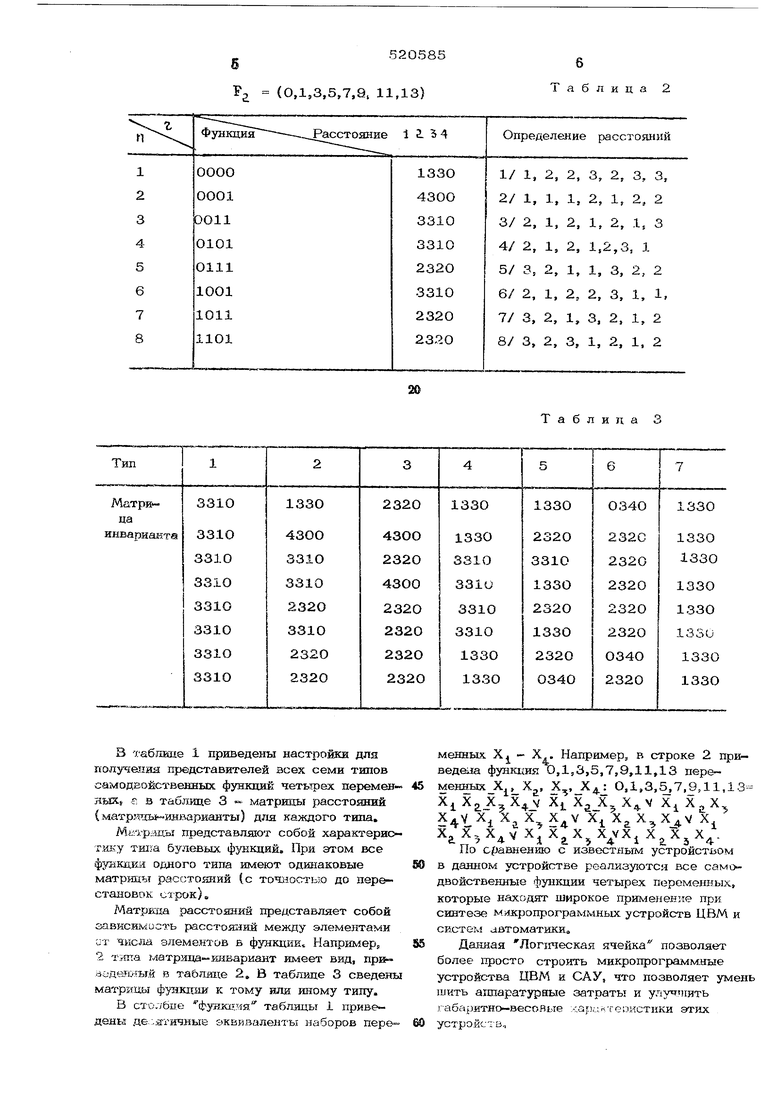

Таблица 1

F (0,1,3,5,7,9. 11,13)

В /.абпние i приведены настройки для получения представителей всех семи типов самодвойственных функций четьфех перемен-

ных, & в таблице 3 матршхы расстояний (матржгы инварианты) для каждого типа.

Мь трлды представляют собой характерис- TJiKy тшга булевых функций. При этом все фзшюоии одного типа имеют одинаковые

матр}щы расстояний (с точностью до перестановок С1рок).

Матррлш расстояний представляет собой зависим и сть расстояний между элементами UT числа элементов в функции Например, 2 Tiina матр л1да шжариант имеет вид, при в таблице 2. В таблице 3 сведены матризхы фунщгии к тому или иному типу.

В столбце Фуйкдия таблицы i приведены де :.йтичные эквиваленты наборов пере-

Таблица 2

Таблица

меннык Х| - X . Например, в строке 2 приведена функция 0,1,3,5,7,9,11,13 пере менных Х ,Х, Х,,Хд2 0,1,3,5,7,9,11., XJL Х XjX,,X X X X, X V Xj X X , X.

По сравнению с кзвестнъсм устройством в данном устройстве реализуются все самодвойственные функции четырех переменных, которые находят широкое применение при синтезе микропрограммных устройств ЦВМ и систем автоматики

Данная Логическая ячейка позволяет более просто строить микропрограммные устройства ЦВМ и САУ, что позволяет умен шить агшаратурвгеае затраты и улучтпить габаритно-весойые характеристики этих устройств. Формула; изобретения Логическая ячейка, содержащая элементы НЕ , И, ИЛИ отличающая с я тем, что, с целью расширения функциональных возможностей она содержит элемен ты сумма по модулю 2, причем первый вхо ячейки с первым входом первого элемента сумма |до модулю 2, выход которого соединен с первым входом первЪго| элемента И и входом первого элемента НЕ, выход соединен соответственно с nei выми входами второго и третьего элементов И, вторые входы которых соединены с выходом второго элемента НЕ вход которого соединен со )ым входом первого элемента И и выходом второго элемента сумма по модулю 2, первый вход которого со вторым входом ячейки, третий вход / которой соединен с nepBbnii входом третьего элемента сумма по модулю 2, выход которого соединен с третьим входом второго элемента И и входом третьего элемента НЕ , выход которого соединен соответст- венно с третьими входами .третьего и перьвого элементов И, четвертый вход третьего элемента И соединен с выходом четвер-) jToro элемента НЕ, вход которого с четвертыми входами первого и второго элементов И и выходом четвертого элемента сумма подмодулю 2 ,| первый вход, которого соединен с четвертым входом , пятый вход которой соединен со вторыми входами всех элементов сумма по модулю 2, второй вход пятого элемента сумма по, модулю 2 соединен с выходом элементаИЛИ, входы KOTOpoго соединены с выходами элементов И, причем выход пятого алемента ьумма по модулю 2 подключен к выходу ячейки. | Источники информации, принятые во вни: мание при экспертизе: 1. Авторское свидетельство № 290275, G :дВ F 1/00, Элемент вычислительной сре-2, Авторское свидетельство № 33355О, 006.1 1/00,

Авторы

Даты

1976-07-05—Публикация

1974-06-19—Подача