выходу модуля блока деления, информационный выход которого подключен к второму информационному входу блока умножения, второй выход которого подключен к информационному входу блока деления, причем блок управления содержит блок постоянной памяти регистр, первый и вторО1Й счетчики, первый и второй коммутаторы, четыре сумматора по модулю два,. дешифратор два элемента НЕ, шесть элементов И и элемент ИЛИ, при этом в блоке управления информационный выход блока постоянной памяти подключен к информационному входу регистра, выход первого разряда которого подключен к счетному входу первого счетчика, выход i-ro (i 1,4) разряда которого подключен к первому входу i-ro ,сумматора по Модулю два, выход которого подключен к i-му входу первого элемента И, выход которого подключен к первс у входу второго элемента И, выход которого подключен к первому входу элемента ИЛИ, выход которого подключен к первому управляющему входу первого коммутатора блока управления, информату онный выход которого поразрядно подклйочен к информационному входу второго счетчика, информационшй выход которого подключен к адресному входу блока постоянной памяти, выходы второго .и третьего разрядов регистра подключены к входам соответственно Первого и рторого элементов НЕ и соединены соответственно с первым и вторьм входами третьего элемента И, выход которого подключен к второму входу второго элемента И и соединен с первыми входами четвертого и пятого элементов И, выходы которых под ключены соответственно к второму и третьему входам элемента ИЛИ, четвертый вход которого подключен к вьшоду шестого элемента И, первый и второй входы которого подключены к выходам соответственно первого и второго элементгв НЕ, выход четвертогоразряда регистра подключен к второму

44117

управлякщему входу первого коммутатора блока управления и счетному входу второго счетчика, вход синхронизациикоторого является входом запуска процессора, выход пятого разряда регистра подключен к вторым входам четырех сумматоров по модулю два, выход шестого разряда регистра подключен к второму входу пятого элемента И, третий вход которого подключен к первому информационному выходу второго коммутатора блока управления, второй информационный выход которого подключён к второму входу четвертого элемента И, выход седьмого разряда регистра подключен к входу дешифратора, выход которого подключен к пернхэму fуправляющему входу второго тора блока управления, третий информационный выход которого является вьсходом аварийного завершения вычислений процессора, первый выход регистра блока управления подключен к первому информационному входу nfepвого коммутатора блока управления, второй информационный вход которого соединен с управляющим входом второго коммутатора блока управления и является входом задания функции процессора, второй выход регистра блока Управления поразрядно подключен к адресному входу блока памяти, выходы восьмого - восемнадцатого разрядов регистра блока управления подключены соответственно к входу синхронизации первого регистра, управляющим входам первого и второго блоков памяти, управлягацим входам первого и третьего коммута1 ор в, управляющим входам второго регистра и второго ко жутатора, входам синхронизации четвертого регистра, блока умножения, третьего регистра и блока деления, третий выход регистра блока управления поразрядно подключен к второму входу сумматора, а второй и третий информационные входы второго коммутатора блока управления поразрядно подключены соответственно к второму выходу второго регистра и третьему выходу блока умножения.«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Специализированный процессор для вычисления элементарных функций | 1984 |

|

SU1265764A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Специализированный процессор | 1977 |

|

SU723581A1 |

| Специализированный процессор | 1977 |

|

SU734705A1 |

| Цифровое устройство для логарифми-РОВАНия дВОичНыХ чиСЕл | 1979 |

|

SU813414A2 |

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1145340A1 |

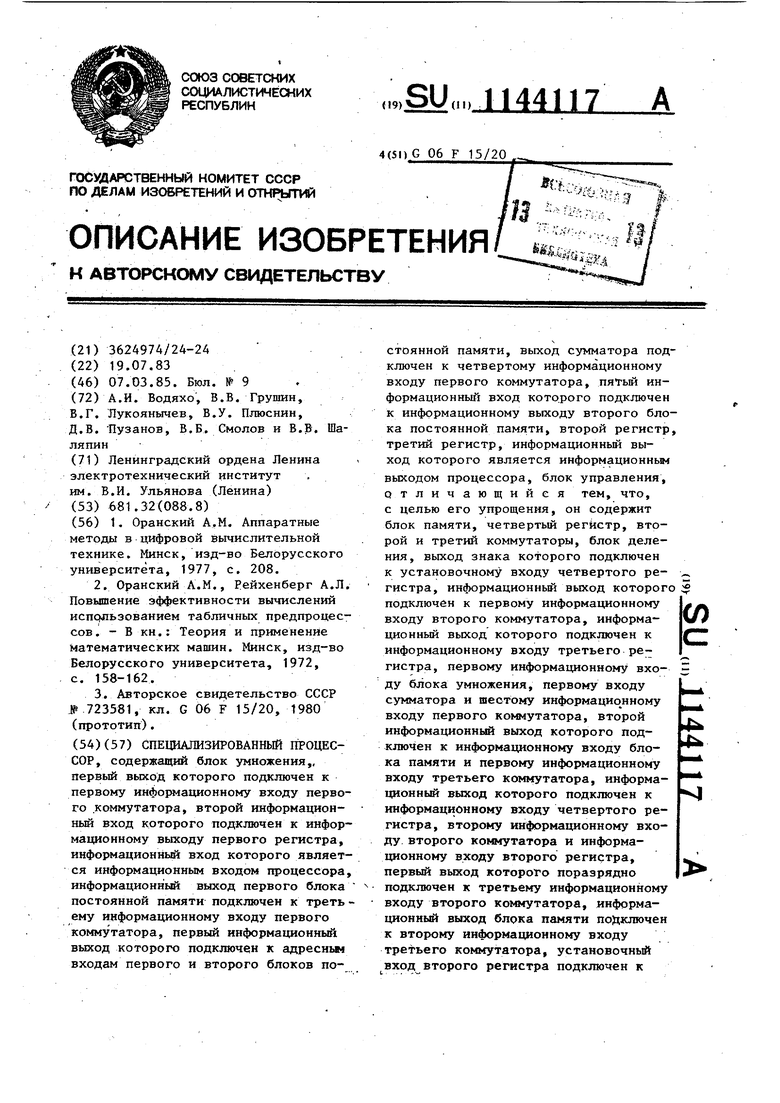

СПЕЦИАЛИЗИРОВАННЫЙ ПРОЦЕССОР, содержащий блок умножения,, первьй выход которого подключен к первому информационному входу первого коммутатора, второй информационный вход которого подключен к информационному выходу первого регистра, информационный вход которого является информационным входом процессора, информационный выход первого блока постоянной памяти подключен к треть ему информационному входу первого коммутатора, первый информационный выход которого подключен к адресным входам первого и второго блоков постоянной памяти, выход сумматора подключен к четвертому информационному входу первого коммутатора, пятьм информационный вход которого подключен к информационному выходу второго блока постоянной памяти, второй регистр, третий регистр, информационный выход которого является информационным выходом процессора, блок управления, отличающийся тем, что, с целью его упрощения, он содержит блок памяти, четвертый регистр, второй и третий коммутаторы, блок деления, выход знака которого подключен к установочному входу четвертого регистра, информационньй выход которого подключен к первому информационному (Л входу второго коммутатора, информационный выход которого подключен к информационному входу третьего регистра, первому информационному входу блока умножения, первому входу сумматора и шестому информацио нному входу первого коммутатора, второй 4 4;: информационный выход которого подключен к информационному входу блока памяти и первому информационному входу третьего коммутатора, информационный выход которого подключен к информационному входу четвертого регистра, второму информационному входу второго коммутатора и информационному входу второго регистра, первый выход которого поразрядно подключен к третьему информационному входу второго коммутатора, информационный выход блока памяти подключен к второму информационному входу третьего коммутатора, установочньй вход второго регистра подключен к

1

Изобретение относится к вычислительной технике и может быть использовано как в качестве периферийного процессора вычислительной системы

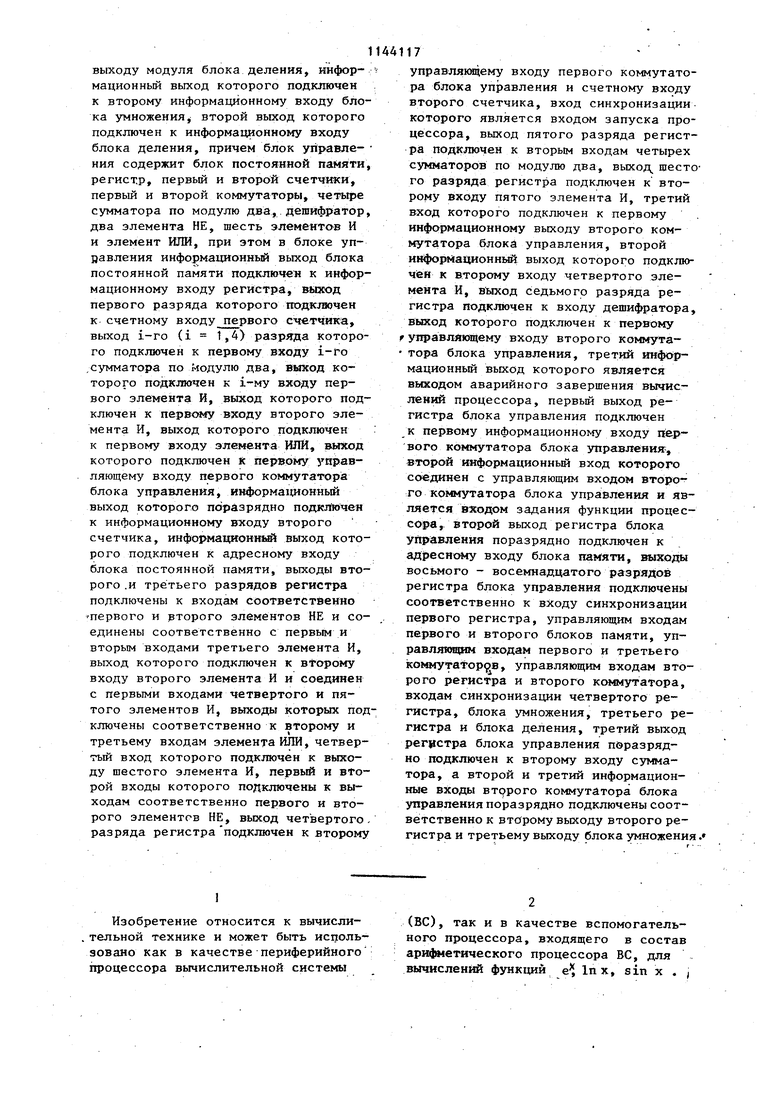

(ВС), так и в качестве вспомогательного процессора, входящего в состав арифметического процессора ВС, для вычислений функций е 1пх, sin х . j 3 Известны процессоры для вычисления элемента-рных функций табличного типа на основе постоянного запоминающего устройства (ПЗУ) У Подобные устройстгза отличаются высоким быстродействием, однако при работе с аргументом, содержащим 16-20 двоичных разрядов, объем ПЗУ становится недопустимо большим. Вр де случаев, в частности в современных универсальных ЦВМ общего назначения, необходимо вычисление функци со значительно большей точностью (50-60 двоичных разрядов). Развитием табличных методов являются таблично-алгоритмические метод позволякицие при приемлемых аппаратурных затратах получить внсокое быстродействие, сочетая его с высокой точностью вычисления zj . Наиболее близким к изобретению по технической сущности является специализированный процессор для вычисления функций е , 1п х, sin х содержащий входной регистрj первый выход которого связан с первыми входами множительного устройства (МУ) и сумматора, выход сумматора соединен с первым входом выходного регистра и вторым входом второго регистра, выход выходного регистра соединен с первыми входами элементов И первой группы, выходы которых подключены к второму входу МУ, к третьему входу которого подключен первый выход счетчика порядка, выход МУ подключен к первому входу входного регистра и к второму входу сумматора, третий вход которого под ключен к выходам элементов И второй группы, первые входы которого подключены к выходу ПЗУ, второй выход входного регистра подключен к перво му входу сдвигателя, выхсд сдвигате ля соединен с входом ПЗУ, третий вы ход входного регистра подключен к входу запоминающего устройства выход которого соединен с четвертым входом МУ, второй выход счетчика порядка подключен к второму входу сдвигателя, второй вход счетчика порядка и третий вход входного регистра подключены к первому и второ му входам процессора, к выходу кото рого подкл;ючен выход выходного регистра 3j . I Недостатками известного устройства являются большая сложность и. 74 как следствие, ограниченные функциональные возможности. Оснопным ограничением расширения реализуемого функционального набора является рост объема памяти, в которой хранятся значения коэффициентов. Например, для вычисления элементарной функции в формате с плавающей запятой при аргументе длиной 6А разряда требуется память коэффициентов около 40 Кбайт. Лругим фактором, ограничивающим число аппаратно реализуемых функций, является существе.нньп разброс относительной частоты появления различных функций. Прямая аппаратная реализация в этом случае приводит к снижению эффективности использования оборудования. Принципиально возможна программно аппаратная реализация редко встречающихся функций с использованием арифметических устройств ЦВМ. Однако в современных высокопроизводительных ЦВМ время пересылки операнда между центральным и периферийным оказывается сравнимо со временем выполнения арифметической операции, что приводит к резкому снижению фактической эффективности от использования специализированного процессора. Поэтому в процессор вводятся средства для аппаратно-программной реализации относительно редко встречающихся функций через аппаратно реализуемый базовый набор. Остальные элементарные функции (ЭФ) и ряд специальных функций (СФ) (показательный интеграл и интегральные синус и косинус) вычисляются по подпрограммам, хранящимся в микропрограммной памяти спецпроцессора. Цель изобретения - упрощение процессора. Указанная цель достигается тем, что cпeциaлизиpoвaнньD процессор, содержащий блок умножения, первый выход которого подкзтючен к первому информационноь4у входу первого коммутатора, второй информационный вход которого подключен к информационному выходу первого регистра, информационный вход которого является информационным входом процессора, информационный выход первого блока постоянной памятиподключен к третьему информационному входу первого коммутатора, первьй информационный выход которого подключен к адресным входам первого и второго блоков постоянной памяти, выход сумматора подключен к четвертому информационному входу первого коммутатора, пятый информационный вход которого подключен к информационному выходу второго блока постоянной памяти, второй регистр, третий регистр, информационный выход которого является информационным выходом процессора, блок управления, содержит блок памяти, четвертый регистр, второй и третий коммутаторы, блок деления, выход знака которого подключен к установочному входу четвертого регистра, информационный выход которого подключен к первому информационному входу второго коммутатора, информационный выход которого подключен к информационному входу третьего регистра, первому информационному входу блока, умножения, первому- входу сумматора и шестому инфор мационному входу первого коммутатора второй информационный выход которого подключен к информационному входу блока памяти и первому информационному входу третьего коммутатора, информационный выход которого подклю чен к информационному входу четвертого регистра, второму информационному входу второго коммутатора и ниформационному входу второго регистра первый выход которого поразрядно подключен к третьему информационному входу второго коммутатора, информационный выход блока памяти подключен к второму информационному входу третьего коммутатора, установочный вход второго регистра подключен к выходу модуля блока деления, информа1 ;ионный выход которого подключен к второму информационному входу бло ка умножения, второй выход которого подключен к информационному входу . блока деления, причем блок управления содержит блок постоянной памяти регистр, первый и второй счетчики, первый и второй KONMyraTOpbi, четыре сумматора по модулю два, дешифратор два элемент НЕ, шесть элементов И и элемент ИЛИ, при этом в блоке управленйя информационньй выход блока постоянной памяти подключен к инфор мационному входу регистра, выход пе вого разряда которого подключен к счетному входу первого счетчика, выход, i-ro (i 1,4) разряда-которого подключен к первому входу i-ro сумматора по модулю два, выход которого подключен к i-му входу первого элемента И, выход которого подключен к первому входу второго элемента И выход которого подключен к первому входу элемента ИЛИ, выход которого подключен к первому управляющему входу первого коммутатора блока управления, информационный выход которого поразрядно подключен к информационному входу второго счетчика, информационный выход которого подключен к адресному входу блока постоянной памяти, выходы второго и третьего разрядов регистра подключены к входам соответственно первого и второго элементов НЕ и соединены соответственно с первым и ъторым входами третьего элемента И, выход которого подключен к второму входу второго элемента И и соединен с первыми входами четвертого и пятого элементов И, выходы которых подключены соответственно к второму и третьему входам элемента ИЛИ, четвертый вход которого подключен к выходу шестого элемента И, первьй и второй входы которого подключены к выходам соответственно первого и второго элементов НЕ, выход четвертого разряда регистра подключен к второму управляющему входу первого коммутатора блока управления и счетному входу второго счетчика, вход синхронизации которого является входом запуска процессора, выход пятого разряда регистра подключен к вторьм входам четырех сумматоров по модулю два, выход шестого разряда регистра подключен второму входу пятого элемента И, третий вход которого подключе 1 к первому информационному выходу второго коммутатора блока управления, второй информационный выход которого подключен к второму входу четвертого элемента И, выход седьмого разряда регистра подключен , к входу дешифратора, выход которого подключен к первому управляющему входу второго коммутатора блока управления, третий информационный выход которого является выходом аварийного завершения вычислений процессора, первый выход регистра блока управления подключен к первому ииформациоииому входу первого коммутатора блока управления, второй информационный вход которого соединен с управляющим входом второго

коммутатора блока управления и является входом задания функции процессора, второй выход регистра блока управления поразрядно подключен к адресному входу блока памяти, выходы восьмого-восемнадцатого разрядов регистра блока управления подключены соответственно к входу синхронизации первого регистра, управляющим входам первого и второго блоков памяти, управляющим входам первого и третьего коммутаторов, управляющим входам второго регистра и второго коммутатора, входам синхронизации четвертого регистра, блока умножения, третьего регистра и блока деления, третий выход регистра блока управления поразрядно подключен к второму входу сумматора, а второй и третий информационные входы второго коммутатора блока управления поразрядно подключены соответственно к второму выходу второго регистра и третьему выходу блока умножения.

Сущность изобретения заключается в многофункциональном использовании операционных устройств и применении однотипных алгоритмов, за счет чего уменьшается оборудование. Оборудование умножителя, которое занимает значительный объем, используется дл деления путем введения небольшого вспомогательного блока и двух регистров. Наличие операции деления позволяет аппаратно реализовать функции типа arctgx, а микропрограммно все остальные элементарные функции (ЭФ). Вычисление каждой аппаратно реализуемой ЭФ может быть

сведено к небольшому числу действий по предварительной обработке аргумента и вычислению степенного ряда

одинаковой, степени. Кроме того, через аппаратно реализуемые ЭФ и степеные ряда невысокой степени можно вычислять ряд специальных функций. Использование однотипных алгоритмов позволяет упорядочить связи между блоками в процессоре, упростить и уменьшить объем микропрограмм,

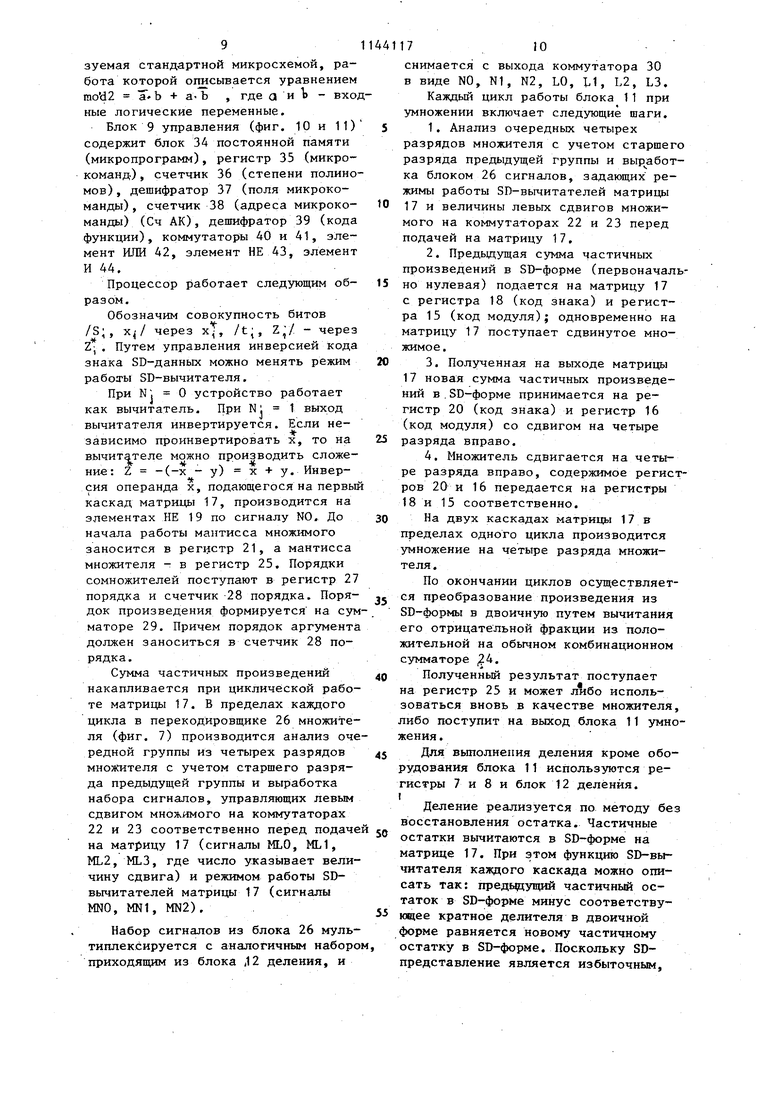

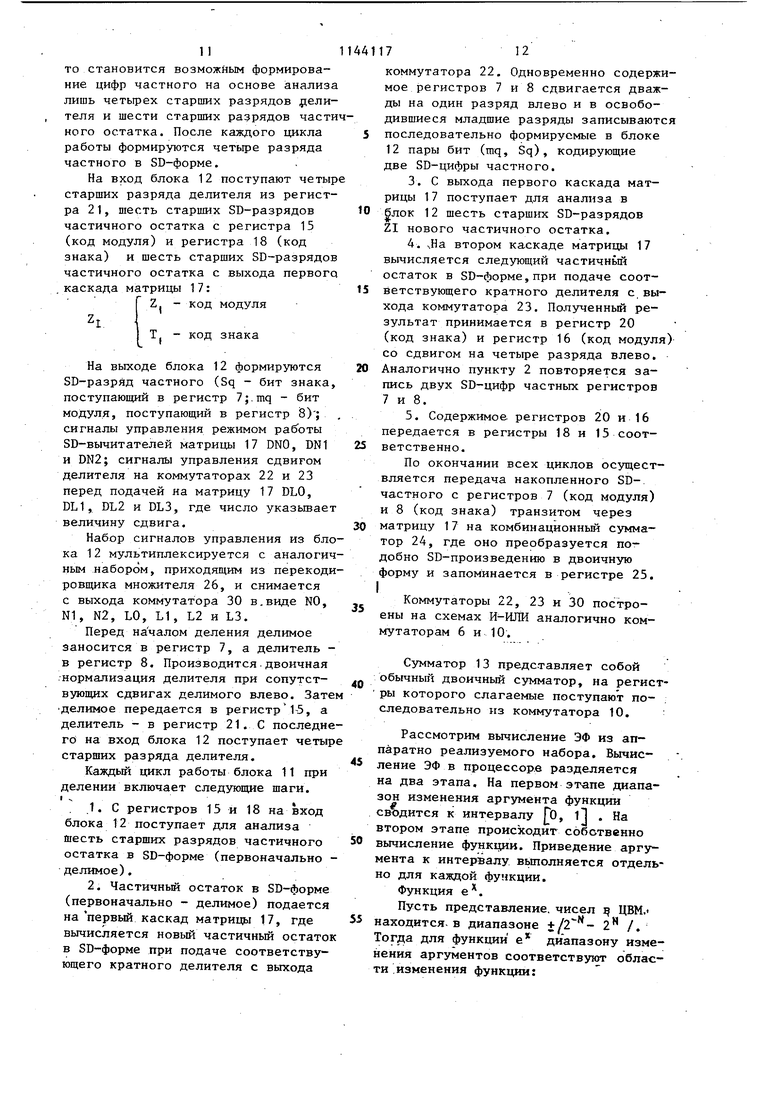

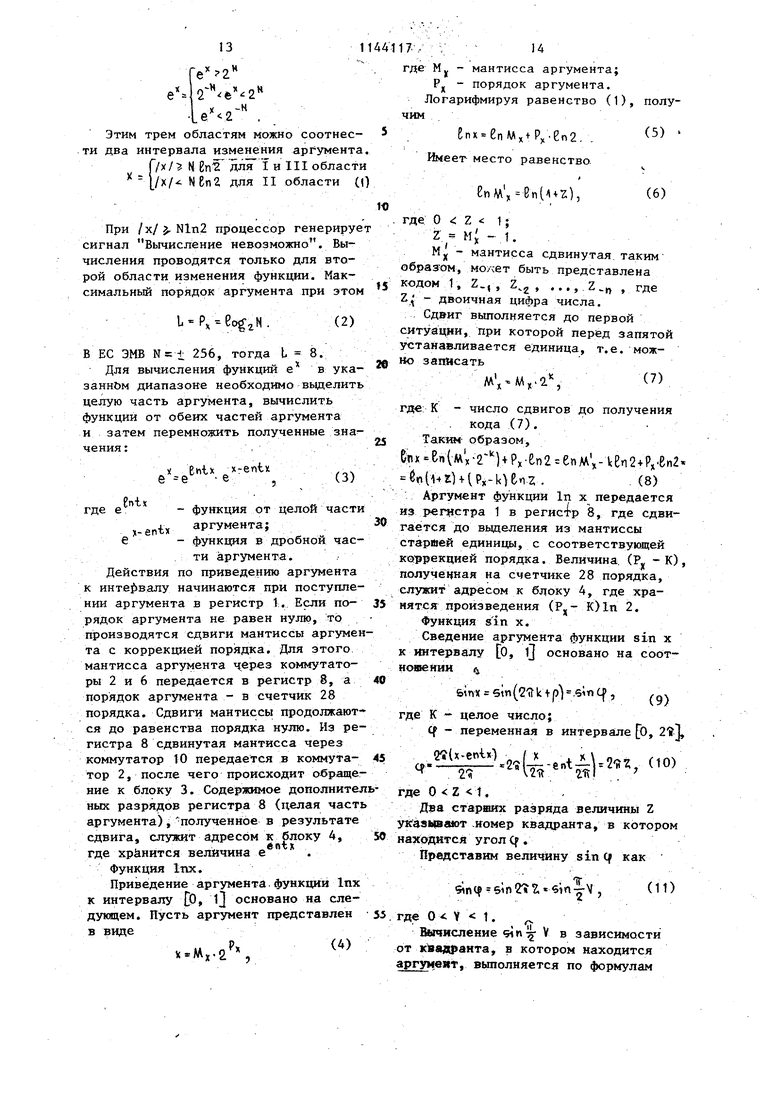

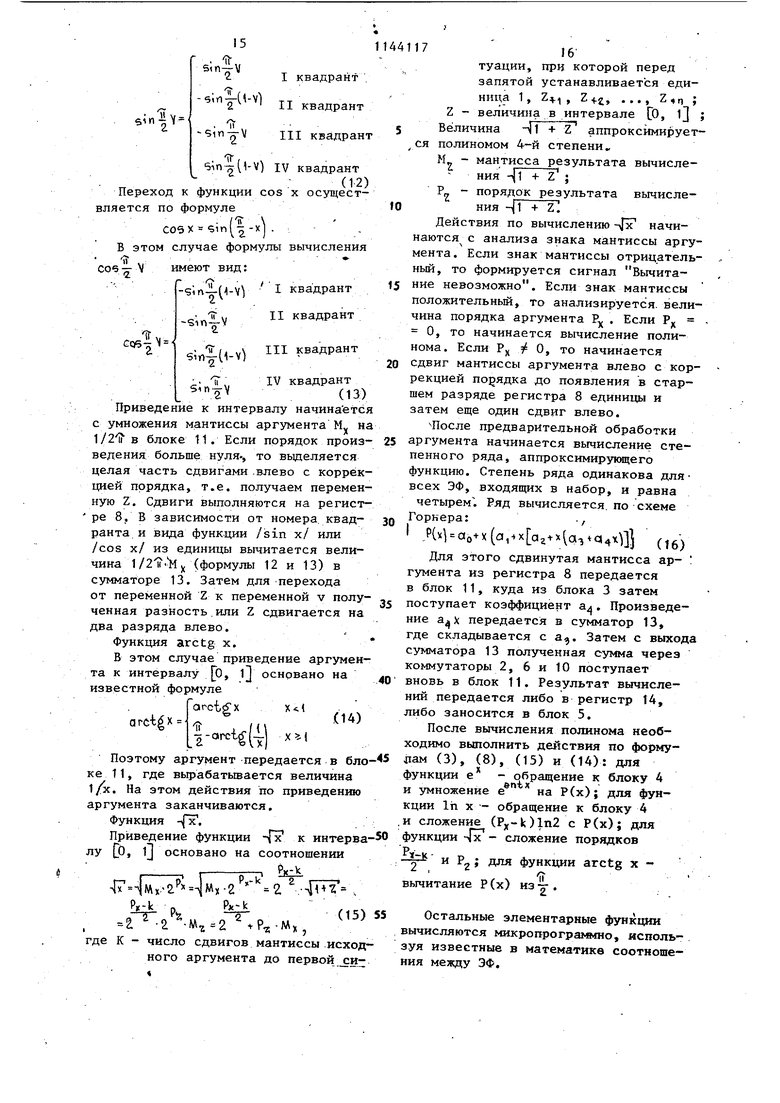

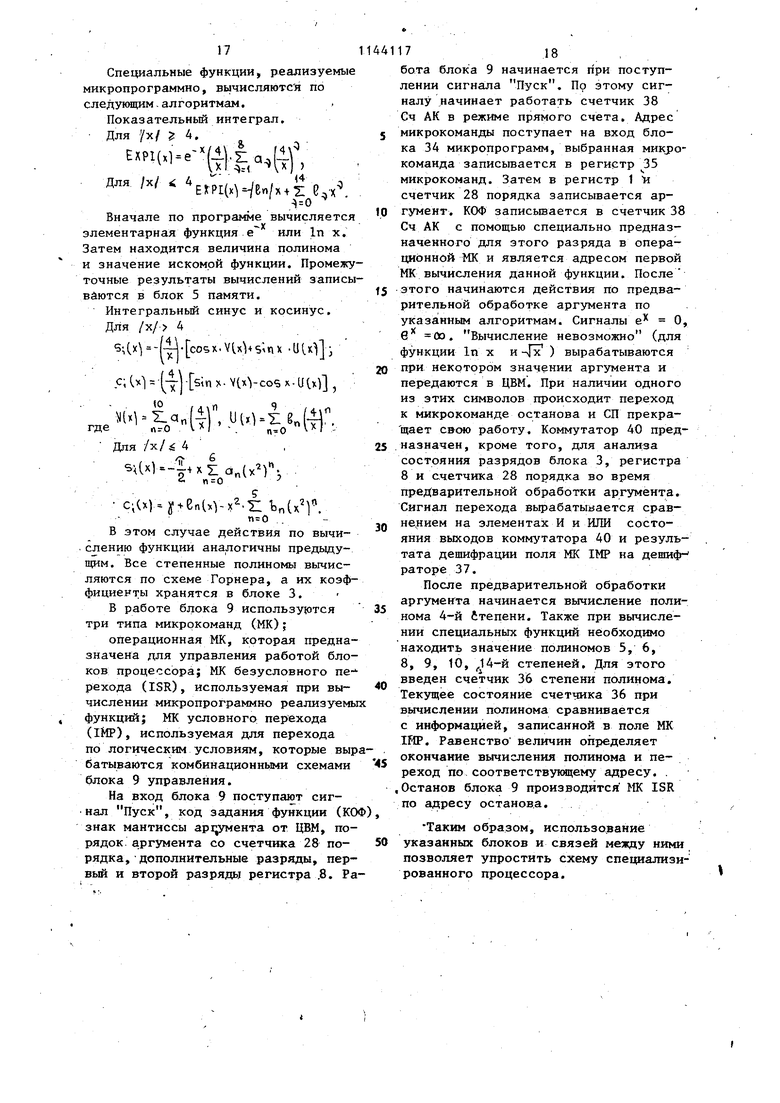

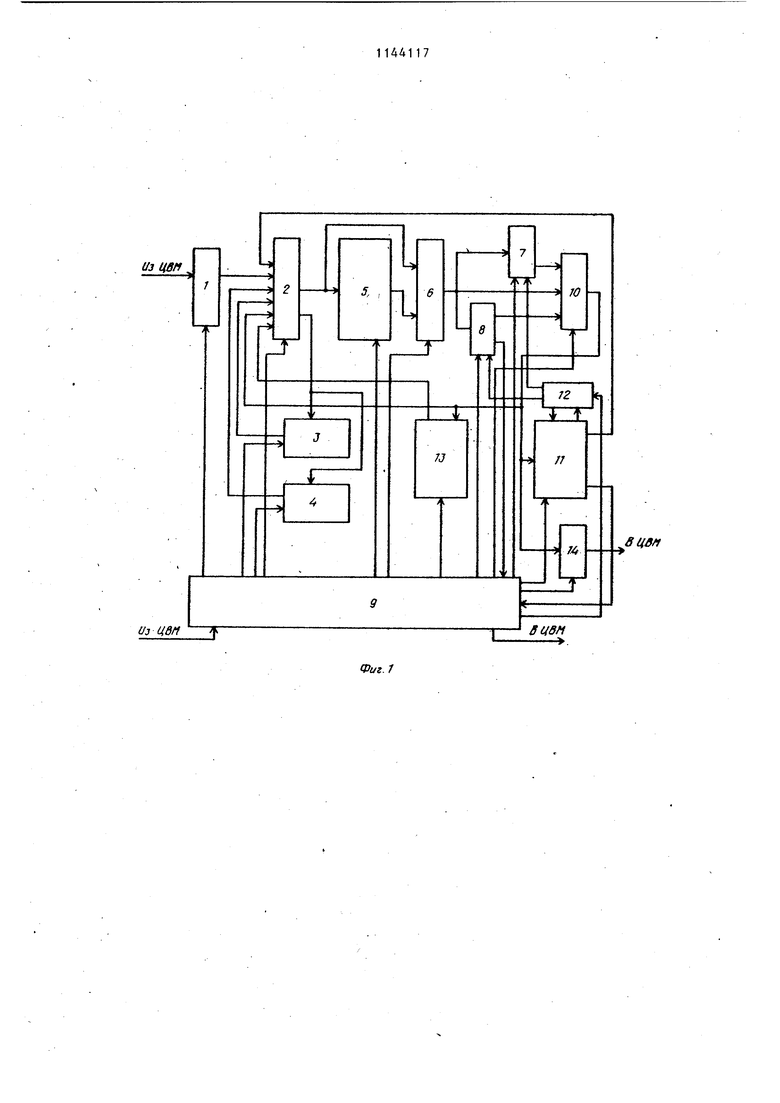

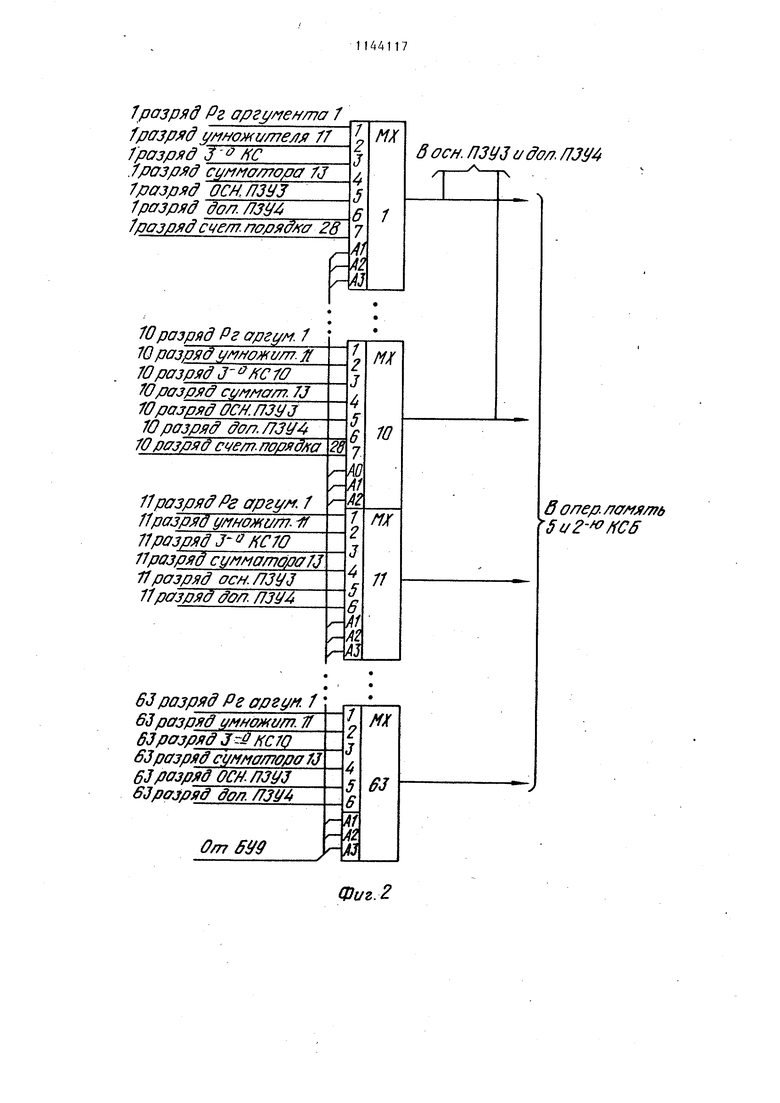

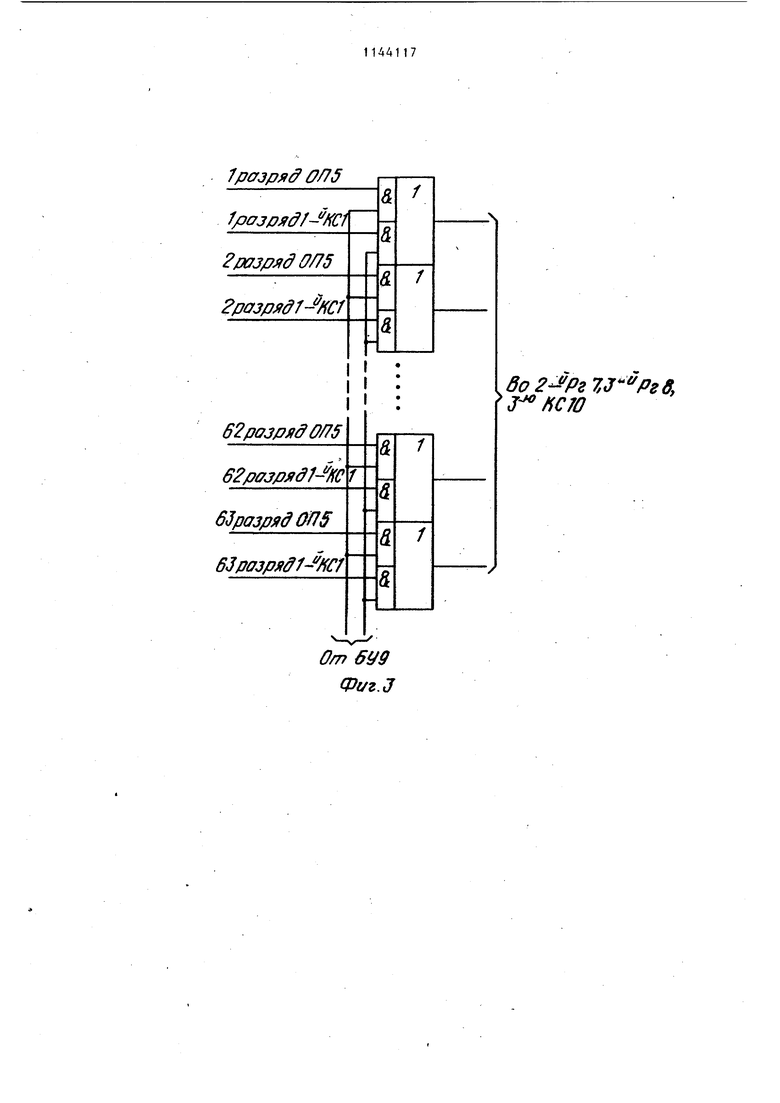

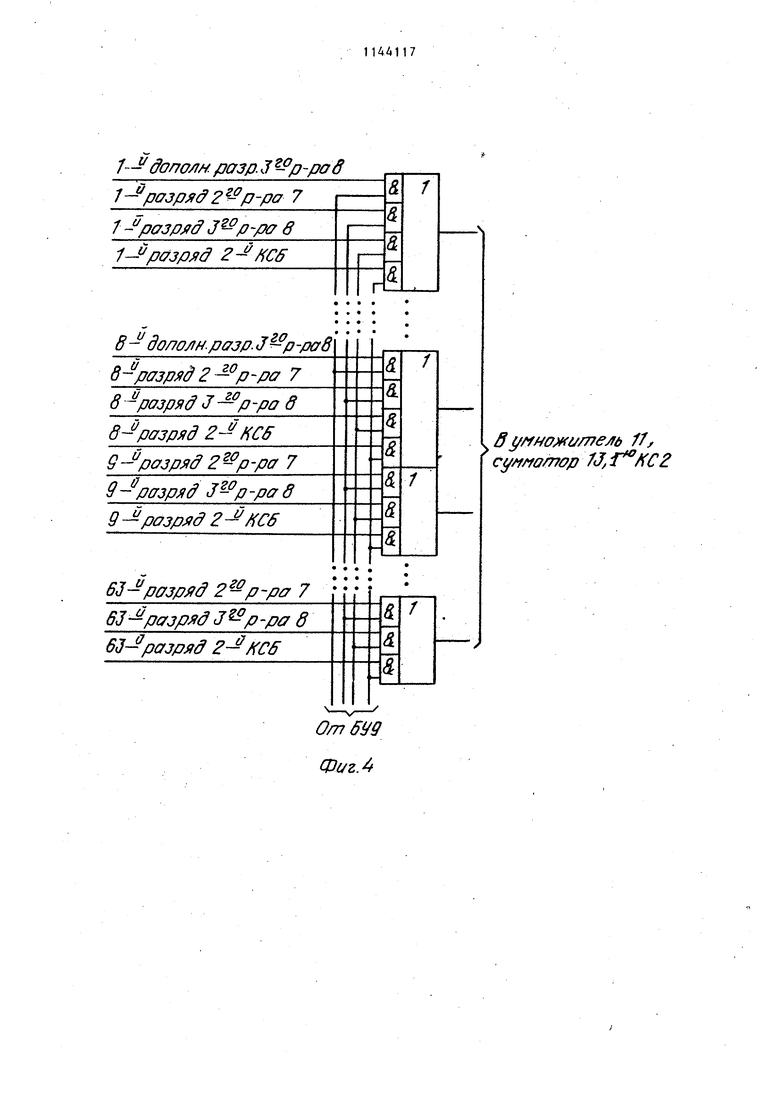

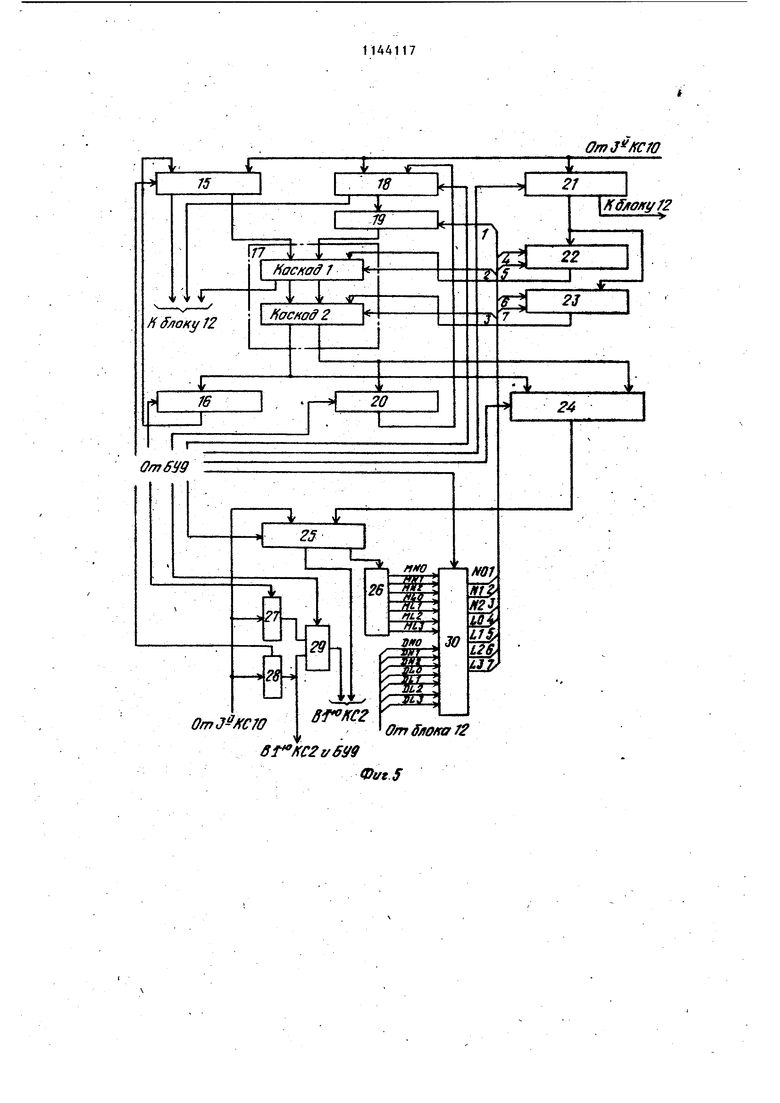

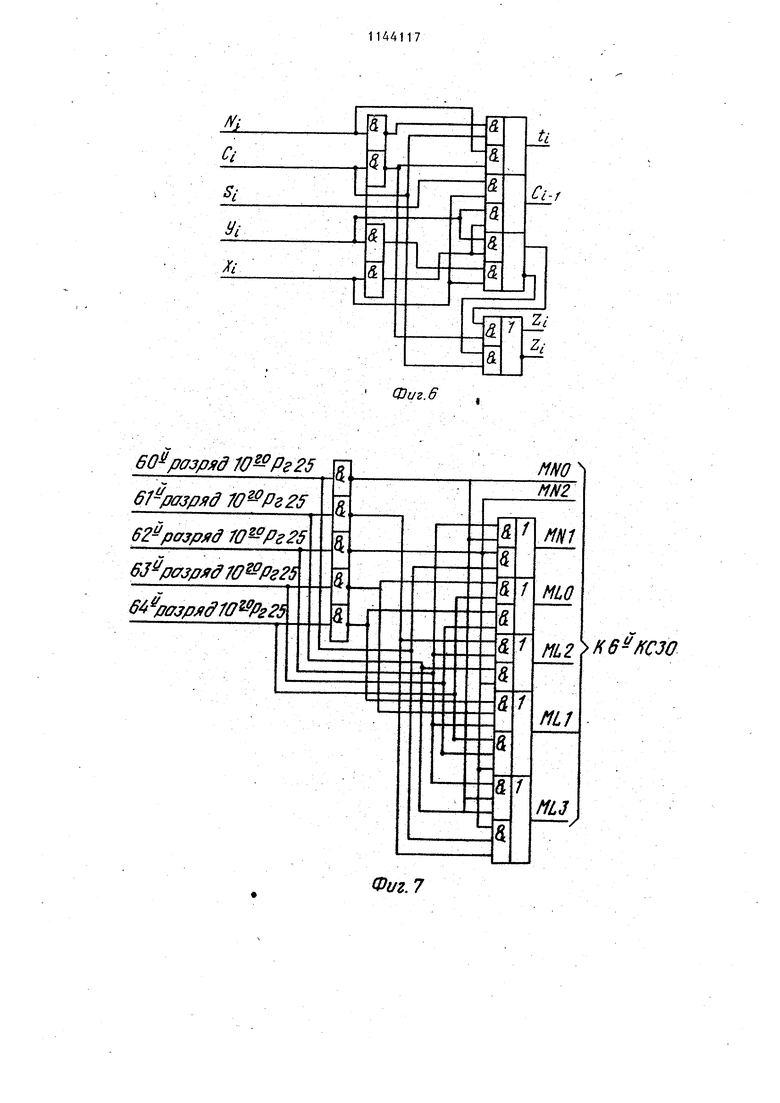

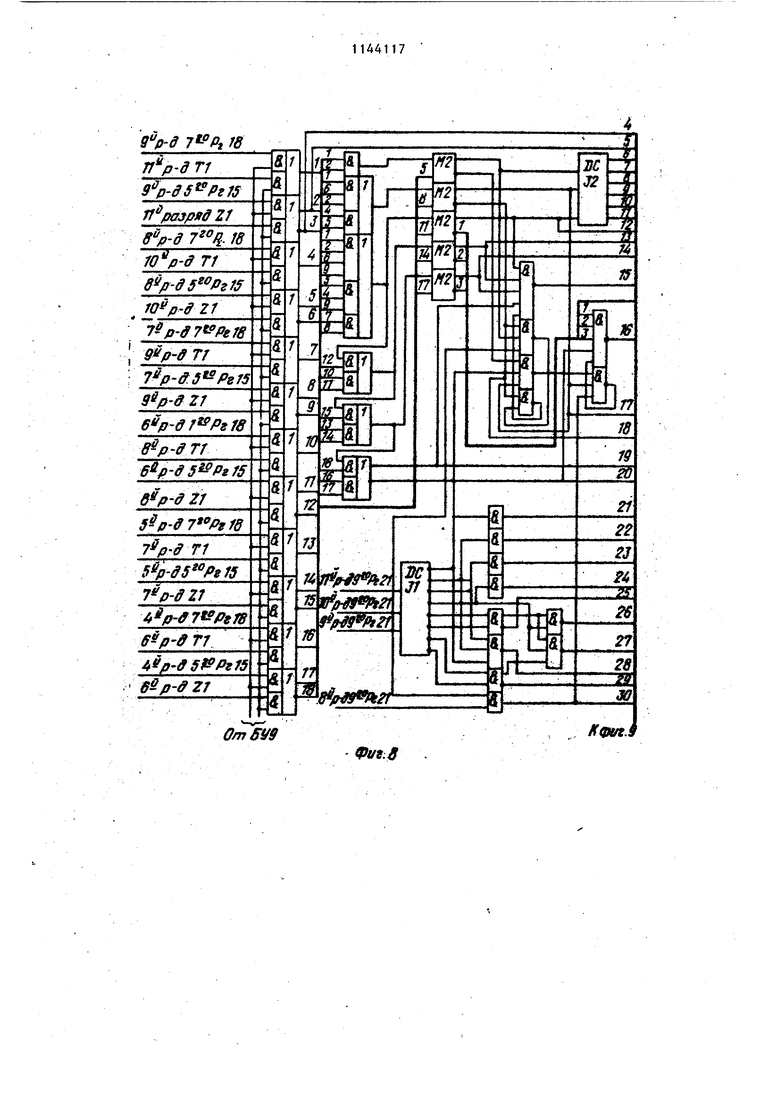

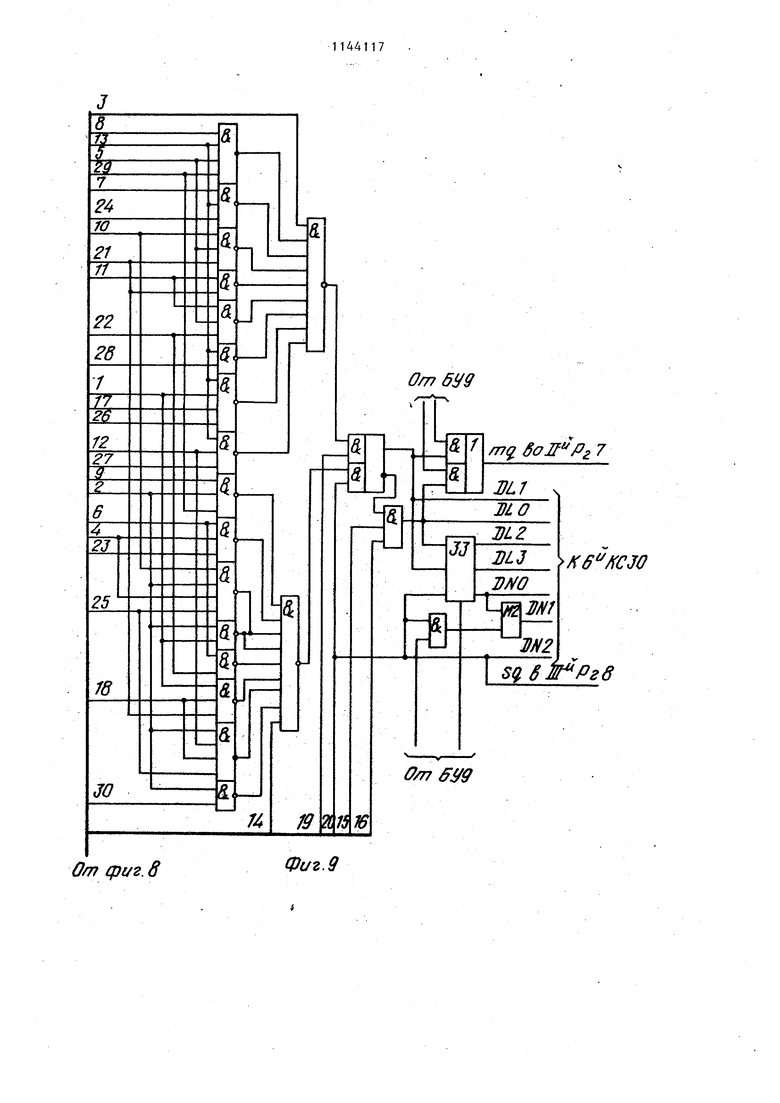

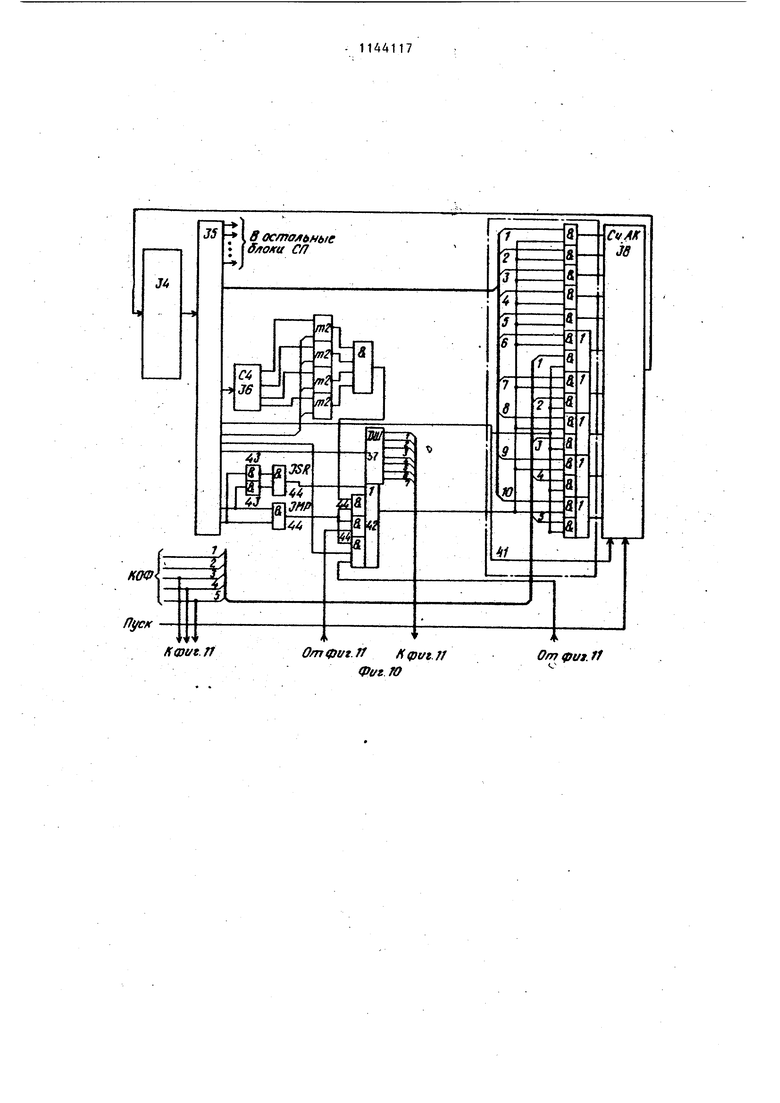

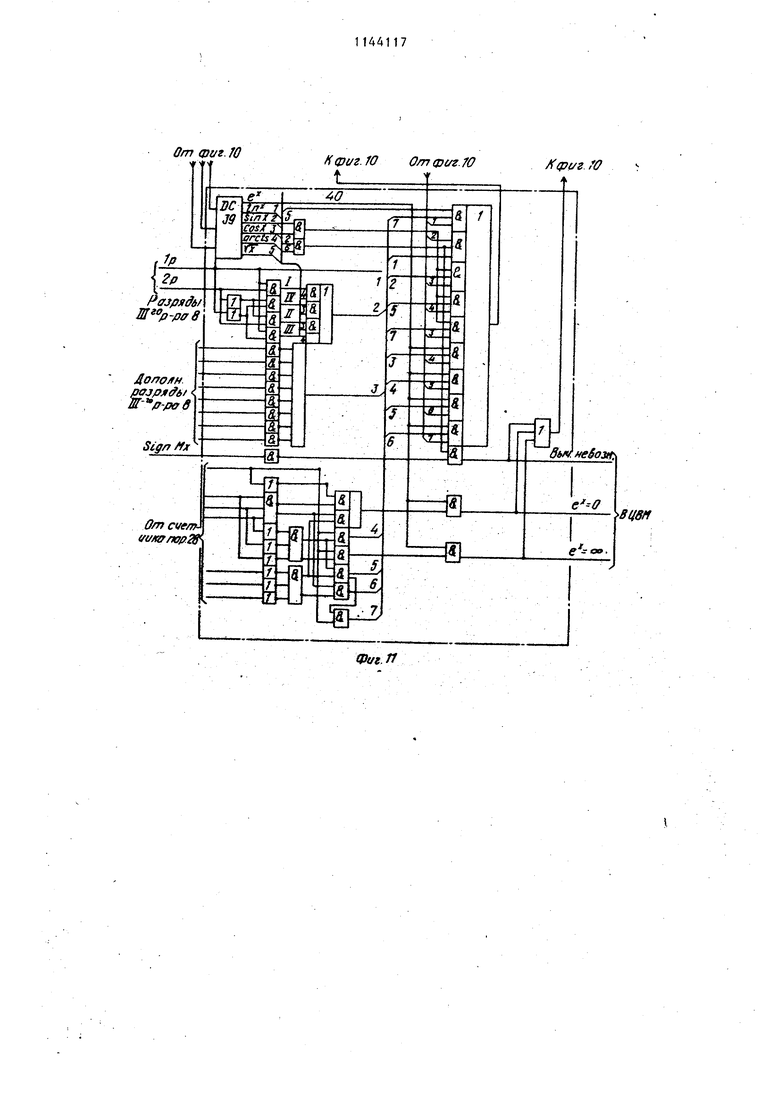

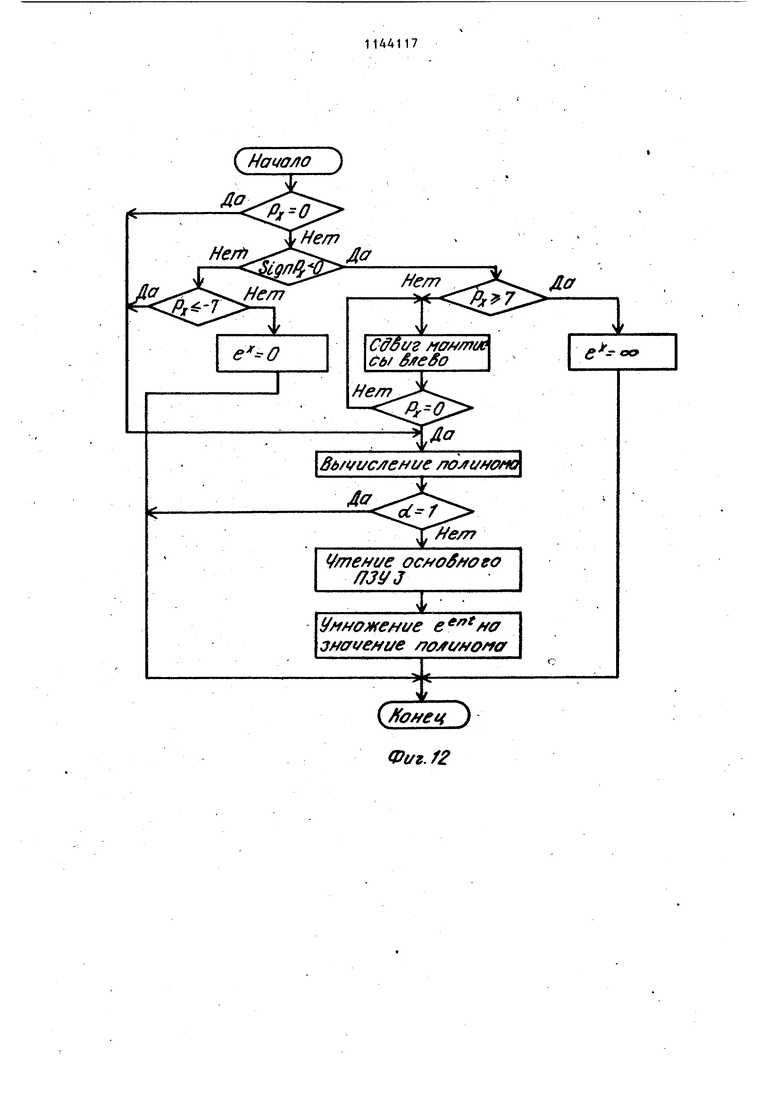

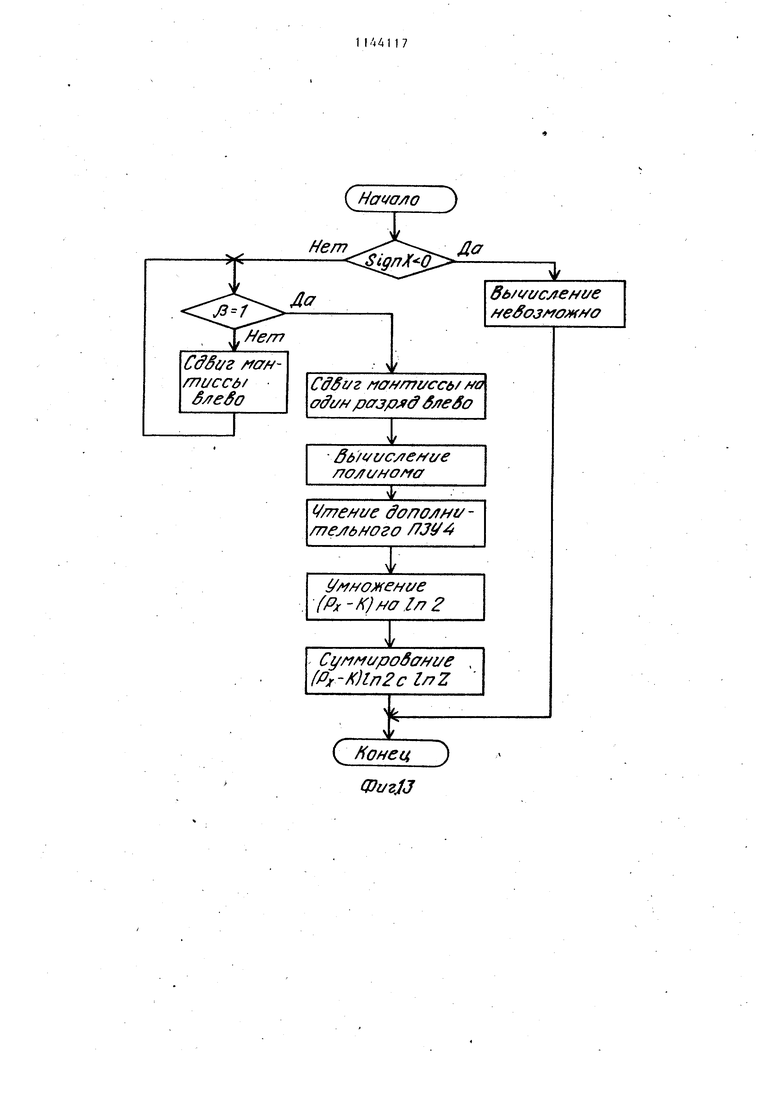

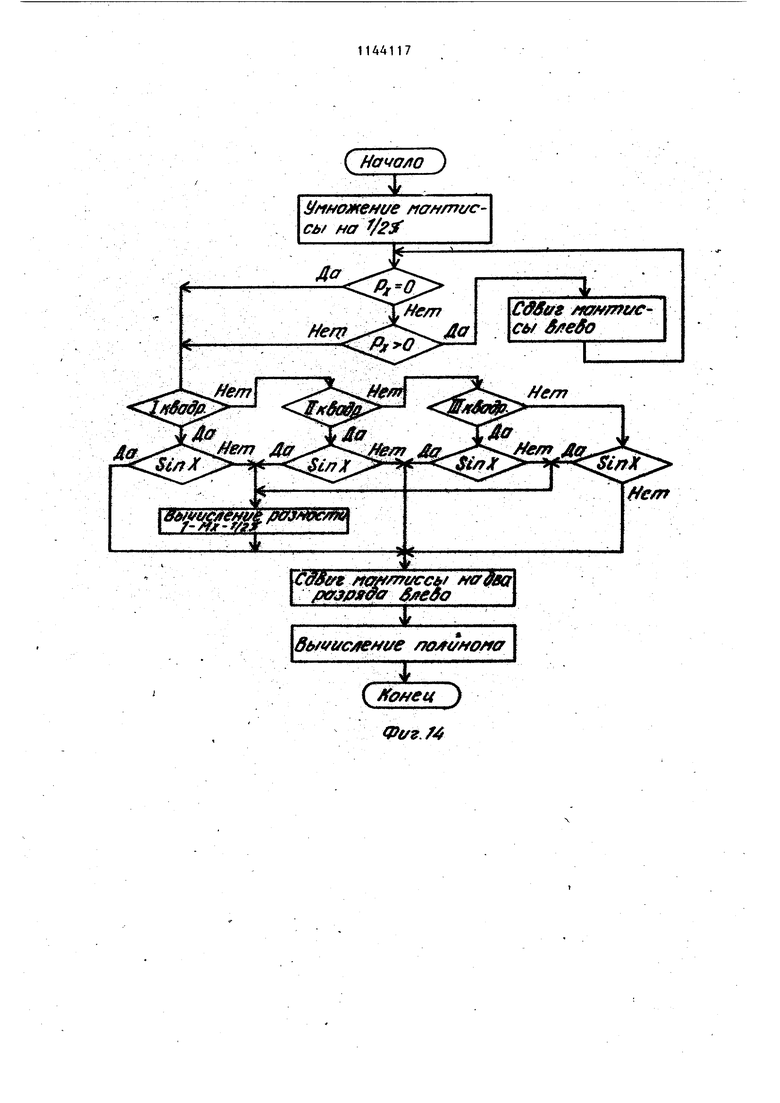

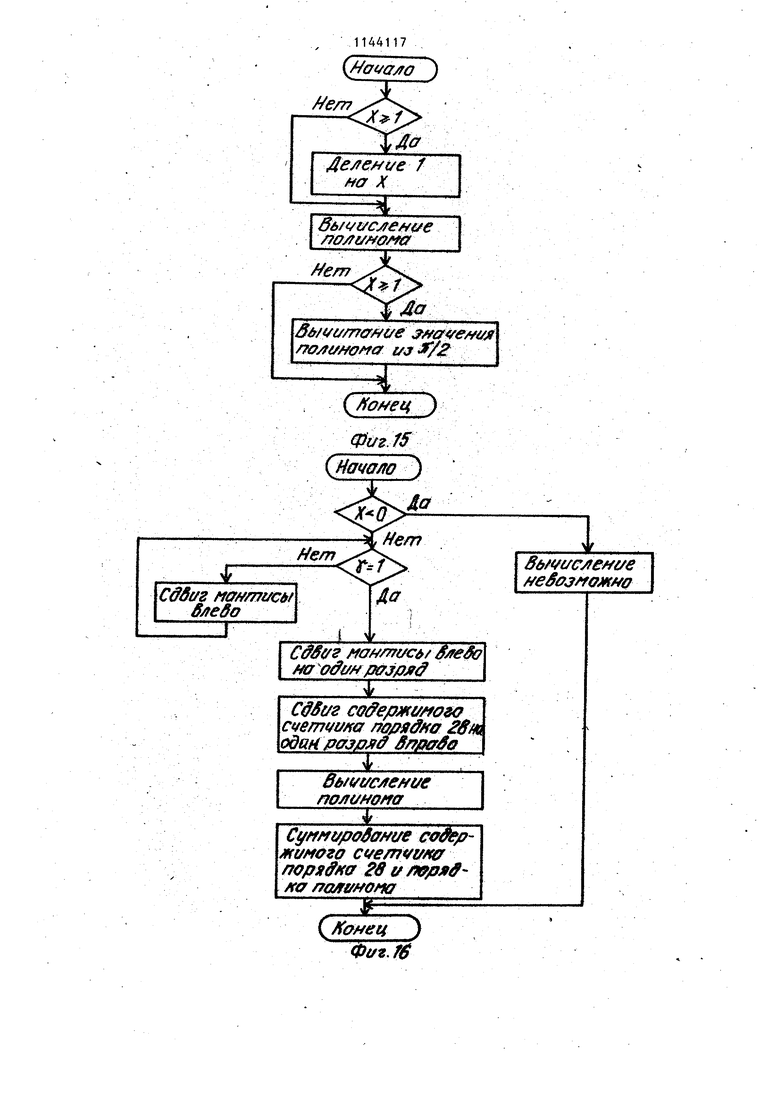

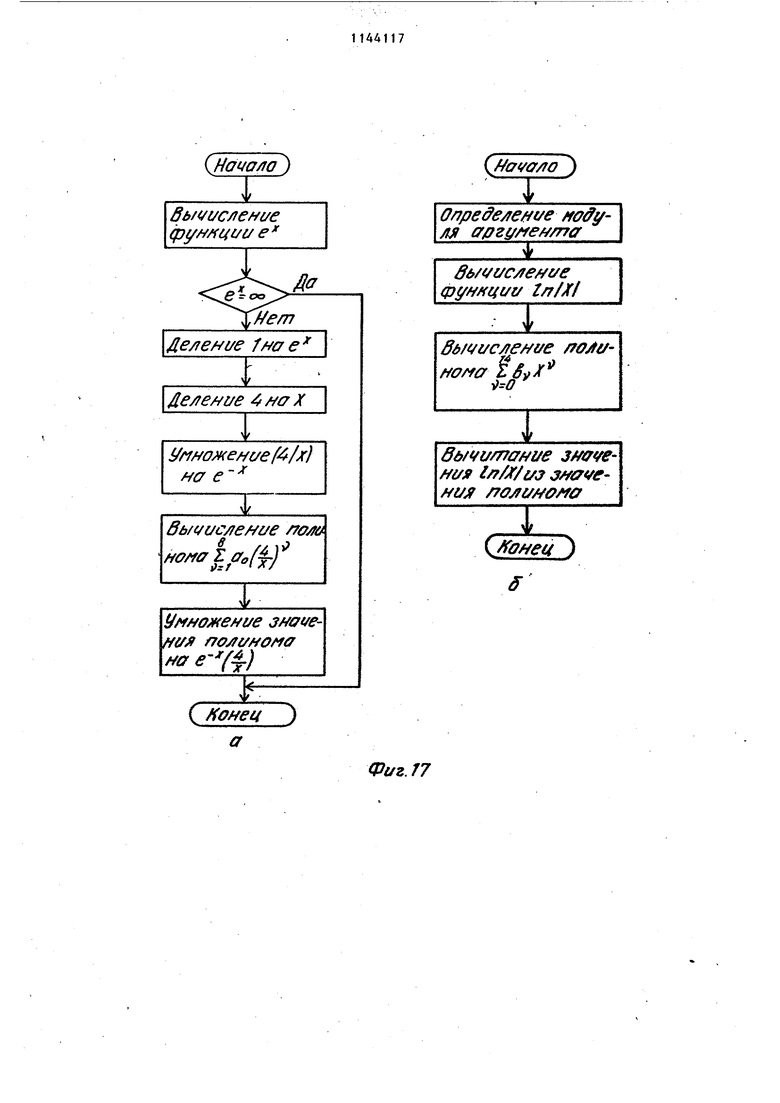

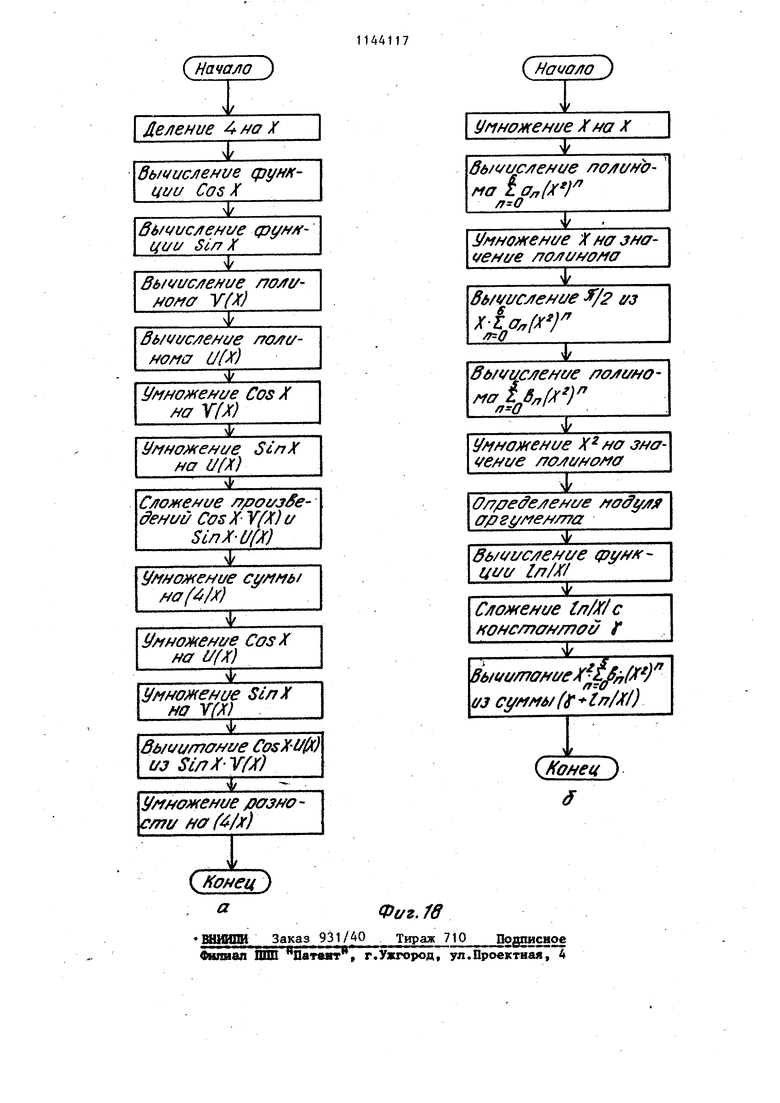

На фиг. 1 представлена структурная схема предлагаемого процессора, на фиг. 2-4 - функциональные схемы коммутаторов; на фиг. 5 - функциональная схема умножителя; на фиг. 6 функциональная схема ячейки матрицы умножителя; нз фиг. 7 - функциональ мая схема перекодировщика умножителя; на фиг. 8 и 9 - функциональные схемы блока деления; на фиг, 10 и 11 - функциональны1е схемы блока управления; на фиг, 12-18 - блок-схемы алгоритмов вычисления функций е (фиг. 12), 1пх (фиг. 13), sin х и cos X (фиг. 14), arctax (фиг. 15) - (фиг. 16), EXPI (фиг. 17), S- (х). С;(х) (фиг. 18).

Специализированный процессор (фиг. 1) содержит регистр 1, коммутатор 2, блоки 3 и 4 постоянной памяти, блок 5 памяти, коммутатор 6, . регистры 7 и 8, блок 9 .управления, коммутатор 10, блок 11 умножения, блок 12 деленияj сумматор 13 и регистр 14.

Коммутатор 2 построен на стандартных микросхемах мультиплексоров (фиг. 2), коммутаторы 6 и 10 .- на элементах И-ИЛИ аналогично на соответствующее число входов (фиг. 3 и 4). Блок 5 памяти объемом 16 слов может быть реализован либо в виде набора регистров, либо на быстродействующих интегральных схемах.

Умножитель 11 (фиг. 5) содержит регистры 15 и 16, матрицу 17,- регист 18, группу 19 элементов Hfe, регистры 20 и 21, коммутаторы 22 и 23, сумматор 24, регистр 25, перекодировщик 26 множителя,, регистр 27 порядка, счетчик 28 порядка, сумматор 29 порядка и коммутатор 30,

Основу умножителя 11 составляет итерактивная неполноразрядная (с целью сокращения аппаратурных затрат) матрица 17. С цельк увеличения быстродействия.матрица17 работает в знакоразрядной (SDj системе счисления, в которой каждая двоичная цифра представлена знаком и модулем (двумя битами) и состоит из двух каскадов SD-вычитателей,

На фиг. 6 показан i-й разряд SD-вычитателя, где Sj - знак разряда уменьшаемого, xj - модуль разряда уменьшаемого, у - разряд вычитаемого в двоичной форме, t - знак разряда разности, Z; - модуль разряда разности. С, - перенос-заем, N: сигнал инвертирования t, j - номер каскада, j 1,2,

Блок 12 деления (фиг, 8 и 9) содержит дешифратор 31 с инверсшл и выходами,- дешифратор 32 и регистр 33

На фиг, 8-10 символом М2 обозиачена схема сложения по iQod2, реали9зуемая стандартной микросхемой, работа которой описьгоается уравнением raod2 T-b + a-b , где а и Ь - вхо ные логические переменные. Блок 9 управления (фиг. 10 и 11) содержит блок 34 постоянной памяти (микропрограмм), регистр 35 (микрокоманд.) , счетчик 36 (степени полино мов), дешифратор 37 (поля микрокоманды), счетчик 38 (адреса микрокоманды) (Сч АК), дешифратор 39 (кода функции), коммутаторы 40 и 41, элемент ИЛИ 42, элемент НЕ 43, элемент И 44. Процессор работает следующим образом. Обозначим совокупность битов /S;, через xj, /t;, Z;/ - через Z. Путем управления инверсией кода знака SD-данньгх можно менять режим работы SD-вычитателя. При NJ О устройство работает как вычитатель. При Nj 1 выход вычитателя инвертируется. Если независимо проинвертировать х, то на вычитателе можно производить сложение: Z -(-X - у) X + у. Инверсия операнда х, подающегося на первы каскад матрицы 17, производится на элементах НЕ 19 по сигналу N0. До начала работы мантисса множимого заносится в регистр 21, а мантисса множителя - в регистр 25. Порядки сомножителей поступают в регистр 27 порядка и счетчик 28 порядка. Порядок произведения формируется на сум маторе 29. Причем порядок аргумента должен заноситься в счетчик 28 порядка. Сумма частичных произведений накапливается при циклической работе матрицы 17. В пределах каждого цикла в перекодировщике 26 множителя (фиг. 7) производится анализ оче редной группы из четырех разрядов множителя с учетом старшего разряда предыдущей группы и выработка набора сигналов, управляющих левым сдвигом множимого на коммутатора;х 22 и 23 соответственно перед подач на матрицу 17 (сигналы MLO, ML1, ML2, ML3, где число указывает вели чину сдвига) и режимом работы SDвычитателей матрицы 17 (сигналы MNO, MN1, MN2), . Набор сигналов из блока 26 муль типлексируется с аналогичным набор приходящим из блока 2 деления, и 1710 снимается с выхода коммутатора 30 в виде N0, N1, N2, LO, il, L2, L3. Каждый цикл работы блока 11 при умножении включает следующие шаги. 1.Анализ очередных четырех разрядов множителя с учетом старшего разряда предьщущей группы и выр аботка блоком 26 сигналов, задающих режимь работы SD-вьгчитателей матрицы 17 и величины левых сдвигов множимого на коммутаторах 22 и 23 перед подачей на матрицу 17, 2.Предыдущая сумма частичных произведений в SD-форме (первоначально нулевая) подается на матрицу 17 с регистра 18 (код знака) и регистра 15 (код модуля); одновременно на матрицу 17 поступает сдвинутое множимое . 3.Полученная на выходе матрицы 17новая сумма частичных произведений в.SD-форме принимается на регистр 20 (код знака) и регистр 16 (код модуля) со сдвигом на четыре разряда вправо. 4.Множитель сдвигается на четыре разряда вправо, содержимое регистров 20 и 16 передается на регистры 18и 15 соответственно. На двух каскадах матрицы 17 в пределах одного цикла производится умножение на четыре разряда множителя. По окончании циклов осуществляется преобразование произведения из SD-формы в двоичную путем вычитания его отрицательной фракции из положительной на обычном комбинационном сумматоре 4. Полученный результат поступает на регистр 25 и может л11бо использоваться вновь в качестве множителя, либо поступит на выход блока 11 умножения . Для вьшолнепия деления кроме оборудования блока 11 используются регистры 7 и 8 и блок 12 деления. I Деление реализуется по методу без восстановления остатка. Частичные остатки вычитаются в SD-форме на матрице 17. При этом функцию SD-вычитателя каждого каскада можно описать так: предыдущий частичный остаток в SD-форме минус соответствующее кратное делителя в двоичной форме равняется новому частичному остатку в SD-форме. Поскольку SDпредставление является избыточным.

1111441

о становится возможным формироваие цифр частного на основе анализа ишь четырех старших разрядов целителя и шести старших разрядов частичного остатка. После каждого цикла 5 работы формируются четыре разряда частного в SD-форме.

На вход блока 12 поступают четыре старших разряда делителя из регистра 21, шесть старших SD-разрядов Ю частичного остатка с регистра 15 (код модуля) и регистра 18 (код знака) и шесть старших SD-разрядов частичного остатка с выхода первого каскада матрицы 17:15

Z. - код модуля

Т - код знака

На выходе блока 12 формируются 20 SD-разряд частного (Sq - бит знака, поступающий в регистр 7;.mq - бит модуля, поступающий в регистр 8); , сигналы управления режимом работы SD-вычитателей матрицы 17 DNO, DN1 25 и DN2; сигналы управления сдвигом делителя на коммутаторах 22 и 23 перед подачей на матрицу 17 DLO, DL1, DL2 и DL3, где число указьшает величину сдвига.30

Набор сигналов управления из блока 12 мультиплексируется с аналогичным набором, приходящим из перекодировщика множителя 26, и снимается с выхода коммутатора 30 в.виде N0, , N1, N2, LO, L1, L2 и L3.

Перед началом деления делимое заносится в регистр 7, а делитель в регистр 8. Производится.двоичная нормализация делителя при сопутст- Q вующих сдвигах делимого влево. Затем делимое передается в регистр М-5, а делитель - в регистр 21. С последнего на вход блока 12 поступает четыре старших разряда делителя.45

Каждый цикл работы блока 11 при делении включает следующие шаги.

. 1. С регистров 15 и 18 на вход блока 12 поступает для анализа щесть старших разрядов частичного 50 остатка в SD-форме (первоначально делимое).

1712

коммутатора 22, Одновременно содержимое регистров 7 и 8 сдвигается дважды на один разряд влево и в освободившиеся младшие разряды записываютс последовательно формируемые в блоке 12 пары бит (mq, Sq), кодирующие две SD-цифры частного.

7 и 8.

По окончании всех циклов осзт ествляется передача накопленного SD-. частного с регистров 7 (код модуля) и 8 (код знака) транзитом через матрицу 17 на комбинационный сумматор 24, где оно преобразуется подобно SD-произведению в двоичную форму и запоминается в регистре 25.

Коммутаторы 22, 23 и 30 построены на схемах И-ИЛИ аналогично коммутаторам 6 и 10.

Сумматор 13 представляет собой обычный двоичный сумматор, на регистры которого слагаемые поступают последовательно из коммутатора 10.

Рассмотрим вычисление ЭФ из аппйратно реализуемого набора. Вычисление ЭФ в процессоре разделяется на два этапа. На первом этапе диапазон изменения аргумента функции св одится к интервалу Го, 1 . На втором этапе происходит собственно вычисление функции. Приведение аргу мента к интервалу вьшолняется отдельно для каждой функции.

Функция е .

Пусть представление, чисел ЦВМ. находится, в диапазоне 2 /. Тогда для функции е диапазону изменения аргументов соответствуют области изменения функции:

13

о:,-.2

6

, Этим трем областям можно соотнести два интервала изменения аргумента. для fa III области Гх/- М6п2 для II области /X/ J. Nln2 процессор генерируе сигнал Вычисление невозможно. Вычисления проводятся только для второй области изменения функции. Максимальный порядок аргумента при этом L-P,-eo,jN. (2) В ЕС ЭМВ N t 256, тогда I 8, Для вычисления функций е в указанном диапазоне необходимо выделить целую часть аргумента, вычислить функции от обеих частей аргумента и затем перемножить полученные значения:, х Entx е е е где е- функция от целой части ,.ent:( аргумента; е - функция в дробной части аргумента. . Действия по приведению аргумента к интef вaлy начинаются при поступлении аргумента в регистр 1. Если порядок аргумента не равен нулю, то . производятся сдвиги мантиссы аргумен та с коррекцией порядка. Для этого мантисса аргумента ерез коьо утаторы 2 VI Ь передается в регистр 8, а порядок аргумента - в счетчик 28 порядка. Сдвиги мантиссы продолжают ся до равенства порядка нулю. Из ре гистра 8 сдвинутая мантисса через коммутатор 10 передается в коммутатор 2, после чего происходит обраще ние к блоку 3. Содержимое дополните ных разрядов регистра 8 (целая част аргумента),полученное в результате сдвига, служит адресом к блоку 4, где кривится величина е , Функция 1пх. Приведение аргумента функции 1пх к интервалу 0, lj основано на следукидем. Пусть аргумент представлен в виде ,РХ () к-Мх-2

1144117 /

14 / . где

MXмантисса аргумента;

РХ порядок аргумента. Логарифмируя равенство (1), чим Cnx .en2. . Имеет место равенство. Enw, Bn(+z), О с Z 1; Z - и - 1. t . Mjj - мантисса сдвинутая, таким образцом, мокет быть представлена кодом 1, Z, , Z,2 2.„ , где Z( - двоичная цифра числа. : Сдвиг вьтолняется до первой ситуацни, при которой перед запятой устанавливается единица, т.е. можно записать к (7) где: К число сдвигов до получения . кода (7). Таким образом, ем 6п(Мх-2)+Рх-еп2 епМх-1«6г12 + . ri(l4Z)p,-kUiZ . .(8) Аргумент функции In х передается из регистра 1 в регистр 8, где сдвигается до вьзделения из мантиссы старшей единицы, с соответствующей коррекцией порядка. Величина. (Р„ - К), полученная на счетчике 28 порядка, служит адресом к блоку 4, где хранятся произведения (P,j- К)1п 2. Функция sin X, Сведение аргумента фу нкции sin х к интервалу О, ij основано на соотноюейин (i ainx бш (2ir kЧ р).6i л ( , где К - целое число; Cf - переменная в интервале О, 27, 2(x.enix) 2( ( где О Z t. Два старших разряда величины Z указывают .номер квадранта, в котором находится угол Cf . Представим величину sin Cf как Sintf-6ili2ir «6in|- f , где О V 1. Вычисление 91П V в зависимости т к адраита, в котором находится ргумент, вьтолняется по формулам 5;n|v Iквадрант. -6;n|-(-vi IIквадрант -Sin-gV IIIквадрант Sin-K I-V) IV квадрант Переход к функции cos х осуществляется по формуле . /ЧГ С05Х 51п| - -х) . В этом случае формулы вычисления « ., имеют вид: -9;4n- V I квадрант II квадрант -SinlV -( III квадрант 6;4ii-v) -. 1Г IV квадрант (13) Приведение к интервалу начинаетс с умножения мантиссы аргумента М, н 1/2i в блоке 11. Если порядок произ ведения больше нуля., то вьзделяется целая часть сдвигами .влево с коррек цией порядка, т.е. получаем перемен ную Z. Сдвиги выполняются на регист ре 8, В зависимости от номера, квадранта и вида функции /sin х/ или /cos X/ из единицы вычитается величина 1 (формулы 12 и 13) в сумматоре 13. Затем для-перехода от переменной Z к переменной v полу ченная разность.или Z сдвигается на два разряда влево. Функхщя arctg X. В этом случае приведение аргумен та к интервалу jjO, 1J основано на известной формуле arctgx x.t arc-t4x Ч(т) - -arct Поэтому аргумент -передается в бл ке 11, где вырабатывается величина 1/х. На этом действия по приведению аргумента заканчиваются. Функция -fST.. Приведение функции -{ЗГ к интерв лу р, l основано на соотношении / Ч Р (15 . -2 .Р,-М,, где К - число сдвигов мантиссы .исхо ного аргумента до первой си 17If, туации, при которой перед запятой устанавливается единица 1, Z. , i-it ; Z - величина в ттервале СО, О Величина Hi + Z аппроксймируется полиномом 4-й степени, М,, - мантисса результата вычисления + z ; Р„ - порядок результата вычисления --J1 + Z. Действия по вычислению -JjT начинаются с анализа знака мантиссы аргумента . Если знак мантиссы отрицательный, то формируется сигнал Вьгаитание невозможно. Если знак мантиссы положительньш, то анализируется, велиЕсли Р чина порядка аргумента Е„ 0, то начинается вычисление полинома. Если Р ф О, то начинается сдвиг мантиссы аргумента влево с коррекцией порядка до появления в старшем разряде регистра 8 единицы и затем еще один сдвиг влево. После предварительной обработки аргумента начинается вычисление степенного ряда, аппроксимирукнцего функцию. Степень ряда одинакова для всех ЭФ, входящих в набор, и равна четырем. Ряд вычисляется, по схеме Горнера:/ I ,P(xl ao+x{a,,q4x) ( Для этого сдвинутая мантисса аргумента из регистра 8 передается в блок 11, куда из блока 3 затем поступает коэффициент а. Произведение передается в сумматор 13, где складывается с а. Затем с выхода сумматора 13 полученная сумма через коммутаторы 2, 6 и 10 поступает вновь в блок 11. Результат вычислений передается либо в регистр 14, либо заносится в блок 5. После вычисления полинома необходимо выполнить действия по формулам (3), (8), (15) и (14): для функции е - обращение к блоку 4 и умножение е на Р(х); для функции In X - обращение к блоку 4 и сложение (Pj,-k)ln2 с Р(х); для функции -SX - сложение порядков и для функции arctg х Mlвычитание Р (х) из -5- . Остальные элементарные функции вычисляются микропрограммно, используя известные в математике соотношения между ЭФ. 17 Специальные функции, реализуемые микропрограммно, вычисляются по следукнцим. алгоритмам. Показательный интеграл. Для /X/ E,n,«, e-«(t|.,lf, для ы 4Е,р(,.ёе,-«. Вначале по программе вычисляется элементарная функция е или In х. Затем находится величина полинома и значение искомой функции. Промежу точные результаты вычислений записы вйются в блок 5 памяти. Интегральньш синус и косинус. Для /х/- 4 S;(.VUVs;nx . с; Ul X vuVcoe X иЫ , « |oMTl.(.bU(4 Для /х/; 4 ч(хУ-|4х|:а„{х). Сч м Л Ci(x).(xv-x.i: ъ„(x В этом случае действия по вычи.слению функции аналогичны предыдущим. Все степенные полиномы вычисляются по схеме Горнера, а их коэф фициенты хранятся в блоке 3. В работе блока 9 использу{отся три типа микрокоманд (МК); операционная МК, которая предна значена для управления работой бло ков процессора; МК безусловного пе рехода (ISR), используемая при вычислении микропрограммно реализуем функций; МК условного перехода (IMP), используемая для перехода по логическим условиям, которые вы батываются комбинационньми схемами блока 9 управления. На вход блока 9 поступают сигнал Пуск, код задания функции (К знак мантиссы ар1 умента от ЦВМ, по рядок а.р гумен та со счетчика 28 порядка, дополнительные разряды, пер вый и второй разряды регистра .8. Р 718 , бота блока 9 начинается при поступлении сигнала Пуск. По этому сигналу начинает работать счетчик 38 Сч АК в режиме прямого счета. Адрес микрокоманды поступает на вход блока 34 микропрограмм, выбранная микрокоманда записьтается в регистр 35 микрокоманд. Затем в регистр 1 счетчик 28 порядка записывается аргумент. КОФ записывается в счетчик 38 Сч АК с помощью специально предназначенного для этого разряда в операционной МК и является адресом первой МК вычисления данной функции. После этого начинаются действия по предварительной обработке аргумента по указанным алгоритмам. Сигналы е О, е 00. Вычисление невозможно (для функции In X и ) вырабатываются при некотором значении аргумента и передаются в ЦВМ. При наличии одного из этих символов происходит переход к микрокоманде останова и СП прекращает свою работу. Коммутатор 40 предназначен, кроме того, для анализа состояния разрядов блока 3, регистра 8 и счетчика 28 порядка во время предварительной обработки аргумента. Сигнал перехода вьфабатывается сравне €ием на элементах И и ИЛИ состояния выходов коммутатора 40 и результата дешифрации поля МК IMP на дешифраторе 37. После предварительной обработки аргумента начинается вычисление полинома 4-й Степени. Также при вычислении специальных функций необходимо находить значение полиномов 5, 6, 8, 9, 10, 14-й степеней. Для этого введен счетчик Зб степени полинома. Текущее состояние счетчика 36 при вычислении полинома сравнивается с информацией, записанной в поле МК 1НР. Равенство величин определяет окончание вычисления полинома и переход по соответствукнцему адресу. . Останов блока 9 производится МК ISR по адресу останова. Таким образом, использование указанных блоков и связей между ними позволяет упростить схему специализированного процессора.

из ii6ff Т

Т,.

7роз ряд Рг орг( /

f/}ff3p( i/fif o t/rne// //

Грозряд Т /fC

.7разряд ci/M/ia/77opcf 7J

7Jrlaзpяд отЛЗУЗ

1 раз ряд дол.

7розр д . порядно 28

W роз ряд Рг аргум. /

10 рОЗРЯ(

Ю разряд (С rff

ЮPffjp c(j/wcrm7j

OpaJSЯд OШ/73УЗ

Ю разряд dof7.f7Jf/4

Юрузряд с(/е/7. порядла

f1 разряд apai/. / Празряд (/ffHo t//77. W

77разряд J /{СЮ

77разряд cy /iomopff J

17розряд осн. /7J{/J 77рсгзряд ол. ПЗУ4

7 2 J

воен. , f7Jf/4

4 5 6 7 А1 А2 А

В оггер. 5f/2-f / C5

Фиг 2

От 6У9 CPi/z.J

6о2-- Рг7,, J- КС 70

3 i/f HO tf/TfeM /Л

ry/r/W/77 7/ /(

Гг От6У9

OmJ ffCrO

ef /fC2t/Sy9

ffmJ /fCfO

Omff/io/arJ2

Фиг 5

Фиг.6

K6 ffC30

Фиг. 7

Фиг.Л

Фиг. 9

От ф .8

От фиг. П K(put.JJ

.TJ

От фаг. ff (pi/e Ю

Фае. Л

Bb/vt/c/reHt/e /fo t/ffOffe

/77€f t/e oc oS/foeo

y/iHo eHt/e yHffvefti/e /jojft/ offor Неш Cffot/г w/w сь/ SjreSo Нел7 4ff

He/7

Фиг. f2 w

Нет C(S(/Z /%7/VCff f/г ffaf/mi/ccb// o /7 LfCC6/ o i/ pcrjp ff S/feSo

dd/f/UC/fe/Y{/€

лоАс/но/ а

or7O/fHt/ /7 eyr6ffO3o /7Jf/4

л ожен&/€ (Px-К) HO 1л 2

(/po6ff i/e , (Р;с-Ю1п2с 1л2

С оиец ) Фt/гJJ Bb/t/i/cACHf/e

(ava/fo e/7

4e/ref t/e f fia X

&6/f/t/CAef(/€

/ O/fVffQffCf

f/em

S /iii/mowif //efffe f/

Ц

AfeT

ffaf//77tfc f ёлебо

J

ffOff/7Tf/c /ff/re

(/ffpffjpjr

coffep t/ffoso ct/emvt//fa /my d/fff xe odttfiffgjffjfff Sffffff e

Bb/(/t/c cf/t/e

nO UHOffOf

Ct/fffft/pa fffftre ef /7тин го cvern ifffff nopxfffta 9 f/ /9ff/j ff/(a /JWfffHom

(f(OHet4 j (fitftfS

Bb f ifc/ie e/e / eS03ffOM(

0t/z.f6

( }

r

Bbf /t/c/i€M{/e (/г/ e

(j ovff/ro

Ofjpede efff/e /toffy/fjf ffffzy ef//r7ff

Делен1/е €

/le/fef i/e 4 на X

86/f/i/c/refit/e

ф((Щ/1/ //7///

Bd/t t/c/ie i/e /fOAi/ // f f « ffff/ ff

V

0

/nнoжe/ c/ef4/xl на e

6b/vuc/feHi/e /го/к/

jM

HO/fff Г

рг/ /

yffHOJf e t/e jffovefflfjf f7O/ft/ffOffff

we-(}

i

( /( J

вь/t/u ffHi/e 3fffftfsfft/Я /ffft eHujf ло/ft/ oAfa

I

(jfOHCU

/f

Е7г/г. 77

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Оранский A.M | |||

| Аппаратные методы в цифровой вычислительной технике | |||

| Минск, изд-во Белорусского университета, 1977, с | |||

| Гидравлическая или пневматическая передача | 0 |

|

SU208A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Повышение эффективности вычислений использованием табличных предпроцессов | |||

| - В кн.: Теория и применение математических машин | |||

| Минск, изд-во Белорусского университета, 1972, с | |||

| Система механической тяги | 1919 |

|

SU158A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-03-07—Публикация

1983-07-19—Подача