входом коммутатора адресных кодов каждого блока хранения и преобразования информации, второй выход каждого одноразрядного блока хранения и преобразования информации, кроме последнего, каждого блока хранения и преобразования информации соединен с первым информационнымвходом последующего одноразрядного блока хранения и преобразования информации, втсэрой выход последнего одноразрядного блока хранения и преобразования информации каждого блока хранения и преобразования информации, кроме последнего, соединен с информационным входом соответствующего регистра и с первым информационным входом первого одноразрядного блока хранения и преобразоват ния информации последующего блока хранения и преобразования информации, второй выход последнего одноразрядного блока хранения и преобразования информации последнего блока хранения и преобразования информации соединен с первым информационным входом первого одноразрядного блока хранения и преобразования информации первого блока хранения и преобразования информации и -с информационным входом соответствующего регистра, второй информационный вхо первого одноразрядного блока хранения и преобразования информации первого блока хранения и преобразования информации соединен с первым информационным входом устройства, третий выход каждого одноразрядного блока хранения и преобразования информации каждого блока хранения и преобразования информации соединен с входом блока выявления нуля, выход которого является первым выходом устройства, четвертый выход каждого одноразряд-, ного блока хранения и преобразования информации каждого блока хранения и преобразования информации, кроме последнего, соединен с вторым инфор- мационным входом первого оДноразрядНого блока хранения и преобразования информации последующего блока хранени и преобразования информации и соединен с вторым выходом устройства, тре тий информационный вход первого одноразрядного блока хранения и преобразования информации соединен с четвертым выходом второго и вторым информационным входом третьего одно- . разрядного блока хранения и преобра зования информации, второй информационный вход ; второго однораэрядного блока хранения и преобразо вания информации соединен с четвертым выходом первого одноразрядного блока хранения и преобразования ин-. формации, третий информационный вход второго одноразрядного блока хранения и преобразования информации сое динен с четвертым выходом третьего и вторым информационным входом четвертого одноразрядного блока хране(ния и преобразования информации, третий информационный вход третье го одноразрядного блока хранения и преобразования информации соединен с четвертым выходом четвертого одноразрядного блока хранения и преобразования информации, третий информационный вход четвертого одноразрядного блока хранения и преобразования информации каждого блока хранения и преобразования информации, кроме последнего, соединен с четвертьом выходом первого одноразрядного блока хранения и преобразования информации последующего блока хранения и преобразования информации, третий информационный вход четвертого одноразрядного блока хранения и -преобразования информации последнего блока хранения и преобразования информации соединен Ь вторым информационным входом устрой ства.

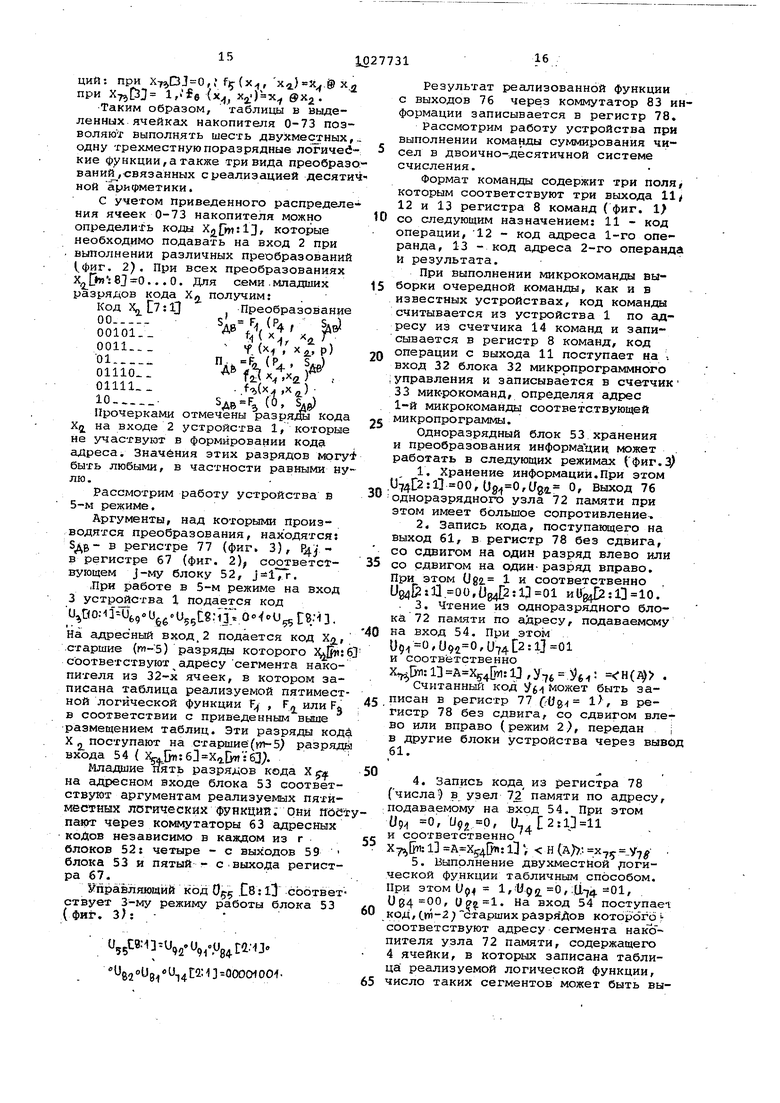

3. система по пп. 1 и 2, о т личающаяся тем, что кажда1й одноразрядный блок хранения и преобразования информации содержит узел памяти, два регистра, коммутатор информации, первый и второй коммутаторы адреса и узел выявления переноса, причем управляющие входы узла памяти, регистров, ком1« та-: торов информации и адреса соединены с управляющим входом блока/ адресный вход блока соединен с первыми информационными входами первого и второго ксячмутаторов адреса, с ад зесным входом узла памяти и с выходами первого и второго коммутаторов адреса, второй информационный вход первого коммутатора адреса соеданен с выходами первого и второго регистг ров информационным входом узла памяти, первым и вторым входами узла выявления переноса, первым и третьим выходами блока, вюрой информационный йход второго коммутатора ajCQJe- са соединен с третьим входом узла выявления .переноса и первым информационным входом блока, выход узла выявления переноса соединен с вторым выходом блока, йыход узла памяти соединен с информационным входом второго регистра, первым информационным входом коммутатора информации и четвертым выходе блока, второй и третий информационные входы коммута ора информации соедине- : ны соответственно с вторым и третьим информационными входами блока, выход коммутатора информации соединен с информационным входом первого регистра, выход второго регистра соединен с первым выходом блока. Изобретение относится к вычисли тельной технике и предназначено дл хранения и преобразования информации в цифровом виде. Известно устройство, в котором преобразование цифровой информации организовано на базе матриц магнит ных сердечников flJ. Недостаткомустройства является сравнительно низкЯё технологичность надежность и быстродействие вследствие невозможности применения в ни полупроводниковых больших интеграль ных схем, отличающихся наиболее выт сокой технологичностью, быстродействием и сравнительно малой стоймостью. Известно устройство, в котором хранение оперативной информации и преобразование с помощью таблиц осуществляется на базе единого накопителя полупроводниковых запоминающих блоков L2J. Недостатком известного устройств является то, что оно может выполнять арифметические операции только в двоичйой системе счисления, что существенно снижает производительность при обработке информации, представленной в двоично-:деся гичной системе счисления. Цель изобретения - увеличение производительности устройства. Поставленная цель достигается те что в систему, содержащую регистр команд, счетчик команд, мультиплексор кода адреса, два коммутатора и блок микропрограммного управления, первый выход регистра команд соединен с первым входом блока микропрограммного управления, выход которог соединен с управляющими входами мул типлексора кода адреса, регистра команд, счетчика команд и двух коммутаторов, второй и третий выходы регистра команд соединены с первым и вторым информационными входами мультиплексора адресных кодов соответственно, первый информационный вход которого соединен с выходом счетчика .команд, содержит устройство хранения и преобразования информации, адресный вход устройства хранения и преобразования информации соединен с выходом мультиплексо ра адресных кодов, управлянвдий вход с выходом блока микропрограммного управления, первый выход - с вторым входом блока микропЕЮГраммного управления, второй выход - с инфор:мационными входами регистра команд счетчика команд, с первыми информационными входами первого и второго коммутаторов и является выходом сис темы,выходы первого и второго коммутаторов соединены соответственно первьаи и вторым инфоЕ 1ационными входами устройства хранения и преобразования информации, вторые HH- формационные входы первого и второго коммутаторов являются первым входом системы, четвертый информационный вход мультиплексора адресных кодов соединен с выходом.блока микропрограммного управления, а пятый информационный вход является вторым входом системы. Кроме того, устройство хранения и преобразования информации содержиф блок выявления нуля и г блоков хранения и преобразования информации, каждый из которых содержит четыре одноразрядных блока хранения и преобразования информации, коммутатор адресных кодов и одноразрядный регистр, причем управлякядие входы кгикдого одноразрядного- блока хранеНИН и преобразования информации каждого блока хранения и преобразования информации соединены с управляющим входом устройства, и с .управляющими входами регистра и KOMf мутатора адресньлх кодов каждого блока хранения и преобразования информации, выход регистра каждого блбка .хранения и преобразования инфор-, мации соединен с первым информационным входом соответствующего . кололутатора адресных кодов и с первьи вы-;ходом каждого одноразрядного блока хранения и преобразования информации соответствующего блока хранения и преобразования информации, адресный вход которого соединён с выхо- . дом соответствующего коммутатора адресных, кодов и со старшими разрядами адресного входа устройства,, младшие разряды которого соединены с вторым информационным входом коммутатора адресных кодов каждого блока хранения и преобразования информации, второй выход каждого одно-разрядного блока хранения и преобразования информации, кроме последнего, каждого блока хранения и преобразования информации соединен с первым информационным входом последующего одноразрядного блока хране-ния и преобразования информации, второй выход последнего одноразрядного блока хранения и преобразования информации каждого блока хранения и преобразования-Информации, кроме последнего, соединен с информационным входом соответ.ствующего регистра и с первым информационным входом первого одноразрядного блока .хранения и преобразования информации последующего блока х ранения и преобразования информации, второй выход последнего одноразрядногоблока хранения и преобразования информации последнего блока хранения . и преобразования информации соединен с первым информационным входом первого одноразрядного блока хранения и преобразования информации первого блока хранения и преобразования информации и с информационным входом соответствующего регистра второй информационный вход первого однораз рядного блока хранения и преобразЬ вания информации первого блока хранения и преобразования информации соединен с первым информационньйи входом устройства, трети.й выход каж дого одноразрядного блока хранения и преобразования информации каждого блока хранения и преобразований информации соединен с входом блока выявления нуля, выход которого является первым выходом устройства, четвертый выход каждого одноразрядного блока хранения и преобразования информации каждого блока хранения и преобразования. инфб мации, кроме последнегр соединен с вторым информационным входом первогб одноразрядного блока хранения и npeобразования информации последующего блока хранения и преобразования информации и соединен с вторым выходом устройства, третий информационный вход первого одноразрядного блока хранения и преобразования информации соединен с четвертым выходом второгЪ и вторым информационным входом треть его одноразр.ядного блока хранения и преобразования информации, второй информационный вход второго одноразрядного блока хранения и преобразования информации соединен с четвертым выходом первого одноразрядного блока хранения и преобразования информации, третий информационный вхой второго одноразрядного блока хранения и преобразования информации соединен с четвертым выходом третьего и вторым информационным- входом ч твертого одноразрядного блока хранения и преобразования информации, третий информационный вход третьего одноразрядного блока хранения и преобразования информации соединен с четверть выходом 1етвертого одноразрядного блока хранения и преобразования информации, третий информационный вход четвертого одноразрядного блока хранения и преобразования информации каждого блока хранения и преобразования информации, крс ме последнего соединен с четвертый выходом первого одноразрядного блока хранения и преобразования информации последующего блока хранения и преобразования информации, третий информационный вход четвертого одноразрядного блока хранения и преобт разования информации последнего блока хранения и преобразования информации соединен с вторам информационным входом устройства. Кроме того, каждый одноразрядный блок хранения и преобразования инфар мации содержит узел памяти, два регистра, коммутатор информации, первый и второй коммутатора адреса и узел выявления, переноса, причем управляющие входы узла памяти, регистров коммутаторов, информации и адреса.соединены с управляющим входом блока, адресный вход блока соедйнен.с первыми информационными входами первого и второго коммутаторов, адреса, с адресным входом узла памяти и с выходами первого и второго коммутаторов адреса, второй .информационный вход первого коммутатора адреса соединен о выходами первого и второго регистров информахщонным входом узла памяти, первым и вторым входами узла выявления переноса, первым и третьим выходами блока второй информационный -вхЬд второго коммутатора аДрера соединен с третьим входом узла выявления переноса а. nepBbtti информационным входом блока, выход узла выявления переноса соединен с вторьа выходом блока, выход узла памяти соединен с информационгдлм входом второго ре.« гистра, первым Информационным входом коммутатора информации и четвертым выходом блока, второй и третий информационюае входы коммутатора информации соединены соответственно с : вторым и третьим информационными входами блойа, выход коммутатора информацин соединен с информационным входом первого регистра, выход второго регистра соединен с первым выходом блока, , На фиг. 1 представлена структур-: ная схема системы для выполнения команд десятичной арифметики табличным способом; на фиг. 2 - структурная схема устройства хранения и преобразования информации на фиг.3 структурная схема одноразрядного блока хранения и преобразования информации j на фиг. 4 - структурная схема блока выявления нуля; на фиг,6 структурная схема узла выявления переносов. Система фиг. 1 включает устройство 1 хранения и преобразования информации с адресным 2, управляющим 3, первым 4 и вторым 5 информационными входами/ П:ервым 6 и вторым 7 выходами регистр 8 команд с информационным 9 и управляющим 10 входа-; ми; регистр 8 команд с инфОрмациойным 9 и управляющим 10 входами пер вым 11, вторым 12 и третьим 13 выхо цами; счетчик 14 команд с информационным 15 и управляющим 16 входами мультиплексор 17 адресных кодов с управляющим 18 и пятью информационHbsviH входами 19 - .23/ первый 24 и второй 25 коммутаторы С управляющими входами 26 и 27/ .первыми 28/,29 и вторыми 30, 31 имформациониыми входами, блок 32 микропрограммного управления, содержащий счетчик 33 микрокоманд с первым 34, вторым 35 и третьим 36 информационными входами и управляющим 37 входом, узел 38 памяти микропрограмм с адресным 39 и управляющим 40 входами-, регистр 41 микрокоманд с информационным 42 и управляющим 43 входами, первым 44 и вторым 45 выходами, узел 46 формирования управляющих сигналов, состоящий из группы элементов И, с информационным 47 и управляющим 48 входами, первым 49 и вторым 50 выходами, генера;то1з 51 тактовых импульсов.

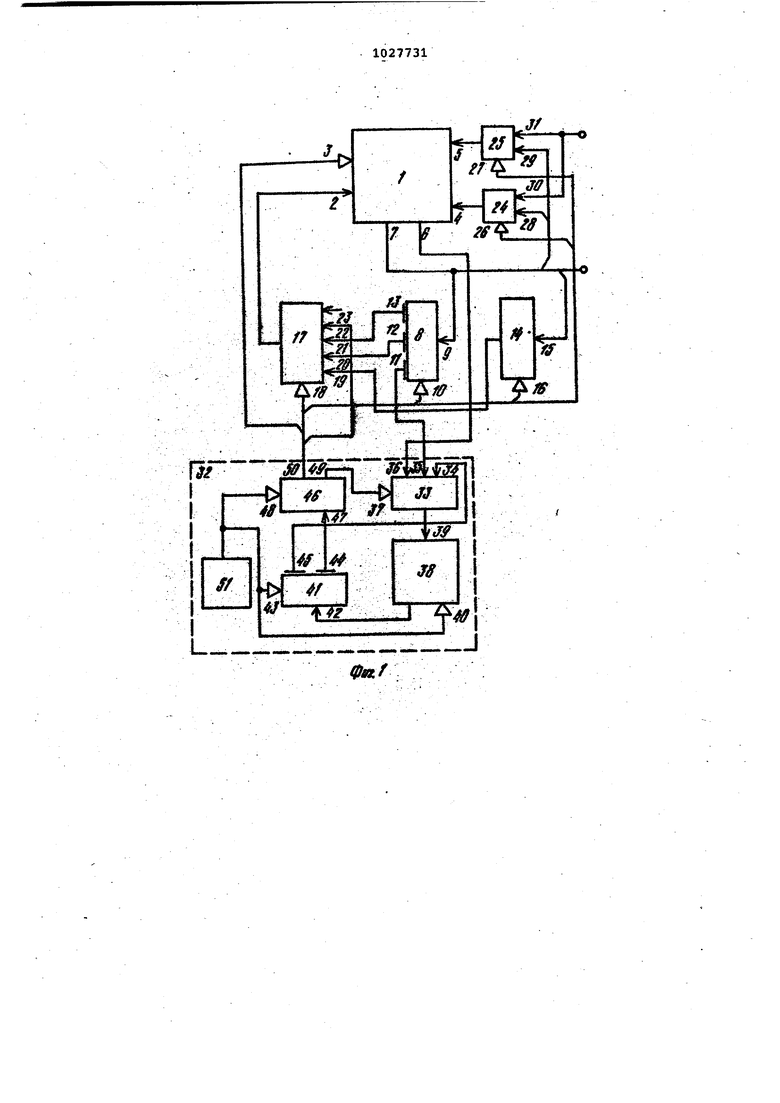

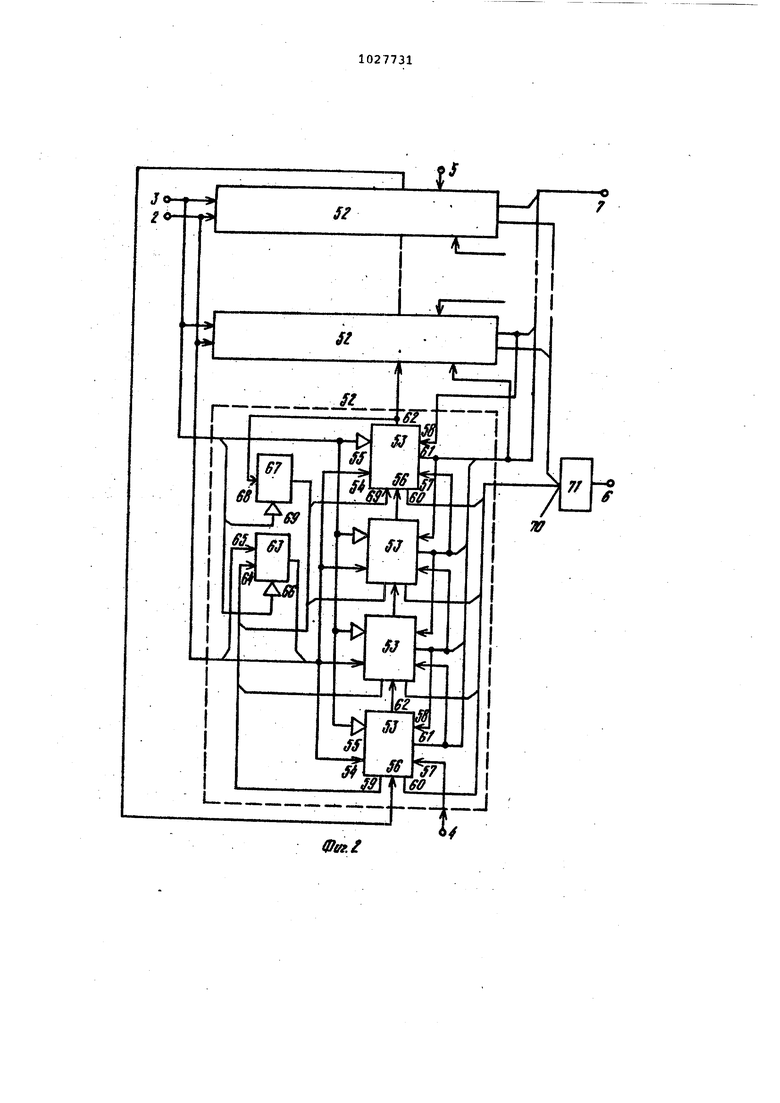

Устройство хранения и Преобразования информации фиг, 2 включает блок 52 хранения и преобразования информации, соответствующий четырем двоичным ид$и одному двоично-десятичному разрядам устройства 1. Блок 52 содержит четыре. одн6разряд-г ных блрка 53 хранения и преобразования информации с адресным 54, управляющим 55, первым 56, вторым 57 и третьим 58 информационными входами, первым 59, вторялм 60, третьим 61 и четвертым 62 выходами , коммутатор 63 адресных кодов с первым 64 и вторым 65 информационными и управщпощлм 66 входами, одноразрядный регистр 67 с информационным 68 и управляющим 69 входами, вход 70 блока 71 выявления нуля.

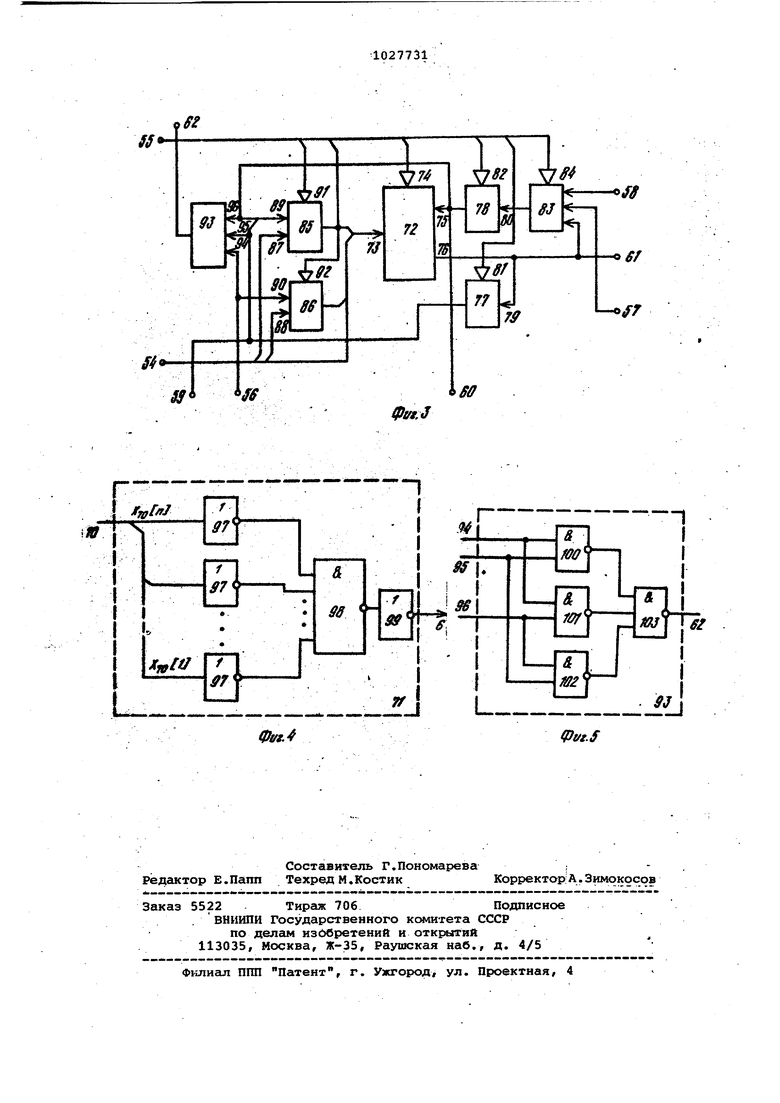

Одноразрядный узел 72 памяти (фиг, 3) с л-разрядным адресным 73, упраалянпцим 74 и инфоЕнлационным 75 входами и выходом 76 включает также одноразрядные регистры 77 и 78 с ин формационными 79, 80 и управляющими 81, 82 входами, коммутатор 83 информации с управляющим входом 84, первый 85 и второй 86 коммутаторы адреса с первьми 87,88 и вторнми 89/ 90 информационньв4И, а также уп- равлявадими.91 и 92 входами, узел 93 выявления переносов с первым 94, вторым 95 и третьим 96 входами.

Блок 71 выявления нуля Сфиг. -4 содержит группу элементов НЕ 97, элемент И 98 и элемент НЕ 99.

Узел 93 выявления переносов Сфиг, 5) содержит элементы И 100 103.

Система работает следующим образом.

Рассмотрим функциональную микропрограмму 1 команды суммирования двоично-десятичных кодов.

MHkponporpaMMa 1.

Начало:

МКР77 : Н(А)7/, / Считывание из накопителя устройсва 1 1-го операнда по адресу, поступающему через мультиплексор 17 с выхода 12 регистра 8 команд, и запись его в регистр 77./

М2. Р787: Н (А)/ : 1J / Считывание из накопителя устройства 1 2-го операнда по адресу, поступающему через мультиплексор IT с выхода 13 регистра 8 команд, и jзапись его в регистр/78. /

МЗ. - Р77 О :-: V ©Ya-)-©Bf--t, 1 -П,

РдЛ , г /W Выполнение 3-местной логической операции вычисления двоичной суммы 5дв по значениям аргументов Х

Цу(. . x-ff ) и Х,2 ( I х 24 ) поступающим из. регистров 77 и 78, а также слову переносов Р (Р,,... , Р ) , поступающему с выходов 62 узлов 93 выявления переносов (фиг. 2 и 3); запись двоичной сумисл SA в регистр 77; запись значений переносов из каждого 4-го разряда устройства

1 (фиг. 2) в гэегистры 6-7 /. М4. , D IT-оПуч. ..П

j) , j l .г. Определяется слово дополнительных переносов в соот тствии с правилами десятичной арифметики и записываехся в регистр 78. Для этого в каждом блоке 52 из четырех разрядов устройства 1 реализуется пятиместная логическая функция Fg, результат р получается на выходах 61 и через коммутатор 83 записываете в регистр 78 со сдвигом циклическим на один разряд влево. На выходе блока 71 выявления нуля формируется сигнал Y ;. Y 1, если Р78 0; Yg О, если . По сигналу Yg выполняется условный переход с помощью счетчика 33 микрокоманд. / МБ. (P4.j,S , j I.,:r, наМЗ. Корректировка суммы Бдрпо-правилам десятичной арифметики путем реализации пятиместных логических функций Р независимо в каждом блоке 52. Скорректированная частичная сумма F ( .SA&J) , , j 1 r записывается в регистр-77. В регистре 78 находится слово дополнительных переносов И, получ.нное при-вьшолнении микрокоманды М4. Выполняется переход к микрокс 4анде МЗ. Таким о&разем, реализуется последовательвый принцип распространения, переносов П из десятичных разрядов. Процесс заканчивается, когда слово переносов станет равньм нулю. Мб. Р78 {§ .) , j 1, г / Корректировка суммы 5де,по правилам Десятичной арифметики. Результат записывается в регистр 78 .-Jf/

К7.Н(:А , . / Запись результата в ячейку накопителя устройства 1 по адресу, код которого поступает с выхода 13 регистра 8 команд. / Конец. .

В микропрограмме обозначено: Р -

содержимое i-ro регистра (i - номер

позиции на фиг. 1-3), Н(А)- со-держимое ячейки накопителя устройства 1 по адресу А.

При выполнении микропрограммы 1 блоком 32 микропрограммного управления формируются следующие посЯед рвательности управляющих сигналов,

Ml. Х(/27:1 - 4)ООрООО«ОоО ООвОо01 00 О О«00о0° 001 010.

При этом X, 7:11 0000000, : (, U2.6-0, со; о, 0lf (, , (}, , « 010, . 010.

Эти управляющие сигналы в соответствии с рассмотренными ВЫше алгоритмами работы операционных обеспечивают выполнения функциональной микрокоманды Ml и запись в счетчик 33 микрокоманд по входу 34 адреса следующей микрокоманды М2.

М2. Уд.27:15 0000000ОоОоООоО 10

ОоОООоООООо1оОо010010

При этом Х,2 0000000, U27 О,

О, 00, , , 66 О . 1°

« 1, U,, 010.

Управляющие сигналы обеспечивают выполнение микрокоманды М2 и заПисЬ в счетчик 33 адреса следующей микро команды МЗ.

МЗ. V..p7:l3 0011000 ОоОоООоО11 1

OololoOOoOoleOloOlO.

При этом X,2.2. 0011000,Ua.7-b, (/г.-) U,,--00,U,--0,U,g-H,U69-H,,0,--(,U,.f, , Ug,--0, ,, О.

Управляюгдие сигналы обесНечивают .выполнение микрокоманды МЗ и запись в счетчик 33 адреса следугошей микроп команды М4.

М4. Г |57:3 0100000« ОР1вОО Оо11«

oOoleOoOoOloloOoOlollO.

При этом 0100000,Ujo о,

. 16° VO a J69-° 66- J9l

Управляющие сигналы обеспечивают; выполнение микрокоманды М4. В счетчик 33 адреса микрокоманд записывается адрес 5-й микрокоманды. Если , то в 4-м такте под действием cHrHaf ла в счетчике 33 прибавляется 1. Полученный код соответствует адресу микрокоманды М5.

М5. Y.I$7:fl 0000000о0о0о00о0о0о11 oOoloOoOoOOoOoloOlooio

При этом 0000000, ,(

: V-°° io ° r-. Ufio-o, Ug.-i.u.-o

Ug, 0,,,,U,.

Управляющие сигналы обеспечивают выполнение микрокоманды М5 и запись в счетчик 33 адрера микрокоманды МЗ по входу 34.

Мб. 1.27:; 0000000«0«.0в00в0о11о:

oOoloOoOoOOoOoOOilooip.

При этом Хга.0000000, U,i7-QO26 O

V°°Vo- г-- .

(,-0,(, Ug.-Q , , .OfO

Управляющие ойгнаЛы ббесйёчйвают выполнение микрокоманды Мб и запись в счетчик 33 адреса микрокоманды М7 по входу 34.

М7. Y 27:il 0000000« 0о0о00о0о10о

44 оОоОоОРОоООоОоОоЦоОЮ.

При этом Хд 0000000, 021 0,,

lJ7fe -°« Ч8-° J69-° J66° в2- , , Ugi--0,Ug 0, ,(

Управляющие сигйалы обеспечивают выполнение микрокоманды М7 и запись в счетчик 33 по входу 34 адреса следующей микрокоманды, обеспечивающий считывание из накопителя устрой,ства 1 следующей команды выполняемой программы.

В микропрограмме 1 рееипизуется последовательный принцип распростраг нения переносов П из десятичньах .разрядов. В худшем случае цикл из микрокоманд МЗ, М4, М5 повторяется г раз. В среднем, согласно известной оценки фон Неймана, он повторяется раз.

Для выполнения вьгчитания десятичных чисел выполняется суммирование прямого кода уменьшаемого с обратным десятичным кодом вычитаемого и I прибавлением циклического переноса из п-го разряда, для чего используется связь выхЬда 62 п-го разряда с входом 56 1-го разряда устройства 1 (фиг. 2). Обратный десятичный код получается таблично реализацией пятиместных логических функций (O. г в г блоках 52 фиг. 2) устрсшг ства 1. Старший (г-й) десятичный разряд устройства 1 (или п-й двоичный) может быть использован как знаковый:код Y п: (n-y) соответствует знаку - код Y:J Un: (п-3)3 0000 соответствует знаку +. Отрицательные десятичные числа хранятся в обратном коде.

С учетом изложенного операций вычитания двоично-десятичных кодов может быть представлена следующей Ш кропрограмл1бй.

Микропрограмма 2. Начало: .

(А) . О... О ,Н (А 0,..., О.

, ,r ,/К Считывание из ячейки накоцителя устройства 1 по адресу ...0 константы ОО (см.табл. 1 функции F (5дв, В) и табл. 2) и запись ее в регистр 78.

При этсни на выходах 62 всех блоков 53 хранения и преобразования информации устанавливаются нули. Запись нулей в одноразрядные регистры 67. V М2, Р787: Н(А)-, . . /Л Считывание из накопителя устройства 1 уменьшаемого по адресу, поступёиощему чер,ез мультиплексор 17 с выхода 12 регистра 8 команд, и запись его в регистр 78.f МЗ. (А, Считывание из накопителя устройс ва 1 вычитаемого по адресу, поступающему из мультиплексор 17 с выхода 13 регистра 8 команд, и запись его в регистр 77. Н4. (F9(X,44t5:ll))h.., (F,(x;;;,t5:lD)), . / Получение .обратного десятичного кода от содержимого регистра 77 Гвы читаемого) и запись результата в регистр 77. С этой целью в блоках 52 (фиг. 2) независимо реализуются пятиместные логические функции .F, от аргументов, котоЕ«ле поступаиот с выходов 59 блока 53 и регистра 6t при этом с выходов регистров 67 поступают нули. М5. Р77С ij7: X2i J± Р.. . I-1, 5P67j : Р43 J-br. /} Реапизация трехместных логических фушсций V ( . «ai P каждом из iei,n разрядов. Аргументы }Ц(... X,,,,), (. .. .ха) поступают с выхёдов регистров 77 и 78 Р(Р„...Р) - с выхода в 62 узлов 93 выявление переносов. Эта операция соответствует выполнению суммирования кодов Х и Х2 по правилам двсдач ной арифметики. Сумма Здцзаписывается в регистр 77. Значение пареносов Р.} из каждого 4-го разряда уст ройства 1 записываются в регистры 6-7. / Мб. , о.. .on/, (P4/ SABJ). j l,r, . ,то На М8, ИНЙЧЕ на М7. / Определяется слово дополнительных переносов в соответствии с правилами десятичной арифметики и записывается в регистр 78. Для этого В каждом блоке 52 реализуется пятиместнёю логическая функция лМ Результат Э со сдвигом (циклическим) на один разряд влево записывается в регистр 78, На выходе блока 71 выявления нуля формируется сигнал Yg : Yg « 1, если Р78 0, Y 0, если Р7Б7т)Ьо. По сигналу Y . выполняется условный переход« Х М7. rP777: F j.-; ),,r, на М5; Корректировка 5 А по правилам дё (сятичной арифметики реализацией .пятиместных логических функций ,F ( , Sig ) в каждом блоке 52. За пись скорректированной частищдй сум№1 5дву « Rf ( ; 5дв), .r в регистр 77. Переход к микрокоманде М5. М8. Р78 : F ( Рд,- , SAB , j-1, г . Корректировка суммы по пралам десятичной арифметики. Результ записывается в регистр 78./ М9. ll(R.)f Р78, Запись результата (разности в ейку накопителя устройства 1 по ресу, код которого поступает с хода 13 регистра 8 команд../ Конец. При выполнении микропрограммы 2 оком 32 микропрограммнаго управния формируются следующие последотельности управляющих сигналов. Ml. Yj27:l 0000000o0o0o00o0ollol оОоО ОоООо1 OoOioOlO. При этом Xjyj 0000000,UjHT0, ,ц,0,ЦвМ, Ufr,H, Ujj-o, u,, ,%--00,Ue4H, . CM, у,-ОЮ M2.iy27:I OOOOOOOoOoOo06oOo6l oQeOoOoOoOOoloQoOloOlO, При этом X-j D: 13 0000000, 6 ° «-°° w-o- (0-° b{. 84 00, Ugi-f, Ugr-°, , M3. Y |;27:33 OOOOOdOoOoOoOQoOolO« - oooOoOoOo OOoOoloOleOlOi При этом XJ,,,D:Ц 0000000,, : йбО.Цб°°J-IO °4e O.U69 -0%--0. ,,0,,,Ug,,,.U5, M4.Yj57jl3 100000600 00000 oloOoOoOOoOeloOloOlO Йри этом X,,j(7:lJ 1000000,U27°, 6 ° Ufe i fAUfeb- -I QO: 0. и 91-0, , Ug,-- a %;,-1, (,0yj010 M5. Yi;27tll 00110000o000o0oiie 44oloOol loOOo Ole 010 При этом X2.a 0011000,Uu7-0, U26-O ,5-00,U,o-0,U,gri,,, .Uв4 o -U9a-- 8Г- r-° 5 -° ° Мб. Y,. 27:13 01000000OolOOo oooloOoOoOlol . При этом Xj, 0100000,Ua,0,U2e u g--oo,u,,u,g-HU,-o;UegH,u,o, u.-o, Ug4--o, Uga-,.U7.o, МТТ Yj. 27:1 0000000 OeQ 00 Cell oOoioOoOoOOoOoloOleOlU. При этом X4 0000000,, Oae-OJ J 6-°oV 18 69 o 66 92-° V° g4°° ,( M8. Y 27:13 0000006eO«OoOOob li: 44 oOolo.OOoOOel OoOloplO. При этом X4a. 0000000,Ui7-0, Чб- V-O- ( бб --V V-0tJ64 Of 92 U8r-O., M9. 27:1 00000000OoOoOOeOelO oOo OOoOoOOoOoOolloOlOi - При этом Х, 0000000,0а7-О, ( (, 00, Ug,--0, ,,U57:ro O При работе с отрицательными числами в двоично-десятичной системе счисленияможет потребоваться коман да получения обратного десятичного кода. Для выполнения такой команды в предлагаемом устройстве может быть использована следующая микропрограмма. Микропрограмма 3. Начало. Ml. Р7 S : 11 (А ) , А с «оХ25 --0. .. О, Jt bi.. ТЧ . Л Р677 0, /Считывание из нулевой ячейки нако пителя устройства константы О и за пись ее в регистр 78. При этом навыходах 62 всех блоков 53 устанавливаются нули. Запись нулевой в регис:р ры 67У М2. Р77 (А) . ,g /Считывание из накопителя устройства 1 операнда по адресу, поступающему через мультиплексор 17 с вьгкоДй 12 регистра 8 команд, и запись его 6 регистр 77./; МЗ. (Р5(Х(;4и13г1 )4) . . . ,ТРз(Хб4:,БЗ:1Ц),. / Получение обратного дегятичного кода от содержимого регистра 77 и запись результата в 78. При этом в каждом из j б 1,г блокоб 52 реализуется пятиместная логическая функция , j)/ М4. Н(А) : ГР78, , /Запись полученного в регистре 78 кода в ячейку накопителя по адресу, поступающему с выхода 13 регистра команд./ . Конец. При выполнении микропрограммы 3 блоком 32 микропрограммного управления формируется следующая последова тельность управляющих сигналов. .2 Чйлг о;ж При этом X,,,Dsi 0000000, 027 С Г6--00, U,o--0,U,gH,U69M, UggrO, Uqa--0, , Uj54-00,(,,U74--0,U,OfO М2. 0000000«0c0o00 0o01o oOoOoOoOoQOo0°loOloOlO При этом )у7:1 0000000,и,, V o-О- 4Ъ (f ,U84--00, , -f, , U, M3. Yj.p7fl 100000000 QeOoOOoOolJ. 0 0°1° QoOo OOoi При этом 7:1 1000000 U, 2б V°° 10. , Ue -0, Обб H, , Ug,(,., (,( М4,У44 27:1 ОООООООоО«ОоОО 0«ЧО 00с При этом 0000000 и,7-0, I и о ОЛ4-- 0, (k9--°.66--0,0).- 0,0,0. ,,,U-,4 -f, U,, Рассмотрим режимы работы устройства 1 хранения и преобразования информации (фиг. 2). 1. Считывание слова по адресу, подзываемому на вход 2. При этом (--Ub °U66oU55t8:300°U55 MJ Код Ufyf,. Соответствует 3-му режиму работы блока 53 ( фиг. 2) : U55t8-l3--U92 J)i°lJ84t J92°U8 °U,4Ci--Q -0 0°Ug4CU.l3oUg,. При этом адрес А, nocTynajouffffl на вход 73 одноразрядных блоков памяти 72, соответствует коду. ,j Cm:ll Код слова, считанного из накопителя по адресу А, поступает на выходы 61 (фиг. 2 и. З) , а также может быть записан в регистр 77 при{/« 1г а также в регистр 78 (прии22 сдвига (), со сдвигом злево ( Ug4 0) вправо (Og4 0)., Причем, если Ug-j о выполняется арифметический сдвиг/ а если Ug. 1, циклический. : 2.Запись слова из регистра 78 (фиг. 3) в накопитель по адресу А Х,(фиг. 2). При этом I --Ufeg UefrO U55 tSMJ rOOoU sDM . КодСиОЗ: соответствует 4-му режиму Жботы блока 53 (фиг. 3 s U55E«-l 92° и9,.У84 LUHJoUga- U8 °U;4Cu- 3 iOOOOOOH . ..3.Реализацияпоразрядных двухместных логических .функций. При эюя-.- U,,t(0.-13 U69 Ub6-U 5t8:3-0-OcU55C8H: Код (Jt5 L8:l соответствует 5-му режиму работы блока 53 (фиг. .OfOOlCOl- Аргументы реализуемой, функции находятся в регистрах 77 и 78. Результат записывается в регистр 78. Код на входе 2 (фиг. 2)X2 :-n:3j соответствует адресу сегмента накопителя из четырех ячеек с таблицей реализуемой двухместной логической функции. :, . 4. Суммирование двух чисел в двоичной системе счисления с использованием схемы сквозного переноса. При Э.ТОМ: „ и,,по-.13-иб9 ибб Ц5С8и: о«о и„С8п .8:и соответствует 6-му режиму работы блока 53j . . 055Ee:i3--092 J9i 84t - JUe Ui4DMl- 1 001001 Слагаемые предварительно записываются в регистры 77 и 78 в 1-м режиме работы устройства 1. Сразу же после записи слагаемых в регистры в последовательно соединенных узлах 93 фиг, 2 и 3) выявления переносов распространяется волна переносов. После завершения переходного процесса на выходах 56 устанавливается код слова переносов. На адресный .вход. 2 устройства 1 подается код (:4.J адреса сегмента накопителя из 8-ми ячеек, в котором записана таблица трехместной логической функции

; r -i-4iPi-i-- ii® i®. , , гдеХ,, г-еразряды слагаемых, а Ei- перенос из ( 1-1)-го разряда.

На выходах 61 получается результат суммирования, который через коммутатор 83 информации записывается в регистр 78. При 1 (фиг. 2) перенос из каждого 4-го разряда устройства 1 с выхода 62 записывается в регистр 67. Эта информация исполь-зуется в 5-м режиме работы устройства 1 при выполнении команд десятичной арифметики.

5. Корректировка десятичных кодов и выявление переносов между десятичными разрядами при выполнении арифМетических операций в двоично-десятичной системе счисления.

При выполнении арифметических операций над числами, представленными в двоично-десятичной системе счисления требуются операции, связанные с обработкой двоичных кодов, представляющих каждай десятичный разряд.

1.Корректировка результата суммирования S двух двоично-десятич- .

ных чисел, выполненного по правилам суммирования двоичных чисел S S,

2.Выявление дополнительного переноса П из одного десятичного разряда в другой.

3.Получение обратного десятичного кода в двоично-десятичном пред- ставлении:

s-e S

Содержание этих операций поясняе таблица 1, в которой приняты обозначения R - результат суммирования двух бдноразрядных десятичных чисел, Р. - перенос из 4-го двоичного разряда при сложении двоично-десятичных кодов по правилам двоичного мирования, S - сумма, получаемая в 4-х двоичных разрядах при двоичном сложении двух одноразрядных десятичных чисел, представленных , в двоично-десятичном коде, и выраженная в десятичном коде, 5д0 ) - сумма S, выраженная в двоичном коде; П - перенос из десятичного разряда, дополняющий перенос Рд, полученный при двоичном сложении-, S- скорректированная по правилам десятичной арифметики сумма S в десятичном коде, ($4.) - скорректированная сумма S в двоичном коде; 5 - обратный десятичный код одноразрядной десятичной переменной S: S 9 S; 5д# Z (Z4 Z Z fj. ) - двоичное представление переменной Т.

Для удобства последующих операций перенос П из десятичного разряда удобно представить четырехразрядным двоичным числом Пдр -ПООО, -в котором переменным может быть только

старший разряд, сортветствуюцщй П.

; Из таблицы следует, что преобразования 5дв % (. , )- и Fa (Рд 5д можно представить как

г системы четырех пятиместных неполностью определенных логических функций, которые должны быть реализованы независимо в каждых четырех двоичных разрядах устройства, соответствующих одному блоку 52 tфиг. 2), Преобразование, связанное с получение м обратного десятичного кода . Здо, - 5д может быть представлено как «истема четырех неполностью определенных четырехместных логических функций.

V Однако с целью унификации средстЬ для выполнении таких преобразований его удобно представить как систему j четырех пятиместных неполностью опрёгделенных логических функций при фик- сированном значении перемё;нной 5 0:5дв F,,(0, 5дв).

Функции R, и Fj определены на 19-ти наборах двоичных переменных (Р4 Зд , S,,, Si , S) а -F, - на десяти наборах (О, 84, S,, S,, S). Тот факт, что реализуемые функции определены не полностью, а лишь на ти из ВОЗМОЖНО37О множества наборов можно использовать для умень;шения числа ячеек накопителя, отведенных для хранения таблиц. При этом можно предложить размещение таблиц в накопителе (см. табл..2. Да&лицы двухместных и трехместной логической функции одинаковы во

«всех П разрядах.

: Таблицы остальных преобразований одинаковы в г группах по 4 двоичных разряда.

Таблица.трехместной логической функции у Х занимает сёг5 мент из восьми ячеек, для обращения к ячейкам которого переменная Р

определяет значение третьего разряда адреса в каждом блоке 53 ; (фиг. 3). Эту функцию можно представить в виде.

(. P(T{i©Xi7

Соответственно таблицу сегмента - 24-31 можно использовать как две таблицы двухместных логических функций: при , f (х, xi)X.S х при Х75р3 (x-j, )x 0x2. Таким образом, таблицы в выделенных ячейках накопителя 0-73 позволяют выполнять шесть двухместных, одну трехместную поразрядные логичей кие функции,а также три вида преобраз ваний, связанных с реализацией десяти ной арифметики. С учетом приведенного распределе ния ячеек 0-73 накопителя можно определить коды ,rn:i, которые необходимо подавать на вход 2 при выполнении различных преобразований (фиг. 2). При всех преобразованиях 8J -0... О. Для семи . младших разрядов кода Х получим: Код Х„ 7:Г} Преобразование (Р4Г 54в) 00---- Вf4(N/ 2 00101-f (XfV Х р) ООН rs:vj, 01 01110-.Ых-f Ля) 01Н1 Ав з ° А 10 S/ Прочерками отмечены разряда кода Хд. на входе 2 устройства 1, которые не участвуют в формировании кода адреса. Значения этих разрядов Mory быть любыми, в частности равными ну лю. рассмотрим работу устройства в 5-м режиме. Аргументы, над которыми производятся преобразования, находятся: 5дв в регистре 77 (фиг, 3), в регистре 67 (фиг, 2) со тветствующем J-му блоку 52, ,r. Лри работе в 5-м режиме на вход 3 устройства 1 подается код .-| J--Ufc,ou oU55D8;i. Сг-- 3. На адресный вход, 2 подается код Х, .старшие (т-5) разряды которого соответствуют адресу сегмента накопителя Из 32-х ячеек, в котором записана таблица реализуемой пятимест ной логической функции F , F, или F в соответствии с приведенным выше размещением таблиц. Эти разряды код X „ поступают на старшие (in-5) разряд входа 54 ( } л1}п:б ХгЕк т:бЗ. Младшие пять разрядов кода X -f на адресном входе блока 53 соответствуют аргументам реализуемых пятиместных логических функции; Ойи noe naipT через коммутаторы 63 адресных коДов независимо в каждом из г блоков 52: четыре - с выходов 59 блока 53 и пятый - с.выхода регистР 67. Управляющий код L J сЬответ ствует 3-му режиму работы блока 53 (фиг. 3): U56Ce- J92%1°. UgjoUg °0 0 °Результат реализованной функции с выходов 76 через коммутатор 83 информации записывается в регистр 78. Рассмотрим работу устройства при выполнении команды суг«1мирования чисел в двоично-десятичной системе счисления. Формат команды содержит три поля, которым соответствуют три выхода 11 12 и 13 регистра 8 команд (фиг. 1 со следующим назначением: 11 - код операции, 12 - код адреса 1-го операнда, 13 - код адреса 2-го операнда и результата. При выполнении микрокоманды выборки очередной команды, как и в известных устройствах, код команды считывается из устройства 1 по адресу из счетчика 14 команд и записывается в регистр 8 команд, код операции с выхода 11 поступает на ( вход 32 блока 32 микропрограммного управления и записывается в счетчик 33 микрокоманд, определяя адрес 1-й микрокоманды соответствующей микропрограммы. Одноразрядный блок 53 хранения и преобразования информаГции может работать в следующих режимах (Фиг.З) 1.Хранение информации.При этом и74Г2:11 00, 08,0,(/81 О, Выход 76 одноразрядного узла 72 памяти при этом имеет большое сопротивление. 2,Запись кода, поступающего на выход 61, в регистр 78 без сдвига, со сдвигом на один разряд влево или со сдвигом на один- разряд вправо. При этом 1182. 1 и соответственно . и94&1Й.00,084Е2:13 01 иирД2:1 10. . 3. Чтение иэ одноразрядного блока 72 памяти по адресу, подаваемому на вход 54. При этом U9V U94 0U74r2:lJ 01 и соответственно Х 1«1:1 А Х54&1:13, Н(; . Считанный код Может быть записан в регистр 77 f08 1, в регистр 78 без сдвига, со сдвигом влево или вправо (режим 2), передан : в другие блоки устройства через вывод 61. 4.Запись кода из регистра 78 (числа) в узел 72 памяти по адресу, подаваемому на .вход 54. При этом ОРИ 0, , Ц, Г 2:1 11 и соответственно 13 А Х5г4рп: U , Н (А).; . 5.Выполнение двухместйой /югической функции табличным способом. При этом Up l/Wpa-О, :U74 . На вход 54 поступает: код, Скй-2 ; старших разрядов которбгЧз соответствуют адресу сегмента накЪпителя узла 72 памяти, содержащего 4 ячейки, в которых записана таблица реализуемой логической функции, число таких сегментов может быть выделено соответственно требуемому числу двухместных логических функций. Аргументы записаны в регистры 77 и 78, Аргументы могут быть считаны из узла 72 памяти и записаны в регистры 77 и 78 в режиме 3. Младшие два разряда адреса поступают через коммутатор 85-с выходов регистров 78 и 77

Х„12.1Т.7рв.{17X,a Cw«3J

Таким образом, код К прва&ляет выбор сегмента из четырех ячеек с требуемой таблицей, а выбор ячейки в сегменте осуществляется комбинаци ей 2-х аргументов ) Результат регшизуемой функции, считанный из узла 72, появляется на выходе 76 и дгшее Через коммутатор 83 записыва- ется в регистр 78

6. Выполнение трехместной логической функции табличным способом При этомUjj 1, Ирг 01, . ; Uo4 «OOrUa 1« На вход -54 посту „. ., ..,.OJ|B,

пает код Сш-З старших разряда которого соотв1втствует адресу сегмента из 8-ми ячеек узла 72 памяти, в котором записана -таблица реализуемой трехместной логической функции. При этом код адреса мируетсй следующим образом:

VW«H 1-. Х54Ет:41){,;: .VT,

На вход 56 поступает перенос из предыдущего разряда (фиг 2/. В ре- гистрах 77 и 78 записаны два аргу.мента Режим 6 используется при сум мировании, при этом реализуется трехместная логическая функция вы числения сунАШ:

ч: п :1в® 5б-,

Результат Чч записываемся в регистр 78.

таким образом, предлагаемое уст ройсфво позволяет повысить произво;ци1гелыюсть работы.

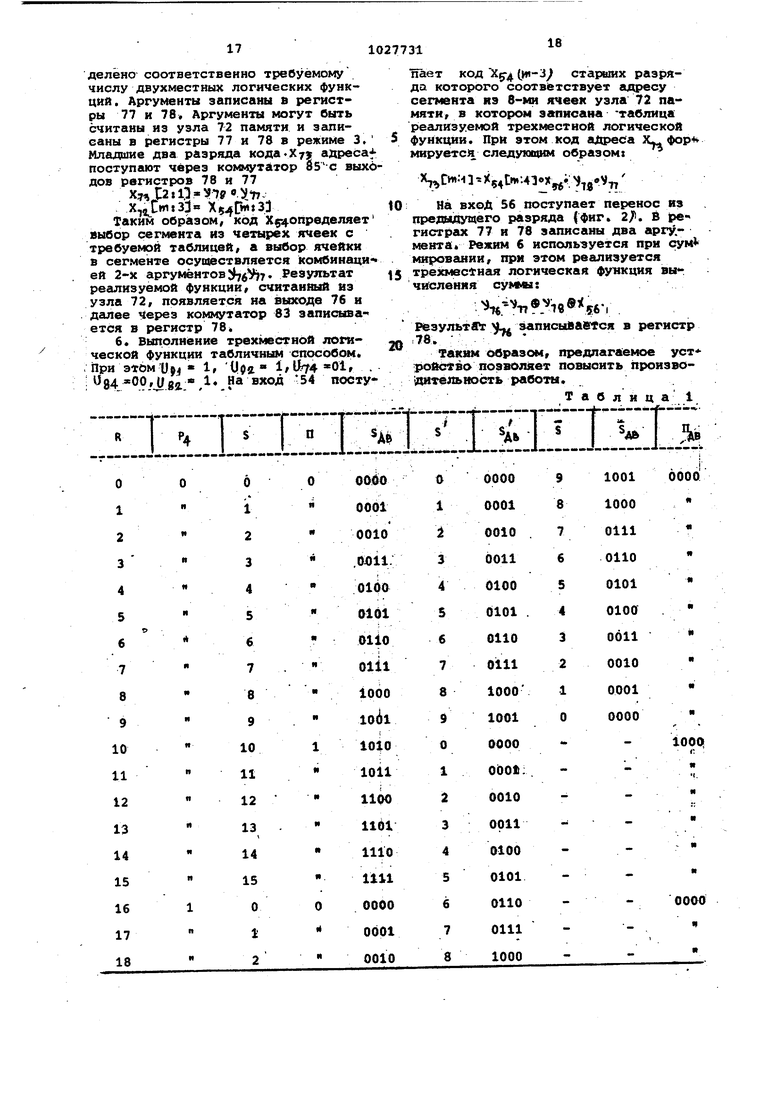

Т а б л и ц а 1

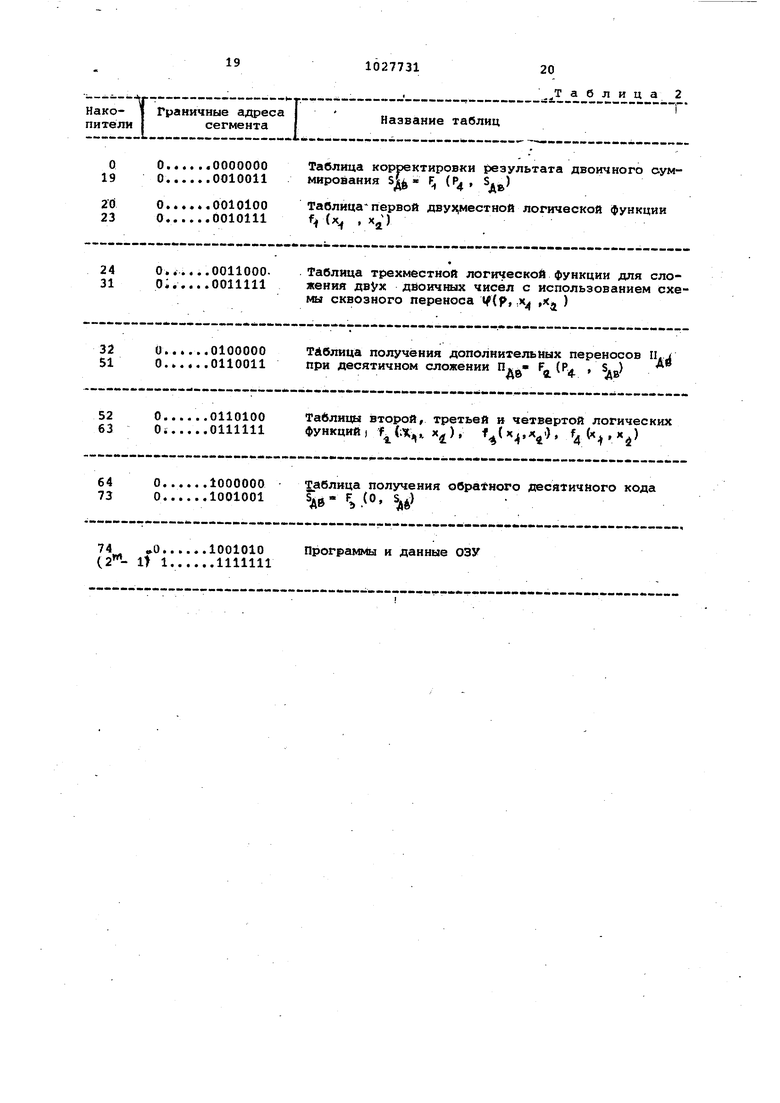

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| УСТРОЙСТВО ОБРАБОТКИ ДВУХМЕРНЫХ И ТРЕХМЕРНЫХ ИЗОБРАЖЕНИЙ | 2005 |

|

RU2289161C1 |

1. СИСТЕМА ДЛЯ ВЫПОЛНЕНИЯ ; КОМАНД ДЕСЯТИЧНОЙ АРИФМЕТИКИ ТАБЛИЧГ Н1Л1 СПОСОБОМ; содержащая регистр команд, счетчик команд, мультиплек:сор кода адреса, два коммутатора и блок.микропрограммного управления, первый выход регистра команд соединен с первым входом блока микропрограммного управления, выход котог ррго соединен с управляющими входами :Мультиплексс ра кода адреса, регистр команд, счетчика команд и двух коммутаторов, второй и третий выходы регистра команд соединены с первые и вторым информащионными входами мультиплексора адресных кодов соответственно, третий информационный вход KOTOjporo соединен с выходом счетчика комайд, отличающ а Я; с я тем, что, с целью увеличения производительности, она содержит устройство хранения и преобразо вания информации, адресный вход коiroporo соединен с выходом мульти.плексора адресных кодов, управляюии й вход - с выходснл блока микропрограммного управления, первый выход - с вторым входом блока микроnpprparatiHoro управлёния второй выход - с информационными входами регистра- команд, счетчика команд, с первыми информационными входёма первого и второго коммутаторов и является выходом системы, выходы первого и второго коммутаторов соединены соответственно с первым и вторым информационными входами устройства хранения и преобразования информации, вторые информационные входал первого и второго коммутаторов являются первым входом системы. четвертый информационный вход мульти плексора адресных кодов соединен с выходом блока микропрограммного управления, а пятый информационный вход является входом системы. . 2. Система по п. 1, отличающаяся тем, что устройство хранения и преобразования информации содержит блок выявления О) нуля и г блоков хранения и преобразования информации, кг1ждый из которых содержит четыре одноразрядных блока хранения и преобразования информации, коммутатор адресных кодов и одноразрядный регистр, причем управляющие входы каждого однораз- ji рддного блока хранения и преобразо-, вания информации каждого блока хранения и преобразования информации соединены с управляющим входом устройства и с управляющими входами регистра и коммутатора адресных кодов каждого блока хранения и преобразования информации, выход регистра каждого блока хранения и преобразования информации соединен с первым информационным входом соответствуюй го коммутатора адресных кодов и с первым выходом каждого одноразрядного блока хранения и преобразования информации соответствующего блока хранения и преобразования информации, адресный вход которого соединен с выходом соответствующего ;коммутатора адресных кодов и со старшими разрядами адресного входа устройства, младаиие разряды которого соединены с вторым информационным

| I | |||

| Патент ОНА № 3001710, кл | |||

| , опублик | |||

| Судно | 1925 |

|

SU1961A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Стена | 1931 |

|

SU26422A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-07-07—Публикация

1981-09-14—Подача