1

Настоящее изобретение относится к импульсной и вычислительной техшцсе, может быть использовано, например, для умножения входной импульсной последовательности посто даой или меняющей-; ся частоты на некоторое целое число.6

Известны устройства для умножения частоты, построенных на принципах дискретной техники fl ,2

Первый из дискретных умножителей частоты содержит формирователь импульсов, RC-цепочку, счетчик, генератор импульсов, делитель частоты, вто- ю рой счетчик, блок памяти и третий счетчик. Выходы блока памяти и третьего счет1шка подключены к элементу совпадения. Однако это устройство работает с невысокой точностью.

Второй умножитель ближе к предлагаемому пс| is функциональному назначению и схемно-конструктивному решению. Он содержит два счетчика, делитель частоты, два триггера, счетных вход первого- из которых соединен с выходом элемента И, первый j вход которого подключен к клемме истошика вход- 20 ного сигнала. Это устройство выбрано в качестве прототипа.-,

Недостаток второго устройства заключается в том, что вследствие кабега фазы, которьш может образоваться вследствие изменения фазы входной 2§

(последовательности икшульсов и нестабильности фазы генератора импульсов, оно умножает частоту импульсов с ошибкой, которая может быть весьма значительной.

: Кроме того, это устройство запоминает значе(Ние частоты входной последовательности импульсов лишь в некоторый начальный отрезок времени и формирует BbixofpjyK) последовательность, соответству юшую этому начальному значению. Изменение часто: :ты входной последовательности никак не сказывает |СЯ на параметрах выходной последовательности импульсов. Эта жесткость существенно снижает воз:можности использования устройства. ; Цель изобретения - повышение точности умножения.

; Предлагаемый дискретный умножитель частоты отличается тем, что в него введены дополнительный делитель частотьи два дополнительных триггера, сумматор, дополнительные элементы И, элементы ИЛИ

и два блокаипдикации, каждый из которых состоит из трех трехвходовых элементов И, входы первого из которых подключены к кулевым выходам, кроMe первого, разрядов счетчика, а выходы второго и третьего - к выходу первого трехв ходовогоЭле менГга И и соответственно к нулевому и единичному вы

ходам первого рйзряда с-№1чик(. Прк зтом выход Бторогс элемента И соедаиек с рдднояиым ВХОДОРЛ liepBoro дополжлельного триггера -i с первыл-ш входа ш первого и вторсго дополнительных элементов И второй вход первого из которьк. подключен I к запрещаю1це лу входу cyMMaiopa, к од1ому уа вы« ходов второго тфиггера к к первым вкодам блока I шщгкадкя, а выход - к: дерзсму t,-i.j/i,y rsepsoro элеряекта 1ПИ; второй вход котсрогг : ;еэ дйя }тель частоты соединен с вькодом n;ojL -; алемента И, I второй вход -которого сое,пг;;гч; : -/гарым ВЫХОДОР,второго дополнительного - : „pa, нулевой вход i которого подключен к -..хс.ду сумматора, к нуле- ; вым Еходарл допо/гЕПельных триггеров и к нулевому входу первого счегчика, а . первого элемента HJWi соединен с первыми входами трет :-его и чет-i вертого дополнительных элег-.гектов И, вторые входы которых подкпг гчекы к выходам второго догголнительногэ триггера и соотзетственао ко вторым входам второго Fi первого uuoVcoB нкдтпсадии, 1ричем выход третье дополнлтдиьного И подкльо чей к суммирую дему г; рБого и к вычитающему входз вгорОГО счетникоа, а четвертого допол.чительиаго элемента И - },; т гугмнрукидему входу второго и к БЬ читающе;,1у «ходу первого счетчиков, разрядные выходы Kovopbus. иодключеяы ко входам блоков иядикаииИ:, еди гиПые вьзходы которых соедкнецьг со зхоцамк вт,1|-;о.го игемепта ИЛИ, выход которого ;йрез /оио./ итеаьньш элемент И coeiJ iieu с нулев1 к з г;л.::Д01ч nc;:F30jo дополнительного триггера .с выхо/дол- допол 11тел лого делителя частоты н с lifipBLiM входогт ujec; ого допол {ительпого элемента И, хзтарой вход котсрс/го подтмгочен ко входу доиол ительного делрпсл; частоты, к счетному входу второго донолнителъпого триггера и к выходу третьего . 1ШИ, входы которого соединены с нулевыми выходами плоков 1ндикащо, а выход luecToro дополнительного эу. ментл И - к первому входу cy ivKTopa, iiropou вхог{ которого подключен к KjfflMwc истсч1 кка входного спгнала.

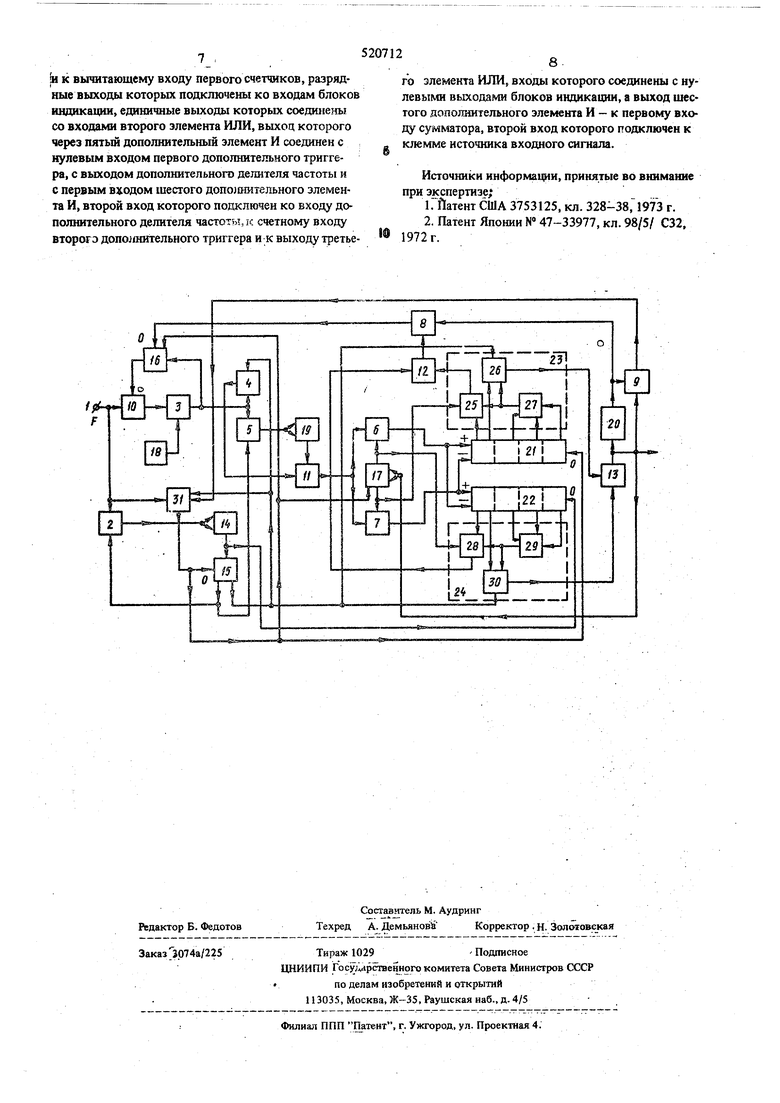

& -чертеже 1111одст; 5 е1г. структурная схема устройства.

Диск :;етньш улПгожителг;. частоты содержит подключае1лЬ1е к .к.пегугме 1 ,тсточника входного сигнала элеьге} ты И 2 :; до1тол П1тель Гые элементы И 4-9, элементы ИЛИ 10-13; тркггерь; 14 и 15, дополнктель ные триггерь 16 н i7. генератор импу;1ьсоз 18, делитель частот), iQ. до юл ;;тел 11ый делитель частоты 20, счокчик;; 21 и 22, ииДЗкалми 23 и 24, трехаходовые элемент, И 25--.ЗС, сумматор 31.

Клелгма i Ч1;рр;з ::iлe ;eнт S-ШИ. 10 соединен с леыентом И 3, второй вхол которого нодклгочен к генератору ,сои 18, а выход - к ед.иикчному входу дополлигельпого триггера 16 и ко входам дополнительных элементов И 4 и 5. Выход дополнительного триггера 16 o;j,jcj j;j4C;i ко г торому И.ХОДУ элемепта ИЛИ К), Охом, cynr-iaTojja 3 ло модулго лва подключен . клс. 1 и к :5ле..1енту И 2, выход которого о;1, К счстпому входу tpiirrepa 4. тпигг;м а 14 сосл п;011 с fy:ieвьi i входом счет чикй 22 н с сди 1ИЧ1;ы пходом pinTTfifi 15, г улевой

ВХОД которого соединен с выходом сумматора 31 н с нулевыми входами дополнительных триггеров 17, 16 и счетчика 21. Один выход триггера 15 соединен с элкмеитарли И 5 и 2, а другой - с дополнительным элемег :UM И 4 и с запрещающим входом сумматора 31./

Выход элемента И 5 соединен со входами делителя частоты 19, выход которого через элемент ИЛИ 11 подсоединен ко входам элементов И б и 7. Второй вход элемента ИЛИ 11 соединен с выходом элемента И 4. Вторые входы элементов И 6 и 7 соединены с выходами триггера 17 и со входами блоков индикации 23 и 24.

Блок индикации 23 состоит иэ трехвходового элемента И 27, соединенного с рулевыми выходагли всех разрядов счетчика 21, кроме первого, и двух трехвходовых схем И 25 и 26, первые входы которых соединены соотйЬтственно с единичным и нулевым выходами первого разряда счетчмка 21, а вторые входы - с выходами элемента И 27.

Аналогично и блок индикации 24 состоит из трехвходоБого элемента И 29, соединенного с ну-; левымл выxoдa ш разрядов счетчика 22 (кроме первого разряда), и трехвходовых элементов И 28 и 30, соединенных с выходами первого разряда счетчика 22 и с выходом элемента И 29.

Выход элемента И 6 соединен с суммирующим входом счетч 1ка 21 и с вычитающим входом счетщка 22, а выход элемента И 7 - с суммирующим входом счетчика 22 и с вычтаающим входом счетчика 21. Нулевые выходы блоков индикации 23 и 24 через элемент ИЛИ ГЗ соединены с выходом устройства и со входами элемента И 9 и делителя частоты 2, выход которого соединен с элементом И 8 и через элемент И 9 - с сумматором 31 Единичные выходы блоков индикации 23 и 24 через элемент ИЛИ 12 соединены со вторым входом элемента И 8, выход которого соединен с нулевым входом триггера 16. Третьи входы элементов И 26 и 30 соединены со вторым выходом триггера 15. Каж.дь1Й блок индикации 23 (24) предназначен для индикации состояния своего счетчика 21 (22). Эти блоки должны реагировать только на два состояния счетчиков - нулевое (во .всех разрядах нули) и единичное (в первом раз.ряде единица, а-в остальных - нули). Таким образом, например, в блоке индикации 23 элемент И 27 фиксирует нулевое состояние во всех разря1 дах, кроме первого, а элементы И 25 и 26, сое- диненные с элементом И 27 и с первым разрядом счетчика 21, фиксируют соответственно наличие едмниды или нуля В первом разряде.

Работает дискретный умножитель частоты следующим образом.

В исходном состоя1ши все триггеры, счетчики и делители находятся в нулевом положении. При этом сигналы могут пройти через элементы И 3,5, 2, 6,28. Первый имнульс входной частоты устанавливает в единичное состояние триггер 14, fa также проходит через элемент ИЛИ 10 и на эле5менте И 3 совпадает с одним из импульсов генератора 18. Импульс совпадения с элемента И 3 устанавливает в единичное состояние триггер 16, благодаря чему через элемент ИЛИ 10 элемент И поддерживается постоянно в открьгтом состоянии. Импульсы с генератора 18 через элементы И 3 и .поступают в делитель частоты 19, а каждый п-ный импульс с л.елителя 19 через элемент ИЛИ Ни элемент И 6 поступает на суммирующий вход счет чика 21 и вычитающий вход счетчика 22. Второй импульс входной частоты Р через элемент И 2 проходит на триггер 14 и переводит его в нулевое состояние, а сигнал с этого триггера устанавливает в нуль счетчик 22 и переводит триггер 15 в еди.ницу. При этом запрещается прохождение сиг налов через элементы И 5, 2, 26 и 30. Нулевое состояние счетчика 22 фиксирует блок индикации и сего выхода через элемент ИЛИ 13 на выход поступает первый импульс, который, кроме того, поступает в делитель частоты 20 и переводит триггер 17 в единичное состояние, благодаря чему раз решается прохожде1ше сигтлов через элементы И 7 и 25 и запрещается-через элементы И 6 и 28. В счетчике 21 к этому моменту зафиксирован необходимый коэффициент деления. Импульсы генератора 18 через элементы И 3, 5, ИЛИ 11, И 7 поступают на суммирующий вход счетчика 22 и вычитающий вход счетчшса 21. В момент, когда в счетчике 21 остается один импульс (состояние единица), сигнал с элемента И 25 через элемент ИЛИ 12 поступает на элемент И 8,однако дальше не проходит, поскольку на второй вход этого элемента лодан запрещающий потенциал с делителя частоты 20. Наконец, когда счетчик 21 оказывается в нулевом состоянии, срабатывает элемент И 26, и сигнал с блока индикации 23 через элемент ИЛИ 13 попадает вновь на выход, в делитель частоты 20, и переводит триггер 17 в нулевое состояние. В этот момент в счет чике 22 записан необходимый коэффициент деления, а счетччк 21 находится в нулевом состоянии. После перебрасывания триггера 17 вновь открываются элементы И 6, 28 и закрьюаются элементы И 7, 25, и очередные импульсы генератора 18 поступают на суммирующий вход счетчика 21 и вычитающий вход счетчика 22. Нулевое состояние счетчика 22 фиксируют элемент И 30, сигнал с ко торого поступает на выход. Устройство работает согласно приведенному выше описанию, пока на выходе не появится ti-шл импульс ( п -коэффициент умножения). С появлением П -ного импульса срабатывает делитель частоты 20, и на его выходе появляется сигнал, разрешающий прохождение импульсов через элементы И 9, 8. В зависимости от того, какой из счетчиков-21 или 22-в этот момент работает ч режиме вычитания, сигнал с элемента И 25 или 28 фиксирует единичное состояние счетчика, проходит через элементы ИЛИ 12, И 8 и устанавливает нулевое состоя1ше триггера 16. Тем самым сле1дующий импульс генератора 18 привязывается к iHtYfflyjibcy Плодкой частоть5 F . Этот импульс переводат счепшк, работающ}П1 Б режиме ВЫЧИТЗЕШЯ {21 или 22) Б нулевое состояш с. сигнал элемента И 26 ; ( 30) через элемент ИЛИ 13 поступает на выход, IB делитель частоты 20 н через элеме гг И 9- на сумматор 3. Если в этот момент на втором входе сум:матера присутствует импульс входной частоты F , на выходе сумматора 31 сигнала нет, и устройство .продолжает работать аналогиггно osincaHHOMy выше. Если импульсы входной частоты F на входе, сигHfijj с сумматора 31 устанавливает в нулевое состояШте триггеры 16, 5, 17 н сяеттек 21, и работа схемы прекращаетхя. Если изменяется период входной частоты (в общую или меиьигую сторону)с приходом очередно- Vo входного игчшульса устройство начинает работать ..сначала. Ф о р м у л а и 3 о п 1J е т : и к я ; Дискр ;н1Г :й VhiHo iciicjib ч;1С;отьь соАе;)/5.;ащкй два с ечч;-исй, ткпть частоты, два триггера, счетный вход nephioro Ил которых С(5е.(ен с iii,ixQ,iiOivi первого элеLviSHTi i1, :ri. вход KoropoiG псплслючец к клемме источника, входиото ciiiuaJia, а ьмрой - через второй трпггс-р - к ныхо1|,у первого ipiirrtpa, гсператор. импулссов. 1И.-1ХОД кото;рого ooojuiuei; с oruivsM пз входов второго элем; нуд И. о т л и ч а ю ш и и с я тем, что, с исл1ло повьииснид ум; 0;1 ен1:к, в него вве- . день дополкительнын .ч,е.;иггечь частоть, два дополнител,иы.х тригге));.. ., i,ono;j:iHTejihHb e элеменTi-, И. элелгеиты ИЛИ и два ологс; 1;1д1ккац(1И каждый из которых состоит из грех трехнходовых элементов И. пходы первого из icoiopbix по.Ллпчекы к .нулевым. ВЫХО.ДЗМ,. кроме первого, разрлдоз счетчика, а входы второго и третьего- к в:;,оду ncpaorti трехвходового элемента И и соотБет:твенио к ;улевому и единич выходам первого раз) счетч;., upji этом i;i-i:.oA второго элемента 1-1 спелииси с одиимчным вхоuoivi licpBoro цополнителыигго -ipi-j гора и с первыми ЕУО/шми псрмго я второго до1;олииуельных элементов И, второй вход nei) из г;оторых подключен к запре ;л;иощему входу гулчя гор., к одному из выходов второго триггера и q:Ui.(M ккодам блоков HtmriKriujtH, авыход - к 1)срБОГ.,у первого элемента ИЛИ, второй вход KDH/jioro через де. .пель частоты еоедипе; с выходом inopoio злеглс-н а И, второй вход которого соединен со вторым ЕЫКОДОМ второго .1,ополинтелыюго триггер;;, )улс;5сГ1 вход которого подключен к пыходу сумматора, к ну;швым входаы доп,о:1 те ты5ых тркггероь и к иуде)ому входу nevij-joro CierMviKa, а выход асрвого пле:менга ИЛИ соедмчен е Heppf-ifjH иходамп грргьего и четвертого допоп ппе,чьмь;:,: элементов И, вход) которых подл- пючсиь; к .дам rrroporo дог;с).И(1Итедьно1о триггера и соогг-чтетнеш.о ко вторым входам второго и }i piiOro блоков iiHiUiKauint, приче -; выход третьего допол п;тедьно1о злемен/л 11 1;о:1;слючеи к сумMipyfCivervty входу первого и i: вьг-г}Г1аю иему входу BTOpOio ечетчшсов, а выхо.д четверто о пополнительного элемсага Г - к еук.мирую:, «ходу второго

к вычитающему входу первого счетчиков, разрядные выходы которых подключены ко входам блоков индикации, единичные выходы которых соединены со входами второго элемента ИЛИ, выход которого через пятый дополнительный элемент И соединен с нулевым входом первого дополнительного триггера, с выходом дополнительного делителя частоты и с первым входом шестого допо)шительного элемента И, второй вход которого подключен ко входу дополнительного делителя частота, к счетному входу второго дoпoJfflИteльнoгo триггера и к выходу третьего элемента ИЛИ, входы которого соединены с нулевыми выходами блоков иидикаини, а выход шестого дополнительного элемента И - к первому входу су-мкгатора, второй вход которого подключен к клемме источннка входного сигнала.

Источники информации, принятые во внимание при экспертизе;

1.Йатент США 3753125, кл. 328-38,l973 г.

2.Патент Японии № 47-33977, кл. 98/5/ С32,

1972г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блокаСРАВНЕНия дВуХ чиСЕл | 1978 |

|

SU798843A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| Генератор последовательности чисел | 1981 |

|

SU999032A1 |

| Частотный детектор | 1982 |

|

SU1137563A1 |

| Цифровое измерительное устройство для обработки сигналов частотных датчиков | 1989 |

|

SU1659891A1 |

| Многоканальное усредняющее устройство | 1978 |

|

SU744609A1 |

| Делитель частоты | 1973 |

|

SU519865A1 |

| Устройство для измерения скорости телеграфирования | 1974 |

|

SU547042A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОКАЗАТЕЛЕЙ КАЧЕСТВА ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 1991 |

|

RU2022348C1 |

J

Авторы

Даты

1976-07-05—Публикация

1975-02-07—Подача