Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано для контроля экспоненциальных переходных процессов в различных технологических объектах, например энергоблоках электростанций.

Цель изобретения - повышение быстродействия контроля установившихся значений экспоненциальных процессов.

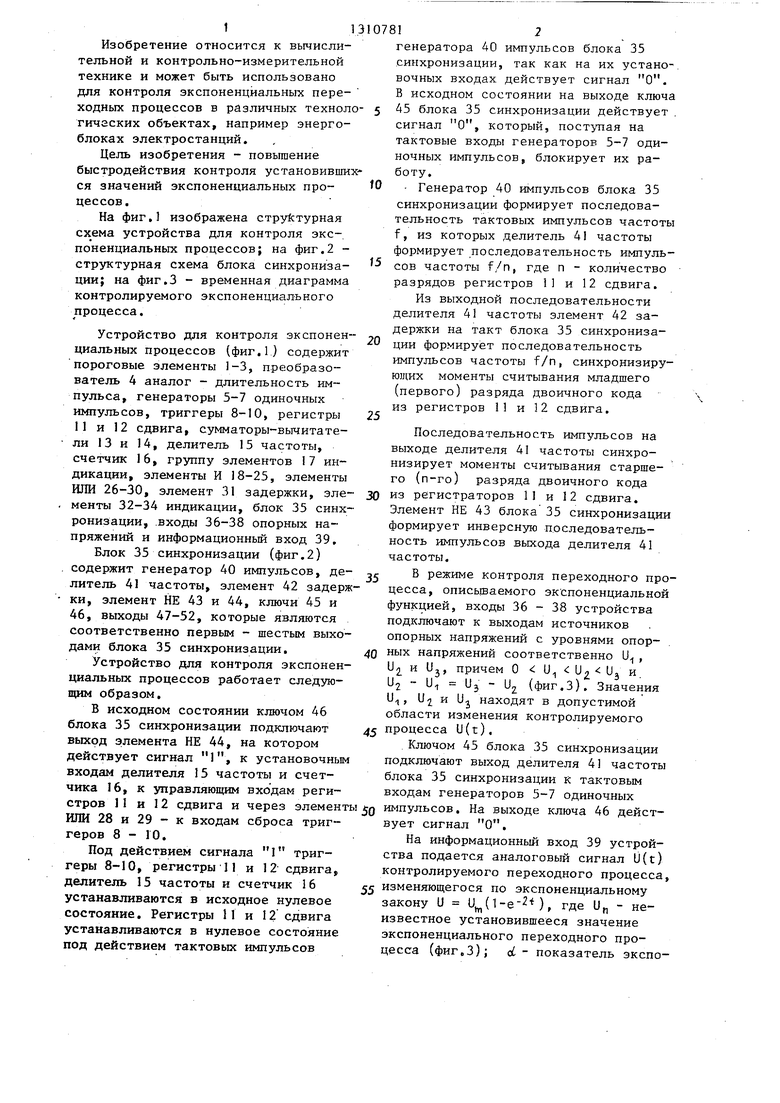

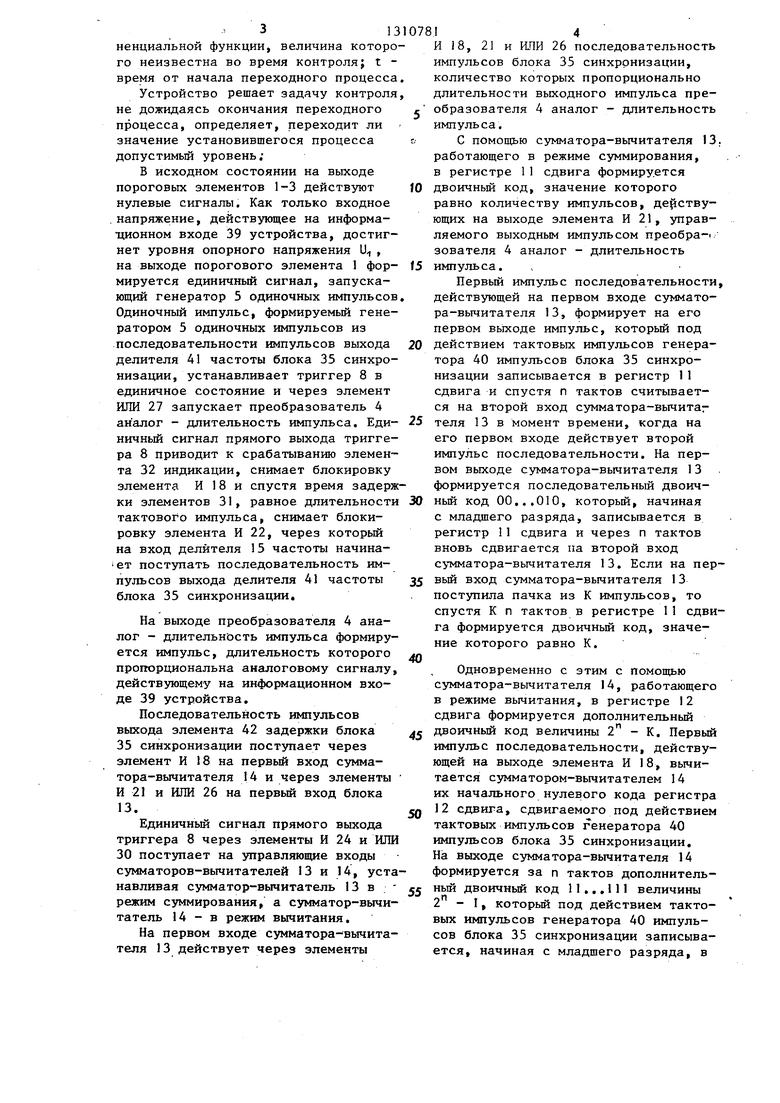

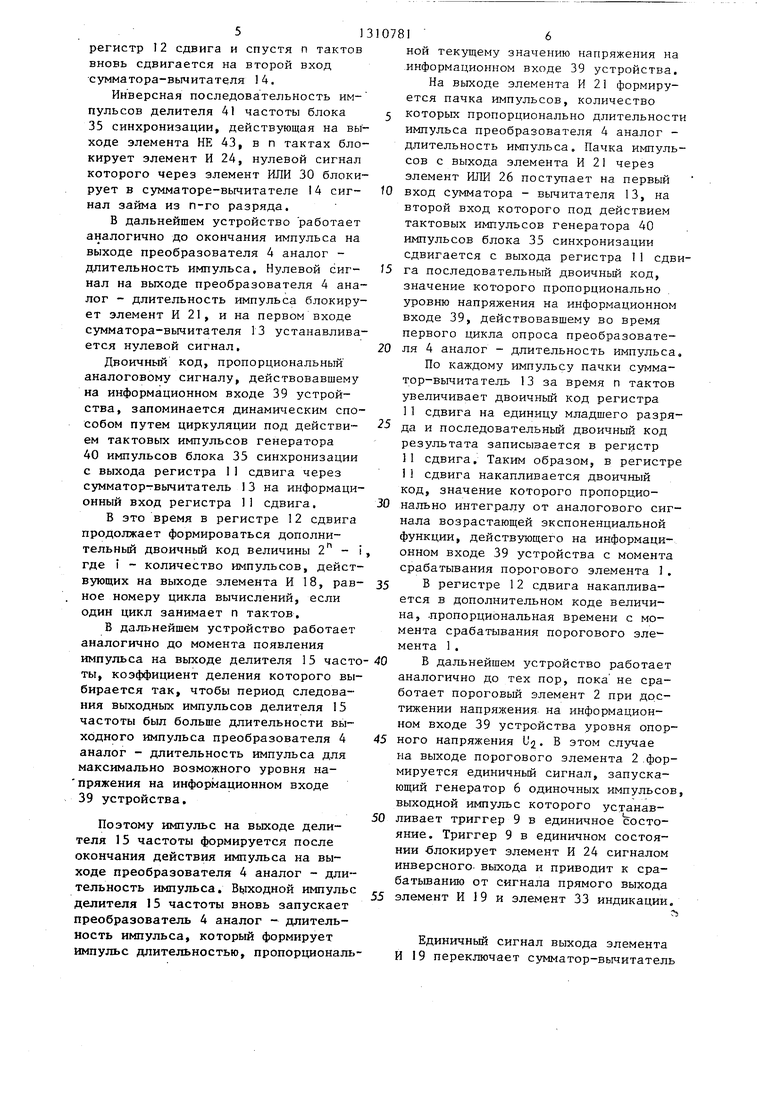

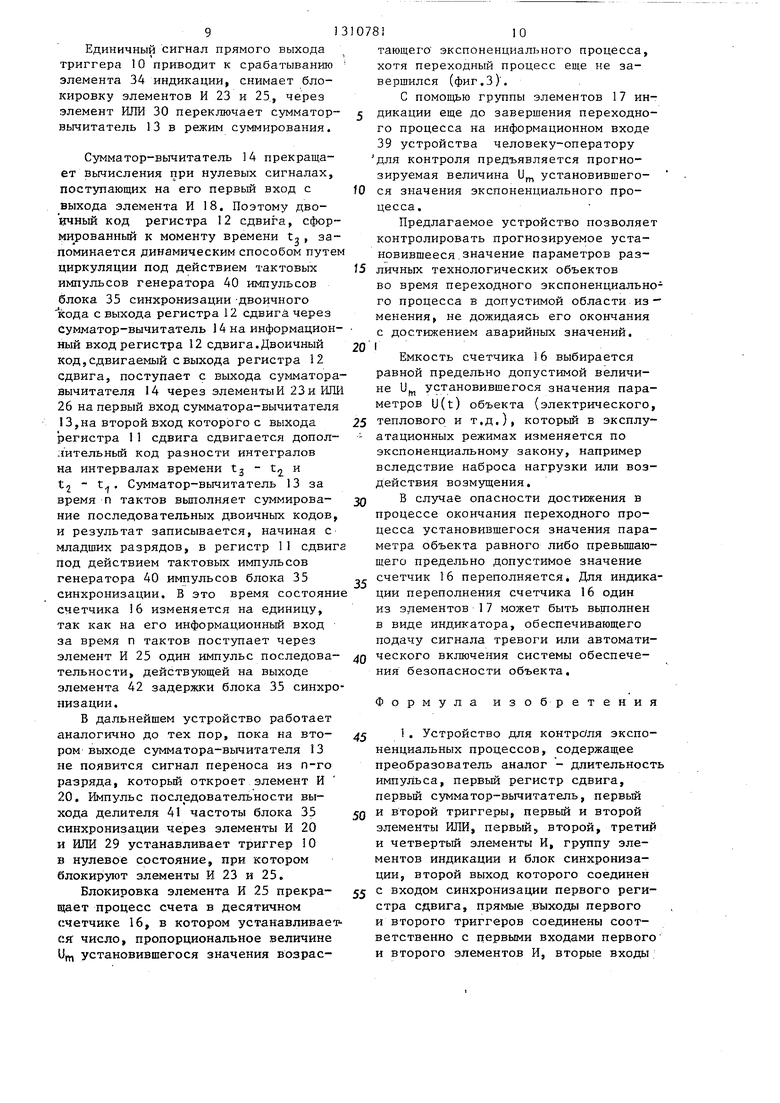

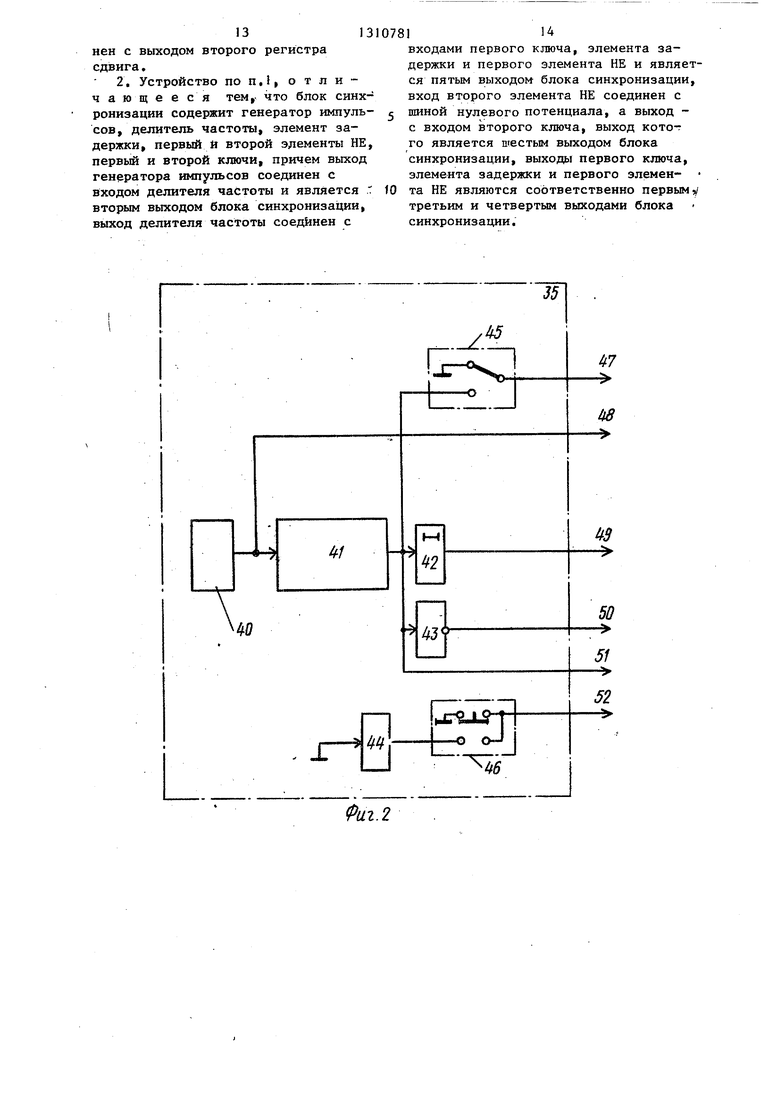

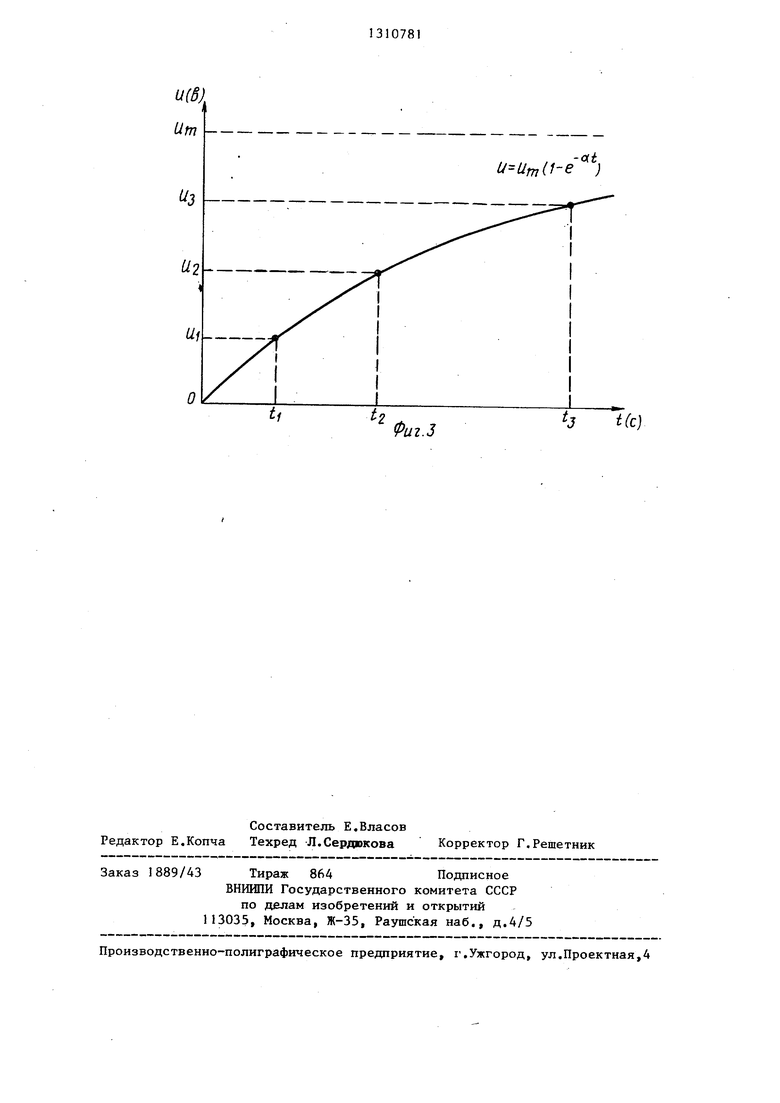

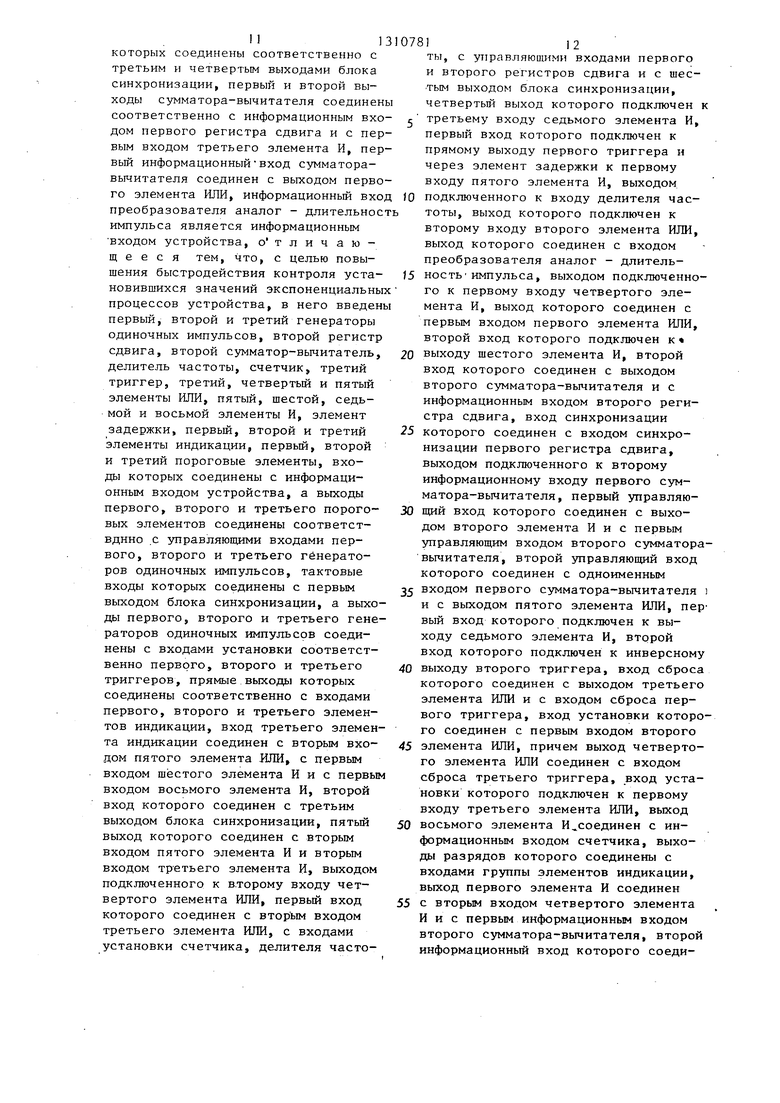

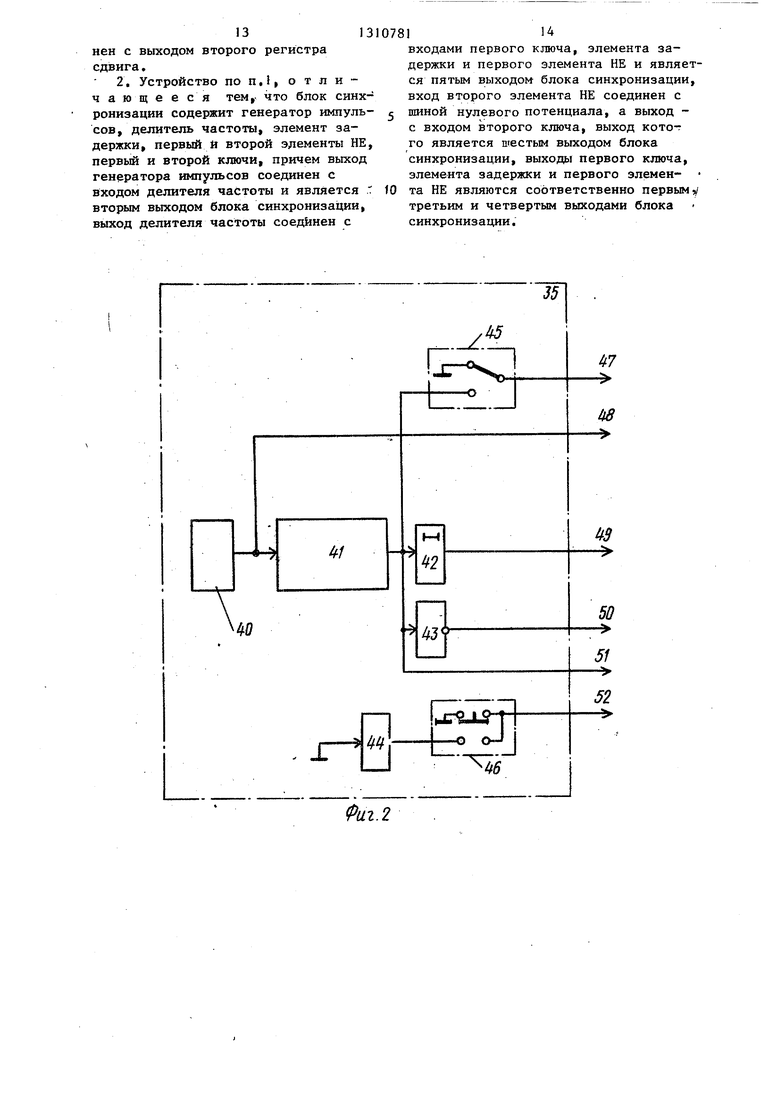

На фиг.1 изображена структурная схема устройства для контроля экспоненциальных процессов; на фиг.2 - структурная схема блока синхронизации; на фиг.З - временная диаграмма контролируемого экспоненциального процесса.

Устройство для контроля экспоненциальных процессов (фиг.1) содержит пороговые элементы 1-3, преобразователь 4 аналог - длительность импульса, генераторы 5-7 одиночных импульсов, триггеры 8-10, регистры 11 и 12 сдвига, сумматоры-вьгчитате- ли 13 и 14, делитель 15 частоты, счетчик 16, группу элементов 17 индикации, элементы И 18-25, элементы

10

15

20

25

генератора 40 импульсов блока 35 синхронизации, так как на их установочных входах действует сигнал О. В исходном состоянии на выходе ключа 45 блока 35 синхронизации действует . сигнал О, который, поступая на тактовые вход генераторов 5-7 одиночных импульсов, блокирует их работу,

Генератор 40 импульсов блока 35 синхронизации формирует последовательность тактовых импульсов частоты f, из которых делитель 41 частоты формирует последовательность импульсов частоты f/n, где п - количество разрядов регистров 11 и 12 сдвига.

Из выходной последовательности делителя 41 частоты элемент 42 задержки на такт блока 35 синхронизации формирует последовательность импульсов частоты f/n, синхронизирующих моменты считывания младшего (первого) разряда двоичного кода из регистров 1 и 12 сдвига.

Последовательность импульсов на выходе делителя 41 частоты синхронизирует моменты считывания старшего (п-го) разряда двоичного кода ИЛИ 26-30, элемент 31 задержки, эле- ЗО из регистраторов 11 и 12 сдвига, менты 32-34 индикации, блок 35 синх- Элемент НЕ 43 блока 35 синхронизации ронизации, .входы 36-38 опорных напряжений и информационный вход 39.

формирует инверсную последовательность импульсов выхода делителя 41 частоты.

Блок 35 синхронизации (фиг.2) содержит генератор 40 импульсов, де- литель 41 частоты, элемент 42 задержки, элемент НЕ 43 и 44, ключи 45 и 46, выходы 47-52, которые являются соответственно первым - шестым выходами блока 35 синхронизации.

Устройство для контроля экспоненциальных процессов работает следующим образом.

В исходном состоянии ключом 46 блока 35 синхронизации подключают выход Э1лемента НЕ 44, на котором действует сигнал 1, к установочным входам делителя 15 частоты и счетчика 16, к управляющим входам регистров 1 и 12 сдвига и через элементы Q импульсов. На выходе ключа 46 дейстИПИ 28 и 29 - к входам сброса триггеров 8-10.

Под действием сигнала I триггеры 8-10, регистры 11 и 12 сдвига, делитель 15 частоты и счетчик 16 устанавливаются в исходное нулевое состояние. Регистры 11 и 12 сдвига устанавливаются в нулевое состояние под действием тактовых импульсов

вует сигнал О.

На информационный вход 39 устройства подается аналоговый сигнал Ll(t) контролируемого переходного процесса, ;j изменяющегося по экспоненциальному закону и и(1-е 2) где и„ - неизвестное установившееся значение экспоненциального переходного процесса (фиг.З); oi - показатель экспо

генератора 40 импульсов блока 35 синхронизации, так как на их устано. вочных входах действует сигнал О. В исходном состоянии на выходе ключа 45 блока 35 синхронизации действует . сигнал О, который, поступая на тактовые вход генераторов 5-7 одиночных импульсов, блокирует их работу,

Генератор 40 импульсов блока 35 синхронизации формирует последовательность тактовых импульсов частоты f, из которых делитель 41 частоты формирует последовательность импульсов частоты f/n, где п - количество разрядов регистров 11 и 12 сдвига.

Из выходной последовательности делителя 41 частоты элемент 42 задержки на такт блока 35 синхронизации формирует последовательность импульсов частоты f/n, синхронизирующих моменты считывания младшего (первого) разряда двоичного кода из регистров 1 и 12 сдвига.

Последовательность импульсов на выходе делителя 41 частоты синхронизирует моменты считывания старшего (п-го) разряда двоичного кода из регистраторов 11 и 12 сдвига, Элемент НЕ 43 блока 35 синхронизации

формирует инверсную последовательность импульсов выхода делителя 41 частоты.

В режиме контроля переходного процесса, описьшаемого экспоненциальной функцией, входы 36 - 38 устройства подключают к выходам источников опорных напряжений с уровнями опор40 ных напряжений соответственно U, U2 и Uj, причем О U : U U и. U2 - U Uj - U (фиг.З), Значения U, U и Uj находят в допустимой области изменения контролируемого

45 процесса Ll(t),

Ключом 45 блока 35 синхронизации подключают выход делителя 4 частот блока 35 синхронизации к тактовым входам генераторов 5-7 одиночных

Q импульсов. На выходе ключа 46 действует сигнал О.

На информационный вход 39 устройства подается аналоговый сигнал Ll(t) контролируемого переходного процесса, ;j изменяющегося по экспоненциальному закону и и(1-е 2) где и„ - неизвестное установившееся значение экспоненциального переходного процесса (фиг.З); oi - показатель экспо 3131

енциальной функции, величина которого неизвестна во время контроля; t - время от начала переходного процесса.

Устройство решает задачу контроля, не дожидаясь окончания переходного процесса, определяет, переходит ли значение установившегося процесса опустимый уровень;

В исходном состоянии на выходе ороговых элементов 1-3 действуют нулевые сигналы. Как только входное напряжение, действующее на информаионном входе 39 устройства, достигнет уровня опорного напряжения Щ, на выходе порогового элемента 1 форируется единичный сигнал, запускащий генератор 5 одиночных импульсов. Одиночный импульс, формируемый генератором 5 одиночных импульсов из последовательности импульсов выхода делителя 41 частоты блока 35 синхронизации, устанавливает триггер 8 в единичное состояние и через элемент ИЛИ 27 запускает преобразователь 4 ан алог - длительность импульса. Единичный сигнал прямого выхода триггера 8 приводит к срабатыванию элемента 32 индикации, снимает блокировку элемента И 18 и спустя время задержки элементов 31, равное длительности тактовог о импульса, снимает блокировку элемента И 22, через который на вход делителя 15 частоты начина- ет поступать последовательность импульсов выхода делителя 41 частоты блока 35 синхронизации.

На выходе преобразователя 4 аналог - длительность импульса формируется импульс, длительность которого проггорциональна аналоговому сигналу, действующему на информационном входе 39 устройства.

Последовательность импульсов выхода элемента 42 задержки блока 35 синхронизации поступает через элемент И 18 на первый вход сумма- тора-вычитателя 14 и через элементы И 21 и ИЛИ 26 на первый вход блока 13.

Единичный сигнал прямого выхода триггера 8 через элементы И 24 и ИЛИ 30 поступает на управляющие входы сумматоров-вычитателей 13 и 14, устанавливая сумматор-вычитатель 13 в - режим суммирования, а сумматор-вычитатель 14 - в режим вычитания.

На первом входе сумматора-вычита- теля 13 действует через элементы

14

И 18, 21 и ИЛИ 26 последовательность импульсов блока 35 синхронизации, количество которых пропорционально длительности выходного импульса пре- образователя 4 аналог - длительность импульса.

С помощью сумматора-вычитателя 13. работающего в режиме суммирования, в регистре 11 сдвига формируется

двоичньй код, значение которого

равно количеству импульсов, дерству- ющих на выходе элемента И 21, управляемого выходным импульсом преобра-1 зователя 4 аналог - длительность

импульса.

Первый импульс последовательности, действующей на первом входе сумматора -вычитателя 13, формирует на его первом вьЬсоде импульс, который под

действием тактовых импульсов генератора 40 импульсов блока 35 синхронизации записывается в регистр 11 сдвига и спустя п тактов считывается на второй вход сзтмматора-вычитаг

теля 13 в момент времени, когда на его первом входе действует второй импульс последовательности. На первом выходе сумматора-вычитателя 13 формируется последовательный двоичный код 00...010, который, начиная с младшего разряда, записывается в регистр 11 сдвига и через п тактов вновь сдвигается па второй вход сумматора-вычитателя 13. Если на первый вход сумматора-вычитателя 13 поступила пачка из К импульсов, то спустя К п тактов в регистре 11 сдвига формируется двоичный код, значение которого равно К.

Одновременно с этим с помощью

сумматора-вычитателя 14, работающего в режиме вычитания, в регистре 12 сдвига формируется дополнительный

двоичный код величины 2 - К. Первый импульс последовательности, действующей на выходе элемента И 18, вычитается сумматором-вычитателем 14 их начального нулевого кода регистра

12 сдвига, сдвигаемого под действием тактовых импульсов генератора 40 импульсов блока 35 синхронизации. На выходе сумматора-вычитателя 14 формируется за п тактов дополнительньш двоичный код 11,,.111 величины 2 - I, который под действием тактовых импульсов генератора 40 импульсов блока 35 синхронизации записывается, начиная с младшего разряда, в

5 1з:

регистр I2 сдвига и спустя п тактов вновь сдвигается на второй вход сумматора-вычитателя 14.

Инверсная последовательность им- пульсов делителя 41 частоты блока 35 синхронизации, действующая на выходе элемента НЕ 43, в п тактах блокирует элемент И 24, нулевой сигнал которого через элемент ИЛИ 30 блокирует в сумматоре-вычитателе 14 сигнал займа из п-го разряда.

В дальнейшем устройство работает аналогично до окончания импульса на выходе преобразователя 4 аналог - длительность импульса. Нулевой сигнал на выходе преобразователя 4 аналог - длительность импульса блокирует элемент И 21, и на первом входе сумматора-вычитателя 13 устанавливается нулевой сигнал.

Двоичный код, пропорциональный аналоговому сигналу, действовавшему на информационном входе 39 устройства, запоминается динамическим способом путем циркуляции под действием тактовых импульсов генератора 40 импульсов блока 35 синхронизации с выхода регистра 11 сдвига через сумматор-вычитатель 13 на информационный вход регистра 11 сдвига,

В это время в регистре 12 сдвига продолжает формироваться дополнительный двоичный код величины 2 - i, где i - количество импульсов, действующих на выходе элемента И 18, равное номеру цикла вычислений, если один цикл занимает п тактов,

В дальнейшем устройство работает аналогично до момента появления импульса на выходе делителя 15 частоты, коэффициент деления которого выбирается так, чтобы период следования выходных импульсов делителя 15 частоты был больше длительности выходного импульса преобразователя 4 аналог - длительность импульса для максимально возможного уровня на- пряжения на информационном входе 39 устройства.

Поэтому импульс на выходе делиеля 15 частоты формируется после кончания действия импульса на выоде преобразователя 4 аналог - длиельность импульса. Выходной импульс елителя 15 частоты вновь запускает реобразователь 4 аналог - длительость импульса, который формирует мпульс длительностью, пропорциональ16

ной текущему значению напряжения на .информационном входе 39 устройства. На выходе элемента И 21 формируется пачка импульсов, количество

которых пропорционально длительности импульса преобразователя 4 аналог - длительность импульса. Пачка импульсов с выхода элемента И 21 через элемент ШШ 26 поступает на первый

вход сумматора - вычитателя 13, на второй вход которого под действием тактовых импульсов генератора 40 импульсов блока 35 синхронизации сдвигается с выхода регистра 11 сдвига последовательный двоичный код, значение которого пропорционально уровню напряжения на информационном входе 39, действовавшему во время первого цикла опроса преобразователя 4 аналог - длительность импульса.

По каждому импульсу пачки сумматор-вычитатель 13 за время п тактов увеличивает двоичный код регистра 11 сдвига на единицу младшего разряда и последовательньш двоичный код результата записывается в регистр 11 сдвига. Таким образом, в регистре 1 сдвига накапливается двоичный код, значение которого пропорционально интегралу от аналогового сигнала возрастающей экспоненциальной функции, действующего на информационном входе 39 устройства с момента срабатывания порогового элемента 1,

В регистре 12 сдвига накапливается в дополнительном коде величина, -пропорциональная времени с момента срабатывания порогового элемента 1 ,

В дальнейшем устройство работает аналогично до тех пор, пока не сработает пороговый элемент 2 при достижении напряжения на информационном входе 39 устройства уровня опорного напряжения Uj. В этом случае на выходе порогового элемента 2 .формируется единичный сигнал, запускающий генератор 6 одиночных импульсов, выходной импульс которого устанавливает триггер 9 в единичное состояние. Триггер 9 в единичном состоянии блокирует элемент И 24 сигналом инверсного- выхода и приводит к сра- батьшанию от сигнала прямого выхода

элемент И 19 и элемент 33 индикации,

Единичный сигнал выхода элемента И 19 nepeKJD04aeT сумматор-вычитатель

713

13 в режим вычитания, а сумматор- вычитатель 14 - в режим суммирования К моменту срабатывания порогового элемента 2 в регистре 11 сдвига сформирован двоичный код, пропорциональный интегралу от входного напряжения действуюшего на информационном входе действующего на информационном входе 3 устройства на интервале времени где t. и t - моменты времени срабатывания соответственно пороговых элементов 1 и 2,

В регистре 12 сдвига сформирован дополнительный код 2 - S , где S - количество циклов вычислений на интервале времени t t Величина S пропорциональна интервалу времени tj t - S n/f, где n - количество разрядов регистров 11 и 12 сдвига; f - частота тактовых импульсов генератора 40 импульсов блока 35 синхронизации.

После срабатывания порогового элемента 2 сумматор-вычитатель 13 производит вычитание из двоичного кода регистра 11 сдвига пачек импульсов, формируемых на выходе элемента И 21 под действием выходных импульсов преобразователя 4 аналог-длительность импульса, которьй опрашивается через элемент ИЛИ 27 последовательностью импульсов делителя 15 частоты

По каждому импульсу, действующему на первом входе, сумматор-вычитатель 13 уменьшает за время n тактов двоичньш код, сдвигаемый с выхода регистра 11 сдвига, на единицу млад- шего разряда и результат вычитания вновь записывается в регистр 11 сдвига под действием тактовых импульсов генератора 40 импульсов блока 35 синхронизации.

В это время по каждому импульсу, действующему на выходе элемента И 18, сумматор-вычитатель 14 увеличивает за время n тактов дополнительный двоичный код, сдвигаемый с выхода регистра 12 сдвига, на единицу младшего разряда и результат суммирования вновь сдвигается в регистр 12 сдвига под действием тактовых импульсов генератора 40 импульсов блока 35 синхронизации.

.Инверсная последовательность импульсов делителя 41 частоты блока 35 синхронизации, действующая на выходе элемента НЕ 43, в п-тактах блокирует элемент И 19, нулевой сиг18

нал которого блокируется в суммато- ре-вьгчитателе 13, сигнал займа из п-го разряда, а в сумматоре-вычита- теле 14 - сигнал переноса из п-го

разряда.

В дальнейшем устройство работает аналогично до тех пор, пока уровень входного уровня опорного напряжения Uj. В этом случае срабатьшает пороговый элемент 3, выходной сигнал которого запускает генератор 7 одиночных импульсов. Одиночный импульс генератора 7 одиночных импульсов устанавливает триггер 10 в единичное

состояние и через элемент ИЛИ 28 устанавливает в О триггеры 8 и 9. К моменту срабатывания порогового элемента 3 в регистре 11 сдвига сформируется дополнительный код разности интегралов от возрастающей экспоненциальной функции на интервалах времени t, - tj и t2 t, где t J - момент времени срабатывания порогового элемента 3. Разность интегралов в регистре 11 сдвига формируется в дополнительном коде, так как при уровнях опорных напряжений Uj - U2 и - и интеграл от воз- :растающей экспоненциальной функции

на интервале t - t всегда больше интеграла на интервале t 11 (фиг.З).

В регистре 12 сдвига к моменту времени tj формируется двоичный

код, пропорциональный разности интервалов времени (tj- t) - (tj - ti) (Sj - Si)n/f, где S - количество циклов вычислений на интервале вре- мени t,, - t2- Двоичный код в регистре 12 сдвига к моменту времени t, положителен, так как при уровнях опорных напряжений Uj - U2 U j - U для возрастающей экспоненциальной функции всегда (.tj) (z i

Триггеры 8 и 9 после установки их в нулевое состояние блокируют соответственно элементы И 24 и 19.

Нулевой сигнал прямрго выхода триггера 8 через элемент 31 задержки блокирует элемент И 22, прекращая поступление импульсов на входе делителя 15 частоты. Элемент И 18 также

переходит в режим блокировки под действием нулевого сигнала прямого выхода триггера 8. Нулевой сигнал выхода элемента И 18 блокирует элемент. И 21 .

91

Единичный сигнал прямого выхода триггера 10 приводит к срабатыванию элемента 34 индикации, снимает блокировку элементов И 23 и 25, через элемент ИЛИ 30 переключает сумматор- вычитатель 13 в режим суммирования.

Сумматор-вьгчитатель 14 прекращает вычисления при нулевых сигналах, поступающих на его первый вход с выхода элемента И 18. Поэтому двоичный код регистра 12 сдвига, сформированный к моменту времени t,, запоминается динамическим способом путем циркуляции под действием тактовых импульсов генератора 40 импульсов

блока 35 синхронизации -двоичного Кода с выхода регистра 12 сдвига через сумматор-вычитатель 14 на информационный вход регистра 12 сдвига.Двоичный код,сдвигаемый с выхода регистра 12 сдвига, поступает с выхода сумматора вычитателя )4 через элементы И 23 и ШШ 26 на первый вход сумматора-вычитателя 13,на второй вход которого с выхода регистра 11 сдвига сдвигается допол- лительный код разности интегралов на интервалах времени tj - t-j, и t2 t, Сумматор-вычитатель 13 за время п тактов выполняет суммирование последовательных двоичных кодов, и результат записывается, начиная с младших разрядов, в регистр 11 сдвиг под действием тактовых импульсов генератора 40 импульсов блока 35 синхронизации. В это время состояни счетчика 16 изменяется на единицу, так как на его информационный вход за время п тактов поступает через элемент И 25 один импульс последовательности, действующей на выходе элемента 42 задержки блока 35 синхронизации.

В дальнейшем устройство работает аналогично до тех пор, пока на втором выходе сумматора-вычитателя 13 не появится сигнал переноса из п-го разряда, которьй откроет элемент И 20, Импульс последовательности выхода делителя 41 частоты блока 35 синхронизации через элементы И 20 и ИЛИ 29 устанавливает триггер 10 в нулевое состояние, при котором блокируют элементы И 23 и 25.

Блокировка элемента И 25 прекращает процесс счета в десятичном счетчике 16, в котором устанавливав р ся число, пропорциональное величине Uni установившегося значения возрас0781

10

тающего экспоненциального процесса, хотя переходный процесс еще не завершился (фиг.З).

С помощью группы элементов 17 индикации еще до завершения переходного процесса на информационном входе 39 устройства человеку-оператору для контроля предъявляется прогнозируемая величина U, установившегося значения экспоненциального процесса.

Предлагаемое устройство позволяет контролировать прогнозируемое установившееся, значение параметров различных технологических объектов

во время переходного экспоненциального процесса в допустимой области из- менения, не дожидаясь его окончания с достижением аварийных значений.

I

Емкость счетчика 16 выбирается

равной предельно допустимой величине и установившегося значения параметров U(t) объекта (электрического,

теплового и т.д.), который в эксплу- атационных режимах изменяется по экспоненциальному закону, например вследствие наброса нагрузки или воздействия возмущения.

В случае опасности достижения в процессе окончания переходного процесса установившегося значения параметра, объекта равного либо превьшгаю- щего предельно допустимое значение счетчик 16 переполняется. Для индикации переполнения счетчика 16 один из элементов 17 может быть вьшолнен в виде индикатора, обеспечивающего подачу сигнала тревоги или автоматического включения системы обеспечения безопасности объекта.

Формула изобретения

1 . Устройство для контрс/ля экспоненциальных процессов, содержащее преобразователь аналог - длительность импульса, первый регистр сдвига, первьш сумматор-вычитатель, первьй

и второй триггеры, первый и второй элементы ИПИ, первый, второй, третий и четвертый эле1 1енты И, группу элементов индикации и блок синхронизации, второй выход которого соединен

с входом синхронизации первого регистра сдвига, прямые .выходы первого и второго триггеров соединены соответственно с первыми входами первого и второго элементов И, вторые входы

1113

которых соединены соответственно с третьим и четвертым выходами блока синхронизации, первый и второй выходы сумматора-вычитателя соединены соответственно с информационным вхо- дом первого регистра сдвига и с первым входом третьего элемента И, первый информационныйвход сумматора- вычитателя соединен с выходом первого элемента ИЛИ, информационный вход преобразователя аналог - длительност импульса является информационным ВХОДОМ устройства, о тличаю- щ е е с я тем, что, с целью повышения быстродействия контроля уста- новившихся значений экспоненциальных процессов устройства, в него введены первый, второй и третий генераторы одиночных импульсов, второй регистр сдвига, второй сумматор-вычитатель, делитель частоты, счетчик, третий триггер, третий, четвертый и пятый элементы ИЛИ, пятый, шестой, седьмой и восьмой элементы И, элемент задержки, первый, второй и третий элементы индикации, первый, второй и третий пороговые элементы, входы которых соединены с информационным входом устройства, а выходы первого, второго и третьего порого- вых элементов соединены соответст- вднно .с управляющими входами первого, второго и третьего гбнерато- ров одиночных импульсов, тактовые входы которых соединены с первым выходом блока синхронизации, а выходы первого, второго и третьего генераторов одиночных импульсов соединены с входами установки соответственно первого, второго и третьего триггеров, прямые выходы которых соединены соответственно с входами первого, второго и третьего элементов индикации, вход третьего элемента индикации соединен с вторым вхо- дом пятого элемента ИЛИ, с первым входом шестого элемента И и с первым входом восьмого элемента И, второй вход которого соединен с третьим выходом блока синхронизации, пятый выход которого соединен с вторым входом пятого элемента И и вторым входом тр-етьего элемента И, выходом подключенного к второму входу четвертого элемента ИЛИ, первый вход которого соединен с втор ым входом третьего элемента ИЛИ, с входами установки счетчика, делителя часто12

ты, с управляющими входами первого и второго регистров сдвига и с шес- Тым выходом блока синхронизации, четвертый выход которого подключен к третьему входу седьмого элемента И, первый вход которого подключен к прямому выходу первого триггера и через элемент задержки к первому входу пятого элемента И, выходом подключенного к входу делителя частоты, выход которого подключен к второму входу второго элемента ИЛИ, выход которого соединен с входом преобразователя аналог - длительность импульса, выходом подключенного к первому входу четвертого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к« выходу шестого элемента И, второй вход которого соединен с выходом второго сумматора-вычитателя и с информационные входом второго регистра сдвига, вход синхронизации которого соединен с входом синхронизации первого регистра сдвига, выходом подключенного к второму информационному входу первого сумматора-вычитателя, первый управляющий вход которого соединен с выходом второго элемента И и с первым управляющим входом второго сумматора вычитателя, второй управляющий вход которого соединен с одноименным входом первого сумматора-вычитателя и с выходом пятого элемента ИЛИ, первый вход которого подключен к выходу седьмого элемента И, второй вход которого подключен к инверсному выходу второго триггера, вход сброса которого соединен с выходом третьего элемента ИЛИ и с входом сброса первого триггера, вход установки которого соединен с первым входом второго элемента ИЛИ, причем выход четвертого элемента ИЛИ соединен с входом сброса третьего триггера, вход установки которого подключен к первому входу третьего элемента ИЛИ, выход восьмого элемента И,соединен с информационным входом счетчика, выходы разрядов которого соединены с входами группы элементов индикации, выход первого элемента И соединен с вторым входом четвертого элемента И и с первым информационным входом второго сумматора-вычитателя, второй информационный вход которого соеди13131

нен с выходом второго регистра сдвига.

2, Устройство по п,1, о т л и чающееся тем что блок синхронизации содержит генератор иьтуль- сов, делитель частоты, элемент задержки, первый и второй элементы НЕ, первый и второй ключи, причем выход генератора импульсов соединен с входом делителя частоты и является вторым выходом блока синхронизации, выход делителя частоты соединен с

Фаг.2

114

входами первого ключа, элемента задержки и первого элемента НЕ и является пятым выходом блока синхронизации, вход второго элемента НЕ соединен с шиной нулевого потенциала, а выход - с входом второго ключа, выход кото- го является шестым выходом блока синхронизации, выходы первого ключа, элемента задержки и первого элемента НЕ являются соответственно первым у третьим и четвертым выходами блока синхронизации.

Щ

yV

(i-e )

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1335989A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано для контроля экспоненциальных переходных процессов в различных технологических объектах, например энергоблоках электростанций. Цель изобрети тения состоит в повышении быстродействия контроля установившихся значений экспоненциальных процессов. Устройство для контроля экспоненциальных процессов содержит пороговые элементы 1-3, преобразователь аналог - длительность импульс а 4, генераторы одиночных импульсов 5-7, триггеры 8-10, регистры сдвига 11 и 12, сумматоры-вычитатели 13 и 14, делитель частоты 15, счетчик 16, группу элементов индикации 17, элементы И 18-25, элементы ИЛИ 26-30, элемент задержки 31, элементы индикации 32- 34 и блок синхронизации 35. Устройство повьшает быстродействие контроля установившегося значения экспоненциального процесса за счет прогнозирования этого значения, а также определяет, переходит ли это значение допустимьй уровень. 1 з.п.ф-лы-, 3 ил. jr i СЛ со. 00

Составитель Е.Власов Редактор Е.Копча Техред Л.Сердвкова

Заказ 1889/43 Тираж 864Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Корректор Г.Решетник

| Устройство для допускового контроля | 1980 |

|

SU898390A2 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для допускового контроля параметров объектов | 1982 |

|

SU1056134A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-05-15—Публикация

1986-02-26—Подача