Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных системах, работающих в реальном масштабе времени, для организации обмена информацией между внешними абонентами вычислительной машины и ее основной памятью.

Известны мультиплексные каналы, содержащие блок памяти подканалов, соединенный с блоком сопряжения с вычислительной машиной, который подключен к регистру адреса данных, регистру кода операций, регистру признаков и счетчику массива данных. Регистр адреса данных соединен с блоком совпадения. Входы регистра адреса данных, регистра кода операций, регистра признаков и счетчика массива данных соединены с выходами блока управления, связанными с блоком сопряжения с устройством вводавывода. Устройство включает также регистр адреса шаблона, триггеры достижения значимости данных и чис ла повторений и счетчик массива данных и числа повторений, подключенные к блоку управления и блоку сопряжения с вычислительной машиной, регистр дг.нных соединен с блоком сопряжения

с вычислительной машиной и блоком переключения, триггер редактирования подключен к блоку управления, блок памяти редактируемых символов соединен с блоком переключения, который подключен к блоку сопряжения,с устройствами ввода-вывода, блоку управления редактирующих символов, блоку совпадения и регистру шабло10на, блок Пс1мяти редактирующих символов соединен также с блоком управления и счетчиком числа повторений, блок управления и счетчик числа повторений подключены к регистру шабло15на. В этих устройствах после выполнения каждого цикла содержимое счетчика массива данных уменьшается на величину, соответствукщую количеству переданных данных T

20

Недостатком этих устройств является низкая пропускная способность, обусловленная невозможностью одновременной обработки и передачи или приема массива данных.

25

Наиболее близким к предлагаемому по технической сущности является мультиплексный канал, содержащий регистр кода операции и указателей, регистр адреса управляющего слова,

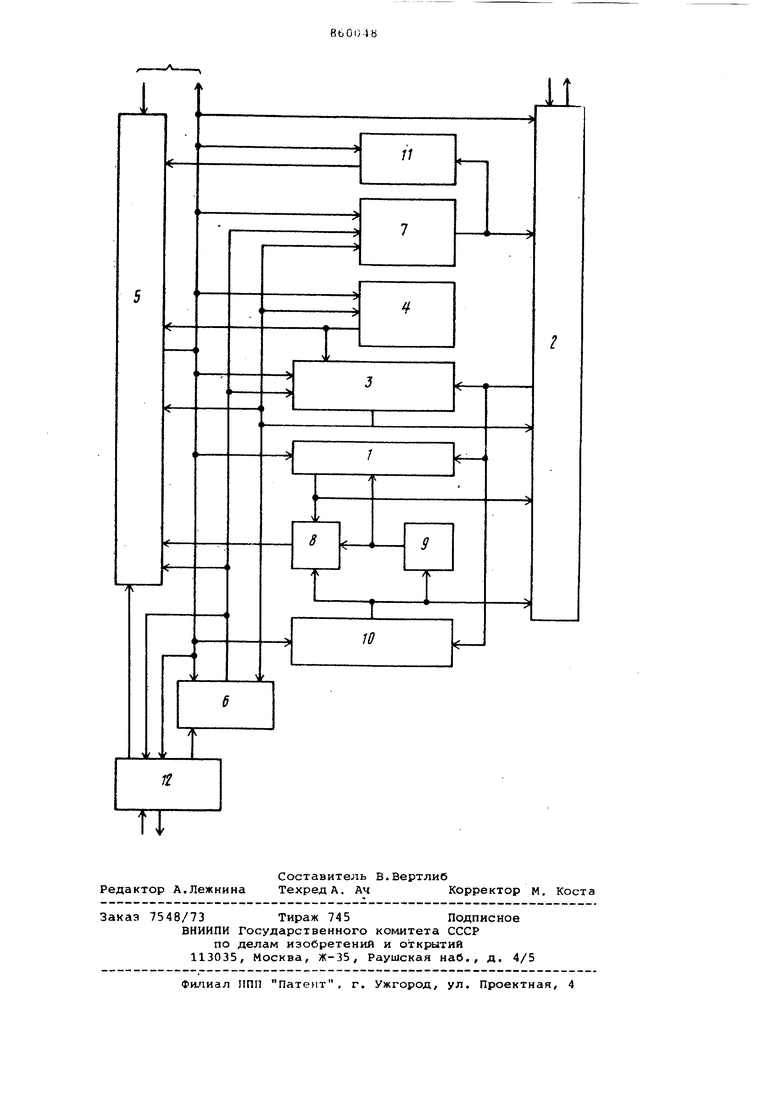

30 регистр текущего адреса, гчетчик | 1анных, регистр связи с интерфейсом, счетчик байтов, регистр номера активного подканала, регистр команд ввода-вывода узел управления каналом и связи с процессором, блок памяти подканалов, узел связи с оперативной памятью и узел связи с внеш ними устройствами, причем вход и выход регистра номера активного под канала соединены соответственно с бл ком памяти подканалов и входами узла связи с оперативной памятью и регистром связи с интерфейсом, выход регистра команд ввода-вывода подключены ко входам блока Псьмяти подканалов и узла управления каналом и связи с процессором, выход которого под ключен к управляющим входг м и выхода регистра кода операций и указателей, регистра текущего адреса, регистра адреса управляющего слова, счетчика байтов и регистра связи с интерфейсом, информационными входами и выходами подключенных к соответствуклдим входам и выходам блока памяти подканалов и узла связи с оперативной памятью.. Недостатком этого канала является низкая пропускная способность невозможности одновременной обработки и передачи или приема массива дан ных вследствие асинхронности процессов обмена и обработки и отсутствия возможности изменения со стороны процессора в процессе обмена размера передаваемого или принимаемого каналом массива данных. Это приводит также к большим аппаратурным затраTciM из-за необходимости иметь значительные объемы памяти для хранения данных обмена потерям времени на выполнение в канале вспомогатель ных операций: пуска и останова под канала и абонентов, ожидания обслуживания запроса канала на прерыва ние программы процессора по концу обмена. Цель изобретения - повышение пропускной способности мультиплексного канала путем организации обмена по кольцевой зоне. Поставленная цель достигается тем что в мультиплексный кангш, содержащий узел связи с процессором, соединенный первьм входом и выходом . соот ветственно с первыми входом и выходо канала, а вторым входом - с выходом регистра команд и данных и первьми входами регистра номера активного подканала, счетчика байтов, регистра связи с интерфейсом и узла связи с оперативной памятью, нтоцмле входы которых подключены к выходу узла связи с процессором- и первьлл входом узла связи с внешними устройствами,, регистра текуи;его адреса и регистра Команд и данных, второй вход которо го соединен с перньм выходом узла связи с оперативной памятью и вторым входом регистра текущего адреса а третий вход - с выходом регистра связи с интерфейсом, вторьл входом узла связи с внешними устройствами и третьими входами регистра номера активного подканала и узла связи с процессором, четвертым входом подключенного к выходу счетчика байтов и четвертому входу регистра команд и данных, а пятьм входом к первому выходу узла связи с внешними устройствами, второй выход которого соединен с третьим входом регистра связи с интерфейсом, а группой входов и выходов - соответственно с группой входов и выходов канала, выход регистра текущего адреса подключен к третьему входу узла связи с оперативной памятью, четвертый вход которого соединен с выходом регистра номера активного пoдкaнгLпa, а пятый вход и второй выход являются соответственно вторыми входом и выходом канала, введены схема сравнения, дешифратор, регистр адреса конца массива и регистр блокировки запросов, причем первый и второй входы регистра адреса конца массива соединены соответственно с первьм и вторым входами регистра текущего адреса, а выход - с первым входом схемы сравнения, шестым входом узла связи с оперативной памятью и через дешифратор с третьим входом регистра текущего адреса и вторьм входом схемы сравнения, третий вход и выход которой подключены соответственно к выходу регистра текущего адреса и шестому входу узла связи с процессором, седьмой вход и выход которого подключены соответственно к выходу и первому входу„, регистра блокировки запросов, вторым входом подключенного к выходу регистра номера активного подканала. На чеотеже представлена блок-схема предлагаемого мультиплексного канала . Мультиплексный канал содержит регистр 1 текущего адреса, узел 2 связи с оперативной памятью, регистр 3 команд данных, счетчик 4 байтов, узел 5 связи с процессором, регистр б связи с интерфейсом, регистр 7 номера активного подканала, схему 8 сравнения, дешифратор 9, регистр 10 адреса конца массива, регистр 11 блокировки запросов и узел 12 связи с внешними устройство1ми. Регистр 1 текущего адреса по своему функциональному назначению аналогичен регистру текущего адреса данных и регистру адреса управлягацего слова в известном устройстве, а регистр 3 и данных - регистру команд ввода-вывода и регистру кода операции и указателей в том же устройстве. Память подканалов размещена в фиксированных ячейках общего поля оперативной памяти к предназначена для хранения текущих параметров программ подканалов, относящихся к пассивным подканалам, либо параметров активного подканала, неиспольг зуемых в данныЛ момент в работе канала. Каждому подканалу отведена в оперативной памяти группа ячеек, в которых размещается адрес очередной команды программы подканала, текущий адрес данных, адрес конца обменного массива, текущее значение счетчика байтов управляющие признаки, характеризующие направление обмена и режима работы подканала. Подканалы в памяти располагаются по возрастанию номера подканала. При формировании адресов, ячеек памяти подкангшов используется содержимое регистра 7 номера активного подканала, поступающее на вход узла 2 связи с оперативной памятью.

Кроме обращения к ячейкам подканальной памяти, узел 2 обеспечивает чтение команд от процессора, располагаемых в фиксированной ячейке, отведенной для этой цели, чтение команд программы подканала, чтение или запись слов данных, запись слов состояния подканала. Нужное обращение в оперативную память имитируется управляк дими сигналами, поступающими на вход И2 узла 5. Адрес команды подканала либо данных определяется содержимьм регистра 1 текущего адреса, поступающим на вход узла 2. Информация, записываемая в оперативную память, поступает с регистров 1,3 и 10 в узел 2.

На регистре 1 производится формирование последовательных адресов обменного массива ячеек памяти либо программы подканала. Информация поступает из подканальной памяти через регистр 1 на вход узла 2, на который сигналы, управляющие занесением и счетом, поступают из узла 5. Сигналы дешифратора 9 определяют количество млс1дших разрядов регистра, участвующих в формировании текущего адреса при обмене по кольцевой зоне оперативной памяти, т.е. количество разрядов регистра, работающих в счетном режиме.

Регистр 3 команд и данных предназначен для хранения команды, хранения и формирования слов данных, слова состояния подканала и информации записываемой в подканальную память. Информация поступает на входы регистра 3 из узла 2, со счетчика 4 байтов и с регистра 6 связи с интерфейсом, а сигналы занесения.и признаки, записываемые в подканальную память ИСЛОВ состояния подканала, поступают в регистр 3 с узла 5, Обмен данными канала с оперативной памятью производится словами, обмен с внеишими устройствами - баОтлмк. Поэтом при чтении информации из йнешнего устройства канал производит ксмпановку слова из поступающих в него байтов, а при записи - развертку слова в последовательность байтов. Для определния конца компановки или развертки слова используется счетчик 4 байтов, который указывает номер последнего обработанного байта в текущем слове данных. Если за одно подключение внешнего устройства через узел 1 к каналу передается только один байт данных, то текущее значение дчетчика байтов хранится в подкангшьной памяти, а при переходе подканала в активное состояние возвращается на счетчик 4 через узел 2 и регистр 3. Сигналы, поступающие с выхода узла 5 управляют занесением на счетчик 4 информации и увеличением его содержимого на единицу.

Непосредственная связь канала с внешними устройствами осуществляется через регистр 6 связи с интерфейсом и узел 12, куда поступает информация, получаемая от внешних устройств, и откуда она выдается во внение устройства. Информация, предназначенная внешним устройствам, поступет на регистр 6 связи с интерфейсом с регистра 3, сигналы управления из узла 5, информация из шин интерфейса с выхода узла 12. На регистр 7 номера активного подканала информация переписывается либо-с регистра 6 либо с регистра 3.

Регистр 10 адреса конца массива предназначен для хранения в процессе выполнения операций обмена данньми с внешними устройствами младших разрядов адреса последней ячейки обменного массива. Разрядность регистра 1 определяет максимальный размер массива. Информация на регистр 10 поступает из подканальной памяти через узел 2, сигналы управления занесением - с узла 5.

Схема 8 сравнения формирует сигнал конца массива при обнаружении равенства содержимого регистра 10 младших разрядов регистра 1.

Дешифратор 9 формирует из содержимого старших разрядов регистра 10 сигналы, поступающие на второй вход схемы 8 сравнения и третий вход регистра 1 при выполнении операций обмена данными с внешним устройством по кольцевой зоне и ограничивающие со стороны старших разрядов количество разрядов содержимого регистров .1 и 10, которые участвуют в сравнении, и количество разрядов регистра 1, которые работают в режиме счета.

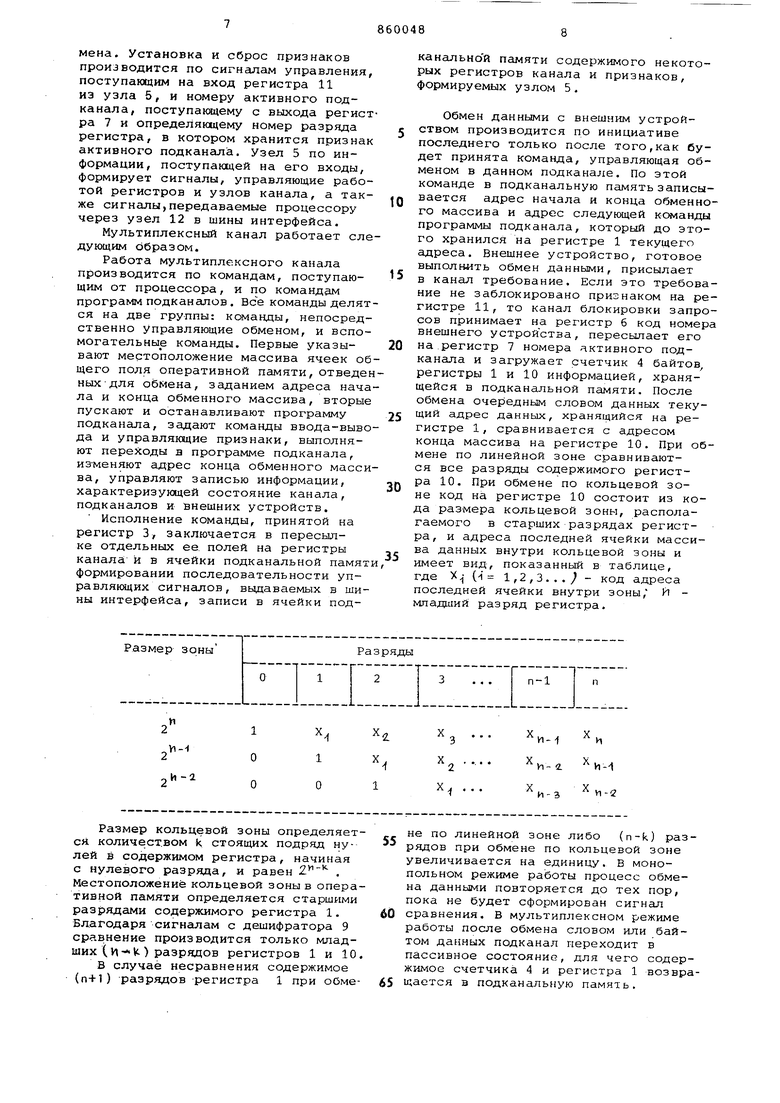

Регистр И блокировки запросов предназначен для хранения по каждому каналу признака, запрещающего обслуживание требования внешнего устройства на выполнение операции обмена. Установка и сброс признаков производится по сигналам управления поступающим на вход регистра 11 из узла 5, и номеру активного подканала, поступакядему с выхода регист ра 7 и определяющему номер разряда регистра, в котором хранится признак активного подканала. Узел 5 по информации, поступающей на его входы, формирует сигналы, управляющие работой регистров и узлов канала, а также сигналы,передаваемые процессору через узел 12 в шины интерфейса. Мультиплексный канал работает сле дующим образом. Работа мультиплексного канала производится по командам, поступающим от процессора, и по командам программ подканалов . команды делят ся на две гру-ппы: команды, непосред ственно управляющие обменом, и вспо могательные команды. Первые указывают местоположение массива ячеек о щего поля оперативной памяти, отведе ных для обмена, заданием адреса нач ла и конца обменного массива, вторы пускают и останавливают программу подканала, задают команды ввода-выв да и управлягацие признаки, выполняют переходы в программе подканала, изменяют адрес конца обменного масс ва, управляют записью информации, характеризующей состояние канала, подканалов и внешних устройств. Исполнение команды, принятой на регистр 3, заключается в пересылке отдельных ее полей на регистры канала.- и в ячейки подканальной памя формировании последовательности управляющих сигналов, выдаваемых в ши ны интерфейса, записи в ячейки подканальной памяти содержимого некотоых регистров канала и признаков, ормируемых узлом 5. Обмен данньами с внешним устройством производится по инициативе последнего только после того,как будет принята команда, управляющая обменом в данном подканале. По этой команде в подканальную память записывается адрес начала и конца обменного массива и адрес следующей команды программы подканала, который до этого хранился на регистре 1 текущего адреса. Внешнее устройство, готовое выполнить обмен данными, присылает в канал требование. Если это требование не заблокировано признаком на регистре 11, то канал блокировки запросов принимает на регистр б код номера внешнего устройства, пересылает его на регистр 7 номера активного подканала и загружает счетчик 4 байтов, регистры 1 и 10 информацией, хранящейся в подканальной памяти. После обмена очередным словом данных текущий адрес данных, хранящийся на регистре 1, сравнивается с адресом конца массива на регистре 10. При обмене по линейной зоне сравниваются все разряды содержимого регистра 10. При обмене по кольцевой зоне код на регистре 10 состоит из кода размера кольцевой зоны, располагаемого в старших разрядах регистра, и адреса последней ячейки массива данных внутри кольцевой зоны и имеет вид, показанный в таблице, где (1 1,2,3... - код адреса последней ячейки внутри зоны/ И младший разряд регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство отсчета времени в цвм | 1977 |

|

SU691828A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Система обмена | 1978 |

|

SU809138A1 |

| Мультиплексный канал | 1974 |

|

SU525941A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Мультиплексный канал | 1977 |

|

SU656048A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для сопряжения | 1978 |

|

SU813400A2 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

.Vl-,и-а

Размер кольцевой зоны определяется количеством k стоящих подряд нулей в содержимом регистра, начиная с нулевого разряда, и равен , Местоположение кольцевой зоны в оперативной памяти определяется старшими разрядами содержимого регистра 1. Благодаря сигналам с дешифратора 9 сравнение производится только младших ( И С- ) разрядов регистров 1 и 10.

В случае несравнения содержимое (п+1) разрядов регистра 1 при обме h-i ИИ

И-2

И- 3

не по линейной зоне либо (n-k) раз5рядов при обмене по кольцевой зоне увеличивается на единицу. В монопольном режиме работы процесс обмена данными повторяется до тех пор, пока не б.удет сформирован сигнал сравнения. В мультиплексном режиме работы после обмена словом или байтом данных подканал переходит в пассивное состояния, для чего содержимое счетчика 4 и регистра 1 возвращается в подканальную память.

По сигналу сравнения при обмане по линейной зоне на регистр 1 записывается из подканальной памяти адрес очередной команды программы подканала и канал переходит к выполнению следующих команд прогрс1ммы. При обмене по кольцевой зоне на регистре 11 устанавливается признак, блокирующий обмен по данному подканалу до тех пор, пока не поступит в канал команда, увеличивающая размер массива данных внутри кольцевой зоны.

Таким образом, мультиплексный канал осуществляет одновременную обработку и передачу или прием массива данных. Для этого процессор готовит в ЗУ информацию неЗольшими порциями, размещая ее в последовательные ячейки кольцевой зоны и сообщая каждый раз каналу об увеличении размера передаваемого массива данных, либо, обработав часть поступившей в кольцевую зону из канала информации, сообщает каналу об увеличении принимаемого массива данных на величину обработанной информации. Увеличение размера массива данных осуществ ляется изменением кода адреса конца массива внутри кольцевой зоны. Про- . цесс может длиться как угодно долго без прекращения обмена, что повышает пропускную способность канала за счет исключения многократных операций пуска и останова подканала и внешних устройств, необходимых при обмене по линейной зоне, экономит память вычислительныхсредств. Размер кольцевой зоны определяется нерегулярностью потока решаемых задач и стремится к величине, равной размеру двух сообщений, а пропускная способность канала стремится к величине, равной скорости передачи дачных между каналом и внешними устройствами. Одновременно сокращаются потери времени процессора на организацию обмена, что приводит к повышению производительности вычислительных средств.

Формула изобретения

Мультиплексный канал, содержащий .узел связи С процессором, соединенный первым входом и выходом соответственно с первьюли входом и выходом канала, а вторым входом - с выходом регистра команд и данных и первьми входами регистра номера активного подканала, счетчика байтов, регистра связи с интерфейсом и узла связи с оперативной памятью, вторые входы

KOTOfAJx по ;;: 1К1чены к выходу узла связи с 1фоцессором и первым входом узла связи с внешними устройствг ми, регистра текущего адреса и регистра команд и данных, второй вход которого соединен с первьФл выходом узла связи с оперативной памятью и вторым входом регистра текущего адреса, а третий вход - с выходом регистра связи с интерфейсом, вторьм входом узла связи с внешними устройствами и третьими входами регистра номера активного подканала и узла связи с процессором, четвертым входом подключенного к выходу счетчика байтов и четвертому входу регистра команд и данных, а пятым-входом - к первому выходу узла связи с внешними устройствами, второй выход которого соединен с третьим входом регистра связи и интерфейсом, а группой входов и выходов - соответственно с группой входов и выходов канала, выход регистра текущего адреса подключен .к третьему входу узла связи с оперативной памятью, четвертый вход которого соединен с выходом регистра номера активного подканала, а пятый вход и второй выход являются соответственно вторыми входом и выходом канала, о т л и ч аю щ и и с я тем, что, с целью повыиения пропускной способности канала, в него введены схема сравнения, де шифраторj регистр адреса конца массива и регистр блокировки запр -JB, причем первый и второй входы рс лстра адреса конца массива соединены соответственно с первым и вторым входами регистра текущего адреса, а выход - с первым входом схемы сравнения, шестьм входом узла связи с оперативной памятью и через дешифратор с третьим входом регистра текущего адреса и вторым входом схемы сравнения, третий вход и выход которой подключены соответственно к выходу регистра текущего адреса и шестому входу узла связи с процессором, седьмой вход и выход которого подключены соответственно к выходу и первому входу регистра блокировки запросов, BTOpfcSvi входом подключенного к выходу регистра номера активного подканала.

Источники информации принятые во внимание при экспертизе

И

Авторы

Даты

1981-08-30—Публикация

1979-10-02—Подача