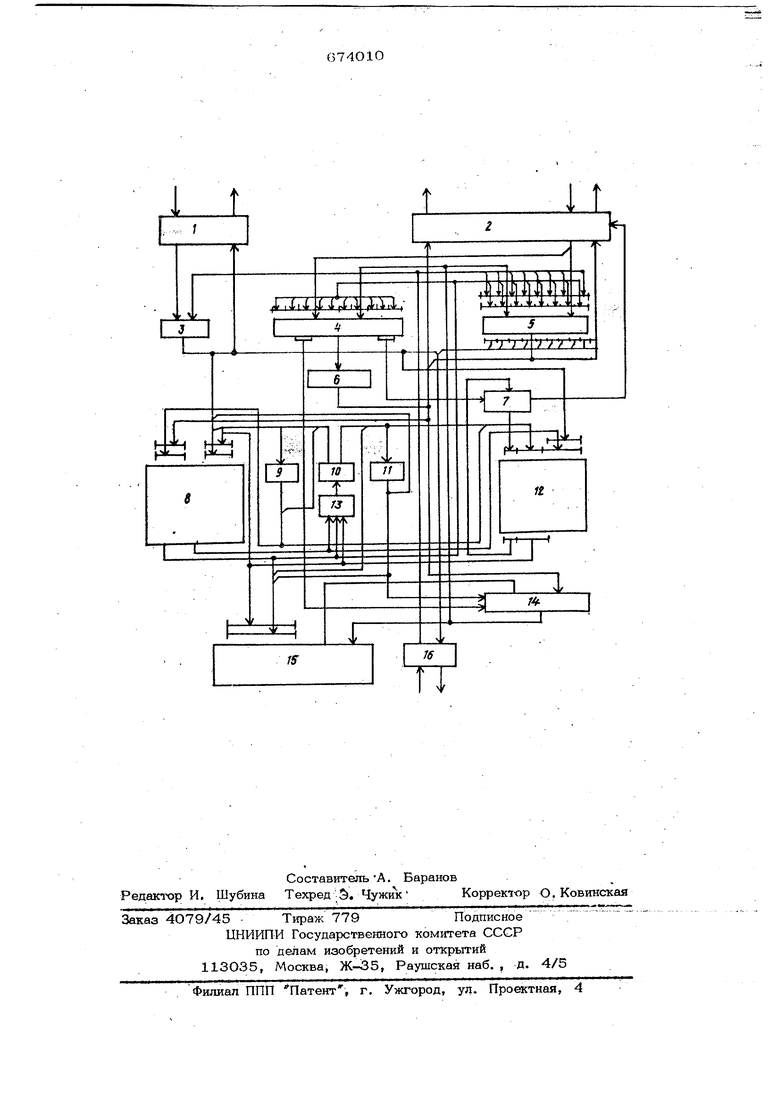

непереданных байтов подключены соответ ственно к третьему выходу регистра управления и ко второму выходу блока pe-t зервной пак1ЯтИ| первый и второй выходы блока анализа непереданных байтов подключены соответственно к четвертым входам блоков резервной памяти и сопряжения с центральной оперативной памятью, первый вход сдвигателя соединен с выходом блока основной , второй вход сдвигателя соединен с выходом блока модификации и вторым выходом регистра информации, третий вход .сдвигатвля подключен к первому выходу регистра управления, четвертый вход сдвигателя подключён к выходу регистра адреса основной памяти, выход сдвигателя соединен с входами блока основной памяти, регистра управления и регистра информашга. На чертеже йрив едена структурная . схема, мультиплексного канала с динамическим распределением памяти. Здесь приняты следующие обозначения: 1 - блок сопряжения с центральным процессором; 2 - блок сопряжения с центральной опера,тивно1й памятью; 3 - регистр подканала; 4 - регистр управления, фиксирующий ключ защить, адрес управляющего слова канала (ардес данньк), код операции, флажки, счет данных; 5 - рогистр информации; 6 - блок модификации, осуществляющий модификацию адреса программы (данных) и счета даииых ; 7 - блок анализа количестаза непереданных байтов, фиксирующий количество непереданных байтов информации, находяшсйхся под управлейием текущего управлякццего епова канала; 8 - блок адресной naivJflTH, предназначенный для хранения таблицы адресов зон основной памяти ynefiiffiieKCHoro канала и табличны занятости (неисправности) этих зон; 9 - пр&обраэЬвйтвль КбДа адреса, осуществляющий преобразование значений младших разрйИовадфеса ИЗ параллельного в позяциршлый код; Ю - рет«истр свободной зоны основной памяти;,11 - регистр адреса основной памяти 12 - блок резервной памяти, состоящий из ассоциативной и информационной частей. Ассоциа тЖная ч(йть 1фед1шзначена для хранения номеров (адресов) внешних устройств, а инфорШцйойная чисть - для хранения алpedoB зон основной (или адресной) пам0ти. Каждой строке в ассоциативной части схютветствуёт строка в инфо1рмационной части резервной памяти. Кроме того, од нобитовая область блока резервной памяти отведста для хранения признака наличия предвыб1эанного- слова; 4.5 - блок определения адреса свободной зоны основной памяти; 14 - сдвигатель, .обеспечивающий сдвиг информации влево и впр.аво; 15 - блок основной памяти; 1 б - ёлок сопряжения с внешними устройствами. Инструкция} состоит из 32 разрядов О-31 (разряды 0-7 - код конструкции, разряды 1б-18-адрес канала, разряды 24 31-адрес внещнего устройства). Адресное слово канала содержит 32 разряда 0-31 (разряды О-З-ключ защиты, разряды ,8-31-адрес управляющ&го слова канала). Управляющее слово канала состоит из 64 разрядов 0-64 (разряды О-7-код операции, разряды 8-31-адрес данньпс, разряды 32-3 6-флажки, разряды 47-63- счет даннь1х); При Поступлении от процессора в канал инструкции Начать ввод-вывод блок 1 сопряжения с центральным процессором выдает признай инструкции и код номера внешнего устройства для фиксации на регистре 3 подканала. Через блок 2 conpsiжения с центральной оперативной памятью производится тфием в канал адресного слова КйИ1ала и по нему - управляющего слова канала с фиксацией.управляющей информации подканала на регистре 4 управления. Модификация адресов центральной оперативной памяти осуществляется блоком 6 модификации. Для промежуточного хранения управляющей информации подканала в блоке 15 основной памяти отводится зона. Адрес этой зоны хранится в блоке 8 адресной памяти. Поиск свободной зоны ведется блоком 13 определения адреса свободшй зоны основной памяти с использованием преобразователя 9 кода адреса и регисг ров 1О и 11., Для плотногч) заполнения основной памяти зона области управляющей информации разделяется на подзоны i-fo и 2-гч типов. Подзоны 1-го типа образуют область основной памяти, предназначенную для хранения восьми байтовьис слов а подзоны 2-го типа - четырех байтовых слов управлйющей информации. Адрес под зоны ii4:x) типа формируются блоком 13 определевкя адреса свободной зовы основной памяти из признака типа подзоны (нулевой разрвд адресйХг едреса зоны (разрядь 1-7), адреса первого байта в зоне (разряды 8-1О) и трансформируются в адрес подзоны 2-го типа путем сдвига вправо н а один разряд и из менения признака типа подзоны.

Управляющая информация записывается в подзону основной памяти через сдвигатепь со сдвигом на четьфе байта вправо, если адрес подзоны кратен четьфе д (нули в двух младших разрядах) и без сдвига, если адрес кратен восьми (нули в трех младших {разрядах). Область данных делится на левую и правую части. Память с иириной выборки восьми байтов содержит в левой части области данных восьми групп ячеек. Первая группа ячеек предназначена для хранения восьми однобайтдвых слов, вторая - для хранения восьми двухбайтовьрс слоев и т. д. Правая часть области данных содержит группы ячеек, которые предназначены для хранения слов с количеством бай - тов, ципилняюших слова на ячеек правой части области дашшх до пошюй ширины выборки восьми байтов. Первая группа ячеек правой частя хранит восемь семибайтовых слов, вторая группа - шестибайтовых слов и т. д. Ячейка адресуется семиразрядшлм кодом. Старший разряд кода адреса определяет признак левой или правой части области данных, следующие три разряда определяют вх)пичество байтов в слове ячейки} младшие три разряда определяют комер ячейки в группе ячеек одного типа.

При вьшопнении операпии Читать канал ий интерфейса на регистр 5 информации принимает байт данных. Длина слов обмена с внешними устройствами один байт. Содержимое счетчика байтов в слове увеличивается на единицу и производится 1тоиск ячейки области данных блока 15 для записи этого байта данных.

Для промежуточного хранегшя данных, относящихся к определенному внешнему устройству, в блоке 15 выделяется .ячейка области данных с числом байтов, со ответствующим номеру npHHHMaeivioix) юга передаваемого байта данных. Например, принят второй байт данных. Совместно с первым байтом, извлеченным из одноёайтовой части памяти. Два байта эТйго подканала помещаются в одну из свободных ячеек двухбайтовой части области данных блока 15 основной памяти.

При аварийном переполнении всей об ласти основной памяти (нет свободных ячеек с числом байтов, необходимых для размещения данных, и большим) предусмотрена запись неполных слов в

центральную оперативную . .Этим исключаются потери информации в аварийных ситуациях.

При обнаружении искомой ячейки прокч водится запись принятых (непереданных) байтов данных в эту ячейку области данных блока 15 через сдвшатеяь 14, который осуществляет сдвиг содержимого регистра 5 при наличии признака в старутем разряде адреса ячейки, соответствующего размещению данных в правой части области данных блока 15,

Считьшание данных при передаче их в центральную оперативную память осущест

вляется на регистр 5 через сдвигатель

14со сдвигом на четьфе байта влево, если в старшем разряде адреса ячейки присутствует признак правой части, и без сдвига, если признак отсутствует.

При отказе блока 8 адресной памяти ее функции полиостью перекладьюаются на блок 12 резервной памяти. При отказе же отдельных ячеек зон блока 8 неисправная ячейка заменяется исправной ячейкой блока 12. В ассоциативной части резервной памяти запоминается адрес внешнего устройства (неисправной ячейки адресной памяти), а в информационной части - адрес отведенной этому внешне. му устройству зоны основной памяти.

Это свойство резервной памяти используется при ПОЛ1ЮМ отказе блока 15 основной памяти. В этом случае адресная память разб1геается на зоны с объемом, до-

статочным для хранения управляющей и передаваемой информации, размещенной в блоке 15, и используется для ее хранения, а резервная Память используется для хранения адресов зон, размеценных в адресной памяти.

При выполнении операции Писать канал читает на регистр 5 информации из центральной оперативной памяти через блок 2 слово даннь. Затем через блек 16 сопряжения с внешними устройствами внешнему устройству вьщается байт данных, сод жимое счетчика байтов в слове уменьшается на единицу и непереданные байты через сдвигатель 14 записываются в соответствующую 5гчейку области данных блока 15. Для пврепвча следукдаего байта данные считьгоаются из блока

15через сдвигатель 14 на регистр 5. После пересьшки кода-операции вкешнему ус-гройству и окончания oftvieHa служебной информацией между каналом тг внешним устройством при условии, что имеет место операции 1Писать и наличия

флажка Цепочка данных, включается блок 7 анализа непёредат&гх байтов, фиксируя количество непереданных байтов (я). При условии что п 8 в однобитовую область блока 12 резервной памяти, где хранится признак наличия предвыборного слова, подается соответствующийсигнал, Из,-.блока 7 управляющий сигнал, сигнализирующий о наличии предвыбранного словар поступает на вход блока 2, Под дейстеио этого сигнала, из центральной Ьперативной памяти п6 адресу, пришедшему из блока 6 модификаций, на ре гистр 4 управления предвыбирается но- вое управляющее слово канала (УСК). Оно записьюается в подзону основной памяти через сдвигатепь 14 со сдвигом на четьтре байта вправо, если афес noja30Hbi кратен четырем {нули в двухМладйих рядах), и без. сдвига, ебли адрес кратен восьми (нули в трех младших разрядах), При передаче последнего байта инфор. мации, находящегося под управлением текущего УСК, предвыбрашюе УСК через двигатель 14 считывается на регистр 4 со сдвигомна чбтьфе байта влево, еели адрес подзоны кратен четырем, и без Сдвнга, если адрес подзоны 7фатен восьми. Применение предлагаемого изобретения трювыщает) коэффициент использования оборудованйя канала, обеспечивает нгепрерью. ныЙ обмен информацией между машиной и внешними устройствами при работе кана-

ла в режиме Запись по цепочке данньтх а также плотное заполнение основной памяти без увеличения общего количества использу(л:ого оборудования.

Формула изобретения Мультиплексный канал с динамическим распределением памяти по авт. свид. Щ 526877, о т л и ч а го .щ и и с я тем, что, с целью повышения коэффиш ента использования оборудования, он дополнительно содфжит блок подсчета количества непереданных байтов исдвигателъ, причем два входа блока подсчета неперо данных байтов подключены соответственно к третьему выходу регистра управления и ко второму вьгходу блока резервной памяти, первый и второй блока подсчёта непереданных, байтов подключе Htj соответственно к четвертым входам блоков резервной памяти И сопр51жения с центральной ойерат ной памятью, первйй вход сдвигателя соединен с выходом , блока основной памяти, второй вход сдви-i гателя соединен, с выходом блока модификалии и Ьторым выходом регистра информашга, третий вход сдвигателя подкгаочен к первому выходу регастра управления. четвертый вход сдвигателя подключен к выходу регистра адреса основной памяти выход сдвигателя соединён с входами бло- ка основной памяти, регистра управления. и регистра информа.ции.

1 t

11

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обмена с косвенной адресацией | 1974 |

|

SU526878A1 |

| Мультиплексный канал с динамическим распределением памяти | 1973 |

|

SU526877A1 |

| Мультиплексный канал | 1976 |

|

SU590725A2 |

| Мультиплексный канал с косвенной адресацией памяти | 1973 |

|

SU514287A1 |

| Мультиплексный канал | 1974 |

|

SU525941A1 |

| Мультиплексный канал | 1973 |

|

SU525079A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Мультиплексный канал с диагностикой неисправностей | 1974 |

|

SU516033A1 |

| Мультиплексный канал | 1975 |

|

SU561955A1 |

| Мультиплексный канал многопроцессорной вычислительной системы | 1973 |

|

SU521559A1 |

Авторы

Даты

1979-07-15—Публикация

1977-03-01—Подача