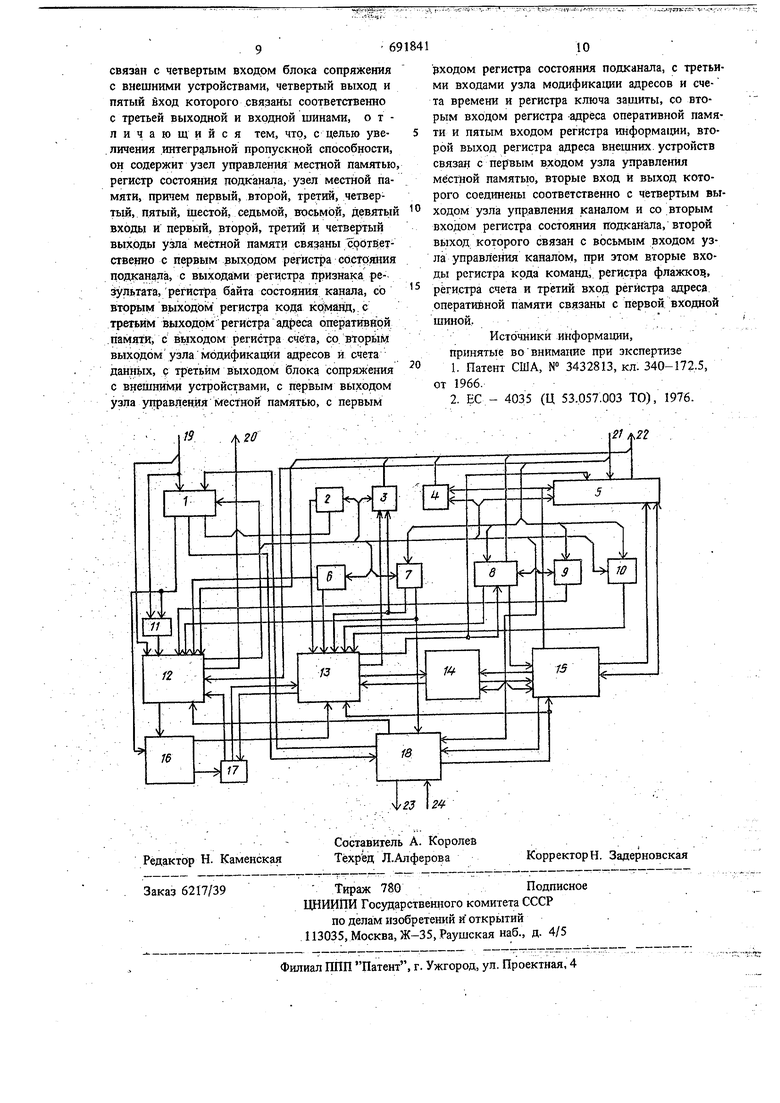

,.-. Изобретение относится к дафровым вычислительным системам. Известен мультиплексный канал 1, который содержит узел местной памяти, узел управляющих и информавдониых регистров, узел мультиплексных подканалов, узел селекторных подканалов, узел модификации управляющей информации, узел ггриорйтетов и узел управления. Мультиплексный канал может работать какв мультиплексном, так и в монопольном режимах передачи данных, в зависимости от подкМючеиного к нему устройства. В мультиплексном режиме канал одновременно способен обслуживать несколько устройств, каждое по своему подканалу. В монопольном режиме только одно устройство может передавать данные через канал. Если канал передает данные в мультиплексном режиме, средства канала выделяются для обслужнвания устройства только на время передачи сегмента информации. Сегмент может содержать один или несколько байтов, позтому такой канал можно назвать байт-мультнплексНедостатком этого устройства является низкая пропускная способность в монопольном режиме передачи данных, что не позволяет использовать канал в режиме мультиплексирования блоков, прн работе с быстродействующими устройствами. Наиболее близким по технической сущности к данному изобретению является селекторный канал 2, который содержит регистр информации, регистр маркеров, регистр ключа защиты, регистр адреса внешних устройств, регистр признака результата, регистр байта состояния канала, регистр кода команд, регистр адреса оперативной памяти, регНстр флажков, регистр счета, блок буферизации данных, узел модификации адресов и счета даННЫх, схему сравнения, блок сощ)яжения с внешними устройствами, узел управления каналом, причем первые выходы регистра информации, регистра адреса, оперативной памяти, узла управления каналом, выходь регистра маркеров, регистра ключа защиты связаны с паровой выходной шиной канала, а первые входы регистра информации и узла управления, каналом соединены с первой входной шгаюй канала, второй выход узла управления каналом связан с первыми входами регистра адреса внешних устройств, регистра клю ча защиты, регистра кода команд, регистра мар керов, регистра счета, регистра флажков, узла модификации адресов и счета даннь1х, регистра адреса оперативной. памяти, блока буферизации ддннйх блока сопряжения с внешними устройствами, со .входами регистра признака результата, регистра байта состояния канала, Со вторым входом perHctpa информации, ттри этом вторые входы регистра адреса, внёцйтих устройств, узла управления каналом и перььга вход схемы сравнения связаны ео второй вход ной шиной; канала, а третий выход узла управления каналом и первые вых:оды регистра адреса внешних устройств и регистра признака результата, связаны со второй .выходной швдгой канала, третий;вход, второй и третий выходы регистра .адреса В1гещнюс устройств, связаны .сбЬтвётственно с первым выходом блока сопря жения с внещнимиустройств.ами, со BtOpblM входом схеМы. сравн.ентга, со вторьШ входом блока .сопряжения р внешними устройствайи, выход с.хемы сравнения соединен с третьим вх домузла управления .каналом,;; четвертай, пятый,Шестой и седьмой входы которого соединены ;соОтветственно. с вь ХЬДом регистра флаж ков, первыми .вь1ходамй регистра кода команд р;егистра.. байта состодайя канала, со вторым выходом блока сопряокения с влешгжми уст-. ройствами, второй, третий, четвертый, пятьш входы и первьгй, второй, третий ичетвертый выходы блока буферизации данньхх соедшены соответственно с первымвых;ддОм узла модифШ анийадресо и счета дашьк, со вторыми вькодами регистра оперативной памяти и ре-; гистра информации, с третьим. ;выходом блока сойряжения с внешними устройствЗми, со вторьш .входом узла модификацииадресов и счеta времени, с третьими входами блока сопряжения с. Внешт йми устройствамии регистра информации,с чет.ве р1:ьтм вхЬдЬЙ/регисТра ;щформаиэяи ивторым входом регистра маркеров второй вход регистра ключа защйтьт связан со вторым выходом регистра кода команд, первы выход которЪго связан с четвертым входом блокэ согфяжеиия с внешними устройствами, четвертый выход и пятый вход которого свяsaitti соответственно с третьей выходной, и вхо ной шинами. Как п;равило, к селекторному каналу подключаются быстродействуюшйе устройства, передающне данные в монопольном режиме. Недостатками такого устройства является то что оно не позволяет мультиплексирование блоков данных; кроме того, недостаточная тфопускная способность - 1,25 мгб. Целью изобретения является обеспечение режима блокового мультиплексирования и повышение интегральной пропускной способности в канале. Это достигается тем, что предлагаемое устройство содержит узел управления .местной . памятью, регистр состояния подканала, узел Местной памяти, причем первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой . и девятый входы и первый, второй, третий и четвертый выходы узла :местной памяти связаны соответствеьшо с первым вьтходом регистра состояния подкана;ла, с выходами регистра признака результата, регистра байта состояния канала, со вторым выходом регистра кода команд, с третьим выходом регистра адреса оперативной памяти, с выходом регистра .счета, со вторым вьхходом узла модификации адрёсов и счета данньк, с третьим выходом блока сопряженияс внешними устройствами, с первым выходом узла 5Т1равле1тя Местной памятью, с первым входом регистра .состояния пОДйанала, с третьим.й входами узла модификации адресов и счета времени и регистра ключазащигь, со вторым Входомрегистра адреса оперативной памяти и пятым Входом регистра информации, при этом второй выход peifHCTpa адреса внешних устройств связан с первьгм . входом узла з равлёнм местной па.мятью, . Btopbie вход и выход которого соединены со- ответственна; с четвертымвыходом узла управления каналом и со вторым входом регистра состояния- подканала, второй вцход которого связан с Восьмьтм .входом узла управления каналом, при этом вторые в.ходь; регистра кода команд,, регистра флажков, ре-гистра счёта .и тр.етйй вход регистра адреса Оперативной памяти связаны с перовой вход.ной:шшой I . ; НаЧертежеприведена структурная схема блок-мультиплексного канала, где 1 - регистр ад,реса внешних устройств; 2 - регистр признака результата, 3 - регистр ключа защиты, 4 - регистр маркеров 5 - регистр информа1ДИИ, 6 - регистр байта состояния канала, 7 - регистр коДаКоманд, 8; - регистр адреса оперативной памяти, 9 - регистр флажков, 10 - регистр счёта, 11 -; схема сравнения, 12 - узел управления каналом, 13 - узел местной памяти, 14 - узел модификации адресов и счета дачных, 15 - блок буферизации Дшшых, 16 -узел управления местной памятью, 17 - регистр состояния подканала, 18 - блок сопряжения, с внешними устройствами, 19 - входная шина канала (связи с центральным процессором), 20 - выходная щина канала (связи с центральным процессором), 21 - входная шина канЯла (связи с управлением оперативной памятью), 22 - выходная шина канала (связи с управлением оперативно памятью), 23 - выходная шина канала (связи с внешними устройствами) 24 - входная шина канала (связи с внешними устройствами). Все команды ввода-вывода, поступающие из центрального njpoueccopa, имеют формат S, который содержит 32 разряда (0-31) (разряда 0-16 - код операций, разряды 16-31 используются для определения адреса канала и внешнего. устройства). Адресное слово Канала (АСК) содержит 32 разряда (0-31) (разряды 0-7 - ключ защиты, 8-31 - адрес первого в канальной программе правпяющего слова канала). Управляю1щее слово канала (УС содержит 64 разряда (0-63) (раз1рядь1 0-7 код команды в канале, разряды 8-31 - адрес данных или адрес УСК, если выполняется операция. в канале, или адрес адресного слова данных, если, есть косвенная адресация данных, разряды 32-37 - флажки, разрядъ 48-63 - счет данных). Адресное:слово данных (АСД)сОдерйсит 32 разряда (0-31) (pS3ряды О-7 - нули, разряды 8-31 - адрес данных). Слово состояния канала (ССК) содержит 64 разряда (0-63) (разряды 0-3 - защиты,, разряд 5 -. п1риз.нак Не вьшолнена регистрация в канале, разрядь 6, 7 - отложенньгй признак результата, разрядЬ 8-31 -- адрес УСК, разряды :32-47 - байтЬ ; состояния канала.и устройства, разрйдь 48-63 - оста;.:точнын сяе;.данных). :; ,:/. л- - : В исходном состояний кШл и всепбдканалы Находите в состоянии Доступен. . ; Реж1ш работы канала задается процессЬррй в момент приема команды процессора на инициирование канальной. программы.; ; . Канал выбирает АСК на региЬтр адреса оперативной памяти 8 и на регистр кода кс1манд 7, после чего адрес УСК и ключ защиты записыва1с тся в подканал в узле местной памяти 13, а ключ защиты в регистр ключа зйццпгы 3. Через блок сопряжения с внешни1ии устройствами 18 под управлением узла управления, каналом 12 происходит свяЗь с внец1ним устройством, адре.с которого принят из центрального процессора на регистр адреса внешних (устройств 1. Под управлением узла управления каналом. из оперативной памяти выбирается УСК.в регистр кода команд 7, регистр адреса, оперативной памяти 8, регистр флажков 9, регистр счета 10. Информация из регистра кода команд 7 передается в узел зтфавленйя каналом 12 для управления операцией и в блок сопряжения с внешними устройствами 18 для передачи кода команд во внешнее запоминающее устройство, адрес данных, или адрес АСД, если есть признак косвенной адресации данных, ИЛИ адрес следующего УСК, если выполняется команда Переход в. канале, лоступает в узел местной памяти 13, информация с регистра флажков 9 передается в узел управления каналом 12 и информация из регистра счёта Ш поступает в подканал в узел местной памяти 13. Если в УСК есть признак косвенной адресации данных, то выбирается АСД в регистр адреса оперативной памяти 8 и адрес данньгх запоминается в узел местной памяти 13. Адрес данньвс и адрес АСД записываются в область местной памяти, общую для всех подканалов, используемую для хранения адресов. Адрес, подканала в узле местной памяти 13 определяется по адресу внещ11его устройства на регистре адреса внешних устройств 1. В область подканала в узле местной памяти 13 записываются также адрес УСК начало Операций, предназначенный для процевдры повторения команды, признак цепочки команд, признак останова операции, состояние подканала, признак результат 1 из регистра признака результата 2, байт состояния канала из регистра байта Состояния канала 6 и байт состояния устройства из блока сопряжения с внешними устройствами 18. Если в канале во время работы был обнаружен какой-либо сбой, или после окончания канальной программы, в канале формируется сЛово состояния канала, которое записывается в оперативную память, после чего подканал для данного устройства переходит в состояние Доступен. Если, в канале 1шициирована канальная программа, информация, передаваемая через канал, проходит по основному тракту передачи давдых: регистр информации 5, блок буферизации данных 15, блок сопряжен1М с внешними устройствами 18. Причем дЛя улучшения характеристик канала блок сопряжения с внешними устройствами обеспечивает двухбайтный ускоренный иетерфейс ввода-вывода. Адреса обращения в оцеративную память и счет даьшых продвигаются с помощью узла модификации адресов и счета данных 14. Во время организации обращения в оперативную память узлом управления каналом 12, адрес обращения выбирается в регистр адреса оперативной памяти 8 из узла местной памяти 13 или формируется на самом регистре Если канал работает в режиме блокового мультитшексироваШм и устройство имеет механизм, позволяющий прерывать связь с каналом на неогран1П1енное время при переходе по цепочке кома1щ, то канал, выполняя цепочку кома1Щ, освобождается для инициирования новой канальной программы или для продолжения 76 ранее прерванной канальной программы с другим устройством. Сведения, необходимые для продолжения канальной программы, хранятся в подканале узла местной памяти 13. Продолжение канальной программы происходит по инициативе устройства. Как только устройство будет готово для продолжения канальной программы, при условии, что свободен интерфейс ввода-вывода, в канал по шине 24 связи с внешним устройством nocTynaei требование от абонента. Кангш, если он не занят .выполнением другой канальной лрограммы Или команды про цессора, устанавливает связь с устройством, выбирает из подканала адрес очередного УСК и клюя защиты на регистр ключа защиты 3 и продолжает канальную программу до следу ощей цепочки команд или до .з:авершения. : Таким образом, в связи с сзодествованием внешних устройств, способных прерывать связь с каналом на неограни 1енное время при переходе по цепочке команд; целесообразно введение режима блокового мультиплексирования, который позволяет ,с одной сторонь: .объединит операции с разделенными концами канала- и устройства в .одну цепочку команд, что снюкает нагрузкуна центральнЬщ процессор со сторо нь1 канала, с другой стороны, обеспечить при этом максимальную загрузку оборудования канала при передаче данных и,наконец, сов.мес тить во времени выполнение установочных и поисковых операций на млогих внещних устройствах, что в целом приводит к павътению производительности в.сей вышслительной сис-темы. . . - :. . Режим блоковрго мультиплексирования достигается введением доп /тнительного блок:а местной памяти, позволяющего хранить .дафор-мацию для продолжения канальной программы после прерывания по цепочке команд. Приме нение двухбайтного ускоренного интерфейса ввода-вывода позволяет увеличить пропускную способность Kaifina по передаче да.н11ых. Применение блок-мультиплексного кадала в вычислительной машине Позволит увеличить производительность по деисте мь1 канал-внещние запоминающие устройства (например магнитные диски) приблизительно в девять раз, что повы сит эффективность вычислительной системы в целом. Формула изобретения Блок-мультиплексный канал, содержащий ре гистр информации,регистр маркеров, регистр ключа защиты, регистр адреса внешних устройств, регистр признака результата, регистр байта состояния канала, регистр кода команд. регистр адреса оперативной памяти, регистр флажков, регистр счета, блок буферизации данных, узел модификации адресов и счета данных, схему сравнения, блок сопряжения с внешними устройствами, узел управления каналом, причем первые выходы регистра информации, регистра адреса оперативной памяти, узла управления каналом, выходы регистра маркеров, регистра ключа защиты связаны с первой выходной шиной канала, а первые входы регистра информации и узла управления каналом соединены с первой входной шиной канала, второй выход узла управления каналом связан с первыми входами регистра адреса внешних устройств, регистра ключа защиты, регистра кода команд, регистра маркеров, регистра счета, регистра флажков, узла модификации адресов и счета даннь1х, регистра адреса оперативнО;й памяти, блока буфериэащ-ш данных, блока сопрях ения.с внешними устройствами, со входами регистра признака результата, регистра байта состояния канала, со вторым входом регистра информации, при этОм вторьге входы регистра . адреса внешних устройств, узла управления, каналом, и первый вход схемы сравнения свя.ззнь1 со второй входной цгиной канала, а третий выход узла управления каналом и первьге выходы регистра адреса внещних устро.йств и регистра признака результата связаны со второй выходной щиной канала, третий вход, второй и третий ВЫХОДЫ регистра адреса внешних . устройств связаны соответственно с первым выходом блока сЬпряжени.я с вйешними устройствами, со BTppbiM входом схемы сравнения., со вторым входом блока сопряжения с внещ- ними устройствами, выход схемы сравнения соедшген. с третьим входом узла управления ка: налом, четвертый, пятый, шестой и седьмой входы которого соединены соответствешю .с выходом регистра флажков, первыми выходами регистра кода команд и регистра байта состояния канала, со вторым выходом блока сопряжения с внешними устройствами, второй, третий, четвертый, пятый входы и первый, второй, третий и четвертый выходы 6ifioKa буферизации Данных соединены соответственно с первым выходом узла модификации адресов и счета данных, со вторыми вьгходами регистра адреса оперативной памяти и регистра информации, с третьим выходом блока сопряжения с внешними устройствами, со вторым входом узла модификации адресов и счета времени, с третьими входами блока сопряжения с внешними устройствами и регистра информации, с четвертым входом регистра информации и вторым входом регистра маркеров, второй вход регистра ключа защиты связан со вторым выходом регистра кода команд, первый выход которого связан с четвертым входом блока сопряжения с внешними устройствами, четвертый выход и пятый вход которого связанъ соответственно с третьей выходной и входной шинами, о т личающийся тем, что, с целью уве.личения .интегр ьной пропускной способности, он содержит узел управления местной памятью регистр состояния подканала, узел местной памяти, причем первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый входы и первый, второй, третий и четвертый выходы узла местной памяти связаны Доответствещо с первым выходом регистра сОе1о;явшя подканада, с выходами регистра признака результата, регистра байта состояния канала, со вторым выходом регистра кода команд, с третьим выходом регистра адреса оперативной .памят:и, с выходом регистра счета, со. вторьщ выходом узла модификации адресов и счета данньгх, с третьим выходом блока сопряжения с внешними устройствами, с первым выходом узда зшравленйя местной памятью, с первым 6 10 рходом регистра состояния подканала, с третьими входами узла модификации адресов и счета времени и регистра ключа зашиты, со вторым входом регистра адреса оперативной памяти и пятым входом регистра информации, второй выход регистра адреса внешних, устройств связан с первым входом узла управления местной памятью, вторые вход и выход которого соединены соответственно с четвертым выходом узла управления каналом и со вторым входом регистра состояния подканала, второй выход которого связан с восьмым входом узла управления каналом, при этом вторые входы регистра кода команд, регистра флажкоч, регистра счета и третий вход регистра адреса оперативной памяти связаны с первой входной шиной, Источники информации, принятые вовнимание при экспертизе 1.Патент США, № 3432813, кл. 340-172.5, от 1966. 2.ЕС - 4035 (Ц 53,057.003 ТО), 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок-мультиплексный канал | 1979 |

|

SU833076A2 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Мультиплексный канал | 1973 |

|

SU525079A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Мультиплексный канал многопроцессорной вычислительной системы | 1973 |

|

SU521559A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Мультиплексный канал | 1979 |

|

SU860048A1 |

| Мультиплексный канал | 1980 |

|

SU938277A2 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

Авторы

Даты

1979-10-15—Публикация

1977-06-27—Подача