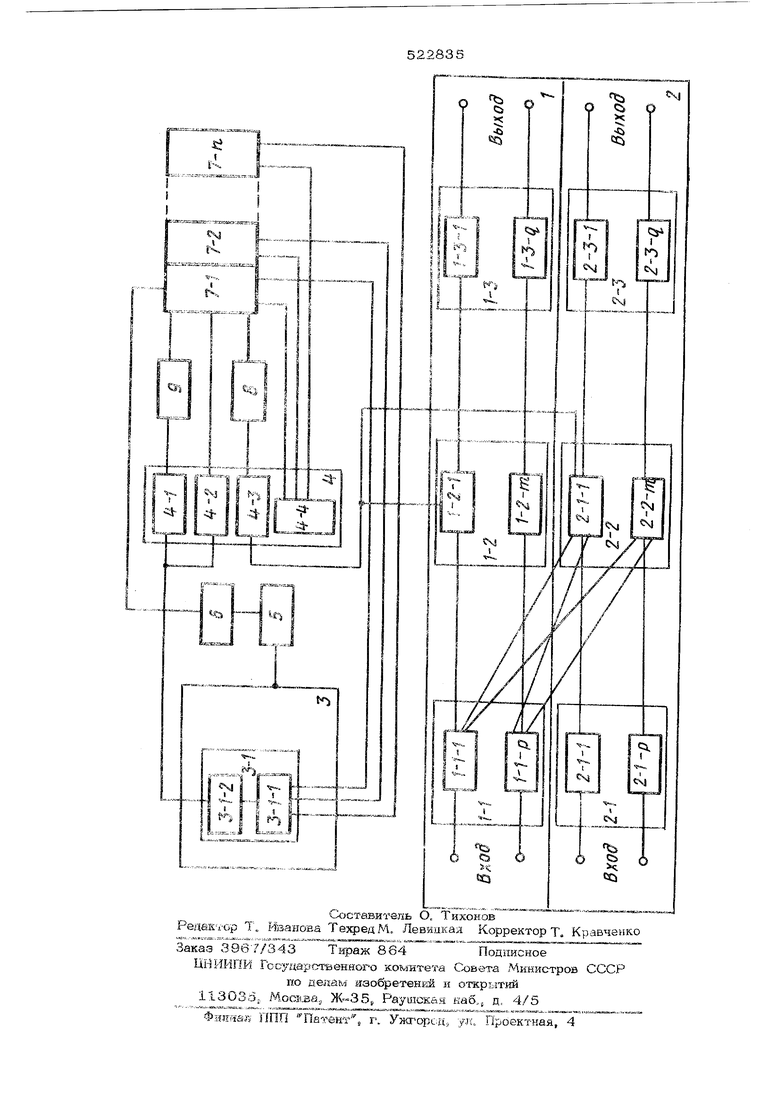

между ценгральным блоком запоминакзн занятости и блоком логических операций ре шения и управления включены последователь но цепь выбора временного канала и регист для обозначения входной или выходной ли НИИ промежуточной стзпени, а при соответствии каждого слова центральногч) блока запоминания занятости одной схеме совпаде - ния с несколькими входами все схемы совпадения содержат по пять входоВв при этом каждый из входов соединен с регистром ад реса центрального блока запоминания заня- TocTHj причем первьш вход соединен с вы - ходом двоичной ячейки для обозначения иепи коммутации, к которой принадлежит про- межуточный коммутатор; второй вход соеди нен с выходом двоично-десятичного дешифратора, соединенного с регистром адреса промежуточных коммутаторов; третий вход соединен с выходом двоично-десятичного дешифратора, соединенного с регистром адреса входных или выходных коммутаторов; четвертый вхоа соединен с выходом регистра для обозначения входящей или выходя щей линии; пятый вход соединен с выходом регистра для обозначения цепи коммутации, к которой принадлежит входной или выход - ной коммутатор. На чертеже пр1тедена блок-схема предлагаемого устройства. Устройство временной ступенчатой коммутации содержит две цепи 1 и 2 коммутации, каждая из которых состоит из последовательно соединенных входной 1-1 и 2-1, промежуточной 1-2 и 2-2 и выходной 1-3 и 2-3 ступеней, причем входная 1-1 и 2-1 ступень состоит из р входных 1-1-1, 1 - 1-р и 2-1-1, 2-1-р коммутаторов с п входящими линиями и т выходами| промежуточ ная 1-2 и 2-2 ступень - из га промежуточных 1-2-1, 1-2- m и 2-2-1, 2. коммутаторов с 2р входами и а выходами выходная 1-3, 2-3 ступень - из (J выходных 1-3-1, 1-3- (} и 2-3-1, 2-3- (J, коммутаторов с m входами и п выходными линиями; кроме того, каждый входной коммутатор 1-1-1, l-1-.p дополнительно соеди нен с промежуточными 2-2-1, 2-2™ лг комг ута7чэрами второй цепи 2 коммутации, а также блок 3 логических операгшй реше ния и управления и центральный блок 4 запоминания занятости, подключенный к обеим цепям 1,2 коммутации и выпопненньй на 2 (р-т) слов из 32 двоичных элементов, соответствующих выходным линиям входных 1-1-1, l-l-p и 2-1-1, 2-1-0 коммутаторов, и па 2 (« т) слов из 32 двоичных элементов, соответстпуюгцих выходным линиям промежуточных 1-2-1, 1-2-m и 2-2-1, 22- tn коммутатороа, при этом блок 3 яо - Гйческих операшш решений и управления содержит регистр 3-1 адре-садии выходных коммутаторов с двоичной ячейкой 3--1-1 ддя обозначения цепи коммутации, которой itpi надлежит выходной , 1-3- и .-lj 2-3- С коммутатор, причем двоичная ячейка соединена с входом одного из дополнительных регис-гров 3-1--2;, соединенно го с регистром 4-1 адреса входных и вы ходных коммутаторов центрального блока 4 запоминания занятости и с регистром для обозначения цепи коммутации,, к кото рой принадлежит промеж5;- очнь5Й 2-2-1 кии 2.2™ го коммутатор, соедикенньш с регистром 4-3 адреса яромежугочного коммутато.ра центрального блока 4 запоминания заня - тости, при этом между .центральным блоком 4 запоминания занятости и блоком 3 йогических операций решения и тиравнения включены последовательно цегш выбора 5 временного канала и регистр 6 для обозначения входной или выходной пинии промежуточной 1-2 и 2-2 ступени, а при соответстани каждого слова центрального блока -4 запоминания занятости одной сзжме /----I совпадения с несколькими входами,, все схемы 7-1,..., 7-п совпадения содержат по пять входов, при этом калсдый из входов соединен с ре гисаром адреса ценарального блока 4 запоминания загштости, причем первый вход соединен с выходом двоичной ячейки 3-1-1 для обозначения цегш коммутации, к кото «рой принадлежит промежуточный , 12- sa и 2,, :-2-ш коммутатор; вто рой вход соединен с ЕЬПЮДОМ двоично-десятичного дешифратора 8, соединенного с регистром -4-3 адреса промежуточных коммутаторов; третий вход соединен с выходом двоично-десятичного дешифратора 9, соединенного чО регистром 4 адреса входных или выходных коммутаторов; четвертый вход соединен с вьсдадом регистра 6 для обозка-чения входящей или выходящей линии; пятый вход соединен с выходом регистра 4--2 для обозначения цепи коммутации, к которой принадлежит ВХОДНСЛ 1. или выходной 1.3-1 коммутатор. Устройство работает .:ледующим образом. Блок 4 запоминания занятости получает , от центрального вычислителя выходного коммутатора 1-3-1, q, или 2-3-1., 2-3 - С номер входного комглутатора 1-1-Ij 1-1-р или 2-1-1, .рэ пос :его опре. деляется номер промежуточного коммутатора 2-2-1,, . Номер ,линии подготовки соединения определяется номером входного коммутатора 1-1-1, 1™1.,-р ипк 2-1-15 2-. -l-p,, соединяемого с промежуточным ком j-лзтатором 2- 2-.lj 2-2-- m или 1.--2-1, 1,2 ra Номер линии соединения огфеде rfflsT-cs номером выходноло ко гмутатора 1..3-1 i 1..3-. % и 2-3-а, соедиршемого с 15оо ле кугсгшь й коммутатором 1-2-1, 1.-. кли 2., 2-2-К1 ПрЕмая связь межиу номером входного ком-ълутатора 1™1.™1„ l-l.-p и номером входной дгшк,- обе;г еп;;25ается благодаря струк - туре ссед ане:аия и закону установления сзйзйй между гфомежуточными , гп В Б:хг)|:;:аь ми l-.-l.-ls жомму ато йми. Ecaui линин промежуточного soMM7i Tai opa i-2.-.l, 1™2--.га содержит свободаьш н,ремэнной кана гопологшяеуврав- ленйй. блока - в регистр адраса 4-1 за- :сясыаае ;-ся нсд-лер зыходкого коммуча1ч ра 1.3..о1,. Ь«-3-f|.i в регистр4 -1 - состояние., казью&кздее грияадлехшость номера про межуточной линии 1 иии 2, а также указывающая аа то., что вронеходит vipoBepsa лйнкк, гозок ейсуточяый ком - кутатор 1-fc-1, 1-«2. ти содер ккт свобод- нь.В1 времйнной каяад,, то яо погике блока 4 новое содер.гканае 4-™2 нередает- Си Б регистр . 4, после t -roro осу щес1вгаяет-с.я зтровзрка южааИд которая заканчяваег-ся устаноЕжой , указыважцей на rOj что временные каналы заняты. Эта one- paiiHs осуще за-вляется по логике блока 4 путем передачи номеров освобожденнык и занятых времеш ых каналов в регистр 4-2, КС-тор ьй Гт оздейожует на дешифратор 8, поз Бол. уст-акоБить информацию, закодиро ваньуш в рег-ЕСГре 4-2. Если по логике блока 4 свободньй вре манной канал на входной к выходной лини ЕХ промажуточного коммутатора 1-2-«1, та не найдеН; то блок 4 осуадествляет сдвиг регистра 4-3 который в этом случае будет содержать кояачество соо-ветствунзщее адресу промежуто етого коммутато ра 2.---2-15 . 1й:, а опйсанньй выше процесс ковтор.иется с загшсью номера линии к обоаначешлем цегш 1 или 2, Если свободный временыей канал ие най.цен промежуточ ным кст./и..;-утетором 2--2- 1; m , то по логнке плоха 4 веет-гэдгвается номер прове ряемого нромежуточного комм; грагора , 2г--2.-- ИЗ г;утем сдвига регистра до 1е-х пор,, пока регис.ф не будет содер жать чесло та ., соответствующее адресу KpoMemyTo ioro -{ют- мутатсра ... m Ее,Ш1 к 3 этом коммутатор , 2 ... . jji К-; иьлееу ;.;Bo6o.o.Hoio временного ка нала, то пойск л.ин1зи прекраилзатся а або .« нев.т по.гаучае-т сггг-нак Занятс.., В случае ва зобнб;1Пех1:-;1.5 работь5 после освсбождения пиliKS: бйож 4 йг. соса-ветству ощий жод. регистр информацию в виде адреса фомежуточного коммутатора 2--2то 5 адреса входного коммутатора 1-1-1, , адреса выходного коммутатора 1-3 I, ft с указанием цепи 1 или 2, поера освобождаемых линий временных кана ов„ Освобождение линии после стирания коов управляющих запоминающих устройств аключается в том, что в двоичных элеменах блока 4 осущес-т-вляется стирание памяти занятости, причем .цвоичнью элементы управляющих и запоминающих устройств освоО)кдаю. без вмешатчгльства блока 3 по - гических операций решения и угфавления. р е т е н и я о р м у л а Устройство временной ступенчатой коы му-гации,, содер: гаш.ее две депл коммугацин, каждая из когорых из последовательно соединенных входной промежуточной и выходной сгупеией, причем выходная ступень сосгоит из р входных коммутаторов с TL входяш,ими линиями и in выходами; промежуточная ступень-из ci щ)омежуточных коммутаторов с 2р входами и выходами; выходная ступень-из О. выходных коммутаторов с Я1 входами и п выходньт1и линиями, кроме TorOj каждый входной коммутатор дополнительно соединен с промежуточными коммутаторами в-торой цегш коммутации а также блок лог.ических операций решения и управления и пенаральный блок запоминания занятости; отличающееся тем, что., с целью ускорения процесса определения свободного пути между одним входом и каким-либо выходом системы, цен тральный блок запоминания занятости подключен к обеим цепям коммуташп и выполнен на 2 (р-пг) слов из 32 двоичных элементов; соответствующих выходным линиях; входных коммутаторов, и на 2(4 -т.) слов из 32 элементов, соответствую щих выходньп, линиям промежуточных ком- мутаторов три этом бг;ок логичес:ккх oneра1шй решения и управления содержит ре -гистр а.дресации выходньт коммутаторов с двоичной ячейкой для обозначения цеш; ком- муташ-ш, которой принадлежит вык.одной коммутатор, причем двоичная ячейка соедипе на с входом одного из дополнительных рр- г-истроп, соединенного с регистром адреса входных и выходных коммутаторов центрального блока запоминания занятости и с регистром для обозначения цешг коммутаци, к которой принадлежит проме)-уточный ыутатор, соединенный с регнсгром адреса

щ)омежуточного коммутаа-ора центрального блока запоминания занятости, щ)и этом между центральным блоком запоминания занятости и блоком логических операций решения управления включены последовательно цепь выбора временного канала и регистр для обозна« чення входной или выходной линии 11ромежу точной ступени, а при соответствии каждого

слова центрального блока запоминания заJ.

нятости одной схеме совпадения с несколь

кими входами, все схемы совпадения содержат по пять входов, при этом каждый из

входов соединен с регистром адреса цен - трального блока запоминания занятости,

щзичем первый вход соединен с выхсйом двоичной ячейки шш обоэначе-щш цепи коммутациИа к которой гфшшднежат гфомежу -точный коммутатору второй вход соединен с выходом двоично десятичного дешифратора S соединенного с регистром адреса промежуточных коммутаторов третий вход соединен с выходом двоично-десятичного деши(| атора5 соединенного с регистром адрэсй вжодных или выходных коммутаторов четвертый вхоя соединен с выходом регистра аля обоана-ченйг входящей линии ил к выходящей ляннв пятый вход соединен с выходом регистра для ойозначения цепи коммутадан, к которой прЕнад-лежит входной или выходкой коммутатор,.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки линии | 1970 |

|

SU485611A3 |

| Устройство для коммутации сообщений | 1988 |

|

SU1529235A1 |

| Автоматизированная система контроля параметров электронных схем | 1981 |

|

SU1010602A1 |

| Многоканальное измерительно-регистрирующее устройство (его варианты) | 1982 |

|

SU1038807A1 |

| Модульная многоуровневая система коммутации процессоров | 1984 |

|

SU1249524A1 |

| СИСТЕМА ВРЕМЕННОГО ЗАПОМИНАНИЯ ИНФОРМАЦИИ | 1991 |

|

RU2138845C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| Дискретное измерительное устройство ДИУ-256/1 с цифровым выходом | 1959 |

|

SU124650A1 |

| СПОСОБ ПРОСТРАНСТВЕННО-ВРЕМЕННОЙ КОММУТАЦИИ | 2011 |

|

RU2458383C1 |

| Неблокирующая система связи,например телефонной | 1970 |

|

SU510179A3 |

Авторы

Даты

1976-07-25—Публикация

1971-02-10—Подача