Изобретение относится к вычислительной технике и может найти применение при создании надежных и высокопроизводительных многопроцессорных вычислительных систем.

Целью изобретения является повышение производительности за счет увеличения пропускной способности при уменьшении временных затрат на управление межпроцессорными взаимодействиями.

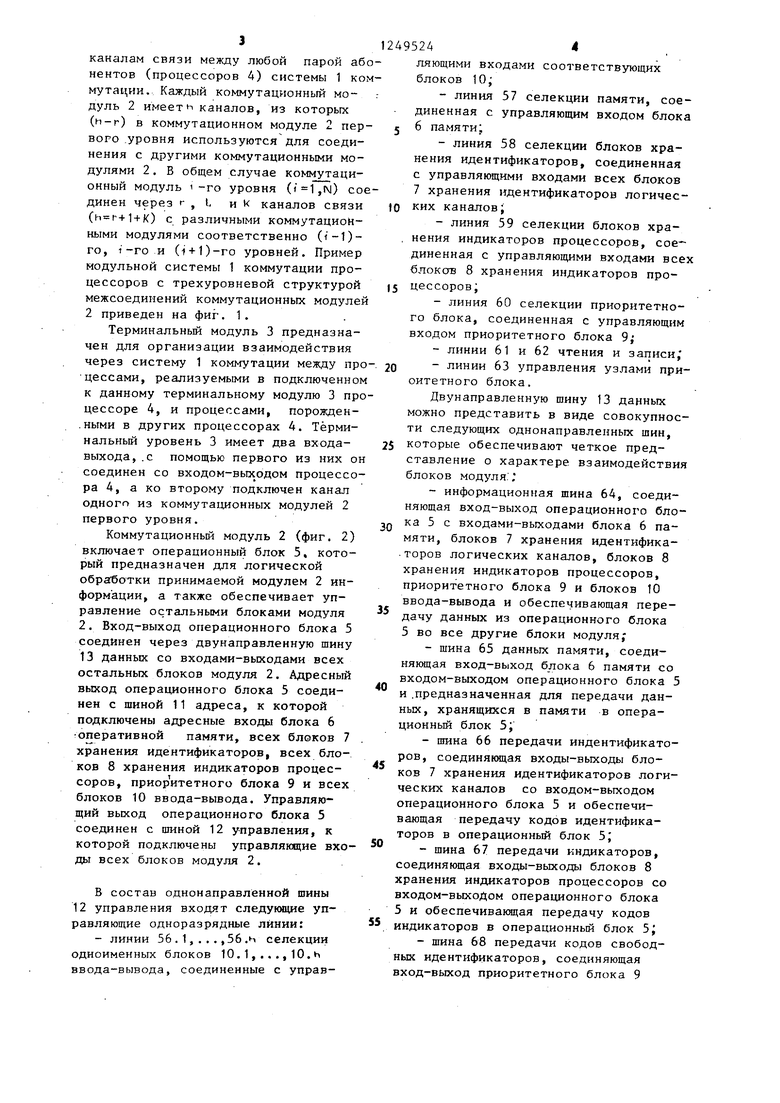

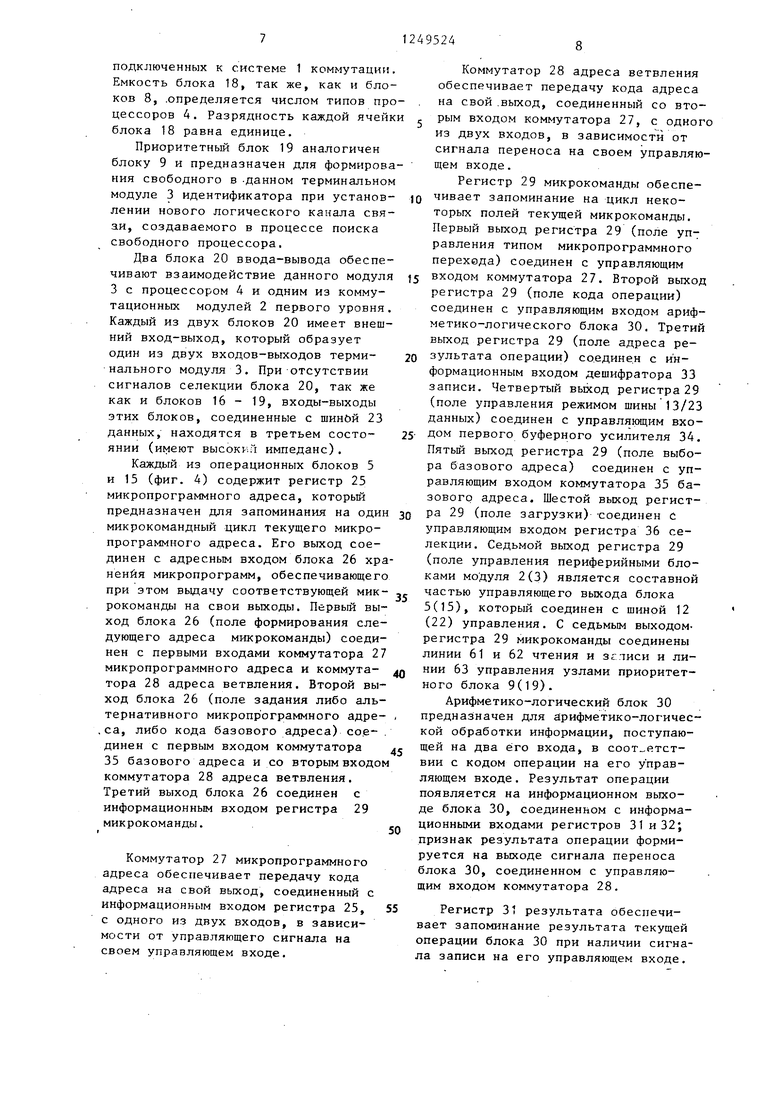

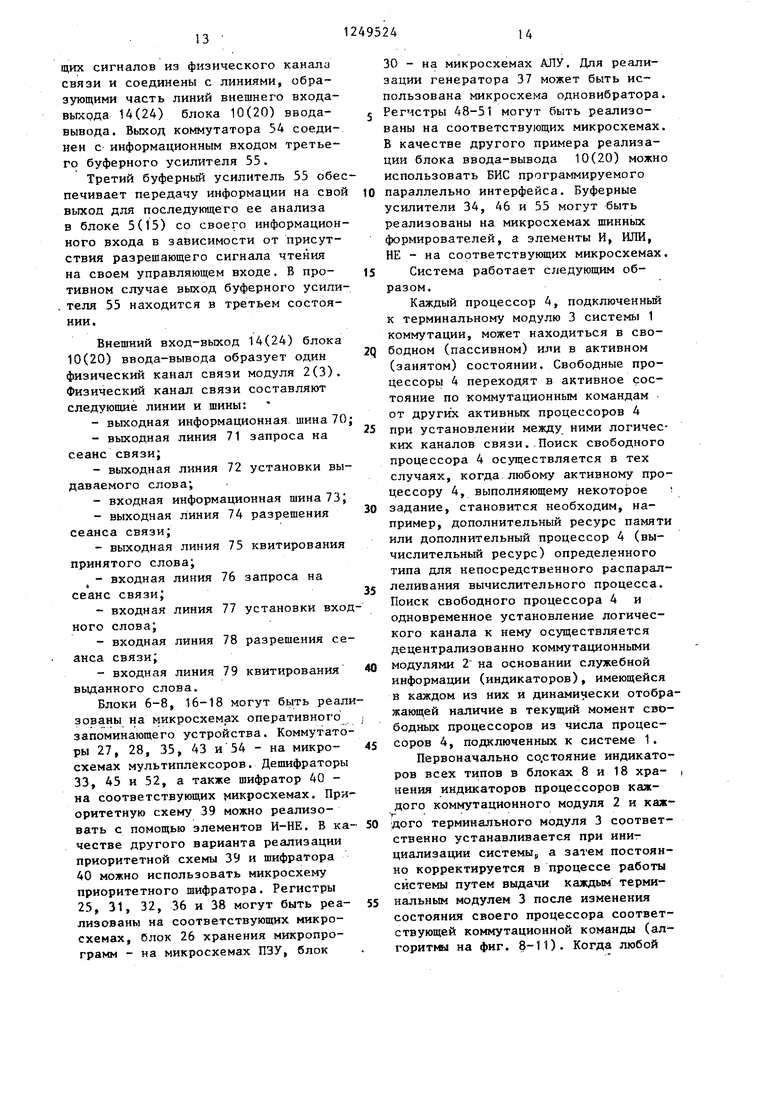

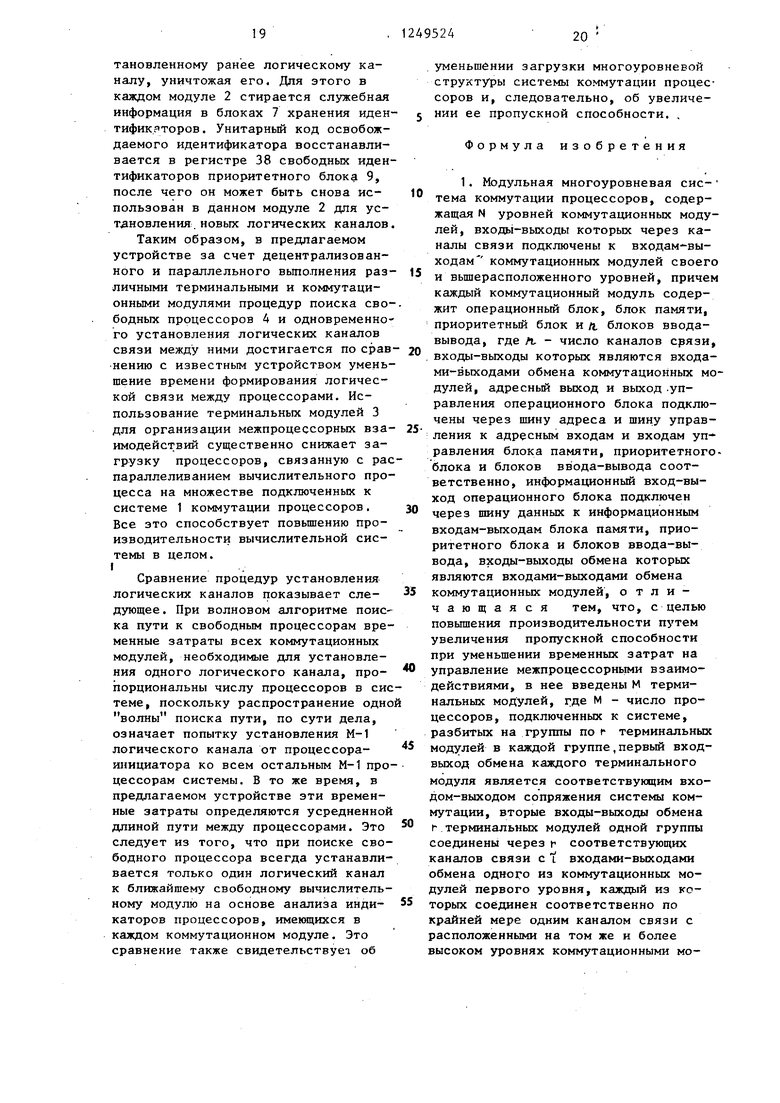

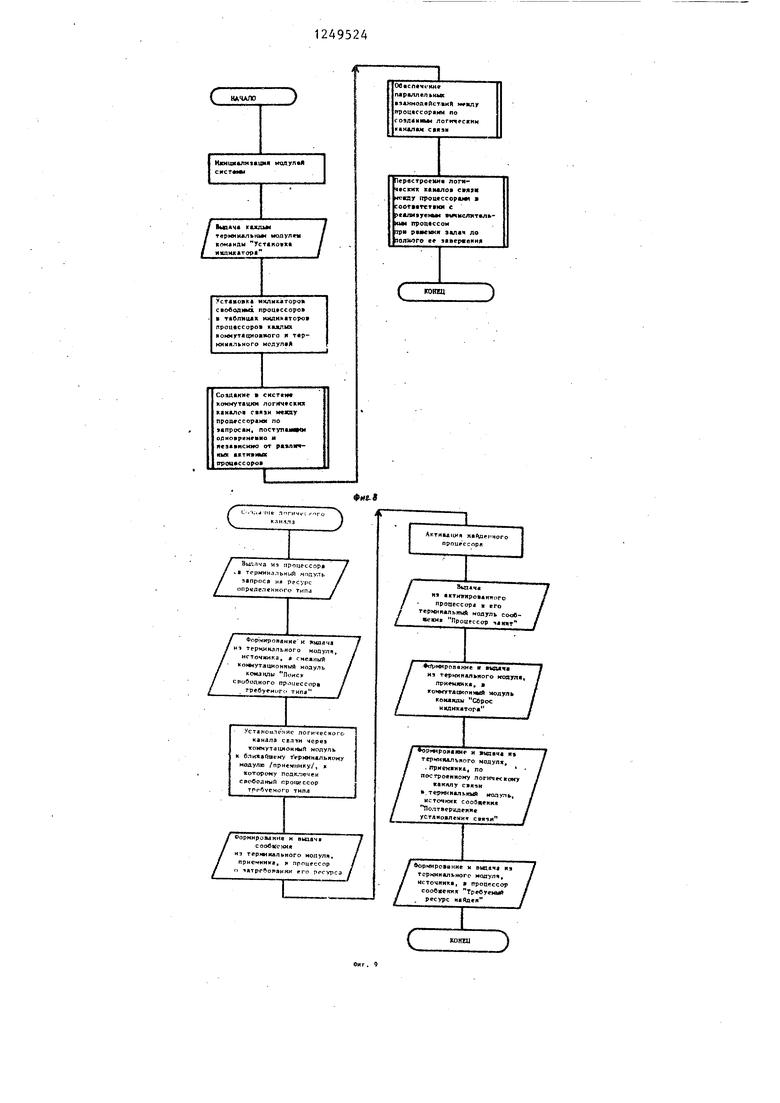

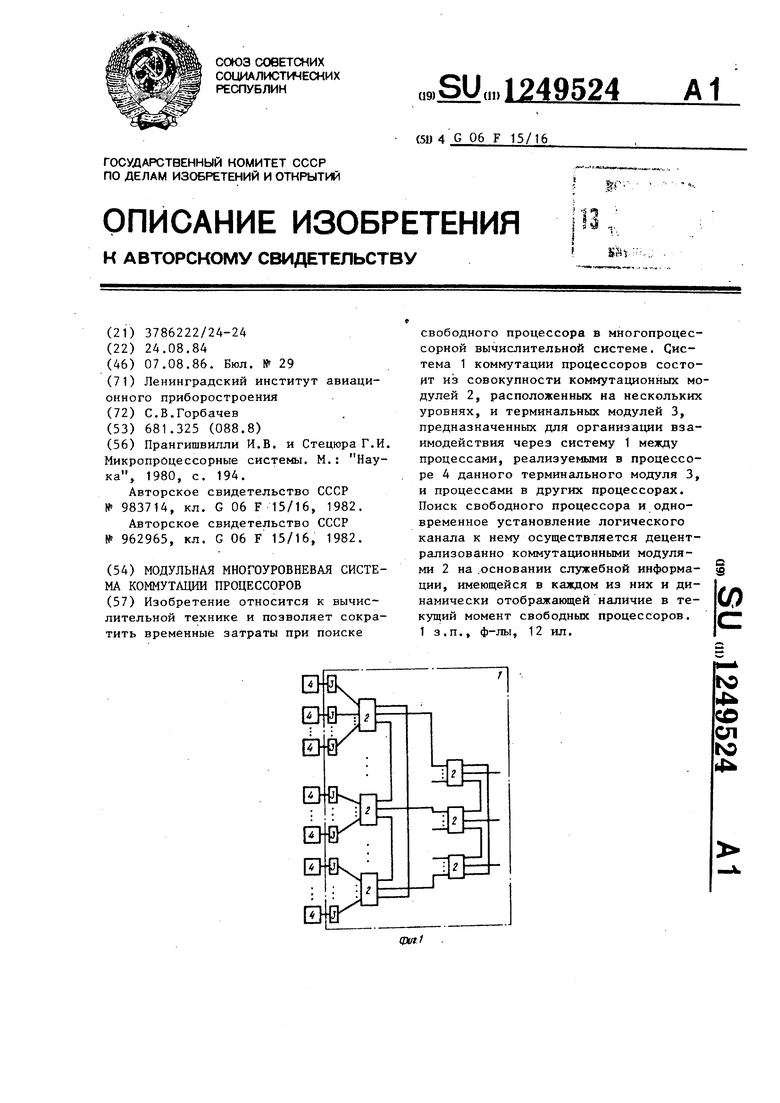

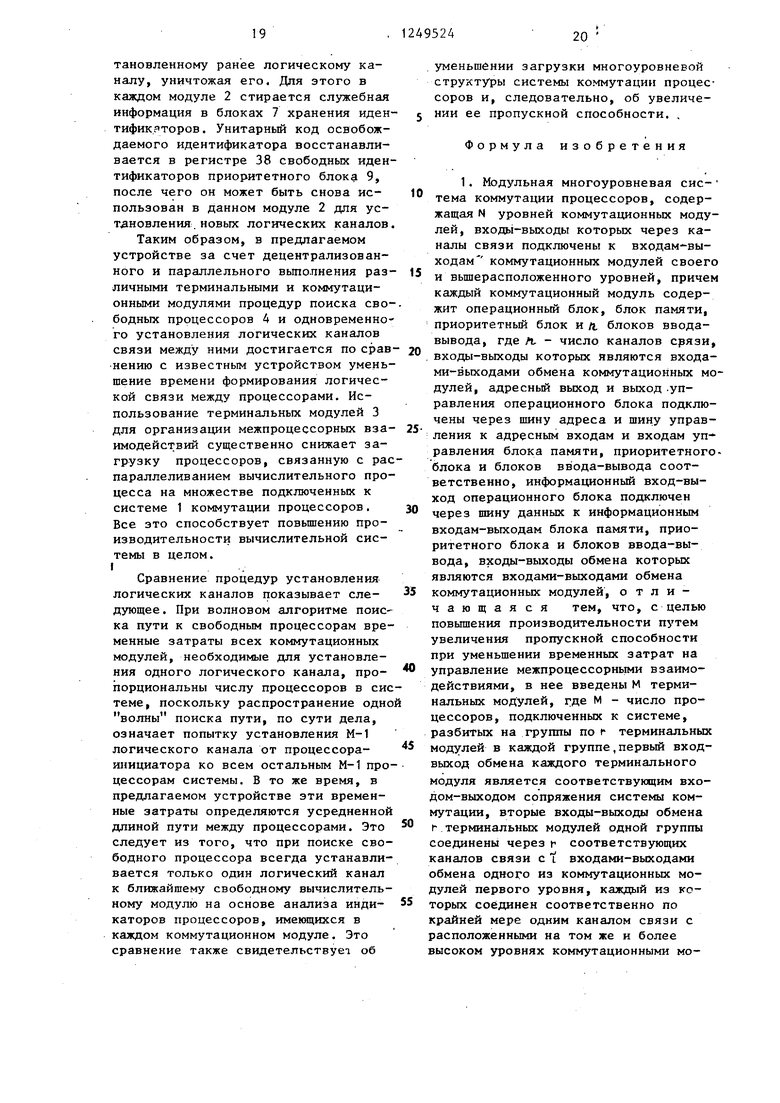

На фиг. 1 приведен пример структурной схемы модульной многоуровневой системы коммутации процессоров; на фиг. 2 - структурная схема коммутационного модуля, на фиг. 3 - струк турная схема терминального модуля; на фиг. 4 - пример реализации функциональной схемы опер;ационного блока модулей; на фиг, 5 - пример реализации структурной схемы приоритетного блока; на фиг. 6 - пример реализации блока ввода-вывода модулей на фиг. 7 - временные диаграммы работы операционного блока; на фиг.8- 12 -алгоритмы функционирования системы коммутации процессоров.

Система 1 коммутации процессоров содержит коммутационные модули 2, терминальные модули 3,- процессоры 4 (фиг. 1).

Коммутационный модуль содержит операционный блок 5, блок 6 памяти, блоки 7.1,...,7.h хранения идентификаторов логических каналов, блоки 8.1,...,8.h хранения индикаторов процессоров, приоритетный блок 9, блоки 10.1,...,10.h ввода-вьшода, шину 11 адреса, шину 12 управления, шину 13 данных, каналы 14.1,..,,14.h связи (фиг. 2). .

Терминальный модуль 3 содержит операционный блок 15, блок 16 памяти, блок 17 хранения идентификаторов логических каналов, блок 18 хранения индикаторов процессоров, приоритетный блок 19, два блока 20.1, и 20.2 ввода-вывода, шину 21 адреса, шину 22 управления, шину 23 данных, входы-выходы 24.1 и 24.2 терминального модуля 3 (фиг. 3).

Операционный блок 5(15) содержит регистр 25 микропрограммного адреса, блок 26 хранения микропрограмм,коммутатор 27 микропрограммного адреса, коммутатор 28 адреса ветвления, регистр 29 микрокоманды, арифметико- логический блок 30, регистр 31 ре20

25

49524 2

эультата, регистр 32 адреса, дешифратор 33 записи, коммутатор 34 данных, коммутатор 35 базового адреса, регистр 36 селекции, генератор 37 5 синхроимпульсов (фиг. 4),

Приоритетный блок 9(19) содержит регистр 38 свободных идентификаторов, приоритетную 39 схему, шифратор 40 индентификатора логического 0 канала, группу 41 элементов НЕ, первую группу 42 элементов И, коммутатор 43 идентификаторов, группу 44 элементов ИЛИ, дешифратор 45 идентификатора, второй буферный усили- 15 тель 46, вторую группу 47 элементов И (фиг. 5).

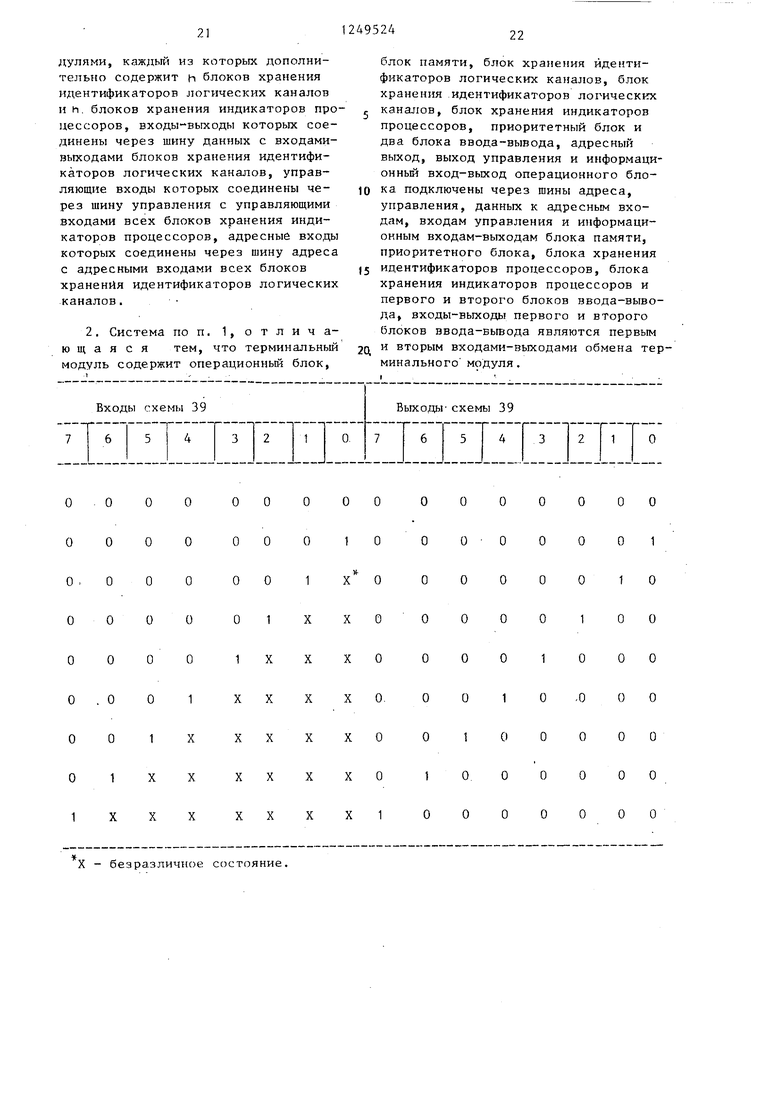

Блок 10(20) ввода-вывода содержит выходной регистр 48, входной регистр 49, регистр 50 управления вьщачей, регистр 51 управления приемом, дешифратор 52 адреса, третью группу 53 элементов И, коммутатор 54 входной информации, третий буферный усилитель 55 (фиг. 6),

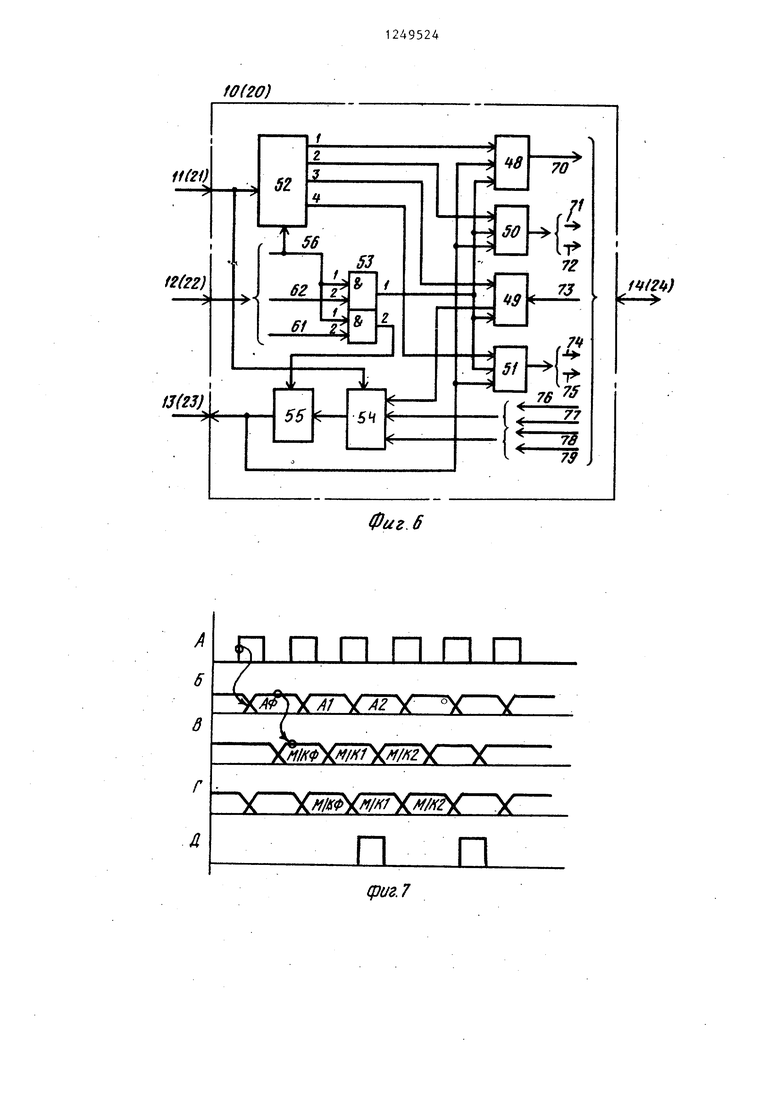

На фиг. 7 А - диаграмма на выходе генератора 37 синхроимпульсов; Б - диаграмма на выходе регистра 25 микропрограммного адреса; В - диаграмма на выходе блока 26 хранения микропрограмм; Г - диаграмма на выходе регистра 29 микрокоманды; Д - диаграмма на выходе дешифратора 33 записи.

Модульная многоуровневая система

1коммутации может обеспечивать взаимодействие произвольного числа М процессоров 4, разделенных на группы по f- процессоров в каждой группе. Отдельный процессор 4 предназначен для выполнения различных операций, необходимых для реализации вычислительного процесса в многопроцессорной вычислительной системе, и может представлять собой универсальную электронную вычислительную машину (микро-ЭВМ). Каждая группа из г процессоров через соответствующие терминальные модули 3 соединена с соответствующим коммутационным модулем

2через f каналов связи. Все коммутационные модули 2 соединены между собой таким образом, что образуют М-уровневую структуру межсоединений.

Коммутационные модули 2 обеспечивают поиск свободных процессоров 4 в системеJ установление логических каналов связи между процессорами 4 и передачу информации по логическим

30

35

40

45

50

55

каналам связи между любой парой абонентов (процессоров 4) системы 1 коммутации. Каждый коммутационный модуль 2 имеетh каналов, из которых (и-г) в коммутационном модуле 2 первого .уровня используются для соединения с другими коммутационными модулями 2. В общем случае коммутационный модуль 1-го уровня (,N) соединен через f , L и k каналов связи (ь г-ь1н-(() с различными коммутационными модулями соответственно (-1)- го, 1-го и (i+1)-ro уровней. Пример модульной системы 1 коммутации процессоров с трехуровневой структурой межсоединений коммутационных модулей 2 приведен на фиг. 1.

Терминальньй модуль 3 предназначен для организации взаимодействия через систему 1 коммутации между про цессами, реализуемьп и в подключенном к данному терминальному модулю 3 процессоре 4, и процессами, порожден- .ными в других процессорах 4. Терминальный уровень 3 имеет два входа- выхода, .с помощью первого из них он соединен со входом-вых одом процессора 4, а ко второму подключен канал одного из коммутационных модулей 2 первого уровня.

Коммутационньм модуль 2 (фиг, 2) включает операционный блок 5, который предназначен для логической обработки принимаемой модулем 2 информации, а также обеспечивает управление остальными блоками модуля 2. Вход-выход операционного блока 5 соединен через двунаправленную шину 13 данных со входами-выходами всех остальных блоков модуля 2. Адресный выход операционного блока 5 соединен с шиной 11 адреса, к которой подключены адресные входы блока 6 оперативной памяти, всех блоков 7 хранения идентификаторов, всех блоков 8 хранения индикаторов процессоров, приор итетного блока 9 и всех блоков 10 ввода-вывода. Управляющий выход операционного блока 5 соединен с шиной 12 управления, к которой подключены управляющие входы всех блоков модуля 2.

В состав однонаправленной шины 12 управления входят следукмцие управляющие одноразрядные линии:

- линии 56. 1, .. .,56.1 селекции одноименных блоков 10.1,...,10.h ввода-вывода, соединенные с управ495244

ляющими входами соответствующих блоков 10j

-линия 57 селекции памяти, соединенная с управляющим входом блока

5 6 памяти;

-линия 58 селекции блоков хранения идентификаторов, соединенная с управляющими входами всех блоков

7 хранения идентификаторов логичес- fO ких каналов;

-линия 59 селекции блоков хра, нения индикаторов процессоров, соединенная с управляющими входами всех блоков 8 хранения индикаторов про- (5 цессоров;

-линия 60 селекции приоритетного блока, соединенная с управляющим входом приоритетного блока 9;

-линии 61 и 62 чтения и записи, 20 линии 63 управления узлами приоитетного блока.

Двунаправленную шину 13 данных можно представить в виде совокупности следующих однонаправленных шин, 25 которые обеспечивают четкое представление о характере взаимодействия блоков модуля:;

-информационная шина 64, соединяющая вход-выход операционного бло,Q ка 5 с входами-выходами блока 6 памяти, блоков 7 хранения идентифика- . торов логических каналов, блоков 8 хранения индикаторов процессоров, приоритетного блока 9 и блоков 10 ввода-вывода и обеспечивающая передачу данных из операционного блока 5 во все другие блоки модуля;

-шина 65 данных памяти, соеди- някяцая вход-выход блока 6 памяти со входом-выходом операционного блока 5 и .предназначенная для передачи данных, хранящихся в памяти в операционный блок 5;

-шина 66 передачи индентификато- ров, соединяющая входы-выходы блоков 7 хранения идентификаторов логических каналов со входом-выходом операционного блока 5 и обеспечивающая передачу кодов идентификаторов в операционный блок 5;

5

0

5

- шина 67 передачи индикаторов.

соединяющая входы-выходы блоков 8 хранения индикаторов процессоров со входом-выходом операционного блока 5 и обеспечиваклцая передачу кодов индикаторов в операционный блок 5;

- шина 68 передачи кодов свободных идентификаторов, соединяющая вход-выход приоритетного блока 9

со входом-выходом операционного бло ка 5 и обеспечивающая передачу двоичных кодов вьщеленных.идентификаторов в операционный блок 5;

- шина 69 передачи входной информации, соединяющая входы-вьщоды блоков 10 ввода-вывода со входом-выходом операционного блока 5 и обеспечивающая передачу в оперг ционный блок 5 входной информации, полученной блоком 10 извне.

Блок 6 памяти обеспечивает хранение программ и данных, в том числе и буферируемьк данных, принятых из- вне. Блоки 7 хранения идентификаторов обеспечивают запоминание идентификаторов, которые используются при передаче по установленным ранее ло ги- ческим каналам связи через данный модуль 2 информации между парами взаимосвязанных таким образом терминальных модулей. Число блоков 7 соответствует числу физических кана- лов данного коммутационного модуля 7. Емкость каждого из блоков 7 определяется числом логических каналов связи, которые можно установить через данный модуль 2.

Блоки 8 хранения индикаторов процессоров используются для хранения служебной информации, обеспечивающей поиск свободных процессоров 4 различных типов, подключенных к систе- ме 1 коммутации, по соответствующему физическому каналу связ и. Емкость блока.8 определяется числом типов процессоров 4. Разрядность каждой ячейки каждого блока 8 равна едини- це. Число блоков .8 равно h .

Приоритетный блок 9 предназначен для вьщеления свободного в данном коммутационном модуле 2 идентификатора при установлении нового логи- ческого канала связи, создаваемого в процессе поиска свободного процессора, t

Блоки 10 ввода-вывода обеспечивают взаимодействие данного модуля 2 с другими модулями 2 и 3. Каждый из блоков 10 имеет внешний вход-выход, который образует один физический канал связи коммутационного модуля 2. При отсутствии сигналов селекции блока 10, так же, как и блоков 6-9, входы-выходы этих блоков, соединенные с шиной 13 данных, находятся в

третьем состоянии (имеют высокий им педанс).

Терминальный модуль 3 (фиг. 3) включает операционный блок 15, который аналогичен блоку 5 и предназначен для логической обработки принимаемой модулем 3 информации, а также обеспечивает управление остальными блоками модуля 3. Вход-выход операционного блока 15 соединен через шину. 23 данных со входами-выходами всех остальных блоков модуля 3. Адресный выход операционного блока 15 соединен с шиной 21 адреса, к которой подключены адресные входы блока 16 памяти, блока 17 хранения идентификаторов, бдока 18 хранения индикаторов процессоров, приоритетного блока 19 и двух блоков 20 ввода-вывода. Управляющий выход операционного блока 15 соединен с шиной 22 управления, к которой подключены управляющие входы всех блоков модуля 3 В состав шины 22 управления входят управляющие линии, аналогичные перечисленным для шины 12 управления. Двунаправленная шина 23 данных также может быть представлена в виде совокупности однонаправленных шин, анало гичнбпс перечисленным для шины 13 данных.

Блок 16 памяти, который аналогичен блоку 6, обеспечивает хранение программ, а также данных, в том числе и буферируемьк данных, принятых извне.

Блок 17 хранения идентификаторов обеспечивает запоминание имен процессоров, активизированных в подключенном к данному модулю 3 процессоре и взаимодействующих с процессами в других процессорах 4, и идентификаторов занятых логических каналов связи, которые используются при передаче по установленным ранее логическим каналам связи через данный модуль 3 информации к взаимосвязанным с данным модулем 3 другим терминальным модулем 3. Емкость блока 17 определяется числом логических каналов связи, которые можно установить через данный модуль 3.

Блок 1В хранения индикаторов процессоров аналогичен блоку 8.i и используется для хранения служебной информации, обеспечивающей поиск свободных процессоров 4 различных типов

подключенных к системе 1 коммутации. Емкость блока 18, так же, как и блоков 8, .определяется числом типов процессоров 4. Разрядность каждой ячейк блока 18 равна единице.

Приоритетный блок 19 аналогичен блоку 9 и предназначен для формирования свободного в -данном терминальном модуле 3 идентификатора при установлении нового логического канала связи, создаваемого в процессе поиска свободного процессора.

Два блока 20 ввода-вывода обеспечивают взаимодействие данного модуля 3 с процессором 4 и одним из коммутационных модулей 2 первого уровня. Каждый из двух блоков 20 имеет внешний вход-выход, который образует один из двух входов-выходов терминального модуля 3. При отсутствии сигналов селекции блока 20, так же как и блоков 16 - 19, входы-выходы этих блоков, соединенные с шинбй 23 данных, находятся в третьем состоянии (имеют ВЫСОКИ; : импеданс) .

Каждый из операционных блоков 5 и 15 (фиг. 4) содержит регистр 25 микропрограммного адреса, который предназначен для запоминания на один микрокомандный цикл текущего микропрограммного адреса. Его выход соединен с адресным входом блока 26 хранения микропрограмм, обеспечивающего при этом вьщачу соответствующей мик- рокоманды на свои выходы. Первый выход блока 26 (поле формирования следующего адреса микрокоманды) соединен с первыми входами коммутатора 27 микропрограммного адреса и коммута- тора 28 адреса ветвления. Второй выход блока 26 (поле задания либо альтернативного микропрограммного адре- . са, либо кода базового адреса) со.е- . динен с первым входом коммутатора 35 базового адреса и со вторым входом коммутатора 28 адреса ветвления. Третий выход блока 26 соединен с информационным входом регистра 29 микрокоманды.

Коммутатор 27 микропрограммного адреса обеспечивает передачу кода адреса на свой выход, соединенный с информационным входом регистра 25, с одного из двух входов, в зависимости от управляющего сигнала на своем управляющем входе.

20

25

,, , j

Коммутатор 28 адреса ветвления обеспечивает передачу кода адреса на свой .выход, соединенный со вто- g рым входом коммутатора 27, с одного из двух входов, в зависимости от сигнала переноса на своем управляющем входе.

Регистр 29 микрокоманды обеспе- JQ чивает запоминание на цикл некоторых полей текущей микрокоманды. Первый выход регистра 29 (поле управления типом микропрограммного перехеда) соединен с управляющим J5 входом коммутатора 27. Второй выход регистра 29 (поле кода операции) соединен с управляющим входом арифметико-логического блока 30. Третий выход регистра 29 (поле адреса результата операции) со.единен с информационным входом дешифратора 33 записи. Четвертый выход регистра 29 (поле управления режимом шины 13/23 данных) соединен с управляющим входом первого буферного усилителя 34. Пятьй выход регистра 29 (поле выбора базового адреса) соединен с управляющим входом коммутатора 35 базового адреса. Шестой выход регистра 29 (поле загрузки) -соединен с управляющим входом регистра 36 селекции. Седьмой выход регистра 29 (поле управления периферийными блоками модуля 2(3) является составной частью управляющего выхода блока 5(15), который соединен с шиной 12 (22) управления. С седьмым выходом- ре гистра 29 микрокоманды соединены линии 61 и 62 чтения и зглиси и линии 63 управления узлами приоритетного блока 9(19).

Арифметико-логический блок 30 предназначен для арифметико-логической обработки информации, поступающей на два его входа, в соот...,етст- вии с кодом операции на его управляющем входе. Результат операции появляется на информационном выходе блока 30, соединенном с информа- ционньми входами регистров 31 и 32; признак результата операции формируется на выходе сигнала переноса блока 30, соединенном с управляющим входом коммутатора 28.

5 Регистр 31 результата обеспечивает запоминание результата текущей операции блока 30 при наличии сигнала записи на его управляющем входе.

30

0

Выход регистра 31 соединен с первым входом блока 30 и информационным входом первого буферного усилителя 34.

Регистр 32 адреса обеспечивает запоминание результата текущей операции блока 30 при наличии сигнала записи на его управляющем входе. Выход регистра 32 является адресным выходом операционного блока 5(15), который соединен с щиной 11(21) адреса. .

Дещифратор 33 записи обеспечивает формирование на одном из своих выходов сигнала записи в зависимости от двоичного кода на информационном входе при наличии синхросигнала на управляющем входе. Первый выход дешифратора 33 соединен с управляющим входом регистра 31, а второй выход- с управляющим входом регистра 32.

Первый буферный усилитель 34 обеспечивает передачу кода операнда на свой выход, являющийся входом-выхо- дом операционного блока 5(15) и соединенный со вторым входом коммутатора 35 базового адреса, со своего информационного входа в зависимости от разрешающего сигнала на своем уп- равляющем входе. При отсутствии разрешающего сигнала выход усилителя 34

находится в третьем состоянии. 1

, Коммутатор 35 базового адреса обеспечивает передачу унитарного код адреса на свой выход, соединенный с информационным входом регистра 36 селекции, с одного из двух входов, в зависимости от сигнала на своем управляющем входе.

Регистр 36 селекции обеспечивает запоминание унитарного кода адреса при наличии сигнала загрузки на его управляющем входе. Выход регистра 36 является составной частью управ- ляющегс выхода блока 5(15). Единичный сигнал в одном из разрядов регистра 36 обеспечивает выбор соответствующего блока модуля 2(3) для текущей с ним работы (выполнение цик ла записи или чтения). С выходом регистра 36 селекции соединены линии 56 селекции блоков 10(2.0) ввода-вывода, линия 57 селекции блоков 6(16) памяти, линия 58 селекции блоков 7(17) хранения индификаторов логических каналов, линия 59 селекции блоков 8(18) хранения индикаторов

процессоров, линия 60 селекции приоритетного блока 9(19).

Генератор 37 синхроимпульсов обе пе ивает выработку непрерывной последовательности синхроимпульсов на своем выходе, который соединен с управляющими входами регистра 25 регистра 29, дешифратора 33. Период следования синхросигналов определяет микрокомандный цикл блока 5(15).

Приоритетный блок 9(19) содержит (фиг. 5) регистр 38 свободных идентификаторов, предназначенный для хранения суперпозиции унитарных кодов свободных идентификаторов, которые используются для маркировки вновь устанавливаемых через данный модуль 2(3) логических каналов. Выход регистра 38 соединен со входо приоритетной схемы 39, с первым входом первой группы 42 элементов И и с первым входом группы 44 элементов RTIIii

Приоритетная схема 39 обеспечивает формирование на выходе, соединенном со входом шифратора 40 идентификатора логического канала и через группу 41 элементов НЕ со вторым входом первой группы 42 элементов И, унитарного кода старшего единичного разряда из суперпозиции унитарных кодов, присутствующей на ее входе. В таблице показано правило функционирования восьмиразрядной приоритетной схемы 39.

Шифратор 40 идентификатора логического канала обеспечивает преобразование унитарного кода со своего входа в двоичный код на выходе, соединенном с информационным входом второго буферного усилителя 46.

Первая группа 42 элементов И предназначена для формирования после очередного выделения унитарного кода свободного идентификатора логического канала новой, скорректированной суперпозиции -унитарных кодов в которой вьщеленный унитарный код погашен. Выход группы 42 элементов соединен с первым информационным входом коммутатора 43 идентификаторов.

Коммутатор 43 идентификаторов обеспечивает передачу информации на свой выход, соединенный с информационным входом регистра 38 свободных идентификаторов, с одного из

двух входов, в зависимости от управляющего сигнала на своем управляюще входе.

Дешифратор 45 идентификатора обе печивает преобразование двоичного кода вновь освободившегося идентификатора со своего входа в унитарный код идентификатора на выходе, соединенном через группу 44 элемен- тов ИЛИ со вторьм информационным входом коммутатора 43 идентификаторов .

Второй буферный усилитель 46 обеспечивает выдачу информации с выхода шифратора 40 идентификатора логического канала на шину 13(23) данных при наличии разрешающего сигнала на управляющем входе. При отсутствии разрешающего сигнала выход буферного усилителя 46 находится в третьем состоянии-.

Вторая группа 47 элементов И предназначена для вьщеления управляющих сигналов с шины 12(22) управления, адресованных к дан-юму приоритетном блоку 9(19). Первые входы всех элементов И группы 47 объединены и соединены с линией 60 селекции, являющейся составной частью управляющего входа блока 9(19). Вторые входы элементов И группы 47 соединены соответственно с другими управляющими сигналами, поступающими с управляющего входа блока 9(19) по управляю- щим линиям 63. Первый выход группы 47 соединен с управляющим входом коммутатора 43 идентификаторов. Второй выход соединен с синхррвходом регистра 38 свободных идентификато- ров. Третий выход соединен с установочным входом регистра 38 и обеспечивает начальную установку в единицу всех унитарных кодов. Четвертый выход соединен с управляющим входом второго буферного усилителя 46.

Каждый из блоков 10(20) ввода-вывода содержит (фиг, 6) выходной регистр 48, обеспечивающий запоминание выдаваемого информационного слова, которое присутствует на шине 13(23) данных, при наличии сигналов записи и селекции на входе загрузки и селектирующем входе. Выход регистра 33 соединен с выходной информационной шиной одного из внешних входов-выходов 14(24) - физических каналов связи модуля 2(3),

с Jo

is 20

25- зо

5

Вход-выход блока 10(20), подключенный к шине 13(23) данных соединен с информационными входами регистра 48, регистра 50 управления выдачей и регистра 51 управления приемом. Адресный вход блока 10(20), .подключенный к шине 11(21) адреса,соединен с информациоиньм входом дешифратора 52 адреса и адресным входом кo мyтaтopa 54 входной информации. Управляющий вход блока 10(20), подключенный к шине 12(22) управления, включает в себя линию 56 селекции данного блока 10(20), соединенную с первыми входами всех элементов и третьей группы 53, а также с управляющим входом дешифратора 52 адреса; линии чтения 61 и записи 62, которые подключены ко. вторым вхйдам соответствующих элементов И группы 53.

Элементы И группы 53 обеспечивают передачу сигналов со своих вторых входов на выходы при наличии разре- тающего сигнала на линии селекции.

Первый выход (линия записи) элементов И группы 53 соединен с син- хровхо дами регистров 48, 49, 50 и 51 j второй выход (линия чтения) соединен с управляюпщм входом третьего буферного усилителя 55,

Регистры 50 управления вьщачей и 51 управления приемом предназначены для синхронизации обмена инфор- мацией по физическому каналу в режиме передачи и приема соответственно. Их выходы являются составной частью внешнего входа-выхода 14(24) данного блока 10(20) ввода-вывода.

Регистр 49 приема информации обеспечивает запоминание входного слова и передачу его на свой выход, соединенный с первым входом коммутатора 54 входной информации,

I

Дешифратор 52 адреса обеспечивает декодирование двоичного кода адреса регистра данного блока 10(20),Четыре его выхода соединены с селектирующими входами соответственно регистров 48, 50, 49 и 51.

Коммутатор 54 входной информации обеспечивает передачу информации на свой вькод с одного из трех входов в зависимости от двоичного кода на своем адресном входе. Второй и третий информационный входы предназначены для передачи входных управляю25

их сигналов из физического канала вязи и соединены с линиями, обраующими часть линий внешнего входа- ыхода 14(24) блока 10(20) ввода- ывода. Выход коммутатора 54 соедиен с информационным входом третьео буферного усилителя 55.

Третий буферный усилитель 55 обеспечивает передачу информации на свой ю ыход для последующего ее анализа в блоке 5(15) со своего информационного входа в зависимости от присутствия разрешающего сигнала чтения на своем управляющем входе. В про- is тинном случае выход буферного усили- теля 55 находится в третьем состоянии.

Внешний вход-выход 14(24) блока 10(20) ввода-вывода образует один Ч физический канал связи модуля 2(3). Физический канал связи составляют следующие линии и шины:

-вьгходная информационная, шина 70;

-выходная линия 71 запроса на сеанс связи;

-выходная линия 72 установки выдаваемого слова;

-входная информационная шина 73J

-выходная линия 74 разрешения сеанса связи;

-выходная линия 75 квитирования принятого слова;

-входная линия 76 запроса на сеанс связи;35

-входная линия 77 установки входного слова;

-входная линия 78 разрешения сеанса связи;

-входная линия 79 квитирования 40 выданного слова.

Блоки 6-8, 16-18 могут быть реализованы на микросхемах оперативного i запоминающего устройства. Коммутаторы 27, 28, 35, 43 и 54 - на микро- 45 схемах мультиплексоров. Дешифраторы 33, 45 и 52, а также шифратор 40 - на соответствующих микросхемах. Приоритетную схему 39 можно реализовать с помощью элементов И-НЕ. В ка- 50 честве другого варианта реализации приоритетной схемы 39 и шифратора 40 можно использовать микросхему приоритетного шифратора. Регистры 25, 31, 32, 36 и 38 могут быть pea- 55 лизованы на соответствующих микросхемах, блок 26 хранения микропрограмм - на микросхемах ПЗУ, блок

30

5

s

Ч

5

0

30 - на микросхемах АЛУ. Цдя реализации генератора 37 может быть использована микросхема одновибратора. Регистры 48-51 могут быть реализованы на соответствующих микросхемах. В качестве другого примера реализации блока ввода-вывода 10(20) можно использовать БИС программируемого параллельно интерфейса. Буферные усилители 34, 46 и 55 могут быть реализованы на микросхемах шинных формирователей, а элементы И, ИЛИ, НЕ - на соответствующих микросхемах.

Система работает следующим образом.

Каждый процессор 4, подключенный к терминальному модулю 3 системы 1 коммутации, может находиться в свободном (пассивном) или в активном (занятом) состоянии. Свободные процессоры 4 переходят в активное состояние по коммутационным командам от других активных процессоров 4 при установлении между ними логических каналов связи. Поиск свободного процессора 4 осуществляется в тех случаях, когда любому активному процессору 4, выполняющему некоторое : задание, становится необходим, например, дополнительный ресурс памяти или дополнительный процессор 4 (вычислительный ресурс) определенного типа для непосредственного распараллеливания вычислительного процесса. Поиск свободного процессора 4 и одновременное установление логического канала к нему осуществляется децентрализованно коммутационными модулями 2 на основании служебной информа1Ц1и (индикаторов), имеющейся в каждом из них и динамически отображающей наличие в текущий момент свободных процессоров из числа процессоров 4, подключенных к системе 1.

Первоначально со.стояние индикаторов всех типов в блоках 8 и 18 хранения индикаторов процессоров каждого коммутационного модуля 2 и кажV дого терминального модуля 3 соответственно устанавливается при иниг циализации системы, а затем постоянно корректируется в процессе работы системы путем выдачи каждым терминальным модулем 3 после изменения состояния своего процессора соответствующей коммутационной команды (ал- гориткы на фиг. 8-11). Когда любой

процессор 4 типа q, становится свобоным, он выдает об этом сообщение в свой терминальный модуль 3, которьй формирует коммутационную команду Установка индикатора tf-го типа.Он распространяется по всем коммутационным модулям 2 и воспринимается всеми другими терминальными модулями 3. Принимая по j -му физическому каналу связи- эту команду, каждый коммутационный модуль 2 проверяет состояние индикатора в J -м разряде ячейки CJ, блока 8 хранения индикаторов маршрутов. Если индикатор равен единице, то команда блокируется. В противном случае устанавливается в единичное состояние соответствующий индикатор в блоке 8, а команда выдается в остальные физические каналы связи кроме J-го канала в соответствии со следующим правилом.

Если команда поступила в модуль 2 с более низкого (i-l)-ro уровня по j-му физическому каналу связи из числа физических каналов связи, то команда передается во все физические каналы связи, ведущие на более высокий или тот же уровни структуры при условии, что индикаторы ти- па fj по другим физическим каналам из числа t-, кроме j-го физического канала, равны нулю (условие А). Команда должна выдаваться в каждый физический канал из числа г , не равный j , если индикаторы типа о по всем другим физическим каналам из числа h , кроме данного, равны нулю (условие Б).

Если команда поступила с более

высокого или того же уровней по некоторому физическому каналуj из числа (L+K) каналов модуля 2, то она выдается в любой другой физический канал, если выполняется ус-

ловие Б.

Когда любой процессор 4 типа с

становится занятым, он выдает в свой терминальный модуль 3 соответствующее сообщение. По этому сообщению в модуле формируется и вьщается в смеж- ный коммутационный модуль 2 коммутационная команда Сброс индикатора ()-го типа, по которой каждый модуль 2, принимая ее по J му физическому каналу, устанавливает в нуль J -и ийдикатор в строке блока 8. Условия вьщачи этой команды в другие физические каналы аналогичны описанным.

Qj 2о

25 д

5

0

.. 5

0 5

При необходимости поиска, дополнительного ресурса свободного процессора 4) типа о любой активный процессор 4 вьщает в свой терминальный модуль 3 соответствующей запрос и сообщает при этом имя порта процесса - инициатора запроса. Из регистра 38 свободных идентификаторов приоритетного блока 19 в данном модуле 3 выделяется код свободного идентификатора, который после этого считается занятым, что фиксируется в соответствующем разряде регистра 38 данного модуля 3. Затем в модуле 3 производится взаимная привязка имени порта и вновь занятого идентификатора, что и означает установление логического канала связи через данный модуль 3. Для этого осуществляется запись кода выделенного идентификатора в блок 17 хранения идентификаторов в первую половину ячейки по адресу, определяемому име- нем порта, а также запись имени порта во вторую половину ячейки блока 17 по адресу, равному коду выбранного идентификатора. После этого модуль 3 формирует и выдает коммутационную команду Установка логического канала к свободному процессору типа Q . Эта команда сопровождается следующими параметрами: идентификатором, соответствующим данному логическому каналу и индик й- тором ( .

При получении этой команды по IJ-му физическому каналу через ,i-и бл ок 10 ввода-вывода каждый коммутационный модуль 2 проверяет наличие индикаторов в строке о блока 8 индикаторов процессоров. Если они есть, то из них выделяется наиболее предпочтительный индикатор, соотв тст- вующий физическому каналу S из числа I- , кроме физического канала j . Из регистра 38 свободных идентификаторов (фиг. 5) выделяется унитарный код наиболее приоритетного свободного идентификатора. В соответствии с правилом функционирования приоритетной схемы 39 (см. таблицу) это будет старший по номеру идентификатор. Первая группа элементов И 42 формирует новую суперпозицию унитарных кодов, в которой выделенный унитарный код вновь занимаемого идентификатора погашен. При подаче

сигнала записи из операционного блока 5 на синхровход регистра 38 в нем запоминается новая суперпозиция кодов. Двоичный код выделенного идеи тификатора с выхода шифратора 40 через второй буферный усилитель 46 считывается в операционный блок 5.

Для установления логического канала через данный модуль 2 принятый с командой и вновь выделенный идентификаторы запоминаются в соответствующих блоках 7 хранения идентификаторов. При этом в блок T.J, в первую половину ячейки по адресу, оп- ределяемому двоичным кодом принятого идентификатора, записывается двоичный код вновь занятого идентификатора и ко выходного физического кана- ла-S , а в блоке 7.S во вторую поло- вину ячейки по адресу, определяемому двоичным кодом вновь выделенного идентификатора, записывается код принятого идентификатора и код входного физического канала j . Затем в команду на место принятого идентификатора подставляется выделенный в данном модуле 2 идентификатор, и команда выдается в определенный ра - нее выходной физический канал S че- рез блок 10. S ввода-вывода.

Обрабатываемая таким образом в коммутационных модулях 2 эта коммутационная команда обеспечивает поиск ближайшего свободного процессора 4 требуемого типа и одновременное установление с ним двустороннего логического канала связи. При поступле- кик в найденный свободный процессор 4 коммутационной команды Установка виртуального канала он переходит 3 активное состояние, в нем порояуда- ется необходимый процесс, имя порта которого он сообщает своему терминальному модулю 3. Это имя порта за- писывается в блок 17 хранения идентификаторов, в первую половину ячейки по адресу, равному коду принятого идентификатора. Кроме того, во вторую половину ячейки блока 17 по ад- ресу, определяемому именем порта, записывается код принятого идентификатора. После этого модуль 3 выдает в систему 1 коммутации коммутацион- ную команду Сброс индикатора типа. Описанная процедура установления логического канала связи при поиске свободных процессоров может

выполняться одновременно в различных модулях системы 1 коммутации процессоров, что обеспечивает возможность параллельной обработки запросов на. свободные ресурсы различных типов, которые независимо поступают в терминальные модули 3.

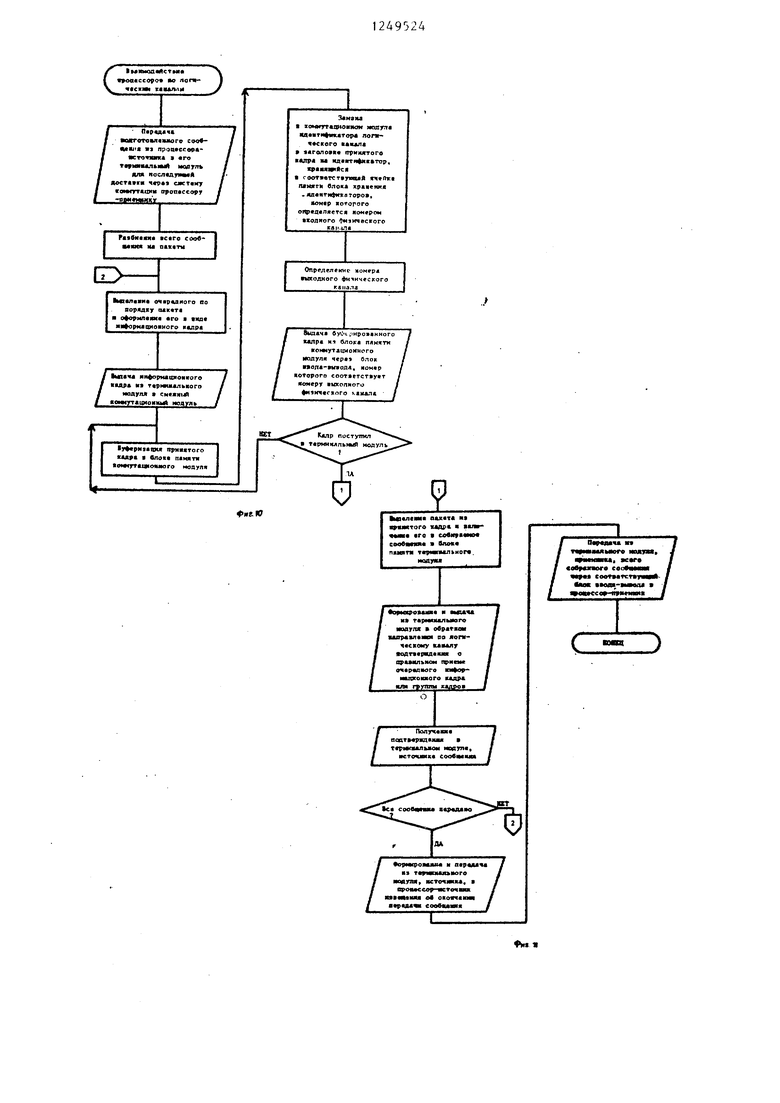

После логического связывания процессоры 4, являющиеся абонентами одного логического канала, мо гут обмениваться информацией по существующему между ними двустороннему логическому каналу (алгоритм на фиг. 10). Для этого передаваемое сообщение из процессора 4 должно поступить через соответствуюш1ий блок 20 ввода-вывода в блок 16 памяти терминального модуля 3. Это сообщение в терминальном модуле разбивается на отдельные пакеты, которые последовательно передаются через коммутационные модули 2 по созданному логическому каналу связи терминальному модулю 3, получателю сообщения. Для этого используются коммутационные команды Передача по прямому (обратному) логическому каналу. Каждая из этих команд содержит в заголовке кроме кода команды еще и иде нтификатор, соответствующий используемому -логическому каналу,Тело команды составляет пакет информации. При прохождении этих команд через модули 2 осуществляется замена принимаемого идентификатора на хранящийся идентификатор в соответствую- щем блоке 7. Номер выходного физического канала также считывается из соответствующей ячейки блока 7.Тер- минсшьный модуль 3, получатель информации, последовательно принимает отдельные пакеты, собирает их в целое сообщение, подтверждая этот факт терминальному модулю 3, отправителю сообщения. Цосле этого принятое сообщение вьюодится в процессор 4j приемник информации. После окончания взаимодействия

процессоров 4 через логический ка- налз связывающий их, этот канал может быть разрушен путем выдачи из терминального модуля 3, инициатора его установления5 коммутационной команды Разрушение виртуального канала, которая сопровождается идентификатором даннол-о канала. Эта команда следует через модули 2 по установленному ранее логическому каналу, уничтожая его. Для этого в каждом модуле 2 стирается служебная информация в блоках 7 хранения идеи тификяторов. Унитарный код освобождаемого идентификатора восстанавливается в регистре 38 свободных идентификаторов приоритетного блока 9, после чего он может быть снова ис- пользован в данном модуле 2 для ус- тдновления.новых логических каналов

Таким образом, в предлагаемом устройстве за счет децентрализованного и параллельного вьтолнения раз- личными терминальными и коммутационными модулями процедур поиска свободных процессоров 4 и одновременного установления логических каналов связи между ними достигается по срав нению с известным устройством уменьшение времени формирования логической связи между процессорами. Использование терминальных модулей 3 для организации межпроцессорных аза- имодействий существенно снижает загрузку процессоров, связанную с распараллеливанием вычислительного процесса на множестве подключенных к системе 1 коммутации процессоров. Все это способствует повьшению производительности вычислительной системы в целом. I

Сравнение процедур установления

логических каналов показывает еле- дующее. При волновом алгоритме поиска пути к свободным процессорам временные затраты всех коммутационных модулей, необходимые для установления одного логического канала, пропорциональны числу процессоров в системе, поскольку распространение одно волны поиска пути, по сути дела, означает попытку установления М-1 логического канала от процессора- инициатора ко всем остальным М-1 процессорам системы. В то же время, в предлагаемом устройстве эти временные затраты определяются усредненной длиной пути между процессорами. Это следует из того, что при поиске свободного процессора всегда устанавливается только один логический канал к ближайшему свободному вычислительному модулю на основе анализа инди- каторов процессоров, имеющихся в каждом коммутационном модуле. Это сравнение также свидетельствув об

.-

j 10

15. - 20 25-зо5й55

ад

уменьшении загрузки многоуровневой структуры системы коммутации процессоров и, следовательно, об увеличении ее пропускной способности. ,

Формула изобретения

1. Модульная многоуровневая сие- тема коммутации процессоров, содержащая N уровней коммутационных модулей, входьНвыходы которых через каналы связи подключены к входам-выходам коммутационных модулей своего и вьшерасположенного уровней, причем каждый коммутационный модуль содержит операционный блок, блок памяти, приоритетный блок и /t блоков ввода- вывода, где л, - число каналов срязи, входы-выходы которых являются входами-выходами обмена коммутационных модулей, адресный выход и выход .управления операционного блока подключены через шину адреса и шину управления к адресным входам и входам управления блока памяти, приоритетного- блока и блоков ввода-вывода соответственно, информационный вход-выход операционного блока подключен через шину данных к информационным входам-выходам блока памяти, приоритетного блока и блоков ввода-вывода, входы-выходы обмена которых являются входами-выходами обмена коммутационных модулей, отличающаяся тем, что, с целью повышения производительности путем увеличения пропускной способности при уменьшении временных затрат на управление межпроцессорньтми взаимодействиями, в нее введены М терминальных модулей, где М - число процессоров, подключенных к системе, разбитых на группы по г терминальных модулей в каждой группе,первый вход- выход обмена каждого терминального модуля является соответствующим входом-выходом сопряжения системы коммутации, вторые входы-выходы обмена f-. терминальных модулей одной группы соединены через г соответствующих каналов связи с t входами-выходами обмена одного из коммутационных модулей первого уровня, каждый из которых соединен соответственно по крайней мере одним каналом связи с расположенными на том же и более высоком уровнях коммутационными МОдулями, каждый из которых дополнительно содержит h блоков хранения идентификаторов логических каналов и h. блоков хранения индикаторов процессоров, входы-выходы которых соединены через шину данных с входами- выходами блоков хранения идентификаторов логических каналов, управляющие входы которых соединены через шину управления с управляющими входами всех блоков хранения индикаторов процессоров, адресные входы которых соединены через шину адреса с адресными входами всех блоков хранения идентификаторов логических каналов.

2. Система по п. 1, отличающаяся тем, что терминальный модуль содержит операционный блок.

00 О О

000000000000

00000001000-00001

0.0ОО001Х 0ооооо10

00 о о01X ХОО о о о

00001ХХХО0001000

0.001ХХХХО.0010-000

о о 1

ХХХХО 0100000

о 1 X X

X X

X о

ХХХХ10000000

X - безразличное состояние.

блок памяти, блок хранения идентификаторов логических каналов, блок хранения идентификаторов логических каналов, блок хранения индикаторов процессоров, приоритетный блок и два блока ввода-вывода, адресный выход, выход управления и информаци- онньй вход-выход операционного блока подключены через шины адреса, управления, данных к адресным входам, входам управления и информационным входам-выходам блока памяти, приоритетного блока, блока хранения

идентификаторов процессоров, блока хранения индикаторов процессоров и первого и второго блоков ввода-вывода, входы-выходы первого и второго блоков ввода-вьгеода являются первым

и вторым входами-выходами обмена терминального модуля.

о о

1000000

CPU г. 5

W(20)

fn п п п п

)

Фиг. 6

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Система для сопряжения терминальных устройств с вычислительной машиной | 1975 |

|

SU596938A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Коммутатор процессоров | 1977 |

|

SU734653A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для сопряжения процессоров | 1981 |

|

SU991404A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

Изобретение относится к вычислительной технике и позволяет сократить временные затраты при поиске свободного процессора в многопроцессорной вычислительной системе. Система 1 коммутации процессоров состоит из совокупности коммутационных модулей 2, расположенных на нескольких уровнях, и терминальных модулей 3, предназначенных для организации взаимодействия через систему 1 между процессами, реализуемыми в процессоре 4 данного терминального модуля 3, и процессами в других процессорах. Поиск свободного процессора и одновременное установление логического канала к нему осуществляется децентрализованно коммутационными модулями 2 на .основании служебной информации, имеющейся в каждом из них и динамически отображающей наличие в текущий момент свободных процессоров. 1 З.П., ф-лы, 12 ил. (Л ;о ел ю

гт п

(риг. 7

Нкицколихвцмя кодулсй

/ ВЧПАЧЛ кахд&м/

/ TepMHKiLnbHbM модулщ/

/ КОМАНДЫ Устако кя/

/ якдмддгор /

с

Виг.лча из iipoueccop тррмннальний модуль запроса ил Ресурс

Формирование и яьшач Н1 тернинлльного кодулч,

источника, я смежный fo№ yTauMOHMtrt модуль

команды Поиск

спибодного процессор

. требуриого типе

Устяноилр няе логического

канала через коммутаиноймыП модуль к блкЖвС1иену т еркннальнрму модулю /приемнику/, к

Которому Подключен

спободныП npoite ссор

TrpftvcMoro типл

Ооркнроалкие к выаачк

СО1 б1СС}О Я

из термиильного модуля.

|Овасп ч -1Ш9 параллсл kHuc

94ММОД1ЙСТВИЙ

|ггроц«ссор ни по

НАЛИМ CRiriN

1ервстро«мив логические к«м«ло« cmnt

«СЖДУ RpCUtCCOpUW

соотвшгспии с ; сАли|уем«« ппмсяхтсл мм процессом три ршмынн 9«лач до юлиого се заверсйння

Вьс1Ач и «тивирошлрного

процессоре в его теркикжлышй модуль сооб- «с«н Процесссгр чнят

1 мнроаакие в выяячш из гвркинаяьного коятлл

при о|ик«, а 1го гугланок(мй модуль

коыакды Сбрсх:

НЩТНКЯТОГй

ортройЯ11не н ташчл и« терчнжалъвого модул, гтрненямкл, по

построенному попммиоиу

каяАлу . тср ииал|.1ад молупь, ксточкик соовщеик 11олт8еркдеин«

ОРМИРОВННИ« М ВВД4Ч ИЯ

тсркнмлльногс мояулч, ксточмнкш, процессор

соовяеяиж Тревуемый , ресурс найден

С|м1(моа«йстмм1 Ч

oa cc4pott во norw- I «Пекин коиимн J

Передача

ШГГОТОМСЯЙОГС С94«ц Ш( яэ проавесооАСТОЧЖПСЖ 1 «го ТВУМПАЛАШМ ИО0ГПЪ

ля пасл«Д гммА ч«р«э cJKTeifT омкгтацим Dponeccopr

Зсмама

конкгтациоюкж шшугта кдвнтифккатора лопгЧФСКОГО АКАЛ«

«аголо 11« пришгтого «др« м мд«тф|к тор, paaJt iftcfl

сОоТ вТСТ ЯаЯвА ТЧФПК lUtwrM ОлокА хржяеккл

.ядвнпфпЕатороа,

ом«р жотогого

(ется номером

«одного физического

кап.и

Опрелелскнс комррд

ШХОДНОГО фН1ИЧ«СХОГО

канала

/

/

/

/

8ыпач калрс н

когмутлциомного

«юдуля блок

Пола-пподА, мон«р

которого соответствует

«омврт юеопного

физического мидла

11)0

мf

мшпп. у

«двушгаего /

«fM eo t «TcniiiM /

йос oni-ммалл у

metutcaf-пяпая

орФОРеМШЯ и ПЩАЧА

иодупк обрагвон

«шфавляшт по яогмчйскому кая&лу

одт ещдвшп о

орамшъмом приеме

ОЧ р«а«ОГО KM Qpмкдкокжаго кадра

ли ТТУТИШ KJAppi

Получ«кн« падт «ряд«)1Ш1 термавалыюн модул « сточних соовжмя

ДА

Пересг)оени« лот f веских клкалов / между процессорами I соответствии е рсяли1уени числит елью 1 процессом при ре- Ч иеннк залАЧН

Дезактивация процессоров, у которых раэруяеи

последний логический каиал

Требуются дополкителыша

свободные гфоцассоры для распараллеливания вычислительного процесса

Соэдакие в системе комнутации логических каналов исяету процессорами по запросам

активных процессоров

Формирование и

выпача иэ терминальных

модулей, чьи процессоры стали свободными команды Установка индикатора

Составитель А.Ушаков Редактор Н.Егорова Техред О.Гортвай Корректор А. Зимокосов

,.«вв™. в..-. мгл «ewe -e--ей - - - -.-.----

Заказ 4326/50 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий. 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Прангишвилли И.В | |||

| и Стецюра Г.И | |||

| Микропроцессорные системы | |||

| М.: Наука, 1980, с | |||

| Кран машиниста для автоматических тормозов с сжатым воздухом | 1921 |

|

SU194A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1976 |

|

SU983714A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многопроцессорная вычислительная система | 1974 |

|

SU962965A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-07—Публикация

1984-08-24—Подача