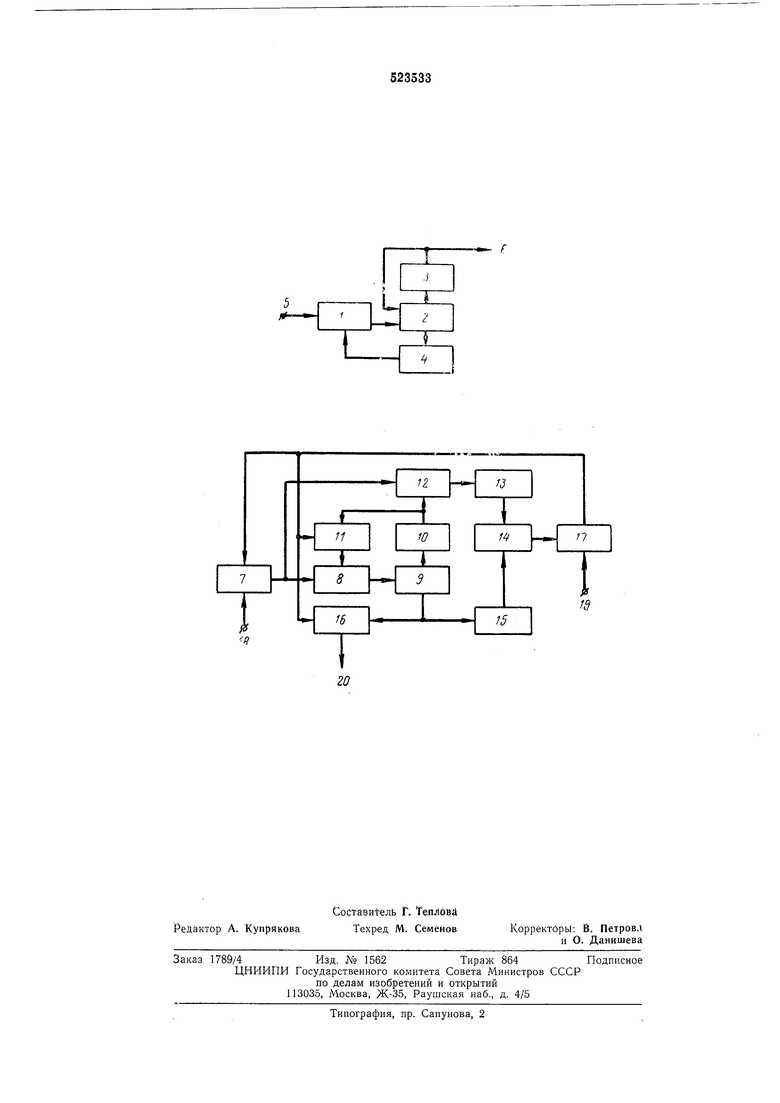

выходу первого элемента И 7 и сумматора 10, а выходом - через счетчик 13 к входу третьего элемента И 14, к другому входу которого подключен выход дешифратора 15 запрещенной комбинации сигналов, вход которого одновременно соединен с другим выходом регистра 9 сдвига и с одним из входов дешифратора 16 синхрокомбинации; триггер 17, выход которого подключен к соответствуюш им входам первого и второго элементов И 7, И, дешифратора 16, а установочный вход соединен с выходом третьего элемента И 14. Входы 18, 19 являются соответственно пнформацион ным ,и управляюш,им входами, а выход 20 - выходом синхросигнала приемной части устройства. Устройство работает следуюш,им образом.

При подаче тактовых силналов на вход 5 передаюш,ая часть начинает генерировать псевдослучайную (синхронизируюш,ую) последовательность. В случае установки в регистре 2 сдвига запреш,енного (нулевого) фазового состояния срабатывает дешифратор 4, с выхода которого сигнал через элемент ИЛИ 1 .поступает на вход установки регистра 2 сдвига в исходное состояние. С соответствующего выхода регистра 2 сдвига сигналы подаются на вход сумматора 3, с выхода которого псевдослучайная последовательность сигналов поступает на вход регистра сдвига и на выход 6.

В приемной части устройства принимаемая последовательность сигналов по входу 18 через элементы И 7 и ИЛИ 8 поступает на вход регистра сдвига 9. На второй вход элемента И 7 подается сигнал разрешения приема с выхода триггера 17. С выхода элемента И 7 принимаемые сигналы также подаются на вход комларатора 12. С соответствующего выхода регистра сдвига 9 принимаемая последовательность сигналов поступает в сумматор 10 и с его выхода па второй вход ко.мпаратора 12, с выхода которого результат сравнения поступает на вход счетчика 13, на выходе которого появляется сигнал, указывающий на факт вхождения приемной части устройства в синхронизм с передающей.

Если на информационный вход 18 поступила запрещенная последователькость сигналов длиной, достаточной для срабатывания счетчика 13, то сигнал на его выходе будет ложным. В этом случае ложный сигнал не пройдет до входа триггера 17, так как сигнал с выхода счетчика 13 на вход установки триггера 17 в положение «1 поступает через элемент И 14, на второй вход которого сишал разрешения подается с выхода дешифратора 15 запрещенной комбинации сигналов при ее отсутствии в регистре сдвига 9. При прохождении сигиала на вход устаиовки триггера 17 в ноложение «1 с его выхода соответствующие сигиалы поступают на входы элементов И 7, И 11 и дешифратора 16. В результате запрещается прохождение принимаемой последовательпости сигналов через элемент И 7 и разрещается через элемент И 11 с выхода сумматора 10 на вход регистра сдвига 9, а также включается деши|фратор 16. С этого момента начинается автономное генерирование

синхронизирующей последовательности в приемной части устройства. При появлении в регистре сдвига 9 сипхрокомбинации На выходе дещифратора 16 выделяется синхросигнал. В соответствующий момент времени по входу 19

подается сигнал установки триггера 17 в положение «О, и приемная часть подготавливается к новому циклу фазирования.

Формула изобретения

Устройство для синхронизации, содержащее в передающей части регистр сдвига, выход которого через сумматор ло модулю два подключен к своему входу, а в .приемной части -

первый элемент И, выход которого через последовательно соединенные элемент ИЛИ, регистр сдвига, сумматор по модулю два, соединенный через второй элемент И с другим входом элемента ИЛИ, компаратор подключен к счетчику, а также триггер, выход которого подключен к соответствующим входам первого элемента И, второго элемента И и дещифратора синхрокомбинации, к другому входу которого подключен второй выход регистра

сдвига, отличающееся тем, что, с целью повыщения надежности работы устройства и увеличения пропускной способиости, в передающую часть введены элемент ИЛИ и дешифратор запрещенной комбинации сигналов,

при этом другой выход регистра сдвига через дешифратор запрещенной комбинации и элемент ИЛИ нодключен к своему другому входу, а в приемную часть - дещифратор запрещенной комбинации сигналов и третий элемент И, причем упомянутый выход регистра сдвига через дешифратор запрещенной комбинации и третий элемент И подключен к зстановочяому входу триггера, а упомянутый выход первого элемента И подключен к второму входу компаратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

| Устройство для сигнализации и контроля объектов | 1978 |

|

SU741301A1 |

| Устройство для передачи информации шумоподобными сигналами | 1984 |

|

SU1256239A1 |

| Устройство диагностического контроля аппаратуры цифровой магнитной записи | 1987 |

|

SU1478253A1 |

| Устройство для сигнализации контроля объектов | 1981 |

|

SU966717A2 |

| Устройство циклового фазирования аппаратуры передачи дискретной информации | 1989 |

|

SU1626432A1 |

| Устройство для передачи коротких сообщений | 1983 |

|

SU1166329A2 |

| Устройство для передачи и приема сигналов начальной синхронизации | 1987 |

|

SU1543559A1 |

| Устройство для передачи и приема дискретной информации | 1980 |

|

SU886295A1 |

Авторы

Даты

1976-07-30—Публикация

1975-01-03—Подача