(54) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Устройство цикловой синхронизации (его варианты) | 1979 |

|

SU864586A1 |

| Устройство цикловой синхронизации | 1979 |

|

SU1259504A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство цикловой синхронизации (его варианты) | 1980 |

|

SU951738A2 |

| Устройство цикловой синхронизации | 1980 |

|

SU1341727A2 |

| Устройство синхронизации | 1980 |

|

SU982205A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство для цикловой синхронизации | 1982 |

|

SU1085005A2 |

1

Изобретение относится к электросвязи и может использоваться для обеспечения циклового фазирования систем передачи дискретных сообщений.

Известно устройство цикловой синхронизации, содержащее последовательно соединенные регистр сдвига, дещифратор, первый анализатор, первый накопитель, блок совпадения и генератор, выход которого подключен к другому входу первого анализатора, другой выход которого через второй накопитель подключен к другому входу первого накопителя, а также последовательно соединенные второй анализатор, блок управления и делитель, выход которого подключен к второму входу блока совпадения и первому входу второго анализатора, а другой вход делителя объединен с входом регистра сдвига и другим входом генератора, выход дещифратора подключен к второму входу второго анализатора, а дополнительный накопитель включен между выходом делителя и третьим входом блока совпадения 1.

Данное устройство обладает низкой помехоустойчивостью и малым быстродействием.

Наиболее близким по технической сущности к предлагаемому является устройство цикловой синхронизации, содержащее распределитель импульсов, один из выходов которого соединен с первым входом первого элемента НЕТ и с первым входом первого элемента И, выход которого подключен к тактовому входу первого накопителя, выход которого подключен к первому входу сброса второго накопителя, выход которого подключен к первому входу второго элемента И,

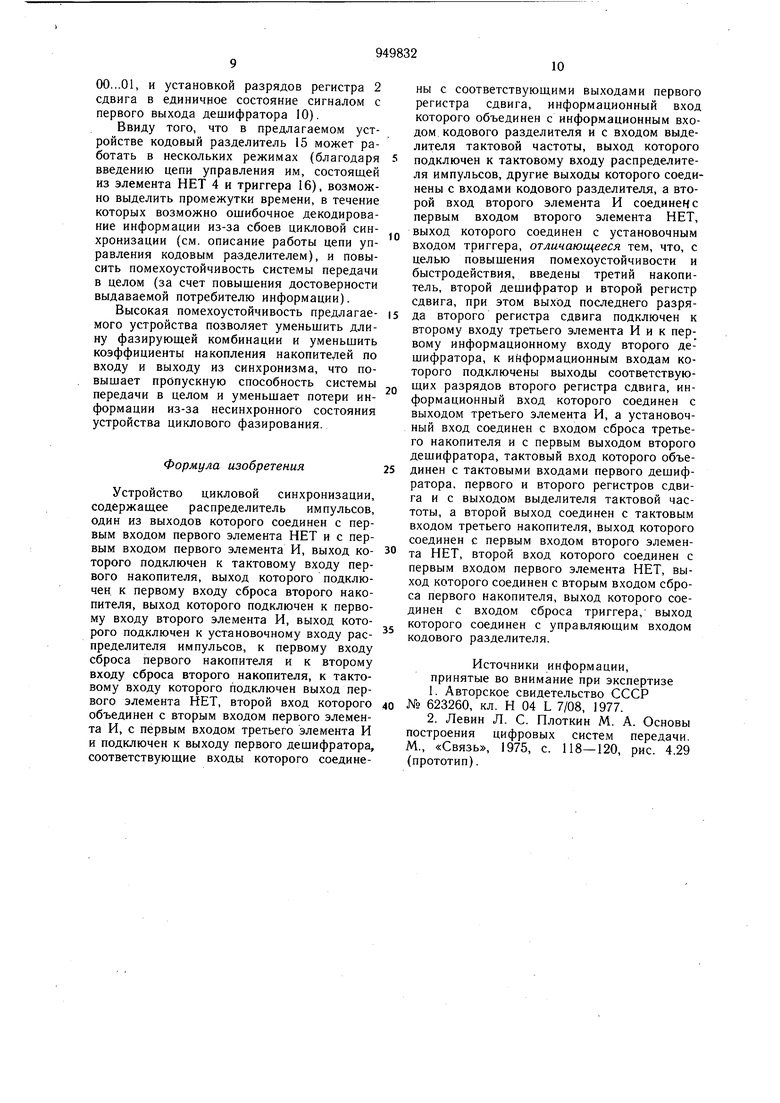

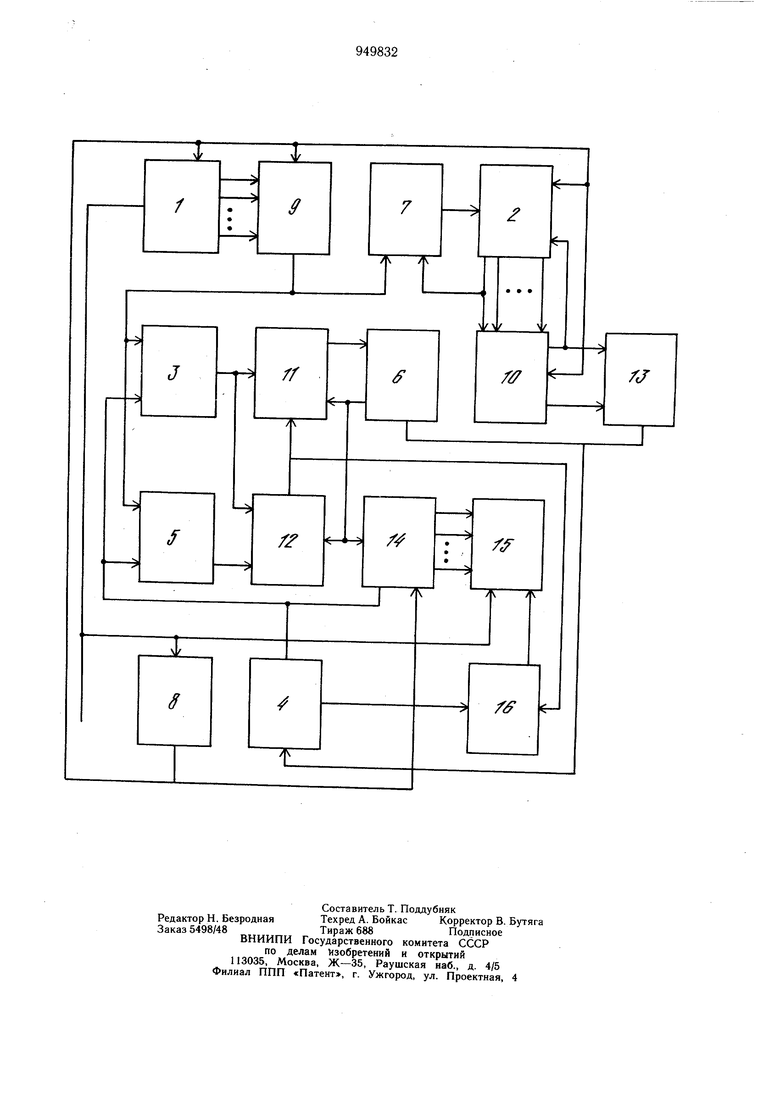

10 выход которого подключен к установочному входу распределителя импульсов, к первому входу сброса первого накопителя и ко второму входу сброса второго накопителя, к тактовому входу которого подключен вы15ход первого элемента НЕТ, второй вход которого объединен с вторым входом первого элемента И, с первым входом третьего элемента И и подключен к выходу первого дещифратора, соответствующие входы которого соединены с соответствующими выходами первого регистра сдвига, информационный вход которого объединен с информационным входом кодового разделителя и с входом выделителя тактовой частоты. ВЫХОД которого подключен к тактовому входу распределителя импульсов, другие выходы которого соединены с входами кодового разделителя, а второй вход второго элемента И связан с первым входом второго элемента НЕТ, выход которого соединен с установочным входом триггера 2. Однако и это устройство обладает низкой помехоустойчивостью и малым быстродействием. Цель изобретения - повышение помехоустойчивости и быстродействия. Указанная цель достигается тем, что в устройство цикловой синхронизации, содержащее распределитель импульсов, один из выходов которого соединен с первым входом первого элемента НЕТ и с первым входом первого элемента И, выход которого подключен к тактовому входу первого накопителя, выход которого подключен к первому входу сброса второго накопителя, выход которого подключен к первому входу второго элемента И, выход которого подключен к установочному входу распределителя импульсов, к первому входу сброса первого накопителя и к второму входу сброса второго накопителя, к тактовому входу которого подключен выход первого элемента НЕТ второй вход которого объединен с вторым входом первого элемента И, с первым входом третьего элемента И и подключен к выходу первого дешифратора, соответствующие входы которого соединены с соответствующими выходами первого регистра сдвига, информационный вход которого объединен с информационным входом кодового разделителя и с входом выделителя тактовой частоты, выход которого подключен к тактовому входу распределителя импульсов, другие выходы которого соединены с входами кодового разделителя, а второй вход второго элемента И связан с первым входом второго элемента НЕТ, выход которого соединен с установочным входом триггера, введены третий накопитель, второй дешифратор и второй регистр сдвига, при этом выход последнего разряда второго регистра сдвига подключен к второму входу третьего элемента И и к первому информационному входу второго дешифратора, к информационным входам которого подключены выходы соответствующих разрядов второго регистра сдвига, информационный вход которого соединен с выходом третьего элемента И, а установочный вход соединен с входом сброса третьего накопителя и с первым выходом второго дещифратора, тактовый вход которого объединен с тактовыми входами первого дешифратора, первого и второго регистров сдвига и с выходом выделителя тактовой частоты, а второй выход связан с тактовым входом третьего накопителя, выход которого соединен с первым входом второго элемента. НЕТ, второй вход которого связан с первым входом первого элемента НЕТ, выход которого соединен с вторым входом сброса первого накопителя, выход которого соединен со входом сброса триггера, выход которого связан с управляющим входом кодового разделителя. На чертеже изображена структурная электрическая схема предлагаемого устройства. Устройство цикловой синхронизации содержит регистры 1 и 2 сдвига, элементы НЕТ 3 и 4, элементы И 5, 6 и 7, выделитель 8 тактовой частоты, дешифраторы 9 и 10, накопители 11, 12 и 13, распределитель 14 импульсов, кодовый разделитель 15 и триггер 16. Устройство работает следующи.м образом. На выход устройства поступает последовательность принимаемых элементов сообщения, вследствие чего на выходе выделителя 8 тактовой частоты формируется последовательность импульсов синхронных и синфазных принимаемым элементам сообщения (частота следования этих импульсов равна частоте телеграфирования), обеспечивающая тактовую синхронизацию работы устройства. Если в регистре 1 сдвига оказывается записанной комбинация, аналогичная фазирующей, то на выходе дешифратора 9 формируется импульс. В случае синфазной работы устройства сигнал на выходе последнего такта распределителя 14 импульсов, период повторения которого равен циклу принимаемых сообщений, совпадает во -времени с сигналом наличия фазирующей комбинации на выходе дещифратора 9, вследствие чего на выходе элемента И 5 формируются импульсы, осуществляющие заряд накопителя 12 (накопителя по входу в сцнхронизм). При поступлении на тактовый вход накопителя 12 d импульсов подряд на его выходе формируется одиночный сигнал, осуществляющий сброс накопителя 11 (накопителя по выходу из синхронизма), а накопитель 12 возвращается в исходное (незаряженное) состояние. Затем вновь происходит его заряд и т. д. Если в момент формирования сигнала на выходе последнего такта распределителя 14 имеет место временное отсутствие сигнала на выходе дещифратора 9 (например, из-за искажения фазирующей комбинации в канале связи), то элемент И 5 остается закрытым, а на выходе элемента НЕТ 3 формируется сигнал, сбрасывающий накопитель 12 в «ноль и заряжающий накопитель 11 на «единицу. При поступлении на вход накопителя 11 b импульсов, если за это время не произошел сброс накопителя 11 сигналом с выхода накопителя 12, на выходе накопителя 11 формируется уровень напряжения, открывающий элемент И 6 по первому входу (устройство приняло решение о выходе из состояния синхронизма). Наличие в составе принимаемых элементов сообщения информационных комбинаций, аналогичных фазирующим, и формирование в соответствующие им моменты времени сигналов на выходе дешифратора 9 не оказывает влияния на работу накопителей 11 и 12, так как эти сигналы не совпадают во времени с сигналами на выходе последнего такта распределителя 14 (не проходят через элемент И 5 и НЕТ 3). Параллельная цепь контроля синхросигнала (элемент И 7,. регистр сдвига 2, дешифратор 10 и накопителя 13) работает следующим образом. В случае отсутствия информации в регистре сдвига 2 (например, в момент включения аппаратуры или после прерываний в канале связи) на первом выходе дещифратора 10 формируется импульс, устанавливающий разряды регистра 2 сдвига в единичное состояние. Под действием тактовых импульсов происходит продвижение единиц по регистру 2 сдвига. Информация с выхода последнего разряда регистра 2 сдвига поступает на второй вход элемента И 7, на первый вход которого в момент обнаружения в составе принимаемой информации комбинаций, аналогичных фазирующим, с выхода дешифратора 9 поступает импульс. Элемент И 7 осуществляет операцию логического умножения поступающей на его входы информации, вследствие чего в регистр сдвига 2 происходит запись единицы только при одновременном поступлении сигналов на оба входа элемента И 7. Таким образом, в устройстве происходит непрерывное последовательное во времени логическое умножение двоичных разрядов, соответствующих по расположению комбинациям, аналогичным фазирующим, Внутри принимаемого цикла сообщений, на соответствующие разряды результата анализа, получаемого из предыдущего цикла приема сообщений. Случайное расположение информационных комбинаций, аналогичных фазирующим, внутри принимаемых циклов сообщения и непрерывное поступление фазирующей комбинации на одной и той же временной позиции в каждом из циклов приводит к тому, что в один из моментов времени в регистре 2 сдвига окажется записанной комбинация 10...О (месторасположение единицы соответствует первому разряду 2 регистра, т. е. она поступает на последний информационный вход дешифратора 10). Вследствие этого на втором выходе дешифратора 10 формируется импульс, свидетельствующий об обнаружении параллельной цепью контроля синхросигнала фазирующей комбинации. Так как в регистре 2 сдвига записана комбинация 10...О, а фазирующая комбинация поступает в каждом цикле принимаемых сообщений, то и сигнал на втором выходе формируется в каждом цикле сообщений. В случае искажения фазирующей комбинации (или временного сбоя в работе системы передачи) сигнал на выходе дешифратора 9 в требуемый момент времени не формируется. Поэтому в, регистре сдвига 2 оказывается записанной нулевая комбинация, вследствие чего на первом выходе дещифратора 10 формируется импульс, устанавливающий разряды регистра 2 сдвига в единичное состояние. Сигналы со второго выхода дещифратора 10 поступают на тактовый вход накопителя 13. Сигналы на выход накопителя 13 с его тактового входа проходят на второй вход элемента И 6 только в том случае, если за промежуток времени между двумя сигналами с первого выхода дешифратора 10, сбрасывающими накопитель 13 в нулевое состояние, на втором выходе дешифратора 10 формируется подряд не менее Е импульсов (где Р - коэффициент накопления накопителя 13). В случае принятия устройством решения о выходе из синхронизма (формирование уровня напряжения на выходе накопителя 11) первый же сигнал со второго выхода дешифратора 10 пройдет через элемент И 6, сигнал с выхода которого сбросит накопители 11 и 12 в нулевое состояние и установит распределитель 14 импульсов в новое исходное состояние. Если это состояние является синфазным (вероятность чего весьма велика из-за высокой помехоустойчивости сигналов наличия фазирующей комбинации, на втором выходе дешифратора 10), то сигнал на выходе последнего такта распределителя 14 совпадает во времени с сигналом на выходе дешифратора, вследствие чего происходит заряд накопителя 12, и работа устройства продолжается вышеописанным образом. Если новое исходное состояние распределителя 14 не является синфазным (вероятность чего крайне мала), то происходит заряд накопителя И, а затем вышеописанным образом установка распределителя 14 в новое исходное состояние. Кодовый разделитель 15 под действием сигналов с выходов распределителя 14 импульсов осуществляет декодирование (определение временной позиции каждого элемента цикла) принимаемых элементов сообщения. Определение режима работы кодового разделителя 15 производится цепью, состоящей из элемента НЕТ 4 и триггера 16. Отсутствие сигнала на выходе триггера 16 разрешает декодирование информации в кодовом разделителе 15 и свидетельствует об уверенности в наличии цикловой синхронизации. Так как установка триггеpa 16 в единичное состояние производится сигналом с выхода элемента НЕТ 4, а его сброс - сигналом с выхода накопителя 12, то сигнал на выходе триггера 16, свидетельствующий о возможности отсутствия цикловой синхронизации, формируется только в еледующих трех случаях:

-если в регистре 2 сдвига циркулирует не одна, а несколько единиц, т. е. если цепь контроля синхросигнала не приняло рещения об обнаружении фазирующей комбинации (вероятность чего достаточна высока как в случаях высокого уровня помех в канале связи, так и в случае циклического повторения кодограмм сообщений или их частей);

-если сигнал на выходе последнего такта распределителя 14 импульсов не совпадает во времени с сигналом на втором выходе дешифратора 10, т. е. если произощел временной сбой в работе передатчика, либо если, в случае циклического повторения информации, содержащей комбинацию, аналогичную фазирующей, произошло искажение фазирующей комбинации;

-если сигнал на выходе последнего такта распределителя 14 совпадает во времени с сигналом на выходе дешифратора 10 в течение менее чем d циклов подряд, т. е. если устройство не приняло рещение о вхождении в синхронизм.

Такое управление режимом работы кодового разделителя 15 позволяет снизить вероятность выдачи потребителю ошибочно декодированной информации (повысить достоверность выдаваемой информации) из-за сбоев цикловой синхронизации. При этом работой элемента НЕТ 4 управляют сигналы с выхода накопителя 13, что также повышает достоверность выдаваемой потребителю информации.

Введение связи между выходом первого элемента НЕТ 3 и вторым сбросовым входом первого накопителя 12 обеспечивает в сравнении с прототипом, где эта связь отсутствует, повышение помехоустойчивости фазирования, так как этим исключается ложный заряд первого накопителя сигналами, которые не следуют один за другим в каждом цикле принимаемых сообщений (т. е. сигналами, сформированными на выходе дешифратора 9 из-за воздействия помех в канале связи или из-за случайных сочетаний информационных элементов сообщения, аналогичных фазирующим). Beроятность этого события в устройстве-прототипе при малой длине фазирующей комбинации достаточно велика, так как время поддержания синхронизма, как правило, выбирается во много раз больщим, чем время вхождения в синхронизм. Кроме того, введение выщеуказанной связи позволяет без снижения помехоустойчивости устройства при восстановлении синхронизма уменьшить коэффициент накопления первого накопителя 12, т. е. повысить быстродействие устройства и увеличить объем выдаваемой потребителю достоверной информации, так как сигнал с выхода накопителя 12 посредством триггера 16 управляет режимом работы кодового разделителя 15.

Параллельная цепь контроля синхросигнала обеспечивает защиту от ложных установок распределителя 14 импульсов в новое исходное состояние, поскольку алгоритм работы этой цепи, состоящей из элемента И 7, регистра сдвига 2, дешифратора 10 и накопителя 13, предусматривает проверку тождественности обнаруженной комбинации (аналогичной фазирующей) фазирующей комбинации путем последовательного во времени логического перемножения всех без исключения сигналов, формируемых на выходе дешифратора 9 (в том числе сформированных как под воздействием помех, так и в результате случайных сочетаний информационных разрядов), а сигнал на установку распределителя 14 в новое исходное состояние формируется в случае циркулирования в регистре 2 сдвига только одной единицы.

В устройстве-прототипе параллельная цепь контроля формирует выходной сигнал при двухкратном повторении на одних и тех же временных позициях циклов принимаемых сообщений первой же комбинации (и при том только одной за время длительности каждого цикла сообщений), которая следует во времени за искаженной фазирующей комбинацией. Поэтому предлагаемое устройство обеспечивает лучшую помехоустойчивость и более высокое быстродействие при восстановлении синхронизма (исключение ложных установок распределителя импульсов уменьщает время несинхронной работы устройства). Особенно это наблюдается в случае циклического повторения кодограмм или их частей, а также в случае малой длины фазирующей комбинации, т. е. когда вероятность формирования из информационных разрядов комбинаций, аналогичных фазирующим и расположенных на одних и тех же временных позициях в нескольких кодограммах весьма велика.

К повыщению быстродействия и помехоустойчивости устройства при восстановлении синхронизма приводит и зависимость числа проверок, через которое параллельная цепь контроля синхросигнала принимает рещение, что данная комбинация является истинно фазирующей, от структуры принимаемых сообщений, а также тем, что в случае искажения фазирующей комбинации, процесс проверки истинности данной комбинации начинается заново (это обеспечивается использованием дещифратора 10, выделяющего комбинации 00,..0 и 00...01, и установкой разрядов регистра 2 сдвига в единичное состояние сигналом с первого выхода дешифратора 10). Ввиду того, что в предлагаемом устройстве кодовый разделитель 15 может работать в нескольких режимах (благодаря введению цепи управления им, состоящей из элемента НЕТ 4 и триггера 16), возможно выделить промежутки времени, в течение которых возможно ошибочное декодирование информации из-за сбоев цикловой синхронизации (см. описание работы цепи управления кодовым разделителем), и повысить помехоустойчивость системы передачи в целом (за счет повышения достоверности выдаваемой потребителю информации). Высокая помехоустойчивость предлагаемого устройства позволяет уменьшить длину фазирующей комбинации и уменьшить коэффициенты накопления накопителей по входу и выходу из синхронизма, что повышает пропускную способность системы передачи в целом и уменьшает потери информации из-за несинхронного состояния устройства циклового фазирования. Формула изобретения Устройство цикловой синхронизации, содержащее распределитель импульсов, один из выходов которого соединен с первым входом первого элемента НЕТ и с первым входом первого элемента И, выход которого подключен к тактовому входу первого накопителя, выход которого подключен к первому входу сброса второго накопителя, выход которого подключен к первому входу второго элемента И, выход которого подключен к установочному входу распределителя импульсов, к первому входу сброса первого накопителя и к второму входу сброса второго накопителя, к тактовому входу которого подключен выход первого элемента НЕТ, второй вход которого объединен с вторым входом первого элемента И, с первым входом третьего элемента И и подключен к выходу первого дещифратора, соответствующие входы которого соединены с соответствующими выходами первого регистра сдвига, информационный вход которого объединен с информационным входом кодового разделителя и с входом выделителя тактовой частоты, выход которого подключен к тактовому входу распределителя импульсов, другие выходы которого соединены с входами кодового разделителя, а второй вход второго элемента И соединен с первым входом второго элемента НЕТ, выход которого соединен с установочным входом триггера, отличающееся тем, что, с целью повышения помехоустойчивости и быстродействия, введены третий накопитель, второй дещифратор и второй регистр сдвига, при этом выход последнего разряда второго регистра сдвига подключен к второму входу третьего элемента И и к первому информационному входу второго дешифратора, к информационным входам которого подключены выходы соответствующих разрядов второго регистра сдвига, информационный вход которого соединен с выходом третьего элемента И, а установочный вход соединен с входом сброса третьего накопителя и с первым выходом второго дешифратора, тактовый вход которого объединен с тактовыми входами первого дешифратора, первого и второго регистров сдвига и с выходом выделителя тактовой частоты, а второй выход соединен с тактовым входом третьего накопителя, выход которого соединен с первым входом второго элемента НЕТ, второй вход которого соединен с первым входом первого элемента НЕТ, выход которого соединен с вторым входом сброса первого накопителя, выход которого соединен с входом сброса триггера, выход которого соединен с управляющим входом кодового разделителя. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 623260, кл. Н 04 L 7/08, 1977. 2.Левин Л. С. Плоткин М. А. Основы построения цифровых систем передачи. М., «Связь, 1975, с. 118-120, рис. 4.29 (прототип).

Авторы

Даты

1982-08-07—Публикация

1981-01-13—Подача