I

} Настоящее изобретение относится к о&ласти радиотехники и может быть;использовано при разработке приборов с применение цифрового измерения относительного ослабления между ;побыми двумя уровнями иссле дуемого сигнала.

Известно устройство, содержащее компаратор, через интегратор подключенный- к выходу первого ключа, управлшощий вход jcoTOporo и управляющий вход интегратора :соединены с выходами блока управления, другой выход которого подключен к управляющему входу второго ключа, через который источник опорного напряжения подключен к опорному входу Гчомпаратора, выход .которого через блок управлекия поды/почен к управляющему входу элемента М-ИЛИ , , ;другой ВХОД последнего соедшшн с выходом генератора счетных импульсов, а выход подключен ко входу счетчика, i выход; кото- рого соединен с одним из входов блока |управления. Недостатком известного устройства является то, что в ряде случаев возникает необходимость в измерениях относи- 1тельного ослабления между любыми двумя

уровнями сигнала, В этом случае, npKMejrni известный преобразователь, нужно HIJOBOCTH измерение ослабления в двух точках, и, iviггем, расчетным путем вычислить искомое олабление. Раздельное измерение и пересчсг) увеличивают общее времп измерения одного :Параметра, :что уменьшает пpoиaвoдитeлыl( :труда.

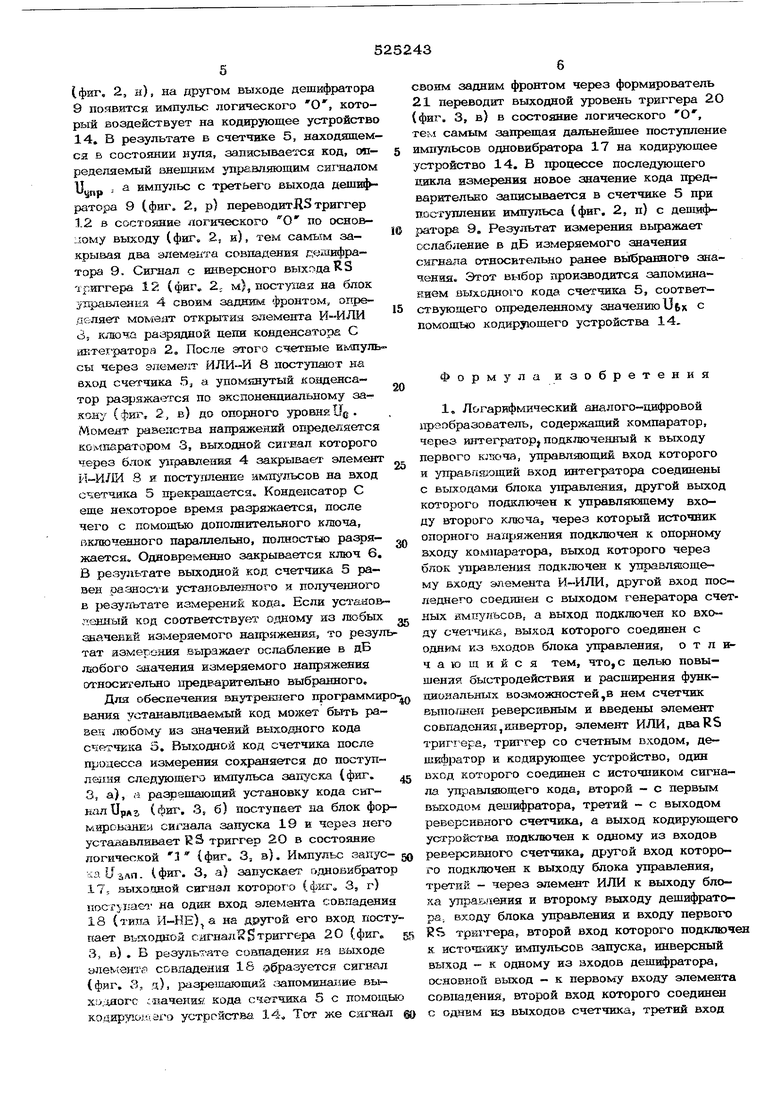

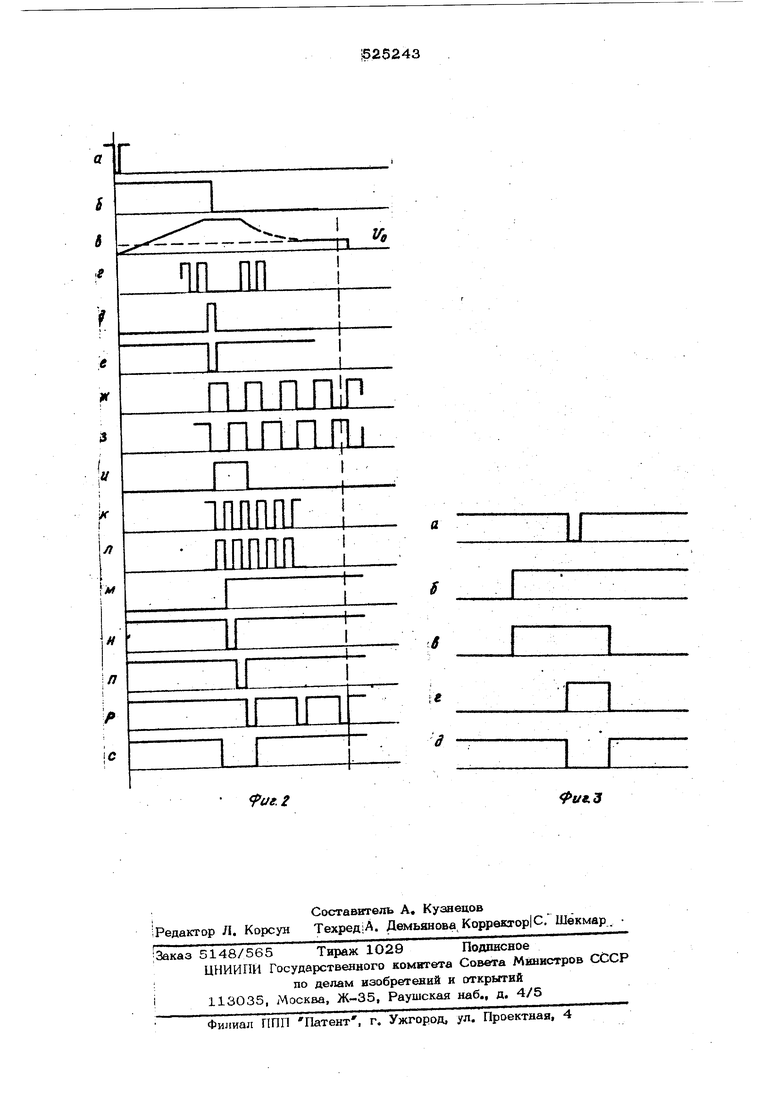

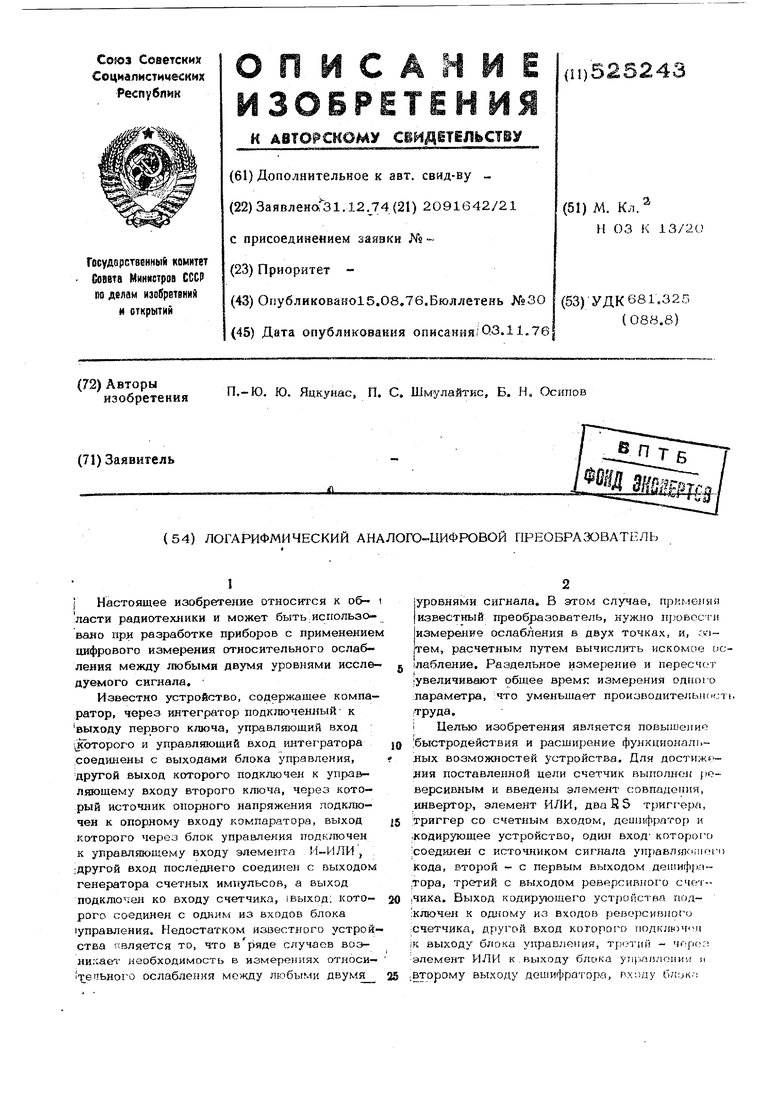

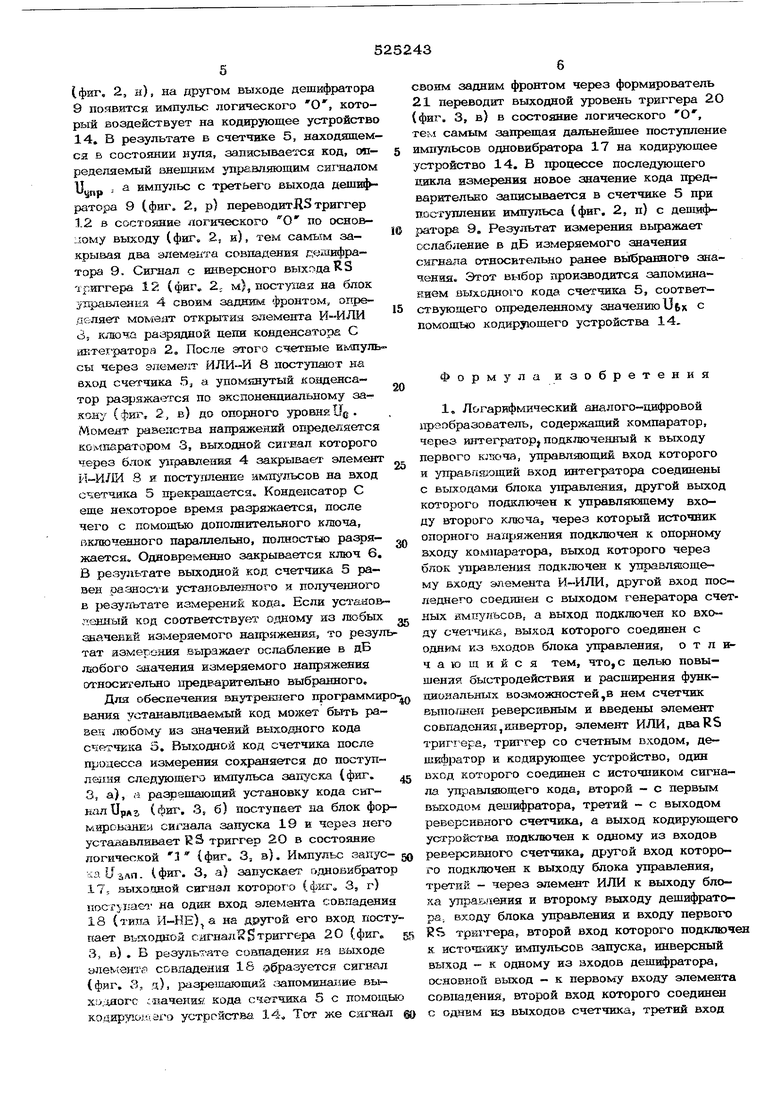

Целью изобретения является повышение ;быстродейстБия и расширение функциональных возможностей устройства. Для достижения поставленной цели счетчик выполнен роверсивным и введены элемент совпадения, инвертор, элемент ИЛИ, дваК5 триггера, ;триггер со счетным входом, доишфратор и -кодирующее устройство, одшг вход которого ;соединен с источником сигнала управлякшк-го Кода, второй - с первым выходом дешиф)атора, третий с выходом реверсив1гого счет-лика. Выход кодирующего устройства подключен к одному из входов реверсивного :Счетчика, другой вход которого подклн) |к выходу блока управления, тротин - элемент ИЛИ к. выходу блока утц.апдоии/г я ,второму выходу дешифратора, блик-: управления и входу первого RB тригтера, второй вход которого подключен к источнику импульсов запуска, инверсный выход - к одному из входов дешифратора, основной выход - к первому входу элемента совпадения, второй вход которого соединен с одним из выходов счетчика, третий вход со входом триггера со счетным входом и через инвертор - с выходом генератора счетных импуль сов и одним из входов дешифратора, два других входа которого подключены к выходам триггера со счетным входом. Установочный вход последнего соединен с выходом элемента совпадения и первым входом второго TR 5 триггера, второй вход которого подключен к третьему выходу дешифратора, инверсный выход - к одному из входов блока управления, а основной - к одному из входов дешифратора Другой целью изобретения является обеспечение внутреннего программирования. Для этого в аналого-цифровой преобразователь введены блок формирования сигнала запуска, дополнительный КЗ триггер, дополнителъ ный элемент совпадения, формирователь и одновибратор, через который источник импул сов запуска соединен со входом блока упра.& ления и с одним из входов дополнительного элемента совпадения, другой вход которого подключен к выходу дополнительного S триггера, один вход которого соединен через блок формирования сигналов запуска с выходом источника сигнала, разрешающего установку кода, а второй вход через формирователь подключен к вьосоду дополннтельно элемента совпадения и входу кодируюшего устройства, На фиг, 1 приведена функциональная схем логарифмического аналого-цифрового преобразователя. На фиг« 2 и 3 временные диаграммы сигналов в различных точках преобразователя. Логарифмический аналого-цифровой преобразователь содержит ключ 1, инвертор 2, компаратор 3, блок управления 4, реверсивный счетчик 5, ключ 6, генератор счетных импульсов, 7, элемент И-ИЛИ 8, дешифратор 9, инвертор 10, элемент совпадения 11, RS триггер 12, триггер со счетным входом 13, кодирующее устройство 14, схему ИЛИ 15, триггер 16, одновибратор 17, элемен совпадения 18, блок формирования сигнала запуска 19, триггер 20 и форм1арователь 21, Преобразователь работает следующим образом. Исследуемый аналоговый Ug поступает на вход ключа 1, В начальный мо мент, до поступления имп -льса -залгуска USASI все ключи закрыты и напряжение аа выходе интегратора 2 равно нулю Импульс запуска (фиг, 2, а) поступает на установочный вход ИЗ триггера 16 и переводит один из его выходов в состо5шие логической . Это напряжение (фиг, 2, б) подается на один из входов элемента совпадения 11, Упомянутый импульс запуска воздействует на бяок }Т1рэ.вления 4, который открывает ключ 1 и схему И-ИЛИ 8„ В результате этого BbJxoAiioe нагфяженке интегратора 2 Ея кнает изменяться (фиг„ 2, в), а имугульсь с генератора счетных импульсов 7 через элемент И-ИЛИ 8 поступают на вход реверсивного счетчика 5 (фиг, 2, г). После накопления счетч. заданного чясла й1уаг.упьсов, на его Бь,гходе появл5гетс0 сигкал логический I (фиг, 2, д). который коступаег на один из входов элемента сов-аадения .11, При совнадении лоплеских I на ее входах (на одном - отйЗ триггера 16, на другом от счетчшса 5, на третьем - от генератора счетных иг.щш.ыюв 7, поступающ1ОС через иквертор Ю) на ез выходе появится логический (фиг,- 2, е), который поступает на установочный вход триггера со счетным входом 13 и переводит его в состояние логической l по основному выходу. ,Этот же сигнал поступает на установочный входи S триггера 12 и переводит его основной выход в состояние логической 1 (фиг. 2, и). Сигнал с инверслого выхода RS тршпгера 12 поступает на блок управления 4 и через нее закрывгпт ключ 1, В интеграторе 2 может быть кспо;Гь.чован, например, операционный усилитель с F;:3icoK:fflvi входным сопротив лением. Это позволит запоминать выходное напряжение Hirrei ратора а течение некоторого интервала времени после закрьггия ключа 1 (фиг. 2, в). Когда иа выходе элемента совпадения 11 появятся логический О (фиг. 2, а)з то на входы дешифратора 9 подаются импульсы: с основного и инверсного выходов jfpHiTepa 13 (фаг, 2, ж, з),с основного выходаR9триггера 12 (фиг. 2, и), с выхода генератора счетных импульсов 7, причем од;«п череа ирвертор Ю (фкг 2, к, п} а другой - с инверсного выхода триггера .16 (фиг. 2, м), Комбиналия упомзнугых импульсов поступает на три трехвходовых элемента совпадения И-НЕ, образующих дешифратор 9, 8результате на одг.ом выходе де лифратора 9появится сигнал логического О (фиг. 2, н), который через элемент ИЛИ 15 переводит в нулевое состг яиие с етчик 5, через блок управления 4 перек/яочаег счеа-чик 5 на вычитание, а также nepeao.eaiT S триггер 16 в состоззкие „логической 1 ;:io ш.1вер( выходу (фиг„ 2, м). Вслед за ймтт. (фиг. 2, н), на другом выходе дешифратора 9 появится импульс логического О, который воздействует на кодирующее устройство 14. В результате в счетчике 5, находшдем- ся в состоянии нуля, записывается код, ояределяемый внешним управляющим сигналом Uyj,p , а импульс с третьего выхода дешифратора 9 (фиг, 2, р) переводитКЗтриггер 12 в состояние логического О по основному выходу (фиг. 2, и), тем закрывая два элемента совпадения к уд1ифратора 9. Сигнал с инверсного триггера 12 (фиг, 2, м), постухшя на блок jTipaBneaiia 4 своим задним фронтом, определяет момеат открытия элемента И-ИЛИ 3, ключа разрядной цепи конденсатора С интегратора 2, После эаого счетные иьшуль сы через элемент ИЛИ-И 8 поступают на вход счетчика 5, а упомйнутый конденсатор раз|)яжается по экспонешщальному закону (фиг, 2, в) до опорного уровняУе , Момеят равенства напряжений определяется компаратором 3, выходной сихнал которого через блок уггравления 4 закрывает элемент й-ИЛИ 8 и поступление имщшьсов на вход счетчика 5 прекрашается Конденсатор С еще некоторое время разряжается, после чего с помощью дополнительного ключа, включенного параллельно, полностыо разряжается. Одновременно закрывается ключ 6, В результате выходной код счетчика 5 равен разности установленного и полученного в 1)езультате измерений кода. Если установленный код cooTBGTCTByfjT одному из любых зваченЕй измеряемого напряжения, то резул тат измерения выражает ослабление в дБ любого значения измеряемого напряжения относительно предварительно выбранного. Для обеспечения внутрекнего программир вания устанавливаемый код может быть равен атюбому из значений выходного кода счр гчика 3. Выходной код счетчика после продесса измерения сохраняется до поступлеггая следующего импульса защска (фиг. 3, а), а раа(рашающий установку кода сигнал С фиг, 3, б) поступает на блок фор мированЕм сигнала запуска 19 и через него устанавливает KS триггер 2 О в состояние логической 3 (фиг„ 3, Б). Импульс эапус sa IJjiAn, (фиг. 3, а) запускает одновибрато ITj выходной сигнал которого (фкг„ 3, г) nocrjiiaea на один вход элемента совпадени i 8 (типа И-НЕ) а на другой его вход пост пает выходной сигная Н триггера 20 (фиг„ 3, в) , В результате совпадении на выходе улемешч совладения 18 образуется сигнал (фиг. 3, и), разрезпаюпщй ;запоминя1.ше вы- x-;j.:XHorc :йачения кода счегчика 5 с помощь кодиру1с 1и aio устройства 14 Тот же сигнал своим задним фронтом через формирователь 21 переводит выходной уровень триггера 2 О (фиг. 3, в) в состояние логического О, тем самым запрещая дальнейшее поступление импульсов одновибратора 17 на кодирующее устройство 14. В тфоцессе последующего цикла измерения новое значение кода предварительно записывается в счетчике 5 при постуллениЕ импульса (фиг. 2, п) с дешифратора 9, Результат измерения вьфажает ослабление в дБ измеряемого значения сз4гнала относительно ранее вЫбранноге значения. Этот выбор производится запоминанием выходного кода счетчика Б, соответствующего определенному значению 13 Ьх с помощью кодирующего устройства 14. Формула изобретения 1, Логарифмический аналого-цифровой преобразователь, содержащий компаратор, через HHTerpaTopj подключенный к выходу первого кгеоча, управляющий вход которого и управляющий вход интегратора соединены с выходами блока управления, другой выход которого подключен к управлякяцему входу второго ключа, через который источник опорного напряжения подключен к опорному входу компаратора, выход которого через блок управления подключен к управляющему элемента И-ИЛИ, другой вход последнего соединен с выходом генератора счетных импульсов, а выход подключен ко входу счеа-чика, выход которого соединен с одним из входов блока управления, отличающийся тем, что, с делью повыщения быстродействия и расширения функциональных возможностей,в нем счетчик выполнен реверсивным и введены элемент совпадения,инвертор, элемент ИЛИ, дваЯЗ триггера, триггер со счетным входом, дешифратор и кодирующее устройство, один вход которого соединен с источником сигнала управляющего кода, второй - с первым выходам дешифратора, третий с выходом реверсивного счетчика, а выход кодирующего устройства подключен к одному из входов реверсивного счетчика, другой вход которого подключен к выходу блока управления, третий - через элемент ИЛИ к выходу блока у11ра.11ения и второму вых.оду дешифратора, входу блока управления и входу первого RS трштера второй вход которого подключен к источнику импульсов запуска, инверсный выход - к одному из входов дешифратора, основной выход - к первому входу элемента совпадения, второй вход которого соединен с одним из выходов счетчика, третвй вход

-со входом триггера со счетным входом п через инвертор - с выходом генератора счетиых импульсов и одним из входов дешиф-j ратора, два других входа которого подключе-i ны к выходам триггера со счетным .входом 5 установочный вход последнего соединен с выходом элемента совпадения и первым входом BTOporoRS триггера; второй вход которого подключен к третьему выходу дешиф ратора,; инверсный выход - к одному изю

входов блока управления, а основной выход

-к одному из входов дешифратора,

2, Преобразователь по п. 1, отличающийся тем, что, с целью обеспечения внутреннего программирования, в ; 15

|нёго введены блок формирования сигнала запуска, дополнительныйК5 триггер, дополнительный элемент совпадения, формирователь и одновибратор, через который источник импульсов запуска соединен со входом блока управления и с одним из входов дополнительного элемента совпадения, другой вход которого подключен к выходу дополнительного триггера, один вход которого соед1шен через блок формирования сигналов запуска с выходом источника сигнала, разрешающего установку кода, а второй вход через формирователь подключен к выходу дополнительного элемента совпадения и входу кодирующего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ИЗНОСА РЕЖУЩЕГО ИНСТРУМЕНТА | 2004 |

|

RU2263300C1 |

| СПОСОБ ИЗМЕРЕНИЯ ИЗНОСА РЕЖУЩЕГО ИНСТРУМЕНТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2354955C1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ КОЭФФИЦИЕНТОВ ПЕРЕДАТОЧНЫХ ФУНКЦИЙ ЛИНЕЙНЫХ ДИНАМИЧЕСКИХ ОБЪЕКТОВ И ЗАДАТЧИК ПРОБНЫХ СИГНАЛОВ ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1997 |

|

RU2131139C1 |

| Устройство для обработки хроматографической информации | 1980 |

|

SU896645A2 |

| Устройство для управления регулируемым преобразователем переменного напряжения в переменное | 1990 |

|

SU1739452A1 |

| Устройство для измерения произведения двух напряжений | 1983 |

|

SU1195265A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

VjffnQ Ураз

Выход

ШЛДШ

ллплш

fus.2

f

t 8

t/e.3

Авторы

Даты

1976-08-15—Публикация

1974-12-31—Подача