сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Система для контроля электронных устройств | 1978 |

|

SU978151A2 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

Изобретение относится к области радиотехники и может быть использовано в системах синхронизации и синхронизирующих устройствах. Цель изобретения - повышение помехоустойчивости. Устройство для коррекции шкалы времени содержит генератор 1. фазосдвигающий блок 2. делитель 3 частоты, преобразователь 4 кода, регистр 5 сдвига, преобразователь 6 кода коррекции, счетчик 7. дешифратор 8. формирователь 9 одиночных импульсов, счетчик 10, распределитель 11 сигналов, элемент И 12, регистр 13 сдвига, регистр 14, блоки сравнения 15 и 16 кодов, дешифратор 17, триггеры 18 и 19, элемент И 20. Устройство обеспечивает возможность приема кодированных команд управления и повторного кода коррекции. 3 ил,

XI

оо

CN О О

Изобретение относится к радиотехнике и может быть использовано в системах синхронизации и синхронизирующих устройствах.

Известно устройство для коррекции шкалы времени, содержащее генератор, фазосд- вигающий блок, делитель частоты, регистр сдвига, счетчик, элемент совпадения, реверсивный счетчик, формирователь сигнала управления, дешифратор, формирователь одиночных импульсов и преобразователь кода коррекции.

Известно также устройство для коррекции шкалы времени, содержащее генератор, делитель частоты, хранитель времени, элементы совпадения, два счетчика импульсов, инвертор, электронные ключи, два формирователя управляющих сигналов и регистр сдвига.

Известно также устройство для коррекции шкалы времени, содержащее генератор, фазосдвигающий блок, делитель частоты, электронны е переключатели, два счетчика, элемент И, сумматор, регистр сдвига, дешифратор, элементы ИЛИ, формирователь одиночных импульсов, блок электронных ключей, инвертор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, триггер.

Такие устройства обладают низкой помехоустойчивостью, т.к. воздействие помех на информационные и управляющие входы может привести либо к искажению записываемого в устройство кода коррекции, либо к записи произвольного кода коррекции и запуску коррекции, а значит к сбою шкалы времени.

Наиболее близким к предлагаемому устройству является устройство для коррекции шкалы времени, которое выбрано в качестве прототипа.

Устройство-прототип содержит генератор, фазосдвигающий блок и делитель частоты, а также регистр сдвига, преобразователь кода коррекции, счетчик, дешифратор, формирователь одиночных импульсов, элемент И, триггер, четыре элемента И, элемент ИЛИ, формирователь импульсов, реверсивный счетчик, формирователь сигнала управления, элемент И-НЕ, Устройство-прототип имеет информационный вход для сигнала Код коррекции, а также управляющие входы Ввод коррекции и Коррекция,

Устройство-прототип обладает низкой помехоустойчивостью. Это связано с тем, что воздействие помех на входы Ввод коррекции или Коррекция приводит к срабатыванию формирователя, сбросу счетчика и, как следствие, разрешению работы преобразователя кода коррекции, запуску формирователя и возможному сдвигу шкалы времени или сбою кода времени.

Кроме того воздействие помех на информационный вход устройства при записи

кода коррекции может привести к его искажению, а значит и к ошибке коррекции, причем эта ошибка может значительно превышать ту ошибку хранения шкалы времени, которую призвана устранить прово0 димая коррекция.

Таким образом недостатком прототипа является низкая помехоустойчивость.

Целью изобретения является повышение помехоустойчивости.

5 Сущность изобретения состоит в том, что в устройство для коррекции шкалы времени, содержащее последовательно соединенные генератор, фазосдвигающий блок и делитель частоты, последовательно соеди0 ненные преобразователь кода коррекции и регистр сдвига, выход младшего разряда которого соединен с первым управляющим входом фазосдвигающего блока, вход преобразователя кода коррекции является ин5 формационным входом устройства, тактовый выход преобразователя кода коррекции соединен со счетным входом счетчика, выходы разрядов счетчика через дешифратор соединены с первым входом

0 формирователя одиночных импульсов, второй вход которого соединен с выходом фазосдвигающего блока, последовательно соединенные триггер и первый элемент И, а также второй элемент И, введены последо5 вательно соединенные дополнительный счетчик, распределитель сигналов и дополнительный триггер, последовательно соединенные дополнительный регистр сдвига, регистр, дополнительный дешифратор и

0 преобразователь кода, а также первый и второй блоки сравнения кодов, при этом информационный вход дополнительного регистра сдвига соединен с информационным выводом преобразователя кода коррекции,

5 тактовый выход которого через второй элемент И соединен с тактовым входом допол- нительного регистра сдвига, выход формирователя одиночных импульсов соединен со счетным входом дополнительного

0 счетчика и со входом распределителя сигналов, второй выход которого соединен с установочным входом триггера, третий выход распределителя сигналов соединен с тактовым входом регистра, а четвертый выход

5 распределителя сигналов соединен с первым управляющим входом преобразователя кода коррекции и со вторым входом первого элемента И, выход которого соединен со входом запуска преобразователя кода, пер- вый выход которого соединен со вторым управляющим входом фазосдвигающего блока, выход которого соединен со входом сигнала синхронизации преобразователя кода, другие выходы которого соединены соответственно с входом сброса и с входами установки первой и второй шкал времени делителя частоты, выход которого соединен со вторым управляющим входом преобразователя кода коррекции и со входом установки регистра, выходы разрядов которого соединены с входом триггера через первый блок сравнения кодов, другие входы которого соединены с выходами соответствующих разрядов регистра сдвига и с первой группой входов второго блока сравнения кодов, причем выходы соответствующих разрядов регистра сдвига за исключением младшего разряда соединены с информационными входами преобразователя кода, управляющие входы которого соединены с выходами дополнительного дешифратора, выходы разрядов дополнительного регистра сдвига соединены со второй группой входов второго блока сравнения кодов, выход которого соединен с третьим входом первого элемен- та И, выход дополнительного триггера соединен с вторым входом второго элемента И, входы установки счетчика и дополнительного счетчика, третий управляющий вход преобразователя кода коррекции и второй вход установки дополнительного триггера соединены между-собой и являются входом управляющего сигнала устройства, выходом контрольного сигнала которого является выход первого элемента I/I

Сущность изобретения состоит в том, что повышение помехоустойчивости достигается за счет-обеспечения возможности управления двоично кодированными командами и приема повторного кода коррекции с конт- ролем правильности его приема.

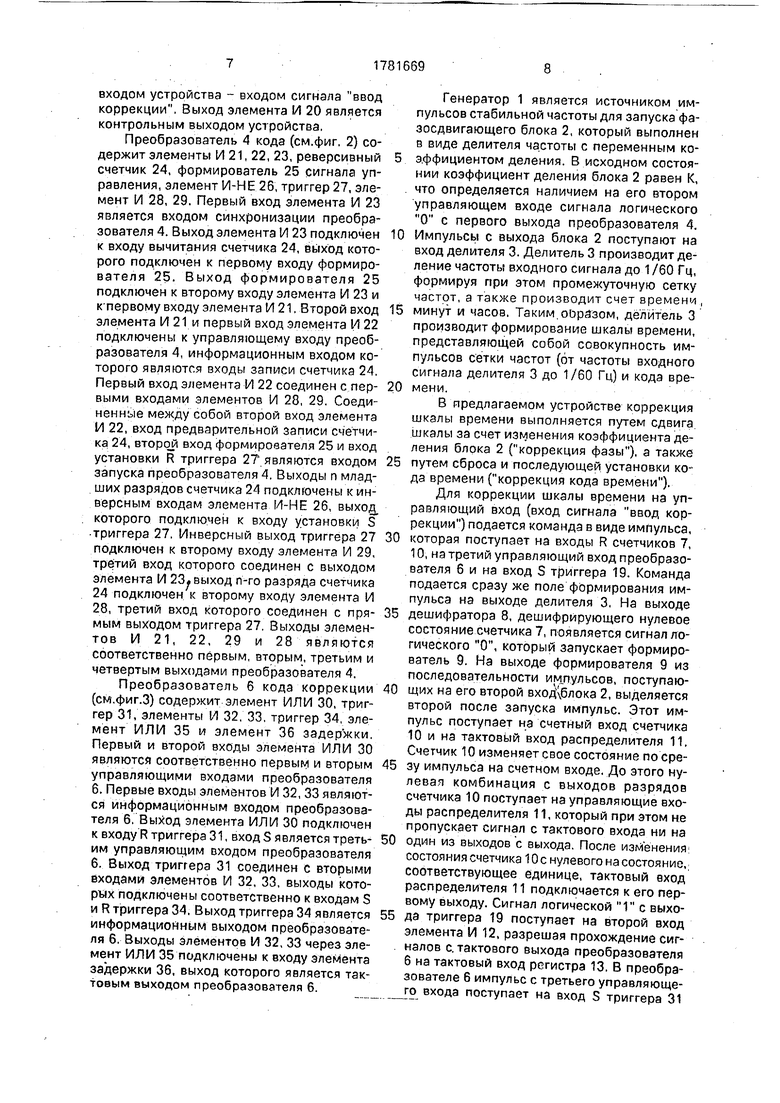

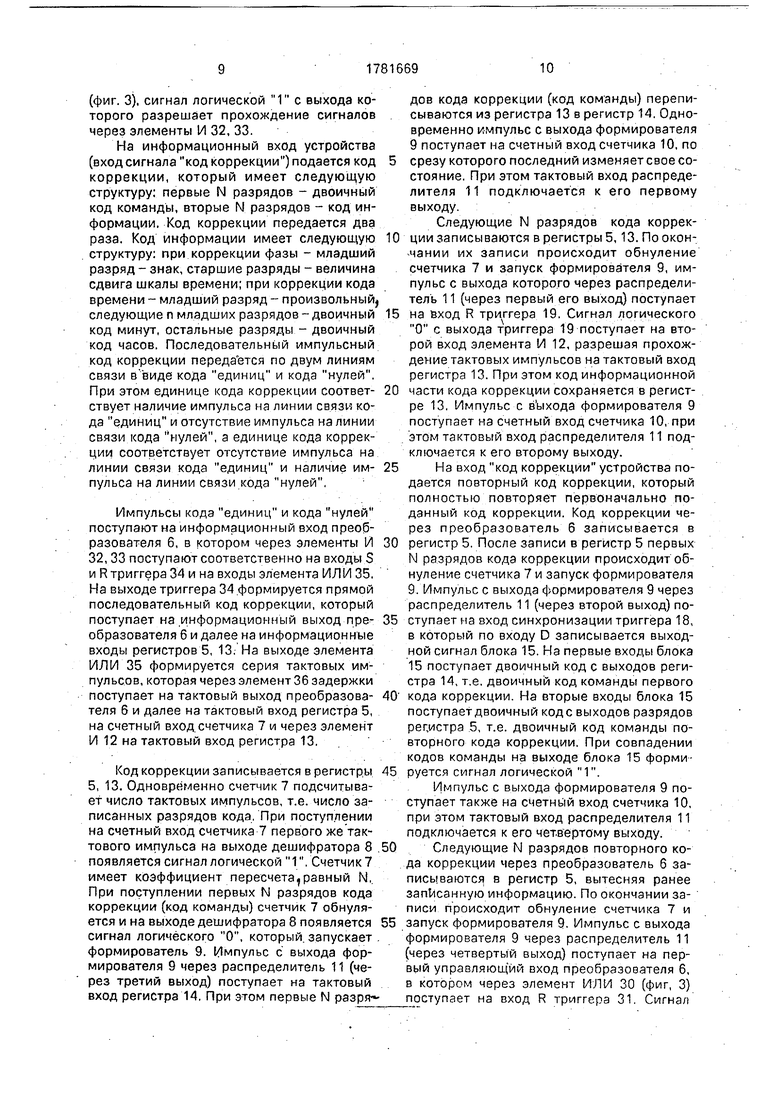

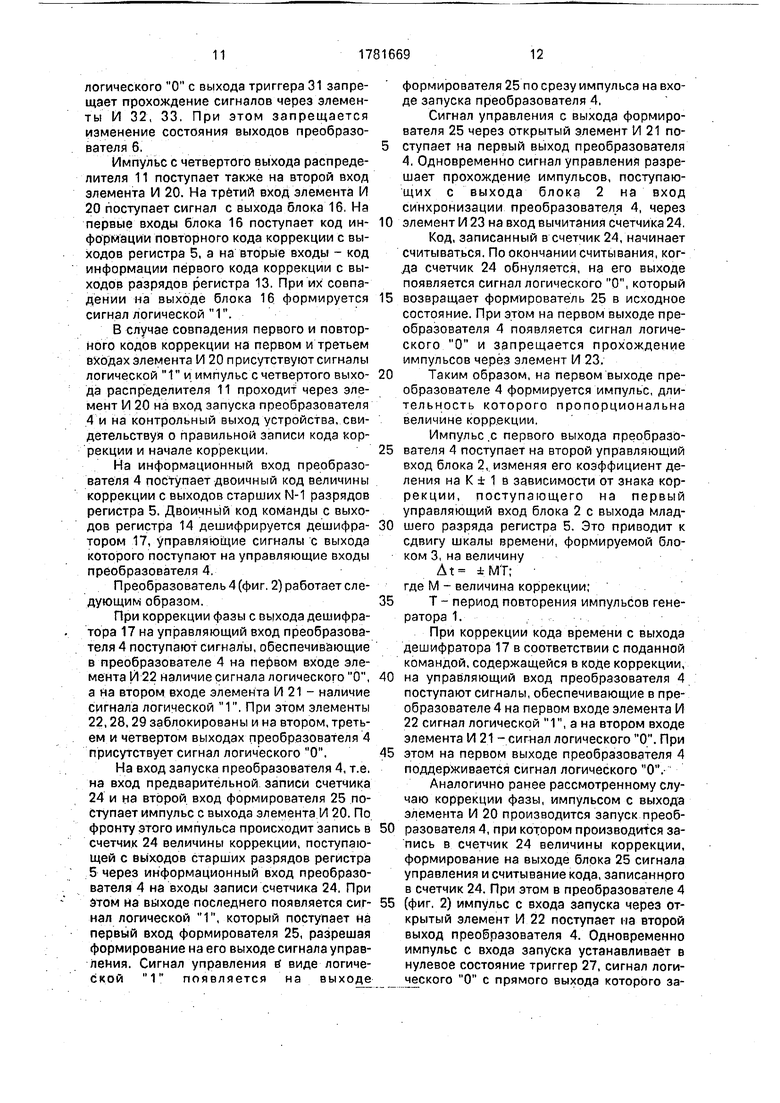

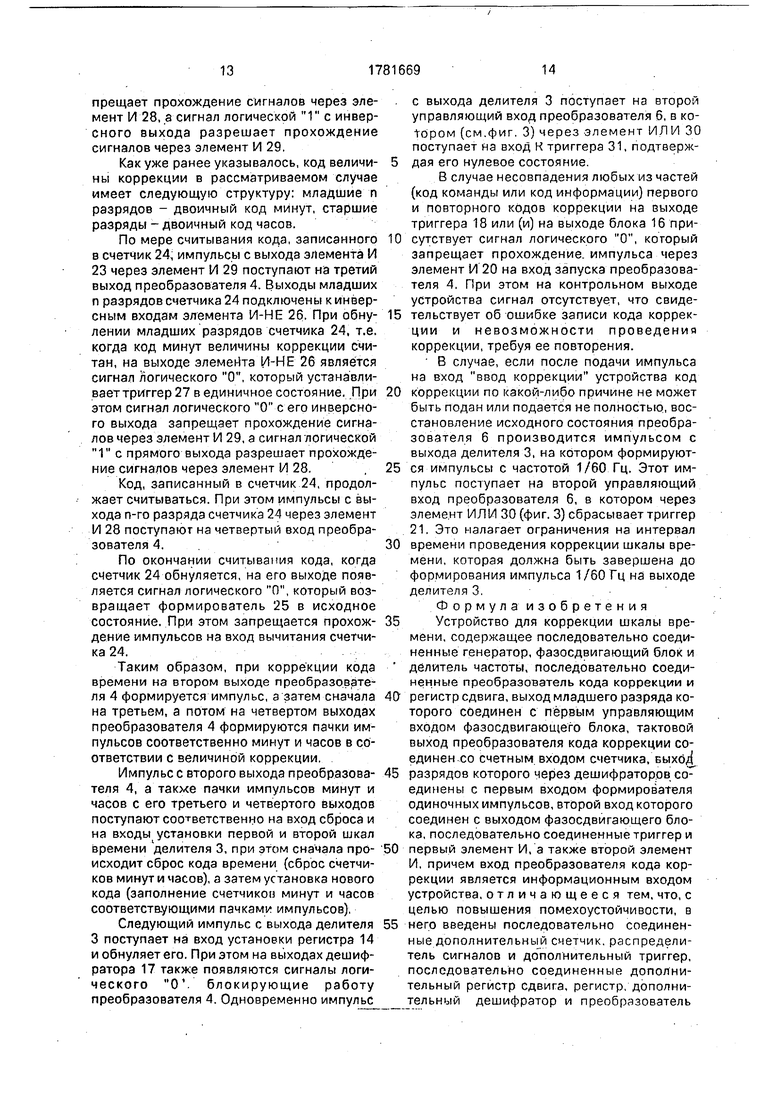

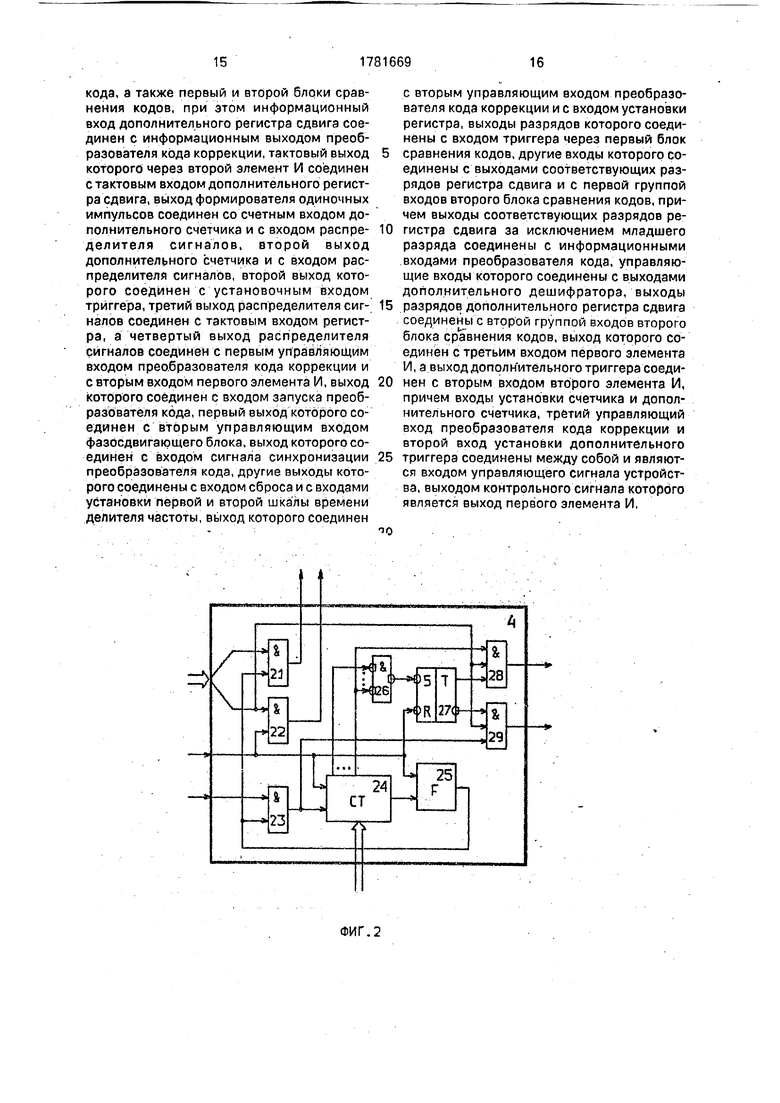

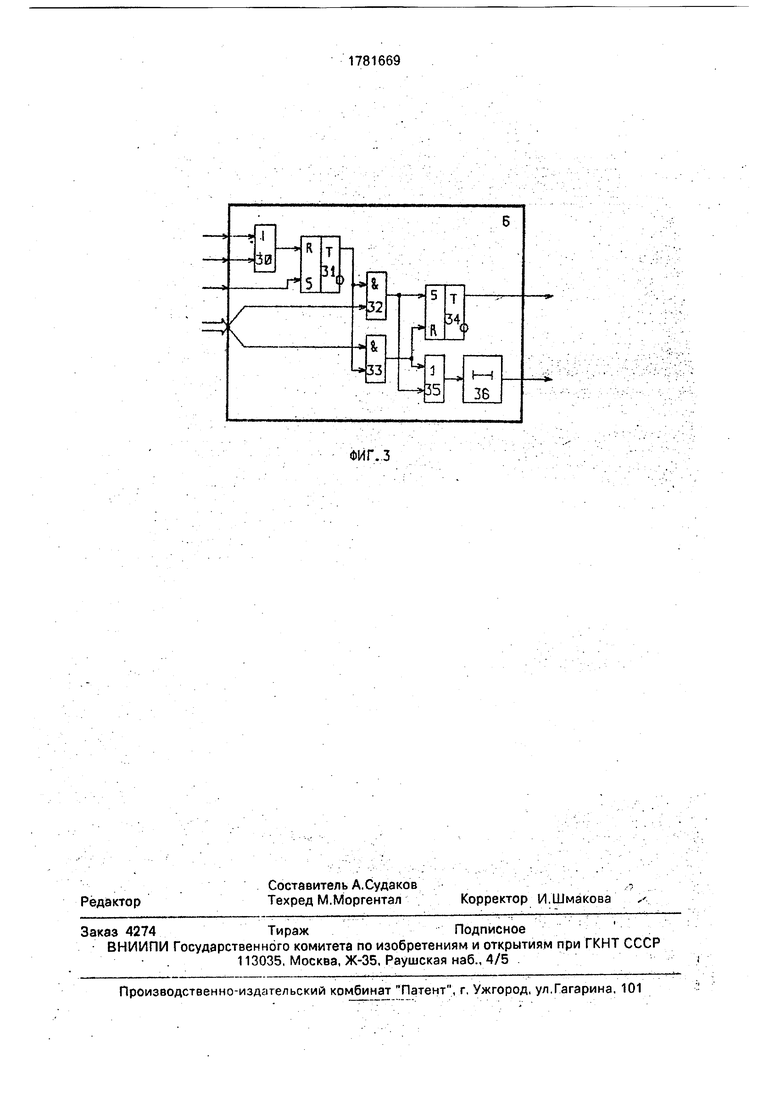

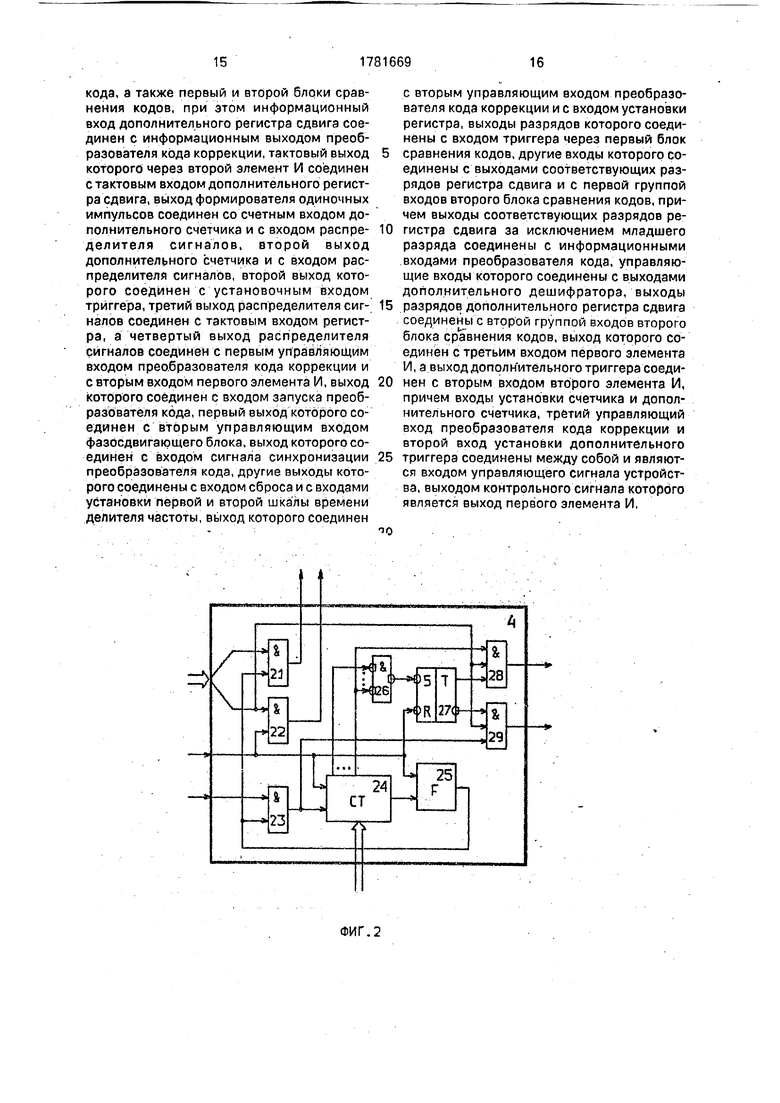

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 -структурная схема преобразователя кода; на фиг, 3 - структурная схема преобразователя ко- да коррекции.

Устройство для коррекции шкалы времени (фиг. 1) содержит последовательно соединенные генератор 1, фазосдвигающий блок 2 и делитель 3 частоты, а также преоб- разователь 4 кода, регистр 5 сдвига, преобразователь б кода коррекции, счетчик 7, дешифратор 8, формирователь 9 одиночных импульсов, счетчик 10, распределитель 11 сигналов, элемент И 12, регистр 13 сдвига, регистр 14, блоки 15, 16 сравнения кодов, дешифратор 17, триггеры 18 19, элемент И 20. Вход преобразователя 6 является информационным входом устройства - входом сигнала код коррекции, а «го информационный и тактовый выходы подключены к соответствующим входам регистра 5, выход младшего разряда которого подключен к первому управляющему входу блока 2, а выходы старших разрядов соединены с информационным входом преобразователя 4. Первый выход преобразователя 4 подключен к второму управляющему входу блока 2, а его второй, третий и четвертый выходы подключены соответственно к входу сброса и к входам установки первой и второй шкалы времени делителя 3. Тактовый выход преобразователь 6 подключен к счетному входу счетчика 7, выходы разрядов которого через дешифратор 8 подключены к первому входу формирователя 9. Второй вход формирователя 9 соединен с входом сигнала синхронизации преобразователя 4 и подключен к выходу блока 2. Информационный вход регистра 13 подключен к информационному выходу преобразователя 6, тактовый выход которого через элемент И 12 подключен к тактовому входу регистра 13, Выход формирователя 9 подключен к тактовому входу распределителя 11 и к счетному входу счетчика 10, выходы разрядов которого подключены к управляющим входам рас- пределителя 11. Первый выход распределителя 11 подключен к первому входу установки (R-вход) триггера 19, выход которого подключен к второму входу элемента И 12. Второй выход распределителя 11 подключен к входу синхронизации триггера 18, выход которого подключен к первому входу элемента И 20. Третий выход распределителя 11 подключен к тактовому входу регистра 14, выходы разрядов которого подключены к первым входам блока 15 и к входам дешифратора 17. Выходы всех разрядов регистра 5 подключены к вторым входам блока 15 и к первым входам блока 16. Выход блока 15 подключен к информационному входу триггера 18. Четвертый выход распределителя 11 подключен к второму входу элемента И 20 и к первому управляющему входу преобразователя 6, второй управляющий вход которого соединен с входом установки регистра 14 и с выходом делителя 3, Выходы разрядов регистра 13 подключены к информационным входам регистра 14 и к вторым входам блока 16, выход которого подключен к третьему входу элемента И 20. Выходы дешифратора 17 подключены к управляющим входам преобразователя 4, вход запуска которого подключен к выходу элемента И 20, Соединенные между собой третий управляющий вход преобразователя 6, второй вход установки (S-вход) триггера 19 и входы установки счетчиков 7, 10 являются управляющим

входом устройства - входом сигнала ввод коррекции. Выход элемента И 20 является контрольным выходом устройства,

Преобразователь 4 кода (см.фиг, 2) содержит элементы И 21, 22, 23, реверсивный счетчик 24, формирователь 25 сигнала управления, элемент И-НЕ 26, триггер 27, элемент И 28, 29. Первый вход элемента И 23 является входом синхронизации преобразователя 4. Выход элемента И 23 подключен к входу вычитания счетчика 24, выход которого подключен к первому входу формирователя 25. Выход формирователя 25 подключен к второму входу элемента И 23 и к первому входу элемента И 21, Второй вход элемента И 21 и первый вход элемента И 22 подключены к управляющему входу преобразователя 4, информационным входом которого являются входы записи счетчика 24. Первый вход элемента И 22 соединен с первыми входами элементов И 28, 29. Соединенные между собой второй вход элемента И 22, вход предварительной записи счетчика 24, второй вход формирователя 25 и вход установки R триггера 27 являются входом запуска преобразователя 4, Выходы п младших разрядов счетчика 24 подключены к инверсным входам элемента И-НЕ 26, выход которого подключен к входу установки S триггера 27. Инверсный выход триггера 27 подключен к второму входу элемента И 29, третий вход которого соединен с выходом элемента И 23. выход n-го разряда счетчика 24 подключен к второму входу элемента И 28, третий вход которого соединен с прямым выходом триггера 27. Выходы элементов И 21, 22, 29 и 28 являются соответственно первым, вторым, третьим и четвертым выходами преобразователя 4.

Преобразователь 6 кода коррекции (см.фиг.З) содержит элемент ИЛИ 30, триггер 31, элементы И 32, 33, триггер 34, элемент ИЛИ 35 и элемент 36 задержки. Первый и второй входы элемента ИЛИ 30 являются соответственно первым и вторым управляющими входами преобразователя 6. Первые входы элементов И 32, 33 являются информационным входом преобразователя 6. Выход элемента ИЛИ 30 подключен к входу R триггера 31, вход S является третьим управляющим входом преобразователя 6. Выход триггера 31 соединен с вторыми входами элементов И 32, 33, выходы которых подключены соответственно к входам S и R триггера 34. Выход триггера 34 является информационным выходом преобразователя 6. Выходы элементов И 32, 33 через элемент ИЛИ 35 подключены к входу элемента задержки 36, выход которого является тактовым выходом преобразователя 6.

Генератор 1 является источником импульсов стабильной частоты для запуска фа- зосдвигающего блока 2, который выполнен в виде делителя частоты с переменным коэффициентом деления. В исходном состоянии коэффициент деления блока 2 равен К, что определяется наличием на его втором управляющем входе сигнала логического О с первого выхода преобразователя 4.

Импульсы с выхода блока 2 поступают на вход делителя 3. Делитель 3 производит деление частоты входного сигнала до 1/60 Гц, формируя при этом промежуточную сетку частот, а также производит счет времени ,

минут и часов. Таким оорйзом, делитель 3 производит формирование шкалы времени, представляющей собой совокупность импульсов сетки частот (от частоты входного сигнала делителя 3 до 1/60 Гц) и кода времени.

В предлагаемом устройстве коррекция шкалы времени выполняется путем сдвига шкалы за счет изменения коэффициента деления блока 2 (коррекция фазы), а также

путем сброса и последующей установки кода времени (коррекция кода времени).

Для коррекции шкалы времени на управляющий вход (вход сигнала ввод коррекции) подается команда в виде импульса,

которая поступает на входы R счетчиков 7, 10, на третий управляющий вход преобразователя б и на вход S триггера 19. Команда подается сразу же поле формирования импульса на выходе делителя 3, На выходе

дешифратора 8, дешифрирующего нулевое состояние счетчика 7, появляется сигнал логического О, который запускает формирователь 9. На выходе формирователя 9 из последовательности импульсов, поступающих на его второй вход блока 2, выделяется второй после запуска импульс. Этот импульс поступает на счетный вход счетчика 10 и на тактовый вход распределителя 11. Счегчик 10 изменяет свое состояние по срезу импульса на счетном входе. До этого нулевая комбинация с выходов разрядов счетчика 10 поступает на управляющие входы распределителя 11, который при этом не пропускает сигнал с тактового входа ни на

один из выходов с выхода. После изменения состояния счетчика 10 с нулевого на состояние, соответствующее единице, тактовый вход распределителя 11 подключается к его первому выходу. Сигнал логической 1 с выхода триггера 19 поступает на второй вход элемента И 12, разрешая прохождение сигналов с. тактового выхода преобразователя 6 на тактовый вход регистра 13. В преобразователе 6 импульс с третьего управляющегр входа поступает на вход S триггера 31

(фиг. 3), сигнал логической 1 с выхода которого разрешает прохождение сигналов через элементы И 32, 33.

На информационный вход устройства (вход сигнала код коррекции) подается код коррекции, который имеет следующую структуру: первые N разрядов - двоичный код команды, вторые N разрядов - код информации. Код коррекции передается два раза. Код информации имеет следующую структуру: при коррекции фазы - младший разряд - знак, старшие разряды - величина сдвига шкалы времени; при коррекции кода времени - младший разряд - произвольны следующие п младших разрядов-двоичный код минут, остальные разряды - двоичный код часов. Последовательный импульсный код коррекции передается по двум линиям связи в виде кода единиц и кода нулей. При этом единице кода коррекции соответ- ствует наличие импульса на линии связи кода единиц и отсутствие импульса на линии связи кода нулей, а единице кода коррекции соответствует отсутствие импульса на линии связи кода единиц и наличие им- пульса на линии связи кода нулей.

Импульсы кода единиц и кода нулей поступают на информационный вход преобразователя 6, в котором через элементы И 32, 33 поступают соответственно на входы S и R триггера 34 и на входы элемента ИЛИ 35. На выходе триггера 34 формируется прямой последовательный код коррекции, который поступает на информационный выход пре- образователя 6 и далее на информационные входы регистров 5, 13. На выходе элемента ИЛИ 35 формируется серия тактовых импульсов, которая через элемент 36 задержки поступает на тактовый выход преобразова- теля 6 и далее на тактовый вход регистра 5, на счетный вход счетчика 7 и через элемент И 12 на тактовый вход регистра 13.

Код коррекции записывается в регистры 5, 13. Одновременно счетчик 7 подсчитывает число тактовых импульсов, т.е. число записанных разрядов кода, При поступлении на счетный вход счетчика 7 первого же тактового импульса на выходе дешифратора 8 появляется сигнал логической 1, Счетчик имеет коэффициент пересчета,равный N, При поступлении первых N разрядов кода коррекции (код команды) счетчик 7 обнуляется и на выходе дешифратора 8 появляется сигнал логического О, который запускает формирователь 9. Импульс с выхода формирователя 9 через распределитель 11 (через третий выход) поступает на тактовый вход регистра 14. При этом первые N разря

дов кода коррекции (код команды) переписываются из регистра 13 в регистр 14. Одновременно импульс с выхода формирователя 9 поступает на счетный вход счетчика 10, по срезу которого последний изменяет свое состояние. При этом тактовый вход распределителя 11 подключается к его первому выходу.

Следующие N разрядов кода коррекции записываются в регистры 5,13. По окончании их записи происходит обнуление счетчика 7 и запуск формирователя 9, импульс с выхода которого через распределитель 11 (через первый его выход) поступает на вход R триггера 19. Сигнал логического О с выхода триггера 19 поступает на второй вход элемента И 12, разрешая прохождение тактовых импульсов на тактовый вход регистра 13. При этом код информационной части кода коррекции сохраняется в регистре 13, Импульс с в ыхода формирователя 9 поступает на счетный вход счетчика 10, при этом тактовый вход распределителя 11 подключается к его второму выходу.

На вход код коррекции устройства подается повторный код коррекции, который полностью повторяет первоначально поданный код коррекции. Код коррекции через преобразователь 6 записывается в регистр 5. После записи в регистр 5 первых N разрядов кода коррекции происходит обнуление счетчика 7 и запуск формирователя 9. Импульс с выхода формирователя 9 через распределитель 11 (через второй выход) поступает на вход синхронизации триггера 18, в который по входу D записывается выходной сигнал блока 15. На первые входы блока 15 поступает двоичный код с выходов регистра 14, т.е. двоичный код команды первого кода коррекции. На вторые входы блока 15 поступает двоичный коде выходов разрядов регистра 5, т.е. двоичный код команды повторного кода коррекции. При совпадении кодов команды на выходе блока 15 формируется сигнал логической 1.

Импульс с выхода формирователя 9 поступает также на счетный вход счетчика 10, при этом тактовый вход распределителя 11 подключается к его четвертому выходу.

Следующие N разрядов повторного кода коррекции через преобразователь 6 записываются в регистр 5, вытесняя ранее записанную информацию. По окончании записи происходит обнуление счетчика 7 и запуск формирователя 9. Импульс с выхода формирователя 9 через распределитель 11 (через четвертый выход) поступает на первый управляющий вход преобразователя 6, в котором через элемент ИЛИ 30 (фиг, 3) поступает на вход R триггера 31 Сигнал

логического О с выхода триггера 31 запрещает прохождение сигналов через элементы И 32, 33. При этом запрещается изменение состояния выходов преобразователя б.

Импульс с четвертого выхода распределителя 11 поступает также на второй вход элемента И 20. На третий вход элемента И 20 поступает сигнал с выхода блока 16. На первые входы блока 16 поступает код информации повторного кода коррекции с выходов регистра 5, а на вторые входы - код информации первого кода коррекции с выходов разрядов регистра 13. При их совпадении на выходе блока 16 формируется сигнал логической 1.

В случае совпадения первого и повторного кодов коррекции на первом и третьем входах элемента И 20 присутствуют сигналы логической 1 и импульс с четвертого выхода распределителя 11 проходит через элемент И 20 на вход запуска преобразователя

4и на контрольный выход устройства, свидетельствуя о правильной записи кода коррекции и начале коррекции.

На информационный вход преобразователя 4 поступает двоичный код величины коррекции с выходов старших N-1 разрядов регистра 5. Двоичный код команды с выходов регистра 14 дешифрируется дешифратором 17, управляющие сигналы с выхода которого поступают на управляющие входы преобразователя 4.

Преобразователь 4 (фиг. 2) работает следующим образом.

При коррекции фазы с выхода дешифратора 17 на управляющий вход преобразователя 4 поступают сигналы, обеспечивающие в преобразователе 4 на первом входе элемента И 22 наличие сигнала логического О, а на втором входе элемента И 21 - наличие сигнала логической 1, При этом элементы 22,28,29 заблокированы и на втором, третьем и четвертом выходах преобразователя 4 присутствует сигнал логического О.

На вход запуска преобразователя 4, т.е. на вход предварительной записи счетчика 24 и на второй вход формирователя 25 поступает импульс с выхода элемента И 20. По фронту этого импульса происходит запись в счетчик 24 величины коррекции, поступающей с выходов старших разрядов регистра

5через информационный вход преобразователя 4 на входы записи счетчика 24. При этом на выходе последнего появляется сигнал логической 1, который поступает на первый вход формирователя 25, разрешая формирование на его выходе сигнала управления. Сигнал управления в виде логической 1 появляется на выходе

формирователя 25 по срезу импульса на входе запуска преобразователя 4,

Сигнал управления с выхода формирователя 25 через открытый элемент И 21 поступает на первый выход преобразователя 4. Одновременно сигнал управления разрешает прохождение импульсов, поступающих с выхода блока 2 на вход синхронизации преобразователя 4, через

0 элемент И 23 на вход вычитания счетчика 24. Код, записанный в счетчик 24, начинает считываться. По окончании считывания, когда счетчик 24 обнуляется, на его выходе появляется сигнал логического О, который

5 возвращает формирователь 25 в исходное состояние. При этом на первом выходе преобразователя 4 появляется сигнал логического О и запрещается прохождение импульсов через элемент И 23.

0 Таким образом, на первом выходе преобразователе 4 формируется импульс, длительность которого пропорциональна величине коррекции.

Импульс .с первого выхода преобразо5 вателя 4 поступает на второй управляющий вход блока 2, изменяя его коэффициент деления на К ± 1 в зависимости от знака коррекции, поступающего на первый управляющий вход блока 2 с выхода млад0 шего разряда регистра 5. Это приводит к сдвигу шкалы времени, формируемой блоком 3, на величину

At ±MT; где М - величина коррекции;

5 Т - период повторения импульсов генератора 1.

При коррекции кода времени с выхода дешифратора 17 в соответствии с поданной командой, содержащейся в коде коррекции,

0 на управляющий вход преобразователя 4 поступают сигналы, обеспечивающие в преобразователе 4 на первом входе элемента И 22 сигнал логической 1, а на втором входе элемента И 21 - сигнал логического О. При

5 этом на первом выходе преобразователя 4 поддерживается сигнал логического О.

Аналогично ранее рассмотренному случаю коррекции фазы, импульсом с выхода элемента И 20 производится запуск преоб0 разователя 4, при котором производится запись в счетчик 24 величины коррекции, формирование на выходе блока 25 сигнала управления и считывание кода, записанного в счетчик 24. При этом в преобразователе 4

5 (фиг. 2) импульс с входа запуска через открытый элемент И 22 поступает на второй выход преобразователя 4. Одновременно импульс с входа запуска устанавливает в нулевое состояние триггер 27, сигнал логического О с прямого выхода которого запрещает прохождение сигналов через элемент И 28, а сигнал логической 1 с инверсного выхода разрешает прохождение сигналов через элемент И 29.

Как уже ранее указывалось, код величины коррекции в рассматриваемом случае имеет следующую структуру: младшие п разрядов - двоичный код минут, старшие разряды - двоичный код часов.

По мере считывания кода, записанного в счетчик 24, импульсы с выхода элемента И 23 через элемент И 29 поступают на третий выход преобразователя 4. Выходы младших п разрядов счетчика 24 подключены к инверсным входам элемента И-НЕ 26. При обнулении младших разрядов счетчика 24, т.е. когда код минут величины коррекции считан, на выходе элемейта И-НЕ 26 является сигнал логического О, который устанавливает триггер 27 в единичное состояние. При этом сигнал логического О с его инверсного выхода запрещает прохождение сигналов через элемент И 29, а сигнал логической 1 с прямого выхода разрешает прохождение сигналов через элемент I/I 28.

Код, записанный в счетчик 24, продолжает считываться. При этом импульсы с выхода n-го разряда счетчика 24 через элемент И 28 поступают на четвертый вход преобразователя 4.

По окончании считывания кода, когда счетчик 24 обнуляется, на его выходе появляется сигнал логического П, который возвращает формирователь 25 в исходное состояние. При этом запрещается прохождение импульсов на вход вычитания счетчика 24.

Таким образом, при коррекции кода времени на втором выходе преобразователя 4 формируется импульс, а затем сначала на третьем, а потом на четвертом выходах преобразователя 4 формируются пачки импульсов соответственно минут и часов в соответствии с величиной коррекции.

Импульс с второго выхода преобразователя 4, а такхе пачки импульсов минут и часов с его третьего и четвертого выходов поступают соответственно на вход сброса и на входы установки первой и второй шкал времени делителя 3, при этом сначала происходит сброс кода времени {сброс счетчиков минут и часов), а затем установка нового кода (заполнение счетчиков минут и часов соответстаующими пачками импульсов).

Следующий импульс с выхода делителя 3 поступает на вход установки регистра 14 и обнуляет его. При этом на выходах дешифратора 17 также появляются сигналы логического О1, блокирующие работу преобразователя 4. Одновременно импульс

с выхода делителя 3 поступает на второй управляющий вход преобразователя 6, в котором (см.фиг. 3) через элемент ИЛИ 30 поступает на вход К триггера 31. подтверж- 5 дая его нулевое состояние.

В случае несовпадения любых из частей (код команды или код информации) первого и повторного кодов коррекции на выходе триггера 18 или (и) на выходе блока 16 при10 сутствует сигнал логического О, который запрещает прохождение, импульса через элемент 14 20 на вход запуска преобразователя 4, При этом на контрольном выходе устройства сигнал отсутствует, что свиде15 тельствует об ошибке записи кода коррекции и невозможности проведения коррекции,требуя ее повторения.

В случае, если после подачи импульса на вход ввод коррекции устройства код

0 коррекции по какой-либо причине не может быть подан или подается не полностью, восстановление исходного состояния преобразователя 6 производится импульсом с выхода делителя 3, на котором формируют5 ся импульсы с частотой 1/60 Гц. Этот импульс поступает на второй управляющий вход преобразователя 6, в котором через элемент ИЛИ 30 (фиг. 3) сбрасывает триггер 21. Это налагает ограничения на интервал

0 времени проведения коррекции шкалы времени, которая должна быть завершена до формирования импульса 1/60 Гц на выходе делителя 3.

Формула изобретения

5 Устройство для коррекции шкалы времени, содержащее последовательно соединенные генератор, фазосдвигающий блок и делитель частоты, последовательно соединенные преобразователь кода коррекции и

Q регистр сдвига, выход младшего разряда которого соединен с первым управляющим входом фазосдвигающего блока, тактовой выход преобразователя кода коррекции соединен со счетным входом счетчика, БЫХОТ

5 разрядов которого через дешифраторов со единены с первым входом формирователя одиночных импульсов, второй вход которого соединен с выходом фазосдвигающего блока, последовательно соединенные триггер и 0 первый элемент И, а также второй элемент И, причем вход преобразователя кода коррекции является информационным входом устройства, отличающееся тем, что, с целью повышения помехоустойчивости, в

5 него введены последовательно соединенные дополнительный счетчик, распределитель сигналов и дополнительный триггер, последовательно соединенные дополнительный регистр сдвига, регистр, дополнительный дешифратор и преобразователь

кода, а также первый и второй блоки сравнения кодов, при этом информационный вход дополнительного регистра сдвига соединен с информационным выходом преобразователя кода коррекции, тактовый выход которого через второй элемент И соединен с тактовым входом дополнительного регистра сдвига, выход формирователя одиночных импульсов соединен со счетным входом дополнительного счетчика и с входом распределителя сигналов, второй выход дополнительного счетчика и с входом распределителя сигналов, второй выход которого соединен с установочным входом триггера, третий выход распределителя сигналов соединен с тактовым входом регистра, а четвертый выход распределителя сигналов соединен с первым управляющим входом преобразователя кода коррекции и с вторым входом первого элемента И, выход которого соединен с входом запуска преобразователя кода, первый выход которого соединен с вторым управляющим входом фазосдвигающего блока, выход которого соединен с входом сигнала синхронизации преобразователя кода, другие выходы которого соединены с входом сброса и с входами установки первой и второй шкалы времени делителя частоты, выход которого соединен

с вторым управляющим входом преобразователя кода коррекции и с входом установки регистра, выходы разрядов которого соединены с входом триггера через первый блок

сравнения кодов, другие входы которого соединены с выходами соответствующих разрядов регистра сдвига и с первой группой входов второго блока сравнения кодов, причем выходы соответствующих разрядов регистра сдвига за исключением младшего разряда соединены с информационными входами преобразователя кода, управляющие входы которого соединены с выходами дополнительного дешифратора, выходы

разрядов дополнительного регистра сдвига соединены с второй группой входов второго блока сравнения кодов, выход которого соединен с третьим входом первого элемента И, а выход дополнительного триггера соединен с вторым входом второго элемента И, причем входы установки счетчика и дополнительного счетчика, третий управляющий вход преобразователя кода коррекции и второй вход установки дополнительного

триггера соединены между собой и являются входом управляющего сигнала устройства, выходом контрольного сигнала которого является выход первого элемента И,

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

Авторы

Даты

1992-12-15—Публикация

1991-02-06—Подача