( 54) АДАПТИВНЫЙ ВРЕМЕННОЙ : ДИСКРЕТИЗЛТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный временной дискретизатор | 1978 |

|

SU721826A1 |

| Адаптивный временной дискретизатор | 1977 |

|

SU696483A2 |

| Адаптивный временной дискретизатор | 1976 |

|

SU570059A1 |

| Адаптивный временной дискретизатор | 1978 |

|

SU777657A1 |

| Адаптивный временной дискретизатор | 1975 |

|

SU542339A2 |

| Адаптивный временной дискретизатор | 1978 |

|

SU746914A1 |

| Телеизмерительная система | 1978 |

|

SU734786A1 |

| Устройство для адаптивной дискретизации | 1979 |

|

SU851416A1 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| Адаптивный временной дискретизатор | 1977 |

|

SU680015A1 |

Изобретение относится к технике дискретизации непрерывных сигналов.

По основному авт. св. № 394800 известен адаптивный временной дискретизатор в котором определение отклонения сигнала от прямой линии осуществляется срав нением разности текущего и начального .значений сигнала с величиной, полученной инерционным (дифференциальным или интегральным) преобразованием этой разности, Он содержит измерительный элемент, соединенный по. входу с блоком памяти, а по выходу с блоком управления и блоком сравнения, и блок выборки сигнала, соединенный с блоком памяти и блоком управления.

Однако известное устройство обладает малой эффективностью при адаптивной дискретизации нестационарных сигналов, в которых относительно короткие интервалы активного сигнала чередуются с достаточно длительными интервалами, значение сигнала которых практически не меняется. Применение такого устройства приводит-к появлению избыточных отсчетов на участках меленного изменения сигнала, т, е. к снижению 5|ффективности адал№ивной дискретизации что обусловлено переходом блока управления в режим насыщения.

Целью изобретения является повышение

эффективности работы адаптивных дискрети- заторов и повышение помехоустойчивости измерений погре:шгости линейной annpoKCjiMaции входного непрерывного сигнала.

Для этого дискретизатор содержит электронный ключ, триггер и второй блок сравнения, при этом выход электронного ключа соединен с входом блока управления, с перьвыми входами блока памяти, блока выборки сигнала, первого блока сравнения и тригге-

ра, первый вход электронного ключа подключен к выходу первого блока сравнения, а второй вход - через триггер к выходу второго блока сравнения, вход которого соединен с первым входом измерительного элемента. Кроме того, первое плечо мостовой схемы измерительного элемента содержит управляемый резистор и конденсатор постоянной емкости, а другое плечо - управляемый ре.зистор и два последовательно соедяненн

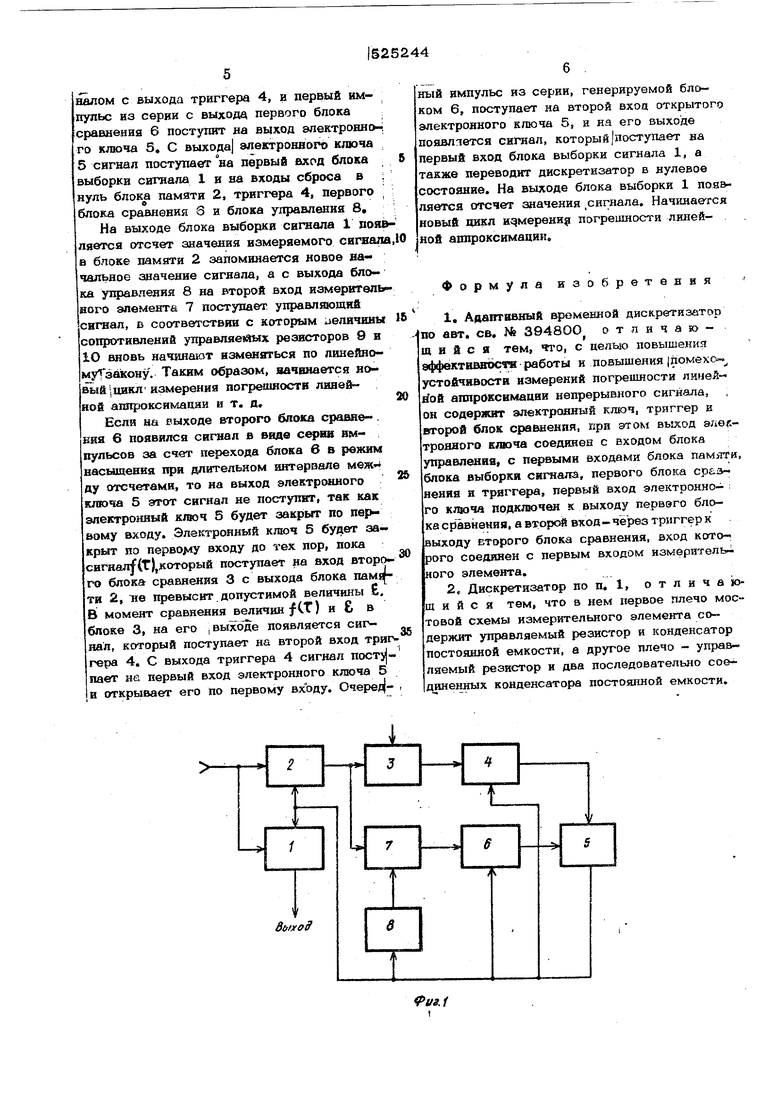

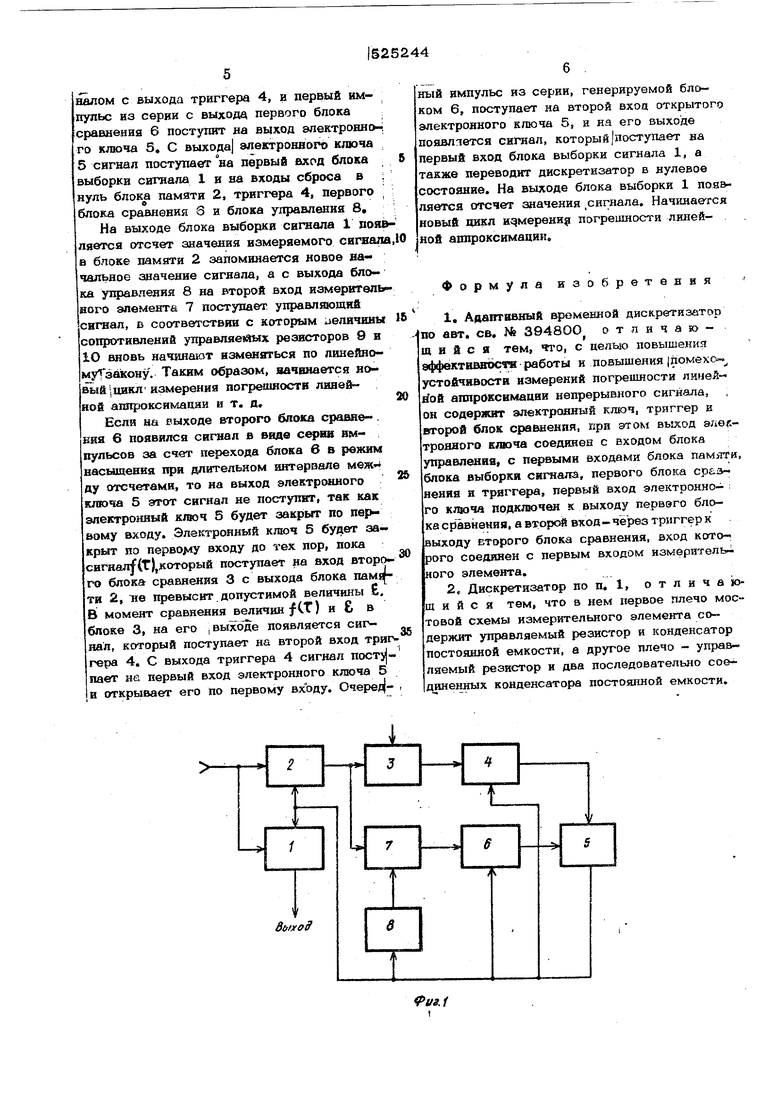

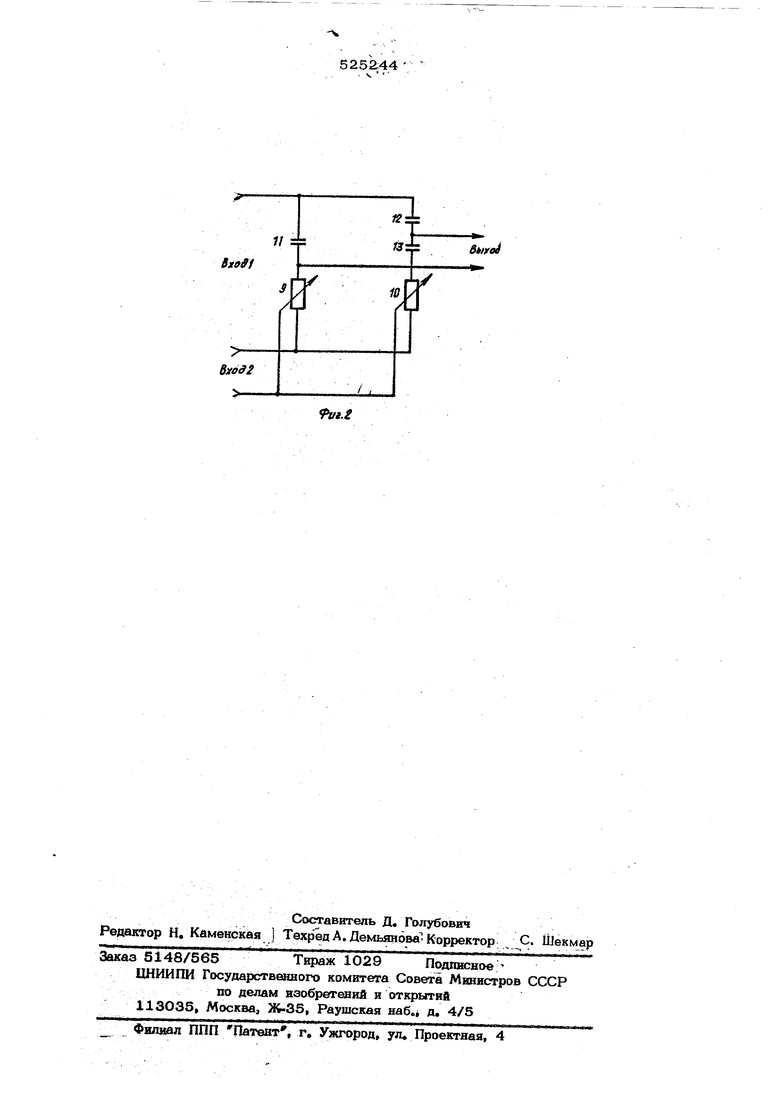

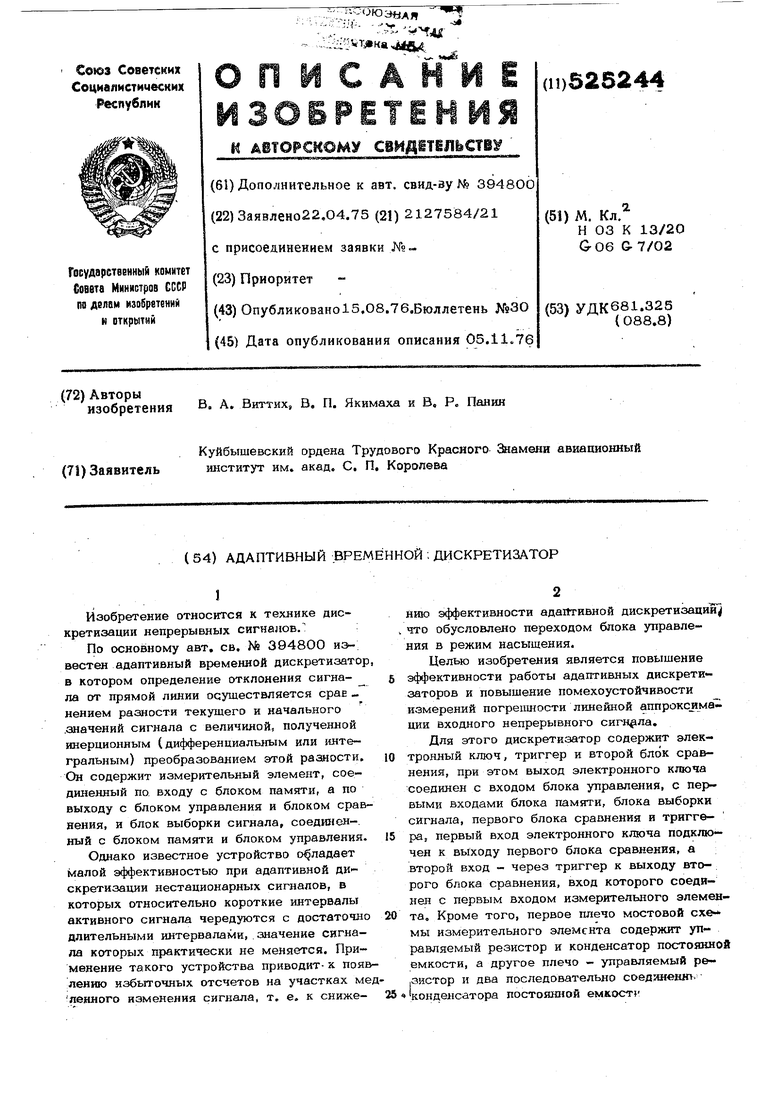

конденсатора постоянной емкост}На фиг, i Т1риведф1а структурная схема дискретизатора, на фиг, 2 - электрическая рхема измерительного элемелта, I Адаптивный временной дискретизатор со держит блок выборки сигнала 1, выход ко- ; toporo служит выходом ;дискретизатора; I блок памяти 2, второй аход которого соединен со вторым входом блока 1 и со входом; дискр& тийатора; второй блок сравнения 3, вход Г которого соединен с выходом блока памяти 2; триггер 4, второй вход которого сое динен С выходом блока 3; электронный ключ 5, выход, которого соединен с первыми вхогдами блока памяти 2, блока выборки сищада 1 и триггера 4, а второй вход соединеа р выходом триггера 4; первый блок срав- . ения 6, выход которого соединен с первым (одом электронного ключа 5, а первый сод соединен с выходом электронного 5; измерительный элемент 7, выход ко торого соединен со вторым входом блока сравнения 6, а первый вход соединен с вы- ходом блока памяти 2; блок управления 8, |вход которого соединен с выходом электронного ключа 5, а выход соединен со вторым; ВХОДОМ иет 1еритвльного элемента 7,, j Измерителпьный элемент 7 представляет робой мост, состоящий из идентичнь1х1 уп)равляемых резисторов 9 и 1О, управляюШие входы которых объединены и являются Ьторым входом измерительного элемента, и конденсаторов постоянной емкости 11, 12 и 13. Отношение величины емкости конденсатора 13 к величине емкости конденсатора |.2 равно двум; посто5шная времени цепи, гостояшей из управляемого резистора 9 к шнденсатора 11, изменяется линейно во вре мени с угловым коэффициентом, равным едизние, а постоянная времени цепи, состоящей ИЗ управляемого резистора 1О и последовательно соединенных конденсаторов 12 и 13 также изменяется во времени линейно с уг10ВЫМ коэффициентом, равным 1/3. Работает дискретизатор следящим образом. В начальный момент времени (Т О) в 5лбке памяти 2 запоминается начальноезначение сигнала S (0), которое вычитается Из последующих текущих значений сигнала ;й(Т)тр есть с выхода блока памяти 2 сиг рал/( SCO) будет поступать на вход второго блока сравнения 3 и первый вход Измерительного элемента 7.. I При сравнении сигнала f.( блоке 3 с допустимой величилой которая определяе Ся исходя из допустимой погрешности аппрок Симации, с выхода блока 3 поступает сигнал на второй вход триггера 4. С выхода тригpopii 4 сигнал поступает на перЕцлй: вход ектронного ключа 5 и открывает его по 1ервг му входу. Сигнал (tic выхода блока памяти 2 посупает на первый вход измерительного эле- ента 7. Напряжение Исц «а конденсаторе момент времени t будет равно: fffl-Uc.. JLSwr 4 н (Т) Ус СГ;-я,(г).а)ПГ)| ак как по услрвию RgCT)-, , то c., деТ - TeKymeei заачеиле времени; 0,tj - интервал дискретизации. Аналогично, учитывая, что по условию Таквм образом, j напряжение i Ifg в диа-{ .оналя мостовой схемы будет равно: . t : и:« Jr fCDdV-f ((t)Lt Если /(Т)изменяется (( Ue Kf 2)TMt-Mat.o t о (То есть, если сигнал есть прямая лннвя, т ; Напряжение на выходе измерительного 1 мента равно нулю. На фнжение на выходе измерительного элемента будет (отдигтаым 1хуг нуля в двух случаях: когда сигнаА $ (if) склоняется от прямой, и когда закон иэменения сопротивления управляемых резистс | ров в измерительном элементе 7 начинает очличаться от линейного в результате перехода блока управления 8 в режим насыщения, что происходит при длительном интервале между отсчетами значений сигнала, Пря этом отличное ОТ нуля напря)кение с выхода нэмерительного элемента t поступает на второй вход первого сравнения 6, При, сравнении этого напряжения с допустимой величиной, которая определяется исходя из ; допустимой погрещности аппроксимации, с выхода первого блока сравнения 6 на второй вход электронного ключа 5 поступает сигнал в виде серии импульсов. .Если импульсный сигнал на выходе блока 6 появился за счет отклонения сигнала fi(t)OT прямой, то к этому моменту времени электронный 1ключ 5 будет открыт по первому аходу сигвалом с выхода триггера 4, в первый импульс из серии с выхода первого блока сравнения 6 поступит на выход электровнсиго ключа 5. С выхода электронного ключа 5 сигнал поступает °на первый вход блока выборки сигнала 1 в на входы сброса в нуль блок памяти 2, триггера 4, первого блока сравнения 3 и блока управления 8, На выходе блока выборки сигнала 1 nosiB лявтся отсчет значения измеряемого сигнал в блоке памяти 2 запоминается новое на« чальное значение сигнала, а с выхода блока управления 8 на второй вход измеритель ного элемента 7 поступает управляющий сигнал, в соответствии с которым величины сопротивлений управляемых резисторов 9 и 1О вновь начинают изменяться по линейному закону. Таким образом, З1ачвнается новь1й,ЦИКЛизмерения погрешности лнне ной аппроксимации и т. д. Если на выходе второго блока сравяе-, ния 6 появился сигнал в вцве серая ом- ; пульсов за сче1 перехода блока в в режим насыщения при длительном интервале ду отсчетами, то на выход электронного ключа 5 этот сигнал не поступит, так как электронный ключ 5 будет закр1ыт по первому входу. Электронный кгаоч 5 закрыт по пepвo y входу до тех пор, пока сигнал(Т),соторый поступает на вход второго блока сравнения 3 с выхода блока пам$ ти 2, тяе превысит, допустимой величины . В момент сравнения величин fCT) и 6 в блоке 3, на его , выходе появляется сигнал, который поступает на второй вход триг гера 4. С выхода триггера 4 сигнал пост; пает Ни первый вход электронного ключа Б и открывает его по первому вхЪду. Очере ный импульс из серии, генерируемой блоком 6, поступает на второй вход открытого электронного ключа 5, и на его выходе появляется сигнал, который )поступает на первый вход блока выборки сигнала 1, а также переводит дискретизатор в нулевое состояние. На выходе блока выборки 1 появляется отсчет значения сигнала. Начинается новый цикл и мерени погрешности линейной аппроксимации Формула изобретения 1,Адаптивный временной дискретизатор по авт. ев, № 394800 отличающийся тем, 4VO, с целью повышения аффектвБоостн работы к повышения j помехе. устойчивости измерений погрешности линей ой аппроксимации непрерывного сигнала, он содержит электронный ключ, триггер и второй блок сравнения, при этом выход элег.тронного ключа соединен с входом блока управления с первыми входами блока памяти, блока выборки сигнала, первого блока нения н триггера, первый вход электронного ключа подключен к выходу перввго блоквср1 внения, авторой вход-через триггер к выходу второго блока сравнения, вход которого соединен с первым входом измеритель ного элемента, 2.Дискретизатор поп, 1, отличающийся тем, что в нем первое плечо мостовой схемы измерительного элемента содержит управляемый резистор и конденсатор постоянной емкости, а другое плечо - управляемый резистор и два последовательно соед енных конденсатора постошшой емкости.

II ф

4:

&иуо

ff

Авторы

Даты

1976-08-15—Публикация

1975-04-22—Подача