1

Изобретение относится к области автоматики- и вычислительной техники, в частч кости к устройствам для дискретизации непрерывных сигналов.

Известен адаптивный временной дискретиэатор LUi содержащий блок выборки данных, блок памяти, вычитатели, делитель, ограничитель, интегратор, блок сравнения, триггер, пороговый элемент, генератор пилообразного напряжения и элемент ИЛИ.

Известен также аоаптивный временный дискретизатор С2, содержащий блок выборки данных, блок памяти, блок управления, блоки сравнения, ключ, триггер и измерительный элемент, включающий в себя узлы параметрического интегрирования.

В этих дискретизаторах оценка погрешности кусочно-линейной аппроксимации определяется путем сравнения разности между текущим значением сигнала и его запомненным предыдущим значением с велиЧиной, полученной после некоторого динамического преобразования этой разности

по выбранному алгоритму. Обшим недостатком устройства является пониженная помехоустойчивость.

Наиболее близким к изобретению является адаптивный временной дискретизатор 3, содержащий блок выборки сигнала, подключенный выходом к выходу дискретизатора, сигнальным входом - ко входу дискретизатора,а управляющим входом к выходу блока сравнения и входу блока управления, выход которого соединен с первым входом первого блока параметрического интегрирования, второй вход которого подключен через блок памяти к входу дискретизатора. Блок параметрического интегрирования входит в состав измерительного элемента, подключенного выходом к входу блока сравнения.

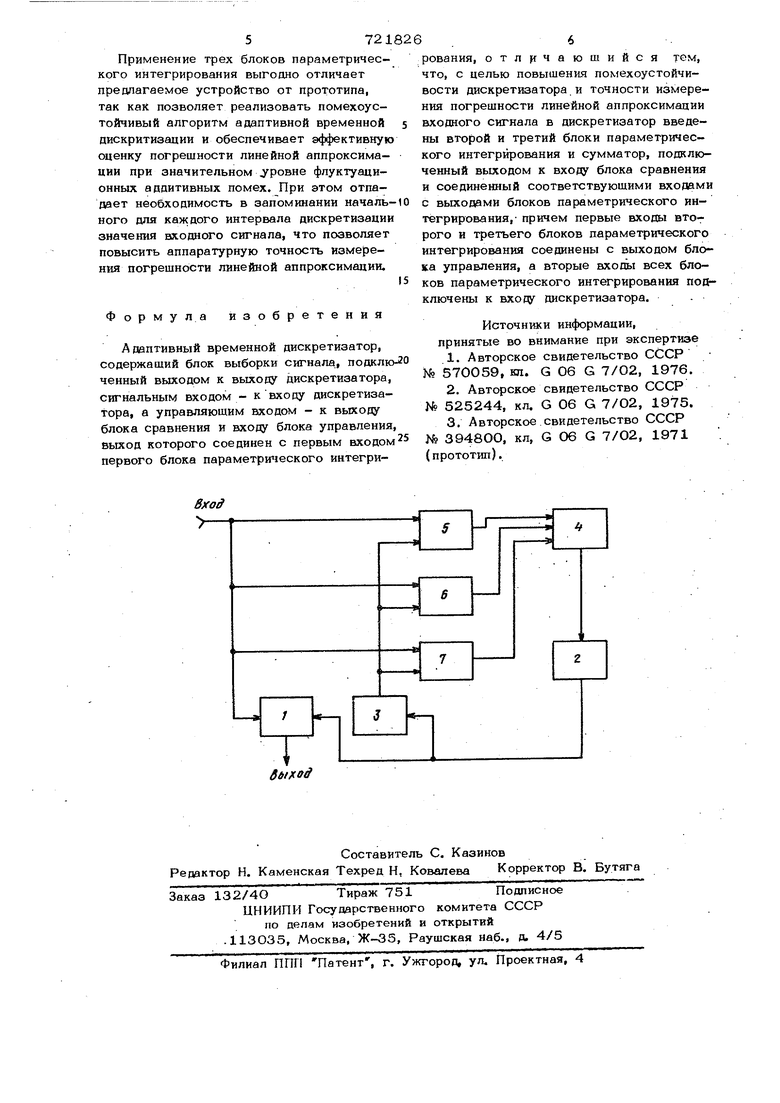

Недостатком такого устройства является низкая помехоустойчивость, которая в случае адаптивной дискретизации сигналов содержащих высокочастотную флуктуационную составляющую помех, приводит к снижению точности измерения погрешности аппроксимации сигнала и уменьшению коэффициента сжатия, а слецовательно, к снижению эффективности адаптивной дискретизации. Наличие в дискретизаторе блока naMfltH также приводти к появлению дополнительной аппаратурной ошибки измерения погрешности аппроксимации. Целью изобретения является повышение помехоустойчивости дискретизатора и точности измерения погрешности линейной аппроксимации входного сигнала. С этой целью в адаптивный временной дискретизатор, содержащий блок выборки сигнала, подключенный выходом к выходу дискретизатора, сигнальным входом - к входу дискретизатора, с управляющим входом - к выходу блока сравнения и входу блока управления, выход которого соединен с первым входом первого блока параметрического интегрирования, введены вто рой и третий блоки параметрического интегрирования и сумматор, подключенный выходом к входу блока сравнения и соединенный соответствующими входами с выхо дами блоков параметрического интегрирования, причем первые входы второго и третьего блоков параметрического интегри рования соединены с выходом блока управ ления, а вторые входы всех блоков параметрического интегрирования подключены к входу дискретизатора, На чертеже показана блок-схема предлагаемого дискретизатора. А даптивный временной дискретизатор содержит блок выборки сигнала 1, подключенный выходом к выхору дискретизатора, сигнальным входом - к входу дне- кретизатора, управляющим входом к выходу блока сравнения 2 и входу блока управления 3. Вход блока сравнения 2 соединен с выходом сумматора 4, соответствующие входы которого подключены к выходам первого, второго и третьего блоков параметрического интегрирования 5, 6 и 7. Первые входь блоков интегрирования 5, 6 и7 соединены с выходом блока управления 3, а вторые входы блоков 5, 6 и 7 подключены к, входу дискретизатора. Дискретизатор работает следующим образом. В начальный момент времени (t О ) вхорной сигнал SCt) поступает на сигнальный вход блока выборки сигнала 1 и вторые входы блоков интегрирования 5, 6 и 7. Блоки параметрического интегрирования 5, 6 и 7, служащие для преобразования г.игнала о (.i),образованы делителями напряжения; каждый из которых содержит правляемый резистор и конденсатор потоянной емкости. Постоянная времени епи, состоящей из конденсатора и управяемого резистора, изменяется линейно о времени с коэффициентом равным /т +1, то есть K.tj ,:;;;7i ем пл г 1 для первого блока интегрироания 5, -т 2 для второго блока 6, - третьего блока 7. Напряжение на выходе каждого блока араметрического интегриро вания 5, 6 и7 напряжение на конденсаторе) в момент ремени i определяется выражением )dt, где С - переменная интегрирования. Входной сигнал S (i:) преобразованный в блоках 5, 6, 7, далее суммируется в сумматоре 4 с масщтабными коэффициентами, равными 1,5; -4 и 2,5 соответственно для выходных напряжений первого, второго и третьего блоков параметрического интегрирования. Таким образом, на выходе сумматора 4 формируется оценка погрешности кусочно-линейной аппроксимации сигнала ), равная (t6ct)dit-4l ( )аС4. t -/оt - о (.t)dlt. в частности, если входной сигнал изменяется линейно, т.е. Stt) SCo)K.t, где Offf - начальное для данного интервала дискретизации значение входного сигнала, k const, то напряжение на выходе сумматора 4 будет равно нулю. Если же входной сигнал изменяется нелинейно, то на выходе сумматора 4 будет формироваться отличное от нуля напряжение, которое поступает на вход блока сравнения 2, где сравнивается с величиной допустимой погрешности аппроксимации .В момент времени Т, когда значение U станет равным с выхода блока сравнения 2 поступает сигнал на управляющий вход блока выборки сигнала 1 и на вход сброса в нуль блока управления 3. На выходе блока выборки 1 появляется отсчет значения сигнала и начинается новый цикл измерения погрешности линейный аппроксимации.

Применение трех блоков параметрического интегрирования выгодно отличает предлагаемое устройство от прототипа, так как позволяет реализовать помехоустойчивый алгоритм адаптивной временной дискритизации и обеспечивает эффективную оценку погрешности линейной аппроксимации при значительном уровне флуктуационных аддитивных помех. При этом отпадает необходимость в запоминании начального для каждого интервала дискретизации значения входного сигнала, что позволяет повысить аппаратурную точность измерения погрешности линейной аппроксимации,

Форму да изобретения

Адаптивный временной дискретизатор, содержащий блок выборки сигнала., подклк ченный выходом к выходу дискретизатора, сигнальным входом - квходу дискретизатора, а управляющим входом - к выходу блока сравнения и входу блока управления, выход которого соединен с первым входом первого блока параметрического интегрирования, отличающийся тем, что, с целью повышения помехоустойчивости дискретизатора и точности измерения погрещности линейной аппроксимации входного сигнала в дискретизатор введены второй и третий блоки параметрического интегрирования и сумматор, подключенный выходом к входу блока сравнения и соединенный соответствующими входами с вькодами блоков параметрического интегрирования,- причем первые входы второго и третьего блоков параметрического интегрирования соединены с выходом блока управления, а вторые входы всех блоков параметрического интегрирования подключены к входу дискретизатора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 570059, KJ1. G 06 G 7/О2, 1976.

2.Авторское свидетельство СССР № 525244, кл, G 06 G 7/О2, 1975.

3.Авторское свидетельство СССР № 394800, кл, G Об G 7/02, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный временной дискретизатор | 1975 |

|

SU525244A2 |

| Адаптивный временной дискретизатор | 1976 |

|

SU575770A1 |

| Адаптивный временной дискретизатор | 1976 |

|

SU577668A1 |

| Адаптивный временных дискретизатор | 1974 |

|

SU660239A1 |

| Адаптивный временной дискретизатор | 1977 |

|

SU680015A1 |

| Адаптивный временной дискретизатор | 1981 |

|

SU1005301A2 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| Адаптивный временной дискретизатор | 1976 |

|

SU570059A1 |

| Адаптивный временной дискретизатор | 1978 |

|

SU777657A1 |

| Адаптивный временной дискретизатор | 1988 |

|

SU1658187A1 |

Авторы

Даты

1980-03-15—Публикация

1978-02-01—Подача