Изобретение относится к устройствам обработки (квантования по времени) электрических сигналов и может быть использовано в устройствах, регистрирующих параметры, которые используются в процессе дальнейшего анализа для восстановления исходной зависимости.

Известен дискретизатор непрерывных сигналов, содержащий блок выборки сигнала, блок памяти, блок сравнения, измерительный элемент и блок управления.

Недостатком данного устройства является низкая точность аппроксимации из-за линейного ее характера.

Наиболее близким к предложенному (прототипом) является адаптивный временной дискретизатор квантования по времени электрических сигналов, содержащий соединенные последовательно первый блок памяти, блок определения приращений, пороговый элемент, блок выборки-хранения, информационный вход которого является входом дискретизатора, второй блок

памяти, генератор пилообразного напряжения, ключ, три блока умножения, сумматор, компаратор, счетчик и два масштабирующих элемента, при этом вход дискретизатора соединен с запускающим входом генератора пилообразного напряжения и через ключ с информационным входом первого запоминающего элемента, выход генератора пилообразного напряжения соединен с информационным входом второго запоминающего элемента и с первым входом компаратора, выход второго запоминающего элемента соединен с первым входом первого блока умножения и через первый масштабный элемент с первым входом второго блока умножения, второй вход которого подключен к выходу счетчика, а выход - к первому и второму входам третьего блока умножения и к первому пходу сумматора, .выход, третьего блока умножения соединен через второй масштабирующий элементе вторым входом сумматора, сыход которого соединен с вторым входом первого

со С

ю

|5

ГО

|Ю

(5 - y(tn+i)-ai(tn+ r )2-a2(tn+ т)-аз , (8)

где tn - момент регистрации n-ro значения сигнала,

y(tn+1) - текущее значение сигнала, поступающего в дискретизатор.

В момент выполнения неравенства

,

где е-заданная погрешность аппроксимации сигнала, выдается команда на осуществление регистрации сигнала. В случае, когда неравенство (9) не выполняется, регистрация осуществляется с максимально возможной длительностью интервала дискретизации, равной периоду развертки гене- ратора пилообразного напряжения.

Цель изобретения достигается тем, что адаптивный временной дискретизатор, содержащий блок выборки-хранения, выход которого является выходом дискретизато- ра, а информационный вход подключен к информационному входу дискрётизатора и входу запуска генератора пилообразного напряжения, соединенного выходом с первым входом компаратора и информационным входом запоминающего элемента, подключенного управляющим входом к выходу порогового элемента, а выходом - к первому входу первого блока умножения и входу масштабирующего элемента, выход которого соединен с первым .входом второго блока умножения, подключенного вторым входом к выходу счетчика отсчетов, а выходом - к входу первого квадратора и первому входу первого сумматора, подключенного вторым входом через второй масштабирующий элемент к выходу квадратора, а выходом - к второму входу первого блока умножения, соединенного выходом с вторым входом компаратора дополнительно включает в свой состав второй квадратор, три блока возведения в степень, семь блоков осреднения, счетчик времени дискретизации, блок вычитания по модулю, шесть блоков памяти, с третьего по семнадцатый блока умножения, второй и третий сумматоры, одиннадцать блоков деления, одиннадцать блоков вычитания, тридцать один элемент задержки, коммутатор и ключ, подключенный информационным входом к выходу генератора пилообразного напряжения, а выходом - к первому информационному входу коммутатора, соединенного вторым ин- формационным входом с выходом компаратора, а выходом - входу счетчика отсчетов, входу обнуления счетчика времени дискретизации, управляющему входу

блока выборки-хранения и входам управления записью с первого по шестой блоков памяти; причем управляющие входы ключа и коммутатора соединены с выходом поро- 5 гового элемента, выход блока выборки-хранения подключен к информационному входу первого блока памяти, соединенного выходом с первым входом первого блока осреднения, первым входом третьего блока

10 умножения и информационным входом вто- рого блока памяти, выход которого подключен к второму входу первого блока осреднения, первому входу четвертого блока - умножения и информационному входу треть15 его блока памяти, соединенного выходом с третьим входом первого блока осреднения и первым входом пятого блока умножения, причем выход генератора пилообразного напряжения подключен к первому входу второго

20 сумматора и информационному входу четвертого блока памяти, выход которого соединен информационным входом пятого блока памяти, первым входом второго блока осреднения, входом первого блока возведения в

25 степень, вторым входом третьего блока умножения и входом первого элемента задержки, подключённого выходом к первому входу шестого блока умножения, соединенного вторым входом с выходом третьего

30 блока умножения, причем выход пятого блока памяти подключен к информационному входу шестого блока памяти, второму входу второго блока осреднения, входу второго блока возведения в степень, второму входу

35 четвертого блока умножения и входу второго элемента задержки, соединенного выходом с первым входом седьмого блока .умножения, подключенного вторым входом к выходу четвертого блока умножения, при40 чем выход шестого блока памяти соединен с третьим входом второго блока осреднения, входом третьего блока возведения в степень, вторым входом пятого блока умножения и входом третьего элемента задерж45 ки, подключенного выходом к первому входу восьмого блока .умножения, соединенного вторым входом с выходом пятого блока умножения, причем первый, второй и третий блоки возведения в степень подклю50 чены выходами сигналов второй степени к соответствующим входам третьего блока осреднения, выходами сигналов третьей степени - к соответствующим входам четвертого блока осреднения, а выходами

55 сигналов четвёртой степени - к соответствующим входам пятого блока осреднения, при этом входы шестого блока осреднения соединены с выходами третьего, четвертого и пятого блоков умножения, входы седьмого блока осреднения подключены к выходам

шестого, седьмого и восьмого блоков умножения, выход второго блока осреднения через четвертый элемент задержки соединен с первым входом девятого блока умножения, выход третьего блока осреднения подключен к входам элементов задержки с пятого по девятый, выход пятого элемента задержки соединен с входами делителя первого и второго блоков деления, выход шестого элемента задержки подключен к входу уменьшаемого первого блока зычитания, выход седьмого, элемента задержки соединен с входом делителя третьего блока деления и через десятый элемент задержки - с входом уменьшаемого второго блока вычитания, подключенного входом вычитаемого к выходу третьего блока деления, выход восьмого элемента задержки соединен с первым входом десятого блока умножения, выход девятого элемента задержки подключен к первому входу одиннадцатого блока умножения, выход четвертого блока осреднения соединен с входами элементов задержки с одиннадцатого по пятнадцатый, выход одиннадцатого элемента задержки подключен к входу делителя четвертого бло- ка деления,, выход двенадцатого элемента задержки соединен с входом уменьшаемого третьего блока вычитания, выход тринадца-. того элемента задержки подключен к входу делителя пятого блока деления, соединенного выходом с входом вычитаемого первого блока вычитания, а входом делимого - с выходом девятого блока умножения и входом делимого второго блока деления.,.подключенного выходом к входу вычитаемого третьего блока вычитания, выход четырнадцатого элемента задержки соединен с входом делителя шестого блока деления и через шестнадцатый элемент задержки - с входом уменьшаемого четвертого блока вычитания, подключенного входом вычитаемого к выходу шестого блока деления, соединенного входом делимого с выходом десятого блока умножения, выход пятнадцатого элемента задержки подключен к первому входу двенадцатого блока умножения, выход пятого осреднения соединен с входом делимого: третьего блока деления, вторыми входами девятого и десятого блоков умножения, первыми входами тринадцатого и четырнадцатого блоков умножения и входом семнадцатого элемента задержки, подключенного выходом к входу делителя седьмого блока деления, выход шестого блока осреднения через восемнадцатый элемент задержки соединен со вторым входом тринадцатого блока умножения, подключенного выходом к входу делимого четвертого блока деления, соединенного

выходом с входом вычитаемого пятого блока вычитания, выход седьмого блока осреднения подключен к входам элементов задержки с девятнадцатого по двадцать

первый, выход девятнадцатого элемента задержки соединен с входом уменьшаемого пятого блока.вычитания, выход двадцатого элемента задержки подключен к входу уменьшаемого шестого блока вычитания,

выход двадцать первого элемента задержки соединен с входом уменьшаемого седьмого блока вычитания, выход первого блока осреднения подключен через двадцать второй элемент задержки к второму входу четырнадцатого блока умножения, соединенного выходом с входом делимого первого блока деления, подключенного-выходом к входу вычитаемого шестого блока вычитания, выход которого-соединен с входом делимого

восьмого блока деления, подключенного входом делителя к выходу третьего блока вычитания и входу делителя девятого блока деления, а выходом - к входу вычитаемого восьмого блока вычитания, соединенного

выходом с входом делимого десятого блока деления, а. входом уменьшаемого - через, двадцать третий элемент задержки к выходу. пятого блока вычитания и входу двадцать четвертого элемента задержки, соединенного выходом с входом вычитаемого девятого блока вычитания, подключенного выходом к входу делимого одиннадцатого блока деления, а входом уменьшаемого - к выходу пятнадцатого блока умножения, соединенного первым входом через двадцать пятый элемент задержки, с выходом первого блока вычитания и входом двадцать шестого элемента задержки, подключенного выходом к входу уменьшаемого десятого

блока вычитания, соединенного выходом с входом делителя десятого блока деления, а входом вычитаемого - с выходом девятого блока деления; подключенного входом делимого через двадцать седьмой элемент за5 держки к выходу второго блока вычитания, причем выход четвертого блока вычитания через двадцать восьмой элемент задержки соединен с входом делителя одиннадцатого блока деления, выход которого подключен к

0 входу двадцать девятого элемента задержки и второму входу двенадцатого блока умножения, соединенного выходом с входом вычитаемого одиннадцатого блока вычитания, подключенного выходом к входу дели5 мого седьмого блока деления, а входом уменьшаемого - через тридцатый элемент задержки к выходу седьмого блока вычитания, соединенного входом вычитаемого с выходом одиннадцатого блока умножения.

jnoflKflK)4eHHoro вторым входом к выходу десятого блока деления, второму входу пятнадцатого блока умножения и входу тридцать первого элемента задержки, выход которого соединен с первым входом третьего сумматора, подключенного вторым и третьим входами к выходам шестнадцатого и семнадцатого блоков умножения соответственно, а выходом - к входу вычитаемого блока вычитания по модулю, соединенного выходом с входом порогового элемента, а входом уменьшаемого-с информационным входом дискретизатора и входом запуска счетчика времени дискретизации, подключенного гвыходом к второму входу второго сумматора, выход которого соединен с в хо- дом второго квадратора и первым входом шестнадцатого блока умножения, подключенного вторым входом к выходу двадцать девятого элемента задержки, а выход второго квадратора соединен с первым входом семнадцатого, блока умножения, подключенного вторым входом к выходу седьмого блока деления.

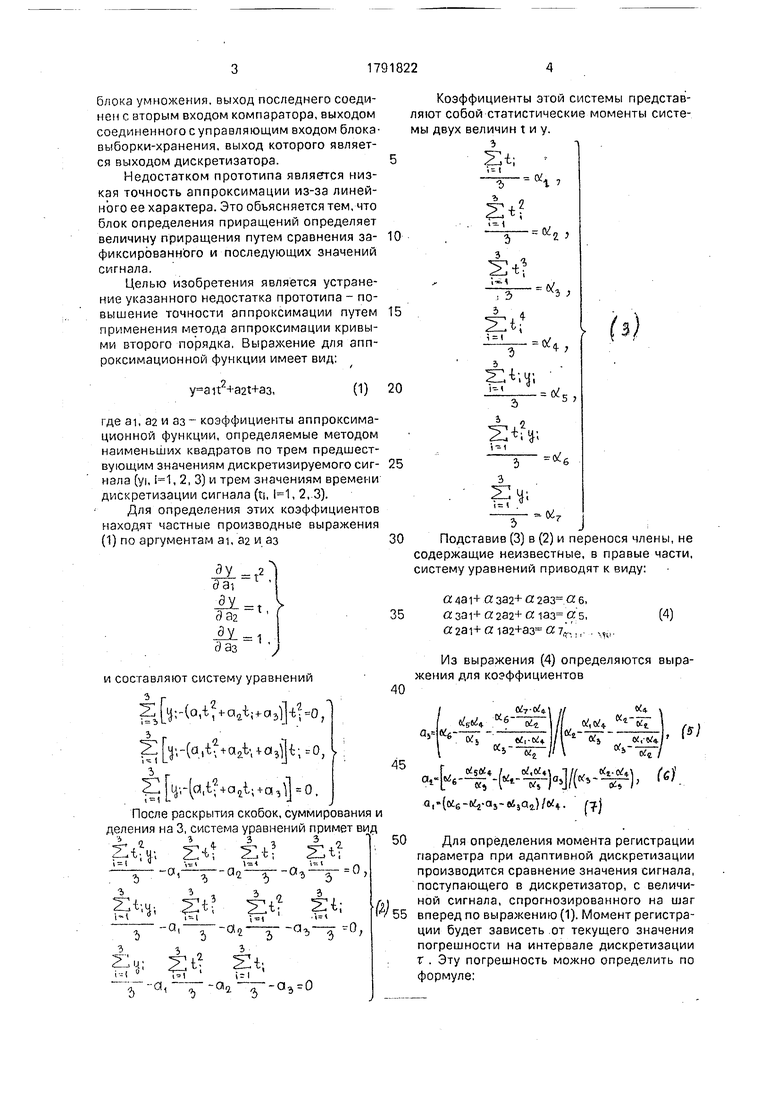

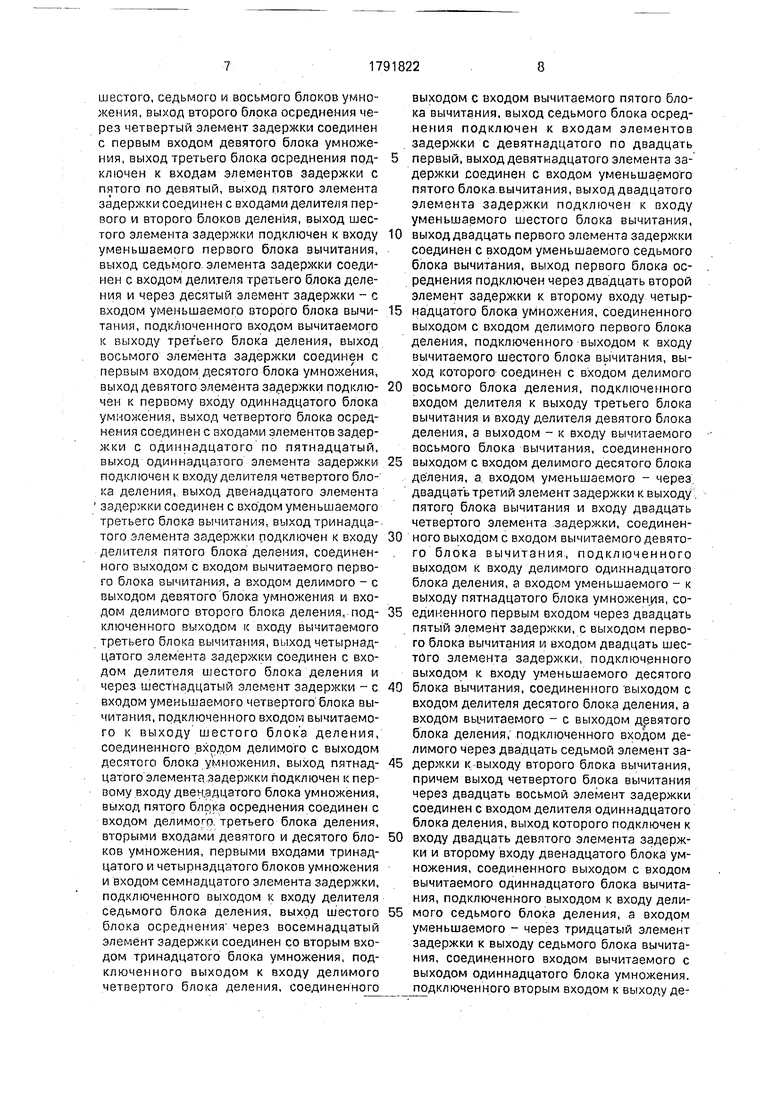

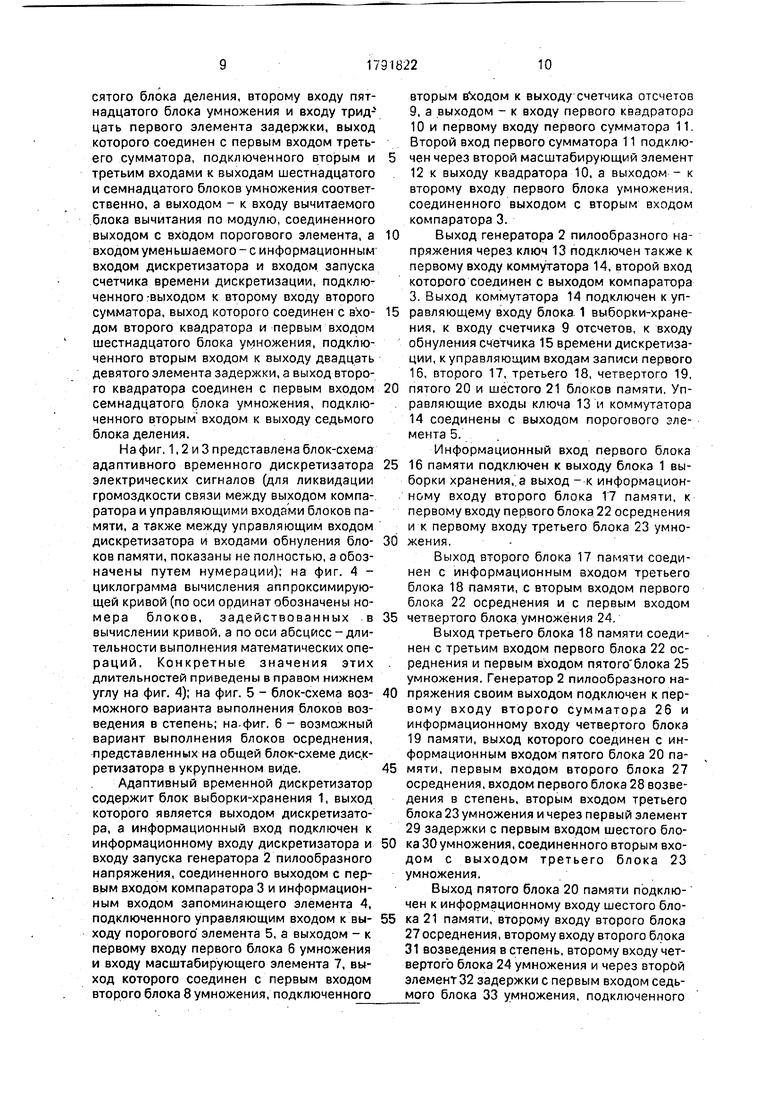

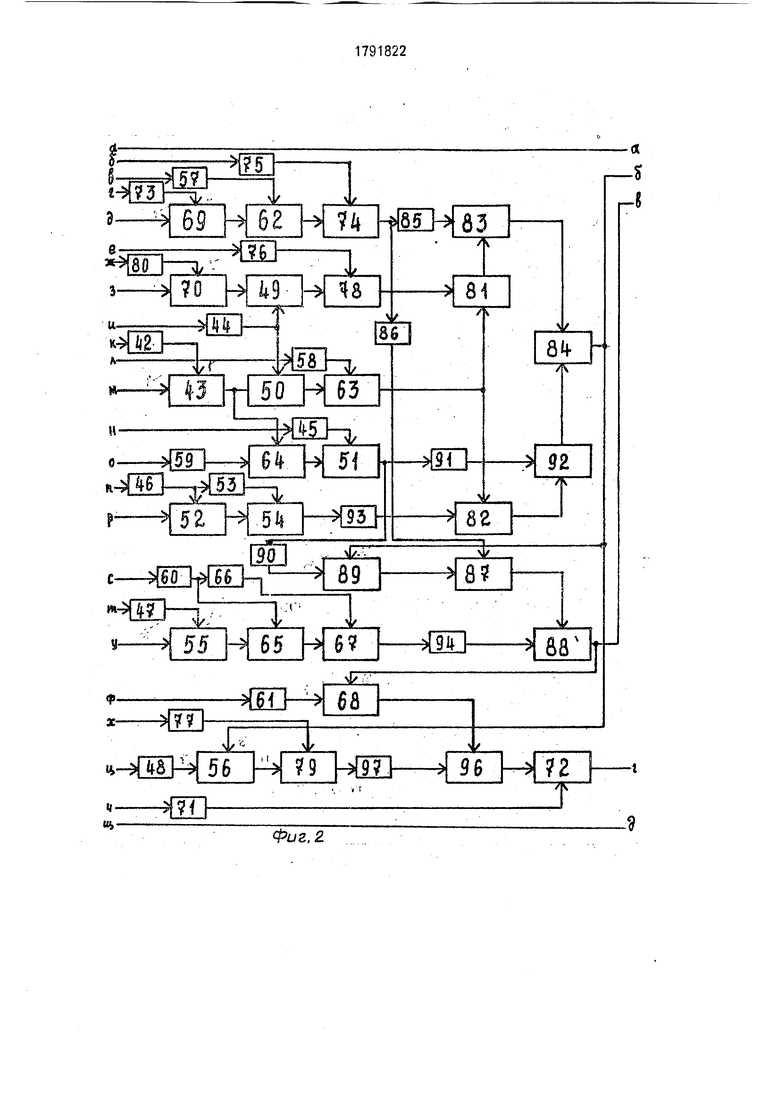

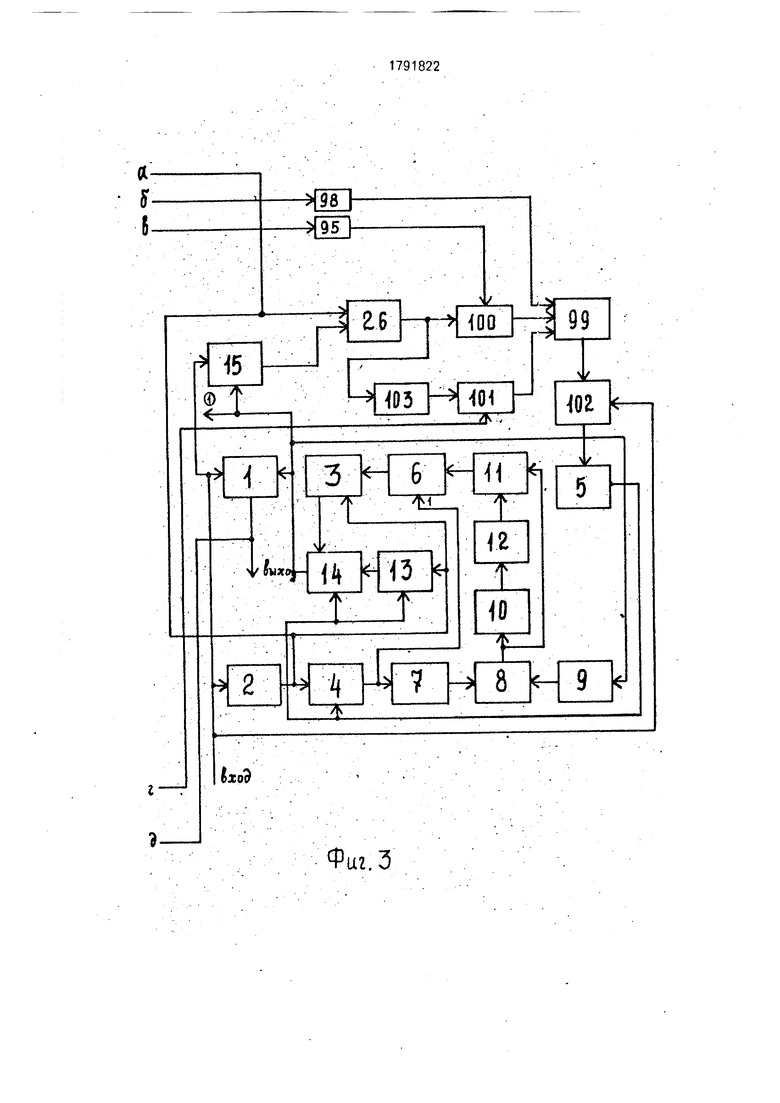

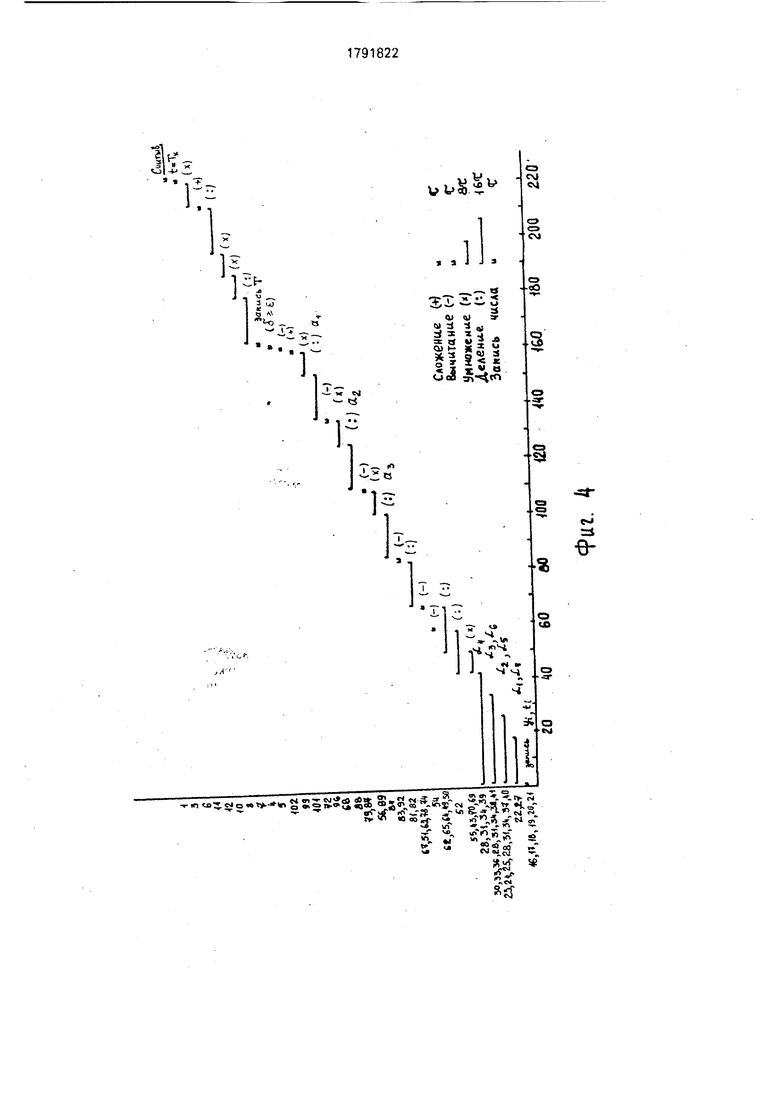

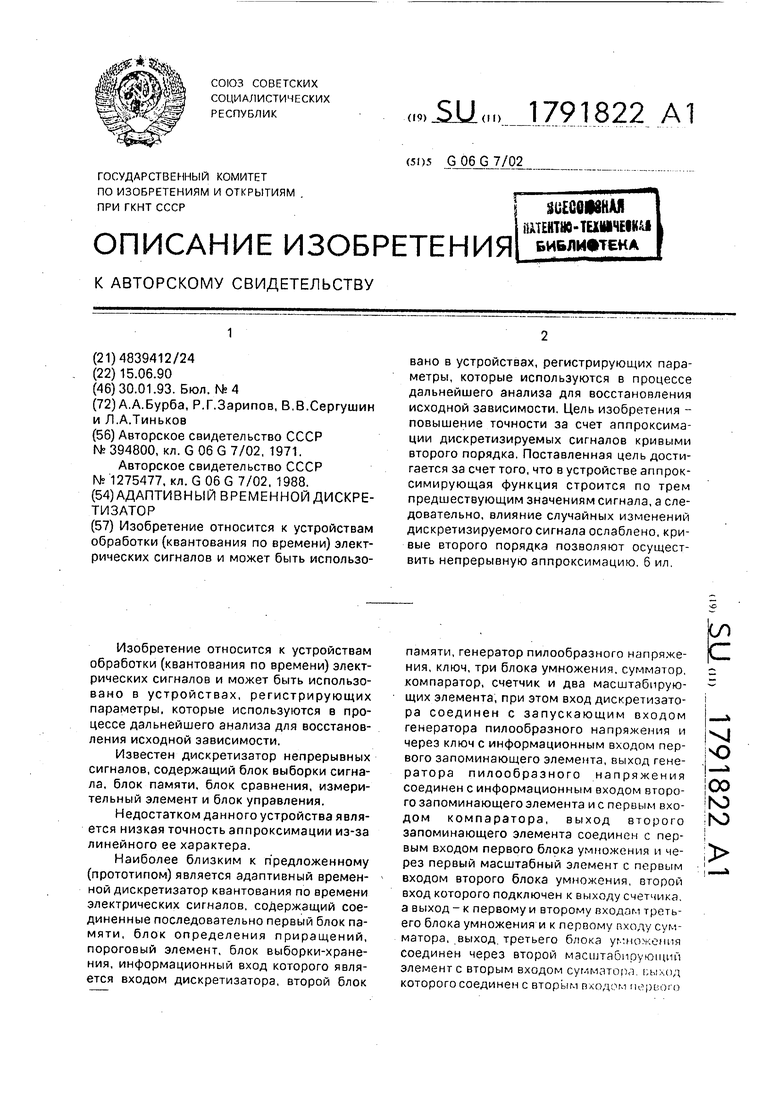

На фиг. 1,2 и 3 представлена блок-схема адаптивного временного дискретизатора электрических сигналов (для ликвидации громоздкости связи между выходом компаратора и управляющими входами блоков памяти, а также между управляющим входом дискретизатора и входами обнуления бло- ков памяти, показаны не полностью, а обозначены путем нумерации); на фиг. 4 - циклограмма вычисления аппроксимирующей кривой (по оси ординат обозначены номера блоков, задействованных в вычислении кривой, а по оси абсцисс - длительности выполнения математических операций. Конкретные значения этих длительностей приведены в правом нижнем углу на фиг. 4); на фиг. 5 - блок-схема воз- можного варианта выполнения блоков возведения в степень; на-фиг. 6 - возможный вариант выполнения блоков осреднения, представленных на общей блок-схеме дискретизатора в укрупненном виде.

Адаптивный временной дискретизатор содержит блок выборки-хранения 1, выход которого является выходом дискретизатора, а информационный вход подключен к информационному входу дискретизатора и входу запуска генератора 2 пилообразного напряжения, соединенного выходом с первым входом компаратора 3 и информационным входом запоминающего элемента 4, подключенного управляющим входом к вы- ходу порогового элемента 5, а выходом - к первому входу первого блока б умножения и входу масштабирующего элемента 7, выход которого соединен с первым входом второго блока 8 умножения, подключенного

вторым выходом к выходу счетчика отсчетов 9, а выходом - к входу первого квадратора 10 и первому входу первого сумматора 11. Второй вход первого сумматора 11 подключен через второй масштабирующий элемент 12 к выходу квадратора 10, а выходом - к второму входу первого блока умножения, соединенного выходом с вторым входом компаратора 3.

Выход генератора 2 пилообразного напряжения через ключ 13 подключен также к первому входу коммутатора 14, второй вход которого соединен с выходом компаратора 3. Выход коммутатора 14 подключен к управляющему входу блока 1 выборки-хранения, к входу счетчика 9 отсчетов, к входу обнуления счетчика 15 времени дискретизации, к управляющим входам записи первого 16, второго 17, третьего 18, четвертого 19, пятого 20 и шестого 21 блоков памяти, Управляющие входы ключа 13 и коммутатора 14 соединены с выходом порогового элемента 5.

Информационный вход первого блока 16 памяти подключен к выходу блока 1 выборки хранения,, а выход - к информационному входу второго блока 17 памяти, к первому входу первого блока 22 осреднения и к первому входу третьего блока 23 умножения.

Выход второго блока 17 памяти соединен с информационным входом третьего блока 18 памяти, с вторым входом первого блока 22 осреднения и с первым входом четвертого блока умножения 24.

Выход третьего блока 18 памяти соединен с третьим входом первого блока 22 осреднения и первым входом пятого блока 25 умножения. Генератор 2 пилообразного напряжения своим выходом подключен к первому входу второго сумматора 26 и информационному входу четвертого блока 19 памяти, выход которого соединен с информационным входом пятого блока 20 памяти, первым входом второго блока 27 осреднения, входом первого блока 28 возведения в степень, вторым входом третьего блока 23 умножения и через первый элемент 29 задержки с первым входом шестого блока 30 умножения, соединенного вторым входом с выходом третьего блока 23 умножения.

Выход пятого блока 20 памяти подключен к информационному входу шестого блока 21 памяти, второму входу второго блока 27осреднения, второму входу второго блока 31 возведения в степень, второму входу четвертого блока 24 умножения и через второй элемент32 задержки с первым входом седь- мого блока 33 умножения, подключенного

вторым входом к выходу четвертого 24 блока умножения.

Выход шестого блока 21 памяти соединен с третьим входом второго блока 27 осреднения, входом третьего блока 34 возведения в степень, вторым входом пятого блока 25 умножения и через третий элемент 35 задержки к первому входу восьмого блока 36 умножения, соединенного вторым входом с выходом пятого блока 25 умножения,

Первый.28, второй 31 и третий 34 блоки возведения в степень подключены выходами сигналов второй степени к соответствующим входам третьего блока 37 осреднения, выходами сигналов .третьей степень - к соответствующим входам четвертого блока 38 осреднения, а выходами сигналов четвертой степени - к соответствующим входам пятого блока 39 осреднения.

Входы шестого блока 40 осреднения соединены с выходами третьего 23, четвертого 24 и пятого 25 блоков умножения..

Входы седьмого блока 41 осреднения подключены к выходам шестого 30, седьмого 33 и восьмого 36 блоков умножения.

Выход второго блока 27 осреднения че- рез четвертый элемент 42 задержки соединен с первым входом девятого блока 43 умножения.

Выход третьего блока 37 осреднения подключен к входам пятого 44, шестого 45, седьмого 46, восьмого 47 и девятого 48 элементов задержки.

Выход пятого элемента 44 задержки соединен с входами делителя первого 49 и второго 50 блоков деления,

Выход шестого элемента 45 задержки подключен к входу уменьшаемого первого блока 51 вычитания.

Выход седьмого элемента 46 задержки соединен с входом делителя третьего блока 52 деления и через десятый элемент 53 задержки - с входом уменьшаемого второго блока 54 вычитания, подключенного входом вычитаемого к входу третьего блока 52 деления.

Выход восьмого элемента 47 задержки соединен с первым входом десятого блока 55 умножения.

Выход девятого элемента 48 задержки подключен к первому входу одиннадцатого блока 56 умножения.

Выход четвертого блока 38 осреднения соединен с входами одиннадцатого 57, двенадцатого 58,тринадцатого 59, четырнадцатого 60 и пятнадцатого 61 элементов задержки.

Выход одиннадцатого элемента 57 задержки подключен к выходу делителя четвертого блока 62 деления.

Выход двенадцатого элемента 58 задержки соединен с .входом уменьшаемого третьего блока 63 вычитания.

Выход тринадцатого элемента 59 задержки подключен к входу делителя пятого бло-. ка 64 деления, соединенного выходом с

0 входом вычитаемого первого блока 51 вычитания, а входом делимого - с выходом девятого блока 43 умножения и входом делимого второго блока 50 деления, подключенного выходом к входу вычитаемого третьего бло5 ка 63 вычитания.

Выход четырнадцатого элемента 60 задержки соединен с входом делителя шестого блока 65 деления и через шестнадцатый элемент 66 задержки - с входом уменьшае0 мого четвертого блока 67 вычитания, подключенного входом вычитаемого к выходу шестого блока 65 деления, соединенного входом делимого с выходом десятого блока 55 умножения.

5Выход пятнадцатого элемента 61 задержки подключен к первому входу двенадцатого блока 68 умножения.

Выход пятого блока 39 осреднения соединен с входом делимого третьего блока 52

0 деления, вторыми входами девятого 43 и десятого 55 блоков умножения; первыми входами тринадцатого 69 и четырнадцатого 70 блоков умножения и входом семнадцатого элемента 71 задержки, подключенного

5 выходом к входу делителя седьмого блока 72 деления.

Выход шестого блока 40 бсреднения через восемнадцатый элемент 73 задержки соединен со вторым входом тринадцатого

0 блока 69 умножения, подключенного выходом к входу делимого четвертого блока 62 деления, соединенного выходом с входом вычитаемого пятого блока 74 вычитания. Выход седьмого блока 41 осреднения

5 подключен к входам девятнадцатого 75, двадцатого 76 и двадцать первого 77 элементов задержки.

Выход девятнадцатого 75 элемента задержки соединен с входом уменьшаемого

0 пятого блока 74 вычитания.

Выход двадцатого элемента 76 задержки подключен к входу уменьшаемого шестого блока 78 вычитания.

Выход двадцать первого элемента 77

5 задержки соединен с входом уменьшаемого седьмого блока 79 вычитания.

Выход первого блока 22 осреднения подключен через двадцать второй элемент 80 задержки к второму входу четырнадцатого блока 70 умножения, соединенного выходом с входом делимого первого блока 49 деления, подключенного выходом к входу вычитаемого шестого блока 78 вычитания, выход которого соединен с входом делимого восьмого блока 81 деления, подключенного входом делителя к выходу третьего блока 63 вычитания и входу делителя девятого блока 82 деления, а выходом - к входу вычитаемого восьмого блока 83 вычитания, соединенного выходом с входом делимого десятого блока 84 деления, а входом уменьшаемого - через двадцать третий элемент

85задержки к выходу пятого блока 74 вычитания и входу двадцать четвертого элемента

86задержки, соединенного выходом с входом вычитаемого девятого блока 87 вычитания, подключенного выходом к входу делимого одиннадцатого блока 88 деления, а входом уменьшаемого - к выходу пятнадцатого блока 89 умножения первым входом через двадцать пятый элемент 90 задержки с-выходом первого блока 51 вычитания и входом двадцать шестого элемента 91 задержки, подключенного выходом к входу уменьшаемого десятого блока 92 вычитания, соединенного выходом с входом делителя десятого блока 84 деления, а входом вычитаемого - с выходом девятого блока 82 деления, подключенного входом делимого через двадцать седьМбй элемент 93 задержки к выходу второго блока 54 вычитания.

Выход четвертого блока 67 вычитания через двадцать восьмой элемент 94 задержки соединен с входом делителя одиннадцатого блока 88 деления, выход которого подключен к входу двадцать девятого элемента 95 задержки и второму входу двенадцатого блока 68 умножения, соединенного выходом с входом вычитаемого одиннадцатого блока 96 вычитания, подключенного выходом к входу делимого седьмого блока 72 деления, а входом уменьшаемого - через тридцатый элемент 97 задержки к выходу седьмого блока 79 вычитания, соединенного входом вычитаемого с выходом одиннадцатого блока 56 умножения, подключенного вторым входом к выходу десятого блока 84 деления, второму входу пятнадцатого блока 89 умножения и входу тридцать первого элемента 98 задержки, выход которого соединен с первым входом третьего сумматора 99, подключенного вторым и третьим входами к выходам шестнадцатого 100 и семнадцатого 101 блоков умножения соответственно, а выходом - к входу вычитаемого блока 102 вычитания по модулю. Выход блока 102 вычитания по модулю соединен с входом порогового элемента 5, а вход уменьшаемого - с информационным входом дискретизатора и входом запуска

счетчика 15 времени дискретизации, подключенного выходом к второму входу второго сумматора 26.

Выход второго сумматора 26 соединен 5 с входом второго квадратора 103 и первым входом шестнадцатого блока 100 умножения, подключенного вторым входом к выходу двадцать девятого элемента 95 задержки. Выход второго квадратора 103 соеди- 0 нен с первым входом семнадцатого блока 101 умножения, подключенного вторым вхо- дом к выходу седьмого блока 72 деления.

Вторые управляющие входы первого 16, второго 17, третьего 18, четвертого 19; пято5 го 20 и шестого 21 блоков памяти являются входами обнуления и управляющими входами дискретизатора.

Вход представленного на фиг. 5 блока возведения в степень подключен к первому

0 и второму входам первого блока 104 умножения и к входу первого элемента 105 задержки, выходом соединенного с первым входом второго блока 106 умножения и с входом второго элемента 107 задержки, вы5 ходом подключенного к первому входу третьего блока 108 умножения.

Выход первого блока 104 умножения подключен к выходу второй степени блока возведения в степень и второму входу вто0 рого блока 106 умножения.

Выход второго блока 106 умножения соединен с выходом третьей степени блока возведения в степень и со вторым входом третьего блока 108 умножения. Выход по5 следнего является выходом четвертой степени блокэ возведения в степень.

Первый, вторсй, третий входы представленного на фхг. 6 блока осреднения подключены соответственно к первому, вто0. рому и третьему входам сумматора 109, выходам подключенного к входу масштабирующего элемента 110, Выход последнего является выходом блока осреднения.

5 Дискретизатор работает следующим образом.

В начальный момент времени через вторые управляющие входы первого 16, второго 17, третьего 18, четвертого 19, пято0 го 20 и шестого 21 блоков памяти подается сигнал на их обнуление. Одновременно с поступлением входного сигнала запускается генератор 2 пилообразного напряжения, работающий в ждущем режиме и имеющий

5 период развертки, равный максимально возможной длительности Тс дискретизации сигнала, а также запускается счетчик 15 времени дискретизации. В этот момент времени ключ 13 замкнут, а выход коммутатора 14 подключен к первому своему входу, поэтому

после отработки генератором 2 пилообразного напряжения полного цикла на управляющий вход блока 1 выборки-хранения через ключ: 13 и первый вход коммутатора 14 подается управляющий сигнал для выборки значения входного сигнала. Одновременно этот же управляющий сигнал поступает на вход обнуления счетчика 15 времени дискретизации, на первые входы управления записью первого 16, второго 17, третьего 18, четвертого 19, пятого 20 и шестого 2J блоков памяти и на вход счетчика 9 отсчетов. Управляющие входы блока 1 выборки-хранения, с первого 16 по шестой 21 блоков памяти, счетчика 9 отсчетов, вход обнуления счетчика 15 времени дискретизации, при подключении к выходу генератора 2 пилообразного напряжения, оказывают уп- равляющее воздействие только при достижении последним наибольшей величины выходного сигнала. С выхода генератора 2 пилообразного напряжения сигнал, пропорциональный текущему времени работы дискретиззтора, поступает также на информационный вход четвертого блока 19 памяти, вытесняя хранившуюся там ранее информацию в пятый блок 20 памяти, а тот, ;В свою очередь, перезаписывает свою информацию в шестой блок 21 памяти. Параллельно с записью моментов времени значения выходного сигнала, соответствующие своим моментам времени, заносятся в первый 16, второй 17 и третий 18 блоки памяти. После отработки генератором 2 пилообразного напряжения трех циклов в блоках памяти будут записаны три значения выходного сигнала (yi, , 2, 3) и три соответствующих им момента времени (ti, 1, 2, 3). Далее вступает в работу часть схемы, обеспечивающая вычисление аппроксимацйон- ной кривой по выражению (1).

Выходной сигнал четвертого блока 19 памяти, пропорциональный моменту времени ts, поступает на первый вход второго блока 27 осреднения, на вход первого блока 28 возведения в степень, на. второй вход третьего блока 23 умножения и через первый элемент 29 задержки на первый вход шестого блока 30 умножения.

Сигнал, пропорциональный моменту времени t2, с выхода пятого блока 20 памяти поступает на второй вход второго блока 27 осреднения на вход второго блока 31 возведения в степень, на второй вход четвертого блока 24 умножения и через второй элемент

32задержки на первый зчод седьмого блока

33умножения. Аналогичном образом сигнал, пропорциональный моменту времени ti, .. .:- ,:г/.v.i шестого блока 21 памяти поступает .егий вход второго 27 осреднения, на вход третьего блока 34 возведения в степень, на второй вход пятого блока 25 умножения и через третий элемент 35 задержки на первый вход восьмого блока 36

умножения.

Сигналы, пропорциональные ti (, 2, 1} с выходов второй степени первого 28, второго 31 и третьего 34 блоков возведения в степень, поступают соответственно на первый, второй и третий входы третьего блока 37 осреднения,

С выходов третьей степени первого 28, второго 31 и третьего 34 блоков возведения в степень сигналы, пропорциональные

ti3 (, 2, 1), поступают соответственно на первый, второй и третий входы четвертого блока 38 осреднения.

Сигналы, пропорциональные ti4(, 2,1), с выходов четвертой степени первого 28,

второго 31 и третьего 34 блоков возведения в степень поступают соответственно на первый, второй и третий входы пятого блока 39 осреднения,.,.,..

Сигналы, пропорциональные зн ачениям уз, У2, У1, с выходов первого 16, второго

17 и третьего 18 блоков памяти поступают

соответственно на первый, второй и третий

входы первого блока 22 осреднения, а также

на первые входы третьего 23, четвертого 24

и пятого 25 блоков умножения.

Сигналы, пропорциональные произведению yi ti (, 2, 1), с выходов третьего 23, четвертого 24 и пятого 25 блоков умножения поступают соответственно на первый, второй и третий входы шестого блока

40осреднения, а также на вторые входы шестого 30, седьмого 33 и восьмого 36 блоков умножения.

С выходов произведений шестого 30, седьмого 33 и восьмого 36 блоков умножений сигналы, пропорциональные произведению yi ti2 (, 2, 1), поступают соответственно на первый, второй и третий входы седьмЬго41 блока,осреднения. С выходов второго 27, третьего 37, четвертого 38, пятого 39, шестого 40, седьмого

41и первого 22 блоков осреднения снимаются сигналы, пропорциональные статистическим моментам (3) системы двух

величин t и у.

С выхода второго блока 27 осреднения сигнал, пропорциональный величине а 1 (3), через четвертый элемент 42 задержки поступает на первый вход девятого блока 43

умножения.

Сигнал, пропорциональный величине о:2 (3) с выхода третьего блока 37 осреднения поступает через пятый элемент 44 задержки на входы делителя первого 49 и

второго 50 блоков деления, через шестой элемент45 задержки на вход уменьшаемого первого блока 51 вычитания, через седьмой элемент 46 задержки на вход делителя третьего блока 52 деления, через седьмой 46 и десятый 53 элементы задержки на вход уменьшаемого второго блока 54 вычитания, через восьмой элемент 47 задержки на первый десятого блока 55 умножения, через девятый элемент 48 задержки на первый вход одиннадцатого блока 56 умножения.

Сигнал, пропорциональный величине аз (3), с выхода четвертого блока 38 осреднения через одиннадцатый элемент 57 задержки поступает на вхо.д делителя четвертого блока 62 деления, через двенадцатый элемент 58 задержки на вход уменьшаемого третьего блока 63 вычитания, через тринадцатый элемент 59 задержки на вход делителя пятого блока 64 деления, че- рез четырнадцатый элемент 6.0 задержки на вход делителя шестого блока 65 деления, через четырнадцатый 60 и шестнадцатый 66 элементы задержки на вход уменьшаемого четвертого блока 67 вычитания, через пят- надцатый элемент 61 задержки на первый вход двенадцатого блока 68 умножения.

Сигнал, пропорциональный величине а А (3), с выхода пятого блока 39 осреднения поступает на первый вход тринадцатого блока 69 умножения, на первый вход четырнадцатого блока 70 умножения, из второй вход девятого блока 43 умножения, на вход делимого третьего блрка 52 деления, на второй вход десятого блока 55 умножения и через семнадцатый элемент 71 задержки на вход делителя седьмого блока 72 деления.

Сигнал, пропорциональный величине о:5 (3), с выхода шестого блока 40 осреднения через восемнадцатый элемент 73 задер- жки поступает на второй вход тринадцатого блока 69 умножения.

Сигнал, пропорциональный величине «б (3), с выхода седьмого блока 41 осреднения через девятнадцатый элемент 75 задер- жки поступает на вход уменьшаемого пятого блока 74 вычитания, через двадцатый элемент 76 задержки на вход уменьшаемого шестого блока 78 вычитания, через двадцать первый элемент 77 задержки на вход уменьшаемого седьмого блока 79 вычитания.

Сигнал, пропорциональный величине а 7 (3), с выхода первого блока 22 осреднения через двадцать второй элемент 80 за- держки поступает на второй вход четырнадцатого блока 70 умножения.

Сигнал, пропорциональный произведению величин ал as , с выхода произведения тринадцатого блока 69 умножений поступает на вход делимого четвертого блок 62 деления с выхода частного которого сиг- Од «5 нал, пропорциональный величине ---:-- ,

поступает нэ вход вычитаемого пятого блока 74 вычитания. С выхода частного пятого блока 74 вычитания сигнал, пропорциональОА «5 ныи разнице а& , через двадцать

СчЗ

третий элемент 85 задержки поступает на вход уменьшаемого восьмого блока 83 вычитания и через двадцать четвертый элемент 86 задержки на вход вычитаемого девятого блока 87 вычитания.

Сигнал, пропорциональный произведению величин сц (7, с выхода произведения четырнадцатого блока 70 умножения поступает на вход делимого первого блока 49 деления с выхода частного которого сигнал, пропорциональный частному от деле04 07

поступает на вход вычитаемого

ния

02

шестого блока 78 вычитания, сигнал разности Об -

ОА ai аг

с последнего поступает на

вход делимого восьмого блока 81 деления. Сигнал, пропорциональный произведению величин CL 04 с выхода произведения девятого блока 43 умножения поступает на входы делимого второго 50 и пятого 64 блоков деления. Сигнал, пропорциональа ОА ныи частному от деления с выхода

частного второго блока 50 деления поступает на вход вычитаемого третьего блока 63 вычитания, с выхода разности которого сигнал, пропорциональный разности

а ОА аз , поступает на входы делителя

восьмого 81 и девятого 82 блоков деления. Сигнал, пропорциональный частному от деле01

.1

СЫч

ния величин (og - а / v ar)

входящих в выражение (5), с выхода частного восьмого блока 81 деления поступает на вход вычитаемого восьмого блока 83 вычитания, сигнал разности которого, пропорциональный величине числителя выражения (5), поступает на вход делимого десятого блока 84 деления.

Сигнал, пропорциональный частному от

а ОА деления , с выхода частного пятого

блока 64 деления поступает на вход вычитаемого первого блока 51 вычитания, с выхода которого сигнал, пропорциональный разноа ОА

через двадцать шестой

СТИ СГ2

03

элемент 91 задержки поступает на вход вычитаемого десятого блока 92 вычитания и через двадцать пятый элемент 90 задержки на первый вход пятнадцатого блока 89 умножения.

Сигнал, пропорциональный частному от деления OA/OI с выхода частного третьего блока 52 деления поступает на вход вычитаемого второго блока 54 вычитания, с выхода которого сигнал разности величин (Xi -OA/OI через двадцать седьмой элемент 93 задержки поступает на вход делимого девятого блока 82 деления. Сигнал, пропорциональный частному от деления величин (ai О4/а2У(аз - а ал/О-г) , входящих в выражение (5), с выхода частного девятого блока 82 деления поступает на вход вычитаемого десятого блока 92 вычитания, с выхода которого сигнал разности, пропорциональный выражению знаменателя уравнения (5), поступает на вход делителя десятого блока 84 деления.

С выхода частного десятого блока 84 деления сигнал, пропорциональный значению коэффициента аз, вычисленному по выражению (5), поступает через тридцать первый элемент 98 задержки на первый вход третьего сумматора 99 и на вторые входы пятнадцатого 89 и одиннадцатого 56 блоков умножения.

С выхода произведения пятнадцатого блока 89 умножения сигнал, пропорциональный произведению аз(22 - а, ОА/ОЗ) , поступает на вход вычитаемого девятого блока 87 вычитания, с выхода которого сигнал, пропорциональный числителю выражения (6), поступает на вход делимого одиннадцатого блока 88 деления.

С выхода произведения десятого блока 55 умножения сигнал, пропорциональный произведению аг щ , поступает на вход делимого шестого блока 65 деления, С выхода частного данного блока сигнал, пропорциональный частному от деления

«2 од

величин -™--, поступает на вход вычитаемого четвертого блока 67 вычитания, С выхода разности последнего сигнал, пропорциональный знаменателю выражения (6), через двадцать восьмой элемент 94 за- .держки поступает на вход делителя одиннадцатого блока 88 деления. С выхода частного одиннадцатого блока 88 деления сигнал, пропорциональный величине коэффициента 32, вычисленной по выражению (6), поступает через двадцать девятый элемент 95 задержки на второй вход шестнадцатого блока 100 умножения и на второй вход двенадцатого блока 68 умножения.

Сигнал, пропорциональный произведению 32 «з , с выхода произведения двенадцатого блока 68 умножения поступает на вход вычитаемого одиннадцатого блока 96

вычитания. С выхода одиннадцатого блока 56 умножения сигнал, пропорцональный произведению аз OQ. , поступает на вход вычитаемого седьмого блока 79 вычитания, с выхода.разности которого сигнал, пропорциональный разности величин % - аз ОД, через тридцатый элемент 97 задержки поступает на вход уменьшаемого одиннадцатого блока 96 вычитания. С выхода разности последнего сигнал, пропорциональный числителю выражения (7), поступает на вход делимого седьмого блока 72 деления. Сигнал, пропорциональный величине коэффициента ai, вычисленной по выражению (7), с выхода частного седьмого блока 72 деления

поступает на второй вход семнадцатого блока 101 умножения. С выхода счетчика 15 времени дискретизации сигнал, пропорциональный времени, прошедшему от момента осуществления последней дискретизации,

поступает на второй вход второго сумматора 2 б

С выхода суммы сумматора 26 сигнал, равный сумме сигнала, пропорционально непрерывному времени работы дискретизатора от момента включения дискретизатора и сигнала, пропорционального времени, прошедшему от момента осуществления последней дискретизации поступает на первый вход шестнадцатого блока 100

умножения и на вход второго квадратора 103.

Сигнал, пропорциональный произведению 32(tn+ т), с выхода произведения шестнадцатого блока 100 умножения поступает

на второй вход третьего сумматора 99.

С выхода второго квадратора 103 сигнал, пропорциональный величине (tn+ т)2, поступает на первый вход семнадцатого блока 101 умножения, где умножается на

коэффициент ai и поступает на третий вход третьего сумматора 99.

С выхода третьего сумматора 99 аппроксимированный по выражению (1) сигнал поступает на вход вычитаемого блока вычитания 102 по модулю, вход уменьшаемого которого подключен к информационному входу дискретизатора. С выхода блока 102 вычитания по модулю сигнал, пропорциональный величине д (8), поступает на вход

5 порогового элемента 5, который проверяет выполнение неравенства (9). Как только неравенство (9) выполнится, на вход запоминающего элемента 4 и управляющие входы ключа 13 и коммутатора 14 поступает управляющий сигнал, по которому ключ 13 размыкается, выход коммутатора 14 подключается к второму своему входу, а запоминающий элемент 4 фиксирует значение напряжения с генератора 2 пилообразного напряжения, пропорциональное времени Т, прошедшему с начала работы до момента срабатывания порогового элемента 5.

Напряжение, пропорциональное Т, поступает на вход первого масштабирующего элемента 7, на выходе которого формируется напряжение, пропорциональное , поступающее на вход второго блока 8 умножения, на другой вход которого поступает сигнал со счетчика 9 отсчетов, фиксирующего число ((сформированных отсчетов выборки. С выхода произведения второго блока 8 умножения напряжение, пропорциональное К L, поступает на вход первого сумматора 11 и на вход первого квадратора 10, с выхода которого сигнал, пропорциональный (К - L)2, поступает на вход второго масштабирующего элемента 12, где делится на два. В результате на выходе первого сумматора 11 формируется напряжение, приближенно соответствующее е . Это напряжение поступает на вход первого блока 6 умножения, вторым входом соединенного с выходом запоминающего элемента 4. С выхода произведения первого блока 6 умножения напряжение, пропорциональное TeKL, поступает на второй вход компаратора 3, на первый вход которого поступает напряжение с выхода генератора 2 пилообраз- ного напряжения, пропорциональное текущему времени t, прошедшему с начала дискретизации сигнала. В моменты времени на выходе компаратора 3 формируются импульсы, которые затем через коммутатор 14 поступают на управляющий вход блока 1 выборки-хранения, счетчик 9 отсчетов, управляющие входы,записи первого 16, второго 17, третьего 18, четвертого 19, пятого 20 и шестого 21 блоков памяти и вход обнуления счетчика 15 времени дискретизации.

Таким образом, в дискретизаторе осуществляется адаптивная выборка значений входного сигнала в моменты времени, подчиняющиеся экспоненциальному закону

TQKL

, 1М,

где М+1 - число отсчетов в выборке. . При этом ослаблено влияние случайных изменений как самого сигнала; так и его временного масштаба на выходную информацию. Следует отметить особенности работы адаптивного временного дискретизатора в первых трех циклах дискретизации сигнала.

Особенностью является то, что в первых трех циклах на выходе третьего сумматора 99 формируется сигнал, отличающийся по величине от регистрируемого сигнала. На- 5 пример, в конце первого цикла его величина равна нулю, так как в начальный момент времени на вторые входы блоков памяти с первого 16 по шестой 21 был подан сигнал обнуления. Поэтому в первом цикле работы

0 дискретизатора статистические моменты системы двух величин t и у, определяемые с помощью выражений (3), а следовательно, и коэффициенты ai, 32, аз, для вычисления которых используются выражения (5). (6), (7),

5 будут также равны; нулю.

Во втором и третьем циклах работы эти величины уже не будут нулевыми, но из-за присутствия нулевых значений ti и yi (, 1) во втором цикле, а также ti и yi () в третьем

0 цикле работы адаптивного временного дискретизатора, статистические моменты данных величин еще не обеспечат точное вычисление прогнозируемого значения сигнала, поэтому на выходе третьего суммато5 ра 99 формируется сигнал, отличающийся

по величине от регистрируемого параметра.

В первом цикле работы дискретизатора

ключ 13 замкнут, а выход коммутатора 14

подключен к первому своему входу, поэтому

0 после отработки генератором 2 пилообразного напряжения полного цикла на управляющий вход блока 1 выборки-хранения через ключ 13 и первый вход коммутатора 14 подается управляющий сигнал для выборки

5 значения входного сигнала.

Во втором и третьем циклах регистрации сигнала работы устройства ничем не . отличается от работы в последующие моменты времени. Сигнал, пропорциональный

0. величине б , определенный по формуле (8), с выхода блока 102 вычитания по модулю, будет превосходить величину заданной погрешности е, т.е. неравенство (9) будет выполняться, следовательно, на выходе

5 порогового элемента 5 будет сформирован управляющий сигнал, обеспечивающий нормальную работу адаптивного временного дискретиэатора.

Положительный эффект, который дает

0 изобретение, заключается в том, что оно позволяет, по сравнению с прототипом (базовым объектом), существенно повысить точность аппроксимации. Это объясняется следующим: так как аппроксимирующая

5 функция строится по трем предшествующим значениям сигнала, то влияние случайных изменений дискретизируемого сигнала ослабление. Кроме того, кривые второго порядка позволяют осуществлять непрерывную аппроксимацию. Моделирование, проведенное на ЭВМ, показывает, что погрешность аппроксимации при использовании предлагаемого устройства снижается на 30...40%. Уменьшение погрешности приво- дит, в свою очередь, к снижению ущерба, возникающего из-за непредвиденных последствий, которые могут появиться по причине большой погрешности аппроксимации при использовании прототипа (например, при контроле).

Экономический эффект от внедрения предлагаемого изобретения может быть оценен суммой предотвращенного ущерба, который мог бы возникнуть прииспользова- нии прототипа.

Формула изобретения . Адаптивный временной дискретизатор, содержащий блок выборки-хранения, выход которого является выходом дискретизато- ра, а информационный вход подключен к информационному входу дискретизатора и входу запуска генератора пилообразного напряжения, соединенного выходом с первым входом компаратора и информацией- ным входом запоминающего элемента, подключенного управляющим входом к вы- ходу порогового элемента, а выходом - к первому входу первого блока умножения и входу масштабирующего элемента, выход которого соединен с первым входом второго блока умножения, подключенного вторым входом к выходу счетчика отсчетов, а выходом - к входу- первого квадратора и первому входу первого сумматора, подклю- ценного вторым входом через второй масштабирующий элемент к выходу квадратора, а выходом - к второму входу первого блока умножения, соединенного выходом с вторым входом компаратора, отличающий- с я тем, что, с целью повышения точности за счет аппроксимации дискретизируемых сигналов кривыми второго порядка, в него дополнительно введены второй квадратор, три блока возведения в степень, семь бло- ков осреднения, счетчик времени дискретизатора, блок вычитания по модулю, шесть блоков памяти, с третьего по семнадцатый блоки умножения, второй и третий сумматоры, одиннадцать блоков деления, одиннад- цать блоков вычитания, тридцать один элемент задержки, коммутатор и ключ, подключенный информационным входом к выходу генератора пилообразного напряжения, а выходом - к первому информационному вхо- ду коммутатора, соединенного вторым информационным входом с выходом компаратора, а выходом - с входом счетчика отсчетов, входом обнуления счетчика времени дискрети- зации, управляющим входом блока

выборки-хранения и входами управления записью с первого по шестой блоков памяти, причем управляющие входы ключа и коммутатора соединены с выходом порогового элемента, выход блока выборки-хранения подключен к информационному входу первого блока памяти, соединенного выходом с первым входом первого блока осреднения, первым входом третьего блока умножения и информационным входом второго блока памяти, выход которого подключен к второму входу первого блока осреднения, первому входу четвертого блока умножения и информационному входу третьего блока памяти, соединенного выходом с третьим входом первого блока осреднения и первым входом пятого блока умножения, причем выход генератора пилообразного напряжения подключен к первому входу второго сумматора и информационному входу четвертого блока памяти, выход которого соединен с информационным входом пятого блока памяти, первым входом второго блока осреднения, входом первого блока возведения в степень, вторым входом третьего блока умножения и входом первого элемента задержки, подключенного выходом к первому входу шестого блока умножения, соединенного вторым входом с выходом третьего блока умножения, причем выход пятого блока памяти подключен к информационному входу шестого блока памяти, второму входу второго блока осреднения, входу второго блока возведения в степень, второму входу четвертого блока умножения и входу второго элемента задержки, соединенного выходом с первым входом седьмого блока умножения, подключенного вторым входом к выходу четвертого блока умножения, причем выход шестого блока памяти соединен с третьим входом второго блока осреднения, входом третьего блока возведения в степень, вторим входом пятого блока умножения и входом третьего элемента задержки, подключенного выходом к первому входу восьмого блока умножения, соединенного вторым входом с выходом пятого блока умножения, причем первый, второй и третий блоки возведения в степень подключены выходами сигналов второй степени к соответствующим входам третьего блока осреднения, выходами сигналов третьей степени - к соответствующим входам четвертого блока осреднения, а выходами сигналов четвертой степени - к соответствующим входам пятого блока осреднения, при этом входы шестого блока осреднения соединены с выходами третьего, четвертого и пятого блоков умножения, входы седьмого блока осреднения подключены к выходам шестого, седьмого и восьмого блоков умножения, выход второго блока осреднения через четвертый элемент задержки соединен с первым входом девятого блока умножения, выход третьего блока осреднения подключен к входам элементов задержки с пятого по девятый, выход пятого элемента задержки соединен с входами делителя первого и .второго блоков деления, выход шестого элемента задержки подключен к входу уменьшаемого первого блока вычитания, выход седьмого элемента задержки соединен с входом делителя третьего блока деления и через десятый элемент задержки - с входом уменьшаемого второго блока вычитания, подключенного входом вычитаемого к выходу третьего блока деления выход восьмого элемента задержки соединен с первым входом десятого блока умножения, выходдевя- того элемента задержки подключен к .первому входу одиннадцатого блока умножения, выход четвертого блока осреднения соединен с входами элементов задержки с одиннадцатого по пятнадцатый, выход одиннадцатого элемента задержки подключен к входу делителя четвертого блока деления, выход двенадцатого элемента задержки соединен с входом уменьшаемого третьего блока вычитания, выход тринадцатого элемента задержки подключен к входу делителя пятого блока деления, соединен- . ного выходом с входом вычитаемого первого блока вычитания, а входом делимого - с выходом девятого блока умножения и входом делимого второго блока деления, подключенного выходом к входу вычитаемого третьего блока вычитания, выход четырнадцатого элемента задержки соединен с входом делителя шестого блока деления и через шестнадцатый элемент задержки - с входом уменьшаемого четвертого блока вычитания, подключенного входом вычитаемого к выходу шестого блока деления, соединенного входом делимого с выходом десятого блока умножения, выход пятнад- цатогоэлемента задержки подключен к первому входу двенадцатого блока умножения, выход пятого блока осреднения соединен с входом делимого третьего блока деления, вторыми входами девятого и десятого блоков умножения, первыми входами тринадцатого и четырнадцатого блоков умножения и входом семнадцатого элемента задержки, подключенного выходом к входу делителя седьмого блока деления, выход шестого блока осреднения через восемнадцатый элемент задержки соединен с вторым входом тринадцатого блока умножения, подключенного выходом к входу делимого четвертого блока деления, соединенного выходом с входом вычитаемого

пятого блока вычитания, выход седьмого блока осреднения подключен к входам элементов задержки с девятнадцатого по двадцать первый, выход девятнадцатого

элемента задержки соединен с входом уменьшаемого пятого блока вычитания, выход двадцатого элемента задержки подключен к входу уменьшаемого шестого блока вычитания, выход двадцать первого элемен0 та задержки соединен с входом уменьшаемого седьмого блока вычитания, выход первого блока осреднения подключен через двадцать второй элемент задержки к второму входу четырнадцатого блока умножения,

5 соединенного выходом с входом делимого первого блока деления, подключенного, выходом к входу вычитаемого шестого блока .- вычитания, выход которого соединен с входом делимого восьмого блока деления, под0 ключенного входом делителя к выходу третьего блока вычитания и входу делителя девятого блока деления, а выходом - к входу вычитаемого восьмого блока вычитания, соединенного выходом с входом делимого де5: сятого блока деления, а входом уменьшаемого через двадцать третий элемент задержки - к выходу пятого блока вычитания и входу двадцать четвертого элемента задержки, соединенного выходом

0 с входом вычитаемого девятого блока вычитания, подключенного выходом к входу де- лимого одиннадцатого блока деления, а входом уменьшаемого - к выходу пятнадцатого блока умножения, соединенного пер5 вым входом через двадцать пятый элемент задержки с выходом первого блока вычитания и входом двадцать шестого элемента задержки подключенного выходом к входу уменьшаемого десятого блока вычитания,

0 соединенного выходом с входом делителя десятого блока деления, а входом вычитаемого - с выходом девятого блока деления, подключенного входом делимого через двадцать седьмой элемент задержки к выхо5 ду второго блока вычитания, причем выход четвертого блока вычитания через двадцать восьмой элемент задержки соединен с входом делителя одиннадцатого блока деления, выход которого подключен к входу

0 двадцать девятого элемента задержки и второму входу двенадцатого блока умножения, соединенного выходом с входом вычитаемого одиннадцатого блока вычитания, подключенного выходом к входу делимого седьмого

5 блока деления, а входом уменьшаемого через тридцатый элемент задержки - к выходу седьмого блока вычитания, соединенного входом вычитаемого с выходом одиннадцатого блока умножения, подключенного вто- рым входом к выходу десятого блока

деления, второму входу пятнадцатого блока умножения и входу тридцать первого элемента задержки, выход которого соединен с лервым входом третьего сумматора, подключенного вторым и третьим входами к выходам шестнадцатого и семнадцатого блоков умножения соответственно, а выходом - к входу вычитаемого блока вычитания по модулю, соединенного выходом с входом порогового элемента, а входом уменьшаемого - с информационным входом дискре0

тизатора и входом запуска счетчика времени дискретизации, подключенного выходом к второму входу второго сумматора, выход которого соединен с входом второго квадратора и первым входом шестнадцатого блока умножения, подключенного вторым входом к выходу двадцать девятого элемента задержки, а выход второго квадратора соединен с первым входом семнадцатого блока умножения, подключенного вторым входом к выходу седьмого блока деления.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ ВРЕМЕННОЙ ДИСКРЕТИЗАТОР | 2015 |

|

RU2583707C1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

| ИНФОРМАЦИОННО-ИЗМЕРИТЕЛЬНАЯ СИСТЕМА ПЕРЕМЕЩЕНИЙ И ДЕФОРМАЦИЙ ОБЪЕКТА | 2005 |

|

RU2307315C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

| Устройство для контроля параметров | 1986 |

|

SU1401483A1 |

| Информационно-измерительная система для определения компонент перемещений и деформаций объекта | 1990 |

|

SU1783283A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ФУНКЦИИ РАСПРЕДЕЛЕНИЯ СЛУЧАЙНЫХ ВЕЛИЧИН И ЕЕ ТОЛЕРАНТНЫХ ГРАНИЦ ПО МАЛЫМ ВЫБОРКАМ | 2014 |

|

RU2553120C1 |

| УСТРОЙСТВО ДЛЯ ВЗАИМОДЕЙСТВИЯ С ЭКСПЕРТАМИ ПРИ ОПРЕДЕЛЕНИИ КАРДИНАЛЬНОЙ СОГЛАСОВАННОЙ ОЦЕНКИ | 2004 |

|

RU2256214C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ОЦЕНКИ ФАЗОВОЙ НАПРЯЖЕННОСТИ РЕСПОНДЕНТА | 2012 |

|

RU2492520C1 |

Изобретение относится к устройствам обработки (квантования по времени) электрических сигналов и может быть использовано в устройствах, регистрирующих параметры, которые используются в процессе дальнейшего анализа для восстановления исходной зависимости. Цель изобретения - повышение точности за счет аппроксимации дискретизируемых сигналов кривыми второго порядка. Поставленная цель достигается за счет того, что в устройстве аппроксимирующая функция строится по трем предшествующим значениям сигнала, а следовательно, влияние случайных изменений дискретизируемого сигнала ослаблено, кривые второго порядка позволяют осуществить непрерывную аппроксимацию. 6 ил.

Фиг. /

I

I

д

е ж

к

I Л

м

н

о к

с т

у

Ф

X

щФиг. 2

Фиг.З

(-.) -д1чнэУ У

(x) ЭТ Н9ЖОНИЯ

/) aTiHBlnhwg {4.) a-nHa o D

| АДАПТИВНЫЙ ВРЕМЕННОЙ ДИСКРЕТИЗАТОР | 0 |

|

SU394800A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптивный временной дискретизатор | 1985 |

|

SU1275477A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-01-30—Публикация

1990-06-15—Подача