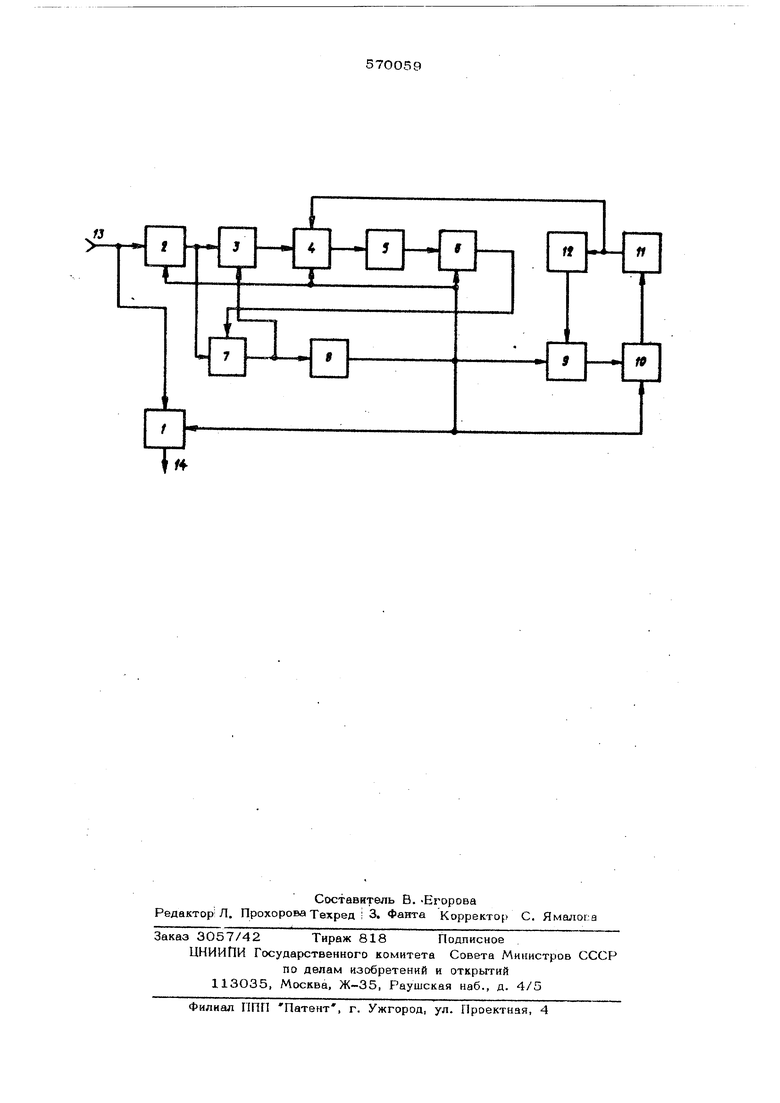

(54) АДАПТИВНЫЙ ВРЕМЕННОЙ ДИСКРЕТИЗАТОР ческий эпементИЛИ 10, генератор 11 пилообразного напряжения, пороговый элемент 12. На вход 13 подан входной сигнал, выход ной сигнал снимается с вьрсода 14. Принцип работы дискретизатора заключае ся в следующем. С начального момента времени ( t 0) разность между текущим значением сигнала S {t) и начальным для данного интервала дискретизации значением сигнала S (О) с блока памяти 2 поступает через вычитагель 3 на делитель 4, где реализуется операция деления на текущее время t ; S{t)-s(o) -7 ) после чего через ограничитель 5 и интегратор 6 поступает на вычитатель 7. В результате такого,преобразования исходного сигнала получаем на вьрсоде вы- читателя 7-оценку погрешности кусочно линейной аппроксимации 5 : (t)-sco)-fMblMlidr , о где t - переменная, интегрирования. При этом дискретнзатор работает в основ ном режиме интерполятора первого порядка. Далее величина & поступает на блок сравнения 8 а в качестве обратной связи на делитель 4 через вычнтатель 3. При достижениии заданной в блоке сравнения 8 величины допустимой погрешности аппроксимации на его выходе появляется CHrHaflf который поступает на второй вход ключа 1 и на аходы блока 2, делитель 4, интегратор 6, триггер 9 и элемент 10. На выходе ключа 1 появляется отсчетное значение сигнала, после чего начинается новый цикл измерения погрешности аппроксимации. Если величина )) , - . . t достигает порога ограничения ограничителя 5, что соответствует быстрому изменению 5 (О. то на вход интегратора начинает поступать постоянное напряжения Cfg-j и в дальнейшем величина о определяется как разность между S(t)S(0)H пилообразным напряжением с интегратора т.а. схема переходйт в режим предсказателя первого порядка. Если же оценка погрешности не успе вает достичь отсчетного уровня, что возможно при постоянном или медленноменяюшемся 5 { t), до того, как напряжение генер тора 11 достигает уровня срабатывания поро гового элемента 12, то импульс последнего перебрасывает триггер 9, при этом генератор 11 запирается через элемент ИЛИ 1О напряжением с триггера 9, что соответствует максимальному )фициенту усиления делителя 4. Интегратор охватывается глубокой отридательной обратной связью, напряжение на его выходе стремиться к нулю, при этом S определяется как разность 9 3(1)-5(0), устройство переходит в режим предсказааля нулевого порядка. При появлении очередного отсчетного имульса триггер принимает исходное состояние, переводя устройство в его основной режим интерполятора первого порядка. В предлагаемом дискретизаторе увеличивается точность при работе в основном режиме интерполятора первого порядка благодаря возможности уменьшения кратности деления делителя,увеличивается коэффициент сжатия системы, т.е. ее эффективность на постоянных или медленно изменяющихся сигналах. Формула изобретения Адаптивный временной дискретизлтор, содержащий управляемый ключ, первый вход которого соединен с первым входом блока памяти и источником входного сигнала, элэ; мент сравнения, выход которого соединен со ; вторыми входами управляемого ключа и блока памяти, генератор пилообразного напряжения, выход которого через пороговый элемент соединен с одним входом триггера, второй вход которого подключен к выходу элемента сравнения, отличающийся тем, что, с целью повышения точности временной дискретизации, в него введены два вьгчитателя, делитель, ограничитель, интегратор и элемент. ИЛИ, причем первые входы вычитателей под-ключены к выходу блока памяти, выход первого вычитателя соединен через последовательно включенные делитель, ограничитель и интегратор со вторым входом второго вьгчитателя, выход которого соединен со вторым входом первого вьяитателя и входом элемента сравнения, при этом первьтйвход элемента ИЛИ и вторые входы делителя и интегратора соедине- ныс выходом элемента сравнения, а третий вход делителя соединен с вьгходом генератора пилообразного напряжения, причем второй вход элемента ИЛИ подсоединен с выходом триггера, а выход элемента ИЛИ подключен-ко входу генератора пилообразного напряжения. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство № 394800, кл. G 06, G- 7/02, 1973. 2.Патент Японии 20904, кл. 11ОК12, 1967.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный временной дискретизатор | 1978 |

|

SU721826A1 |

| Адаптивный временной дискретизатор | 1976 |

|

SU577668A1 |

| Адаптивный временной дискретизатор | 1981 |

|

SU1005301A2 |

| Устройство для сжатия информации | 1982 |

|

SU1056244A1 |

| Адаптивный временной дискретизатор | 1986 |

|

SU1401500A1 |

| Устройство для сжатия данных | 1987 |

|

SU1522268A1 |

| Линейный аппроксиматор | 1983 |

|

SU1157548A1 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| Устройство для вычисления функций | 1978 |

|

SU679991A1 |

| Аналого-цифровой низкочастотный фазометр | 1990 |

|

SU1780042A1 |

Авторы

Даты

1977-08-25—Публикация

1976-04-28—Подача