1

Изобретение относится к вычислительной технике и может быть использовано в информационно вычислительных системах и автоматизированных системах управления.

Известны генераторы векторов для сиотемы отображения графической информации, х;одержащие приемный регистр, быходы приращений координат которого подключены ко входам коммутатора, а выходы знаков приращений -. ко входам управления реверсом счетчиков координат, выходы которых соединены с цифро-аналоговыми преобразовате- пями„ счетные входы - с выходами цифрового интерполятора, а эходы блокировки счета- соответстБенно с первым и вторым выхода-ми коммутатора, третий выход которого подключен к управляющему входу (цифрового ннтерпопятора и через элемент ИЛИ . ко вхогДУ генератора тактовых импульсов, перв85й выход которого соединен через распредели гбль импульсов со входами цифрового интерполатора, группы вентилей и элементы И. Генератор векторов содержит также по. стоянное запоминающее |устр ойство, предкаэначенное для записи и хранения койов тан

jFeHCOB углов воспроизводимых линий. Наличие постоянного запоминающего устройства не соответствует требованию единой элемент ной базы, усложняет {устройство в целом , повышает его стоимость. При этом построение длинных векторов из нескольких корот. ких, соединяемых последовательно, требует большей памяти ЭВМ, увеличивает число обрашаннй к ЭВМ и усложняет программирование. Поэтому необходимо иметь возможность ш 1черчивать длинные векторы по одному значению координаты приращения, а не сумме приращений коротких векторов. Увеличение же разрядности адресов (L .Д- ) постоянного запоглинаюшего устройства увеличивает емкость постоянного запоминающего устройства и количество оборудования, применяемого для его возбуждения. Так, например, при П разрядных адресах постоянного запоминакхцего устройства число возможных углоц а значит и значений тангенса только для ут пов с фиксированной одной стороной, pajlR&A максимальному приращению, составит z. откуда емкость постоянного запоминакхцего .устройства для этих значений - Ti;Z бит.

Это иекоторая часть требуемой емкости постоянного запоминающего yf;тpoйc1 s,a,

UeJib изобретения . таростить генератор и сократить избыточность нн формации при о&г. мене с внешкз ми устройствами,g

Это достигает-ся тем, что генератор со. держит 1ШФРОВОЙ блок делений, состоящий из регистра дел1мого й репютра делителя, вь ходь прямого и обратного кода которого™ подключены через соответствугощие группы |0 вентилей ко входам регистра делимого, знйг ковые выходы которого соединены с одними иа входов элементов И, причем вторЪй . ход генератора тактовых икшуто сов подклкь чен ко входам одной из групп вентилей, а |g 1третий к импуль-сному входу цифрового нн- терполятор 1 и другим входам элементов И, выход одного из которых соединен со дами группы вентилей, а выход дру того эле. И «- с дополните .льны м тжодом расгфеделителя импульсов.

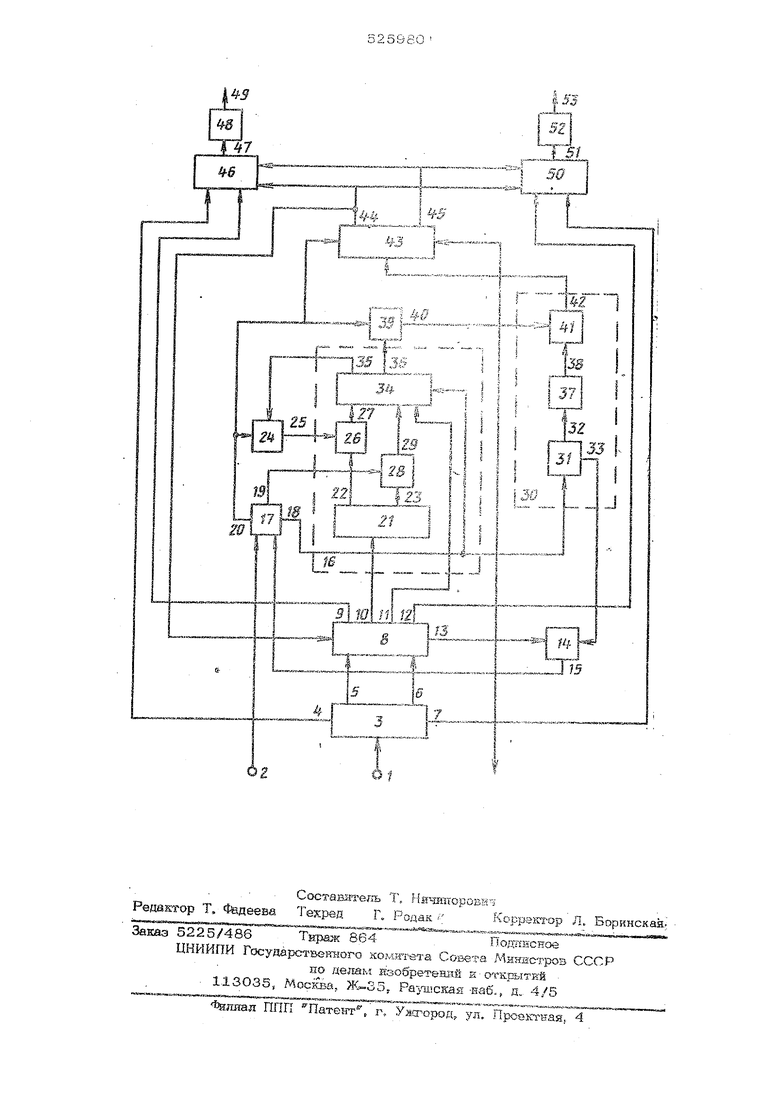

На чертеже дана блок-схема предлагае мого генератора векторов, где 1 - вход ко, ординат прирашений вектора; 2 - вход за- пускающего имг ульса; 3 - приемгый рбггистрй§ 4 -. выход знака ттрираьчения д к ; 5 . вы« ходы .разрядов .ярирашеиия Д х ; 6 - вьгхо ды разрядон5 npiipaJueiUiH . л v; 7 выход ; знака прирашония ; 8 - .мугатор при, ращений координат; 9 вы-цоц коммутатора, 30 управляющий приемом в коорди1штгп:.й счет. чик X . , импульсного кодш Д X. с выходов цифрового интерполятора; 10 « выходаг большого пркраще 1ия; 11 выходы меньиюго прирашеиия; 12 - выхоя коммггатора, лчтрав-ЗЗ ляющий Приемо:-( в кооршпгатшзШ , число,имггульсного кода Av с выходов цифррвогО интерполатора; 13 выкоя призна ка конца вектора; 14 - собнрател ;;ная схема ИЛИ; 15 - выход собиратеяьн-ой скемы.; 16 Ю цифровой бгюк деления; 17 «-- генератор та.товых импульсов; 18 - выход нервог-о гак. тового импульса генератора таЕтоЕ4 гк пыиушу сов; 19 - выход второго тактового .импульса генератора тактовых импупьсов; 2О -. выход ® третьего тактового .кмаупьса генератора тактовых: импульсов; 21 « регдатр дегштеля; 22 ,выходы прямого кояа делителя: 23 -. выхошл обратного кода делителя; 24 « зло мент И; 25 «« вытсод элемента ; 26 груа- па вентилей прямого кода делйте гя; ходы вентилей прямого кода делителзз; 28 . группа вентилей обратного кода делителя; 29 V- выходы: вентилей обратт ого кода делИ тепя ЗО .-. распределитвга:з импуяьсов iiocne™ доватеявного кода частного; 31 32 - выходы всех разрядов счетчика;-33 « выход счетчика, соответствующий получению всех разрядов частного; 34 регистр дедк- мого- сумматор; 35 -- единичный выход зна.

ковогх разряда сумматора; 36 . нулевой вы- код знакового разряда сумматора; 37 - де шифгштор распределителя импупьсов частного, 38 « выходы дешифратора; 39 . элемент И; 40 «. выход элемента И; 41 группа венти яей Лля выходов дешифратора рас1тр1 делителя импульсов час-тного; 42Г выход;./ вентилей дешифратора; 43 щгфровой интерполятс ; 44 выход число- нм1тульского кода больше-,

ГО прнршцетаяГЧ гагход чис11&-импульс - . ного кода меньшего прирашения; 46 . ре™ версивньгй координаты к; 47 - выходы реверсивнох о счетчика координаты х-) ; 48 цифрхэ налоговый преобразователь координаты ; ; 49 . выход цифро- налогово го преобразователя координаты х ; 50 . ; реверсйвггый счетчик координаты V; 51 етлходы реверсивного счет-чика координаты V; 52 цифрО -.анапоговый преобразователь кооршзнаты -з; 53 выход цкфро--ана, яогоБого преобразователя координаты У,

Приемный регистр 3 предназначен для : хранегшя приращений координат вектора и их знаков на в}эемя построения вектора. Выхо- Шл 4 к 7 приемного регистра 3 управляют реверсом коорди штных счетчиков 46 и 50 соответственно. Г3ы.ходь 5 и 6 приемного регистра1 выдак т параллельный двоичный код прирашений . , Коммуа атор 8 при} ашенйй коор;шнат сравнивает коды приращений координат и по выходу 10 выдает код болы-пего приращения в регистр делите i ля 21, .цифрового блока 16 деления, а по выходу 11 выдает код меньшего приращения/ в регистр делнмога сумматор 34 цифрового блока 18 деления. Еыходы 9 и 12 комму- татора прирашений 8 управляют приемом реверсивным счс-гъ-як. 46 координаты х ji реверсивным счетчиком 50 координаты у число -импульсных кодов приращений именно своей координаты. Выход 13 коммутатора 8 выдает импульс по скончании построеш1я вектора, Собиратега- над схема ИЛИ 14 предназначена для на своем выходе 15 импульса, по которому заканшвается процесс деления в цифровом блоке 16 деления, Цнфровой блок 16 деления предназначен для де ления меньшего прираш.ения на больлюе и получения последовательного кода частного. Генератор 17 тактовых импульсов предназначен для получения импульсов, управляющих П}х цессом деления, Р егистр 21 дели теля предназначен для .хранения значения большего прирашения. Выходьг 22 регистра 21 предназначчЭ1а1 для выдачи прямого кода большего прираиленн.Л. Выходы 23 регистра 21 предназначены для выдачи обратного кода бо гьшего тоиращения. Элемент И 24 и группа вентилей 26 предназначена для пода 435 в регистр делимого-сумматер прямого ко да дедителя с целью восстаноьлб)ш; ucr, если результат в сумматоре иослз очареднсIf о . вычитание; делителе:; из ср тгутого на разряд впево а;:ачекия деянмГ6г 6 оказался I отрицательным. Группа вентилей 28 хгредна значена для во втором такте .цжаш деления обратного кода делителя в регистрсумматор 34 делимого, гястр-сумматор 34 делимого предназ начен для сложения значения делимого с прямым или обратным кодом делителя в висймости от выходов 35 и 36 знакового разряйй. Элемент И 39 предназначен для. получения на его выходе 40 поспедователь« ного кода частного. Распределитель нмпуль сов последовательного кода частного ЗО состоит из счетчика 31, дехяяфрат-ора 37, пы венталей 41 и предназначен для подачи импульсов кода частногО( следующкк начй ная со старшего разряда, в соответстБующие разряды регистра цифрового интерполятора 43. Цифровой интерполятор 43 выдает на вьь ходе 44 гшсдо-импульсный код большего прхь ращения постоянной частоты, не зависеоцей от вегшчннь приращения, и на выходе 45 число-импульсный код меньшего приращения, равномерно распределенный на отрезке вре- мени, необходимом для .преобразования кода большего прирашения. Реверсивные счетчики координат 46 и 50 к цифро-аналоговые прю- образователи 48 и 52 цредназначены для преобразования числа.импульснъ х кодов при ращений координат с выходов 44 н 45 в ступенчатое линейно изменяющееся напряз 1еа ние на выходах 49 и 53, Устройство работает след; 1ощим образом. По входу 1 в приемный регистр 3 запи™ сываются коды приращенш« коорш кат векто ра и их зна1ш. Значения прирашений с ъыу.о-дов 5 и 6 приемного регистра 3 в парал дельном коде вьшаклся ка коммутатор 8 Приращений. Коммутатор 8 прирашений сравнивают приращений и по вьссодам 1О всегда выдает код большего приращениЯ; а по выходам 11 код меньшего прнрашения. Выходы 9 и 12 коммутатора 8 приращеш й определя1Ш какое именно из приращений MeHbmeej а какое большее. Код бо.яьшего при ра1дения с выходов 10 записывается в р&« гйстр 21 делителЯд а код мешэшего прира-щенияС выходов 11 записывается, в-регкстр делимого- Сумматор 34. С прнходом затгуска юшего импульса по входу 2 запускается г-енератор 17 тактовых импульсов,° Первый тактовый имп7у71ьс с выкода 18 генератора 17 тактовых импульсов сдвига ет делимое в сумматоре 34 tia окии разр.в.д влево и записывает единиц-у г, счетчик 31 распредел 5те11я 30 имттукьсов. Вгорой так--. гоБЫй импул1: с с зыхода 10 ге-нера ора 17 J riiZiiSi ii-uiyJIbCU;. i; Ji-luur ОбратНЫЙ КОД деяктеля через грукну вентилей 28 в cyiv матор 34. Если прн этом окажется, что сдвинутое значенме AeraiMoro в сумматоре больше делитедя, то в знаковом разряде сумматора будет записан О, что соответ етвует единицу ь старшем разряде частного, На элемент И 39 по нулевому Быксщу 36 знакового р азряда сумматора 34 будет выдано разрешегше, А по eKSHii4Kot.ry выходу . 35 зна1сового разряда сумматора 34 на эпе мент И 24 будет действовать запрет. Поэтому третий тактовый импульс с выхода 2 О через элемент И 39 поступит на входы грзилы вентилей 41, и через тот вешиль, который вторым своим исодом подсоединен. к едйнич71ому выходу дешифратора, а своим выходом ко входу ртаршего разряда perHCTw pa цифрового интерпол51тор)а , запишет единицу в этот разряд. Если же окажется, что после второго такта сдвинутое делимое меньн ше делителя, то в знаковом разряде сумматора будет записана 1 и на элемент И 39 н по выходу 36 будет выдан запрет и единица в соответствующий разряд регистра ш-1фрового интерполятора 43 не запишется. По выходу 35 будет действовать разрешение и третий тактовый икшупьс с выхода 2 О генератора 17 тактовых импульсов через эпе- мент И 24 а груп1ту вентилей 26 прямой код делителя в сумматор 37, что вызовет восстановление остатка в нем. Далее щпш получения очередного разряда част ного повторяется. Таким образом, частное последовательным кодом, начиная со старшего разряда, подается в соответствующие раэряды регистра цифрового;интерполятора. Работа цифроБ01Х) блока 16 деления 16 к цифрово) интерполятора 43 происходит одновременно. Это осуществляется запуском генератора цифрового интерполятора уже в первом цикле третям тактовым импульсом с вьжода 20 генератора 17 тактовых импульсов одновременно с записью в регистр цш} ; рового интерполятора старшего разряда часть, ного. С выхода 44 цифрового интерполятора 43 серия импульсов с частотой генератора цифрового интерполятора 43 будет поступать в один из реверсгшных счетчиков 46 или 5 О в зазисимостк от состояния выходов 9 и 12 коммутатора приращений 8, определяющих, какое из приращений больше. С вы- i хода 45 щ{фрового интерполятора 43 числоимпульсный зсод будет поступать в счетчик. Реверсок счетжков 46 и 50 управлякт БЫХО.ЦЫ 4 и 7 приемного регистра 3. При этом на выходах 49 и 53 цифро-анало- , говых преобразоватглей получается шнейнс (В уюншошееся ступенчатое напряжение. Ик пульсы с выхода 44 цифрового интерполятоijpa 43 постулают в коммутатор 8 приращ&ний, где каждый импульс уменьшает на едишаойгу значение большего приращения. После того, как оно станет равным нулю, коммутатор прирашений 8 импульсом с выхода 13 возвращает в исходное состояние цифровой интерполятор 43, посылает запрос на координаты следующего вектора и через собирательную схему ИЛИ 14 возвращает в исходное состояние цифровой блок 16 деления, ео ли до этого через второй вход собирательной схемы 14 цифровой блок 16 деления не Bejv нул в исходное состояние импульс с выхода 33 счетчика 31, соответствующий записи кода младшего разряда частного в регистр цифрового интерполятора 43. Формула изобретения Генератор векторов для системы отображения графической информации, содержащий пpиe tный регистр, выходы приращений координат которого подключены ко входам кол мутатора, а выходы знаков приращений - ко входам управления реверсом счетчиков коор. гдинат, выходы которых соединены с цифроаналоговыми преобразователями, счетные вхо ды - с выходами цифрового интерполятора, а входы блокировки счета - соответственно с первым и вторым выходами коммутатора, третий выход которого подключен к управляющему входу цифрового интерполятора и через элемент ИЛИ - ко входу генераторвл тактовых импульсов, первый выход кЪторогрсоединен через распределитель импульсов со входами цифрового интерполятора, группы вентилей и , элементы И, отличающимися тем, что, с целью упрощения генератора и сокращения избыточности информации при обмене с внешними устройствами, он содержит шф-. ровой блок деления, состоящий из регистра (делимого и регистра делителя, выходы прямого и обратного кода которого подключены через соответствующие группы вентилей ко входам регистра делимого, знаковые выходы которого соединены с одними из входов элементов И, причем второй выход генератора тактовых импульсов подключен ко входам одной из групп вентилей, а третий - к импульсному входу цифрового интерполятора и к другим входам элементов И, выход одного из которых соединен со входами другой группы Ьентилей, а выход другого элемента И - с дополнительным входом распределителя им- , пульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор векторов | 1981 |

|

SU1010646A1 |

| Цифровой интерполятор | 1976 |

|

SU651317A1 |

| Линейно-круговой интерполятор | 1982 |

|

SU1149218A1 |

| Устройство для определения аргумента вектора | 1986 |

|

SU1319024A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для вывода графической информации | 1978 |

|

SU752403A1 |

| Линейно-круговой интерполятор | 1984 |

|

SU1215090A2 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

Авторы

Даты

1976-08-25—Публикация

1974-05-17—Подача