Изобретение относится к автоматике, к цифровой вычислительной технике и предназначено для повышения функциональности, а также производительности цифровых вычислительных систем.

Известен матричный параллельный делитель целых беззнаковых двоичных чисел без восстановления остатка (An unsigned divider using non-restoring divide with uncorrected remainder: http://code-all.blogspot.com/2010/10/example-of-parallel-4-bit-divider-model.html). Он содержит матрицу размерности N X N управляемых одноразрядных полных сумматоров-вычитателей (CAS - Controlled Add/Subtract). Каждый из этих элементов представляет собой полный двоичный сумматор (fadd), имеющий вход для бита переноса из младшего разряда, выход бита переноса в старший разряд, два входа для однобитных аргументов, причем к одному из входов подключен двухвходовый логический элемент «Исключающее ИЛИ» (хог), позволяющий инвертировать значение подаваемого на его вход одноразрядного аргумента при подаче на второй вход управляющего сигнала логической «1» и пропускающий значение этого аргумента без изменения при подаче управляющего сигнала логического «0». Таким образом, логический элемент «Исключающее ИЛИ» играет роль управляемого инвертора, позволяющего полному двоичному сумматору работать в качестве вычитателя при подаче на его вход для бита переноса из младшего разряда логической «1» и инверсии одного из аргументов.

В пределах одной строки матрицы входы для бита переноса полных двоичных сумматоров соединяются с выходами бита переноса в старший разряд двоичных сумматоров, расположенных в строке правее, образуя сквозной канал переноса для N ячеек строки матрицы, которые образуют в совокупности N-разрядный полный сумматор. Управляющие входы N логических элементов «Исключающее ИЛИ» также объединяются и соединяются с входом бита переноса самого младшего полного сумматора в строке, обеспечивая, таким образом, способность N одноразрядных полных сумматоров в строке выполнять функцию N разрядного двоичного вычитателя.

Устройство является комбинационным и работает с 2⋅N-разрядным двоичным делимым (dividend) и N-разрядным двоичным делителем (divider), которые обычно удерживаются на время проведения операции в 2⋅N-разрядном и N-разрядном регистрах соответственно. Результат N-разрядное двоичное частное (quotient) и N-разрядный двоичный остаток (remainder) фиксируются в N-разрядных регистрах по окончанию операции деления. Перечисленные регистры обычно являются частью цифровой вычислительной системы, которая строится по синхронному принципу.

Следует также отметить, что параллельный делитель такого типа обычно работает с беззнаковыми модулями чисел, а вопросы знака результата и предотвращения деления на ноль решаются в таком случае отдельно.

Первая строка матрицы, представляющая собой N-разрядный управляемый двоичный сумматор-вычитатель, подключается своими входами одного из аргументов к старшим 2⋅N-1 разрядам делимого (поскольку старший разряд разряд знака двоичного числа, а делитель работает с модулями чисел). На входы второго аргумента через управляемый инвертор поступают N-разрядов делителя, причем на входы управления N-разрядного инвертора и вход бита переноса самого младшего полного сумматора в строке принудительно подается логическая «1», форсируя таким образом операцию вычитания N-разрядного делителя из старших N-разрядов делимого, начиная с 2⋅N-1 разряда.

На выходе N-разрядного двоичного сумматора-вычитателя первой строки матрицы формируется частная разница, старший разряд которой определяет ее знак. Управляемый N-разрядный двоичный сумматор вычитатель следующей строки матрицы подключается к младшим N-1 выходным разрядам сумматора-вычитателя первой строки, а на младший его разряд подается 2⋅N-2 разряд делимого. Через N-разрядный инвертор на входы второго аргумента этого сумматора вычитателя вновь подключаются разряды делителя. Управление инвертором и входом бита переноса сумматора вычитателя текущей строки через логический элемент отрицания «НЕ» осуществляется старшим разрядом N с выхода сумматора-вычитателя предыдущей строки. Управляемые сумматоры вычитатели всех последующих строк матрицы по индукции подключаются аналогично: входы к N-1 выходным разрядам сумматора вычитателя предыдущей строки, управление инвертором и входом бита переноса сумматора-вычитателя текущей строки осуществляется инвертированным старшим разрядом знака результата сумматора-вычитателя предыдущей строки. На вход младшего разряда сумматора - вычитателя текущей строки подается соответствующий младший разряд делимого, а через управляемый инвертор подключаются N разрядов делителя.

Принцип работы данного устройства похож на алгоритм привычного всем деления десятичных чисел на бумаге «уголком в столбик» и сводится к последовательным операциям вычитания. Упрощает этот алгоритм тот факт, что в двоичной системе счисления нет необходимости подбирать множитель для очередного разряда частного, поскольку возможны лишь два варианта: уменьшаемая часть старших разрядов делимого либо содержит в себе вычитаемый делитель, и тогда в очередной разряд частного записывается «1», либо делитель больше этой части старших разрядов делимого, и в очередной разряд частного записывается «0».

Если частный остаток после вычитания делителя из старших разрядов делимого содержит «0» в старшем разряде (старший вывод сумматора вычитателя в строке знак двоичного числа), то это значит, что частный остаток число положительное или ноль, следовательно, делитель содержался в старших разрядах делимого, в очередной разряд частного следует записать инверсию знакового разряда - «1». К частному остатку добавить со стороны младших разрядов следующую цифру делимого и продолжить операцию вычитания делителя, поскольку логическая «1» в разряде частного форсирует выполнение операции вычитания управляемым сумматором-вычитателем следующей строки.

Если же частный остаток после вычитания делителя из старших разрядов делимого содержит «1» в старшем разряде, то это значит, что частный остаток число отрицательное, следовательно, делитель меньше значения старших разрядах делимого, из которых он вычитался, следовательно, в очередной разряд частного следует записать инверсию знакового разряда «0». По привычной нам логике деления отрицательный остаток следовало бы «восстановить» до значения перед операцией вычитания, добавить к нему со стороны младших разрядов следующую цифру делимого и вновь продолжить операцию вычитания делителя из этого числа. Но особенность двоичной системы счисления позволяет нам выполнить следующее аппаратное упрощение, реализованное в схеме данного параллельного матричного делителя.

При делении без восстановления остатка используется тот факт, что каждый последующий делитель в два раза меньше предыдущего, поскольку сдвинут к младшему разряду добавляемого справа очередной цифры частного, а в двоичной системе счисления сдвиг числа в сторону его младших разрядов эквивалентен делению этого числа на два. Поэтому сложение делителя с последующим вычитанием его половины всегда будет совпадать с простым добавлением половины делителя. Таким образом, если старший разряд частного равен «1», то предыдущее значение делителя делится пополам и затем вычитается из частичного делимого для получения следующего разряда частного. Если же старший разряд частного равен «0», то делитель делится пополам и затем добавляется к частичному делимому для получения следующего разряда частного. Эта процедура продолжается до тех пор, пока не будет получено требуемое количество разрядов частного. Очевидно, что аппаратно двоичный параллельный матричный делитель реализует именно такой алгоритм «без восстановления остатка», поскольку если соответствующий разряд частного равен «0», то управляемый сумматор-вычитатель следующей строки матрицы включается на выполнение операции сложения, а делитель, подключенный к его младшим разрядам, фактически сдвигается вправо и складывается с частичным делимым.

Все инвертированные разряды знака в строках управляемых сумматоров вычитателей таким образом поразрядно формируют частное, а на выходе сумматора-вычитателя последней строки матрицы получается остаток. Он может быть отрицательным, и в этом случае для получения корректного значения остатка необходимо дополнительно сложить его с делителем.

К недостаткам матричного параллельного делителя целых беззнаковых двоичных чисел без восстановления остатка обычно относят высокую аппаратную сложность, но основным его недостатком в данном случае является его неспособность выполнять функцию деления троичных чисел, где дополнительным логическим уровнем является логическое состояние «НЕИЗВЕСТНО» («НЕ ОПРЕДЕЛЕНО»), потенциал которого соответствует половине положительного напряжения питания. Следует также сразу отметить, что и алгоритм, реализуемый схемой матричного параллельного делителя, не подходит для деления чисел троичной системы счисления, поскольку троичное число может содержаться в уменьшаемом и два раза, а сдвиг троичного числа в сторону младших разрядов эквивалентен делению его на три.

Известен четырехквадратный матричный делитель без сохранения остатка с индикацией переполнения и заключительной знаковой коррекцией (Рабинер Л., Гоулд Б. Теория и применение цифровой обработки сигналов. М: Мир, 1978. с. 580). Он содержит (Фиг. 8.37, с. 584): комбинационную матрицу суммирующих и вычитающих логических элементов (фактически в каждой строке матрицы управляемые сумматоры вы читатели, как и в схеме рассмотренного ранее матричного параллельного делителя). На вход схемы поступают 2⋅N-разрядное делимое и N-разрядный делитель, оба в дополнительном коде, а на выходе образуются N-разрядные частное и остаток. 2⋅N-разрядное двоичное делимое и N-разрядный двоичный делитель, также обычно удерживаются на время проведения операции в 2⋅N-разрядном и N-разрядном регистрах соответственно. Результат N-разрядное двоичное частное и N-разрядный двоичный остаток также фиксируются в N-разрядных регистрах по окончанию операции деления.

Матрица управляемых сумматоров-вычитателей реализована по тому же принципу, что и в случае рассмотренного ранее матричного параллельного делителя, но поскольку операция деления в данном случае выполняется над числами со знаком, в схему введены дополнительные логические элементы «Исключающее ИЛИ», контролирующие знак предыдущего частичного делимого и частного остатка. Для коррекции итогового результата деления в матрицу введен дополнительный сумматор вычитатель.

В основу работы матричной схемы положен метод деления без восстановления остатка, принцип которого полностью аналогичен рассмотренному ранее для матричного параллельного делителя. Практическая же реализация этого алгоритма для четырехквадрантного случая (когда приходится учитывать все возможные комбинации знаков делителя и делимого) требует введения дополнительных логических элементов «Исключающее ИЛИ». Основой матричного деления является последовательность этапов сложения и вычитания. На каждом этапе в зависимости от знаков частичного делимого и самого делителя производится либо сложение, либо вычитание соответствующего делителя из соответствующего частичного делимого. На матрицу может поступать любая комбинация знаков делителя и делимого, но в конце при определенных комбинациях необходима коррекция разрядов частного.

Вычисление разрядов частного на каждом этапе производится по следующим правилам:

1. Если текущее частичное делимое положительно, в соответствующий разряд частного записывается «1». В противном случае записывается «0».

2. Если делитель и текущее частичное делимое имеют одинаковые знаки, следующий пробный делитель нужно вычесть.

3. Если делитель и текущее частичное делимое имеют разные знаки, следующий пробный делитель следует добавить.

Если делимое положительно, то независимо от знака делителя частное будет правильным. Если делимое отрицательно, то независимо от знака делителя будет получен обратный код частного. Правильное значение частного в дополнительном коде получается после дополнительной коррекции, основанной на учете знаков операндов. Предположим, например, что делитель положительный, а делимое отрицательное. В этом случае отрицательное частное будет получено в обратном коде. Поэтому для перехода к дополнительному коду к результату необходимо добавить «1».

Если делитель и делимое отрицательны, то частное должно быть положительным. Но ответ будет получен в обратном коде, поэтому необходима простая инверсия разрядов частного. Во всех случаях коррекцию результата можно производить с помощью дополнительного этапа сложения (вычитания) на выходе матрицы. Лишь в одном случае коррекция не нужна - когда и делитель, и делимое положительные.

Коррекция осуществляется по следующим правилам.

1. Если и делитель, и делимое положительные, присвоить знаковому разряду частного значение «0» и ничего не делать со значащими разрядами.

2. Если и делитель, и делимое отрицательные, присвоить знаковому разряду частного значение «0» и проинвертировать значащие разряды.

3. Если делитель положительный, а делимое отрицательное, присвоить знаковому разряду значение «1» и добавить «1» в младший разряд частного.

4. Если делитель отрицательный, а делимое положительное, присвоить знаковому разряду значение 1, проинвертировать значащие разряды частного и добавить к нему 1.

Недостатками четырехквадрантного матричного делителя без сохранения остатка с индикацией переполнения и заключительной знаковой коррекцией являются повышенная аппаратная сложность и неспособность выполнять функцию деления троичных чисел, причем заложенный в его схеме алгоритм также не может быть использован для деления чисел троичной системы счисления.

В обеих рассмотренных схемах используется метод деления без восстановления остатка, который предполагает неявный сдвиг делимого относительно делителя посредством выполнения операций сложения/вычитания делителя с частным остатком, к которому добавляется очередная младшая цифра делимого со стороны его младшего разряда.

Следовательно, делители можно значительно упростить схемотехнически, оставив в схеме лишь один N-разрядный управляемый сумматор вычитатель, а сдвигать делимое относительно разрядов делителя - с помощью сдвиговых регистров соответствующей разрядности, поскольку в цифровой вычислительной системе, строящейся по синхронному принципу, регистры, так или иначе, используются для сохранения на время операции деления исходных данных и фиксации результатов деления.

Известна схема для беззнакового двоичного деления (Schematic logic circuit diagram for unsigned binary division: https://ebrary.net/206262/computer_science/division). Она содержит (FIGURE 7.11): (N+1)-разрядный управляемый параллельный полный двоичный сумматор («(n+l)-bit adder») способный выполнять функцию вычитания в арифметике дополнения до двух, имеющий специальный вход управления его функцией «Суммирование/Вычитание» («Add/Subtract»), к входам «слагаемого/вычитаемого» которого подключен (N+1)-разрядный параллельный регистр делителя М («Divisor (M)»), а к выходам старшими разрядами - 2»М-разрядный универсальный регистр делимого [А-Q] («Dividend [A-Q)]») с параллельной загрузкой и способностью к последовательному сдвигу влево в сторону старших разрядов, в младших разрядах которого в результате процедуры деления сформируется частное Q («Quotient (Q)»), а в старших - остаток А («Remainder (А)»). Функционирование схемы обеспечивает блок логики контроля, управления сдвигом и суммированием/вычитанием («Shift and add/subtract control logic»), на основе анализа входного сигнала старшего бита остатка А (представляющего собой знак остатка) вырабатывающий управляющие сигналы для управляемого параллельного полного двоичного сумматора вычитателя: «Суммирование/Вычитание» («Add/Subtract»), 2⋅N-разрядного универсального регистра делимого [A-Q]: «Сдвиг влево» («Shift left»), а также бит установки частного («Quotient setting»), устанавливаемый в процессе деления в младших разрядах частного Q.

Работает схема для беззнакового двоичного деления следующим образом. Перед началом процедуры деления цифровая вычислительная система, в состав которой входит данная схема деления, заносит параллельно в регистр делителя М значение положительного двоичного делителя, а в регистр делимого [A-Q] - значение положительного двоичного делимого так, что его значащие разряды попадают в младшую часть этого регистра, в которой будет накапливаться значение частного Q, а в старшую часть, соответствующую остатку А, - бит знака и дополнительные нулевые биты. Это значит, что процедура деления выполняется над модулями делителя и делимого, поскольку в их старших разрядах присутствует «0», а, следовательно, эти числа априори положительны. Вопросы определения знака результата и предотвращения деления на ноль решаются в этом случае также отдельно.

После того, как делимое и делитель занесены в соответствующие им регистры, схема управления разрешает сдвиг на 1 бит влево, в сторону старших разрядов, и в младшую часть регистра делимого [A-Q] (в разряды остатка А) вдвигается старший бит делимого. Поскольку старший бит остатка содержит значение «0», то есть, остаток положительный, блок логики контроля и управления активным сигналом «Суммирование/Вычитание» разрешает управляемому параллельному полному двоичному сумматору-вычитателю произвести вычитание значения делителя М из разрядов остатка А, причем результат вычитания записывается параллельно в биты остатка А. Далее схема продолжает работу циклически по следующим правилам, за исполнение которых отвечает блок логики контроля и управления, анализирующий старший бит знака остатка А.

1. Если знак остатка А равен «0» (остаток положительный), установить младший бит q0 частного Q в сдвиговом регистре делимого [A-Q] равным «1»; в противном случае установить младший бит q0 частного Q равным «0».

2. Если знак остатка А равен «0» (остаток положительный), сдвинуть регистр [A, Q] влево на 1 бит и вычесть делитель М из остатка А; в противном случае, если знак остатка А равен «1», сдвинуть регистр [A, Q] влево на 1 бит и прибавить значение делителя М к остатку А.

Вся процедура повторяется до тех пор, пока все значащие разряды делимого не будут сдвинуты в биты остатка А, и со значением остатка А будет произведено действие суммирования с числом делителя М или же вычитания последнего. В результате в младшей части сдвигового регистра делимого [A-Q] накопится значение частного Q, а в старшей части - значение остатка А.

Таким образом, данная схема выполняет процедуру беззнакового двоичного деления без восстановления остатка. Алгоритм деления практически такой же, как и схеме матричного делителя, но реализуется не одновременно со всеми разрядами делимого и делителя, а циклически в результате побитных сдвигов регистра делимого, что приводит к значительному аппаратному упрощению схемы делителя, естественно, несколько увеличивая время деления.

Следует также отметить, что итоговое значение остатка может быть отрицательным, и в этом случае для получения корректного значения необходимо дополнительно сложить его с делителем.

Схема для беззнакового двоичного деления без восстановления остатка, является синхронной и схемотехнически весьма простой. Тем не менее, основным недостатком данной схемы, выбранной в качестве прототипа, является то, что она не способность выполнять функцию деления троичных чисел, и заложенный в ее основе алгоритм также не может быть непосредственно использован для деления чисел троичной симметричной системы счисления.

Технической проблемой заявляемого технического решения является создание аппаратно простой схемы беззнакового делителя, способного выполнять функцию деления целых троичных чисел в симметричной троичной системе счисления.

Технический результат заключается в повышении производительности цифровых вычислительных систем, имеющих в своем составе заявляемую схему беззнакового делителя, и расширении их функциональных возможностей без значительного аппаратного усложнения.

Технический результат достигается тем, что последовательный делитель троичных целых чисел, согласно изобретению, содержит блок логики контроля, управления сдвигом и суммированием/вычитанием, управляемый полный сумматор-вычитатель, к входам «слагаемого/вычитаемого» которого подключен параллельный регистр делителя, а к выходам старшими разрядами - 2⋅N-разрядные универсальные регистры, делимого с параллельной загрузкой и способностью к последовательному сдвигу влево, в сторону старших разрядов, в младших разрядах которого в результате процедуры деления сформируется частное, а в старших остаток, при этом все элементы выполнены на основе троичной логики, полный сумматор-вычитатель выполнен одноразрядным, регистр делителя с параллельной загрузкой и способностью к последовательному сдвигу вправо, в сторону младших разрядов, а 2⋅N-разрядные универсальные регистры делимого наряду с параллельной загрузкой и способностью к последовательному сдвигу влево обладают способностью к последовательному сдвигу вправо, при этом вычитание выполняется последовательно, сдвигом вправо регистров делителя и остатка через сумматор вычитатель, N-разрядный цифровой компаратор, счетчик циклов вычитания до двух, инвертор управляющего сигнала вычитания-сложения, троичный логический элемент «МАХ», триггер, хранящий результат предыдущей операции вычитания, и цифровые коммутаторы троичных логических сигналов, позволяющие в совокупности блоку логики контроля, управления сдвигом и суммированием/вычитанием осуществлять алгоритм деления троичных целых чисел.

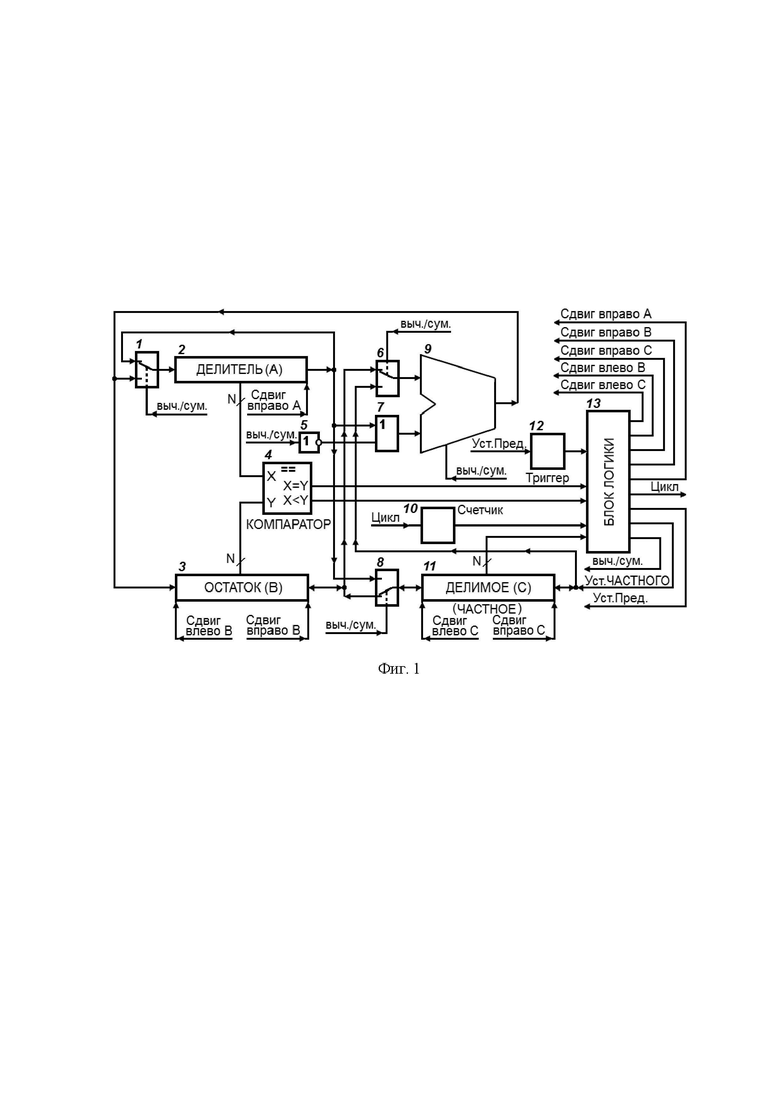

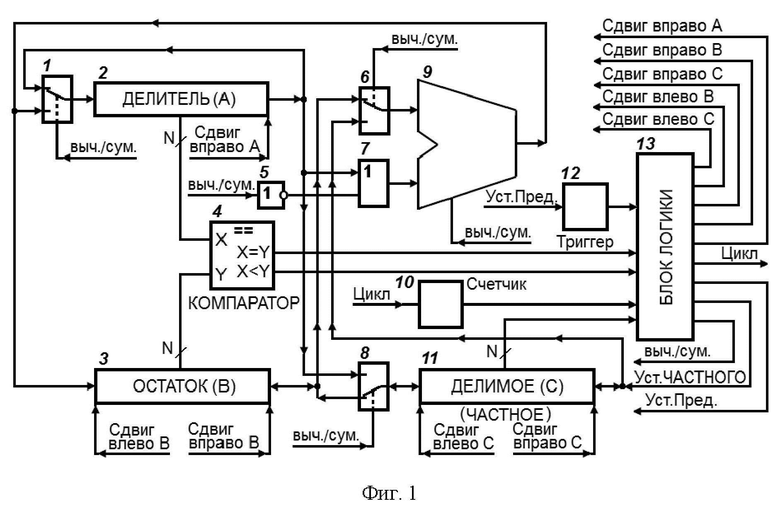

Изобретение поясняется чертежами, где на фиг. 1 приведена функциональная схема устройства; на фиг. 2 приведена принципиальная электрическая схема устройства.

На фиг. 1 приняты следующие обозначения.

1, 6, 8 - цифровой коммутатор троичных логических сигналов;

2 - «ДЕЛИТЕЛЬ (А)» - троичный N-разрядный регистр А с параллельной загрузкой и функцией сдвига вправо, содержащий значение делителя;

3 - «ОСТАТОК (В)» - троичный N-разрядный универсальный регистр В с параллельной загрузкой и функцией сдвига как вправо, так и влево, содержащий в результате выполнения операции значение остатка от деления;

4 «КОМПАРАТОР» троичный N-разрядный цифровой компаратор;

5 - инвертор управляющего сигнала вычитания-сложения («выч./сум.»);

7 - троичный логический элемент «МАХ» (http://elibrary.sgu.ru/VKR/2020/11-04-04_006.pdf), троичный аналог двоичного логического вентиля ИЛИ;

9 - троичный 1-тритный управляемый полный сумматор-вычитатель;

10 «Счетчик» счетчик циклов вычитаний до двух;

11 «ДЕЛИМОЕ (С)» троичный N-разрядный универсальный регистр С с параллельной загрузкой и функцией сдвига как вправо, так и влево, исходно содержащий значение делимого, а в результате выполнения операции деления - значение частного («ЧАСТНОЕ»);

12 «Триггер» триггер с динамическим управлением, хранящий результат предыдущей операции вычитания;

13 - «БЛОК ЛОГИКИ» - блок логики контроля, управления сдвигами и операциями суммирования вычитания;

«Сдвиг вправо А» - управляющий сигнал разрешения сдвига вправо регистра А;

«Сдвиг влево В» управляющий сигнал разрешения сдвига влево регистра В;

«Сдвиг вправо В» управляющий сигнал разрешения сдвига вправо регистра В;

«Сдвиг влево С» - управляющий сигнал разрешения сдвига влево регистра С;

«Сдвиг вправо С» - управляющий сигнал разрешения сдвига вправо регистра С;

«Цикл» управляющий сигнал подсчета циклов вычитания;

«выч./сум.» (вычитание/суммирование) управляющий сигнал выбора операции вычитания или сложения;

«Уст. ЧАСТНОГО» - сигнал установки значения очередного разряда частного;

«Уст. Пред.» - сигнал установки значения результата предыдущей операции вычитания.

Усложнение функциональной схемы последовательного делителя целых троичных чисел по сравнению с двоичным прототипом вызвано тем, что троичное число делителя может содержаться в уменьшаемой части делимого два раза, что потребовало выполнения подсчета циклов вычитания отдельным счетчиком и хранения результата предыдущей операции вычитания в дополнительном триггере предварительного результата. Особенность троичной симметричной системы счисления, заключающаяся в том, что значение цифры в отдельном разряде числа зависит от цифр в старших разрядах (к примеру, число 2 выглядит как +1 в старшем разряде и -1 - в младшем, т.е. 3-1=2), привела к необходимости реализации оригинального алгоритма формирования очередной цифры частного. Вместе с тем введение в схему троичного цифрового компаратора позволило повысить производительность делителя, блокируя выполнение циклов вычитания, в которых уменьшаемая часть делимого заведомо меньше значения делителя.

Последовательный делитель целых троичных чисел, функциональная схема которого приведена на фиг. 1, содержит управляемый троичный полный одноразрядный сумматор-вычитатель 9 к входу «слагаемого/вычитаемого» которого через троичный логический элемент «МАХ» (троичный аналог ИЛИ) подсоединен младшим разрядом N-разрядный регистр делителя 2 с параллельной загрузкой и способностью к последовательному сдвигу вправо; ко второму входу сумматора-вычитателя 9 через цифровой коммутатор троичных логических сигналов 6 подключен младшим разрядом регистр остатка 3, который через цифровой коммутатор 8 соединен также с регистром делимого 11, образуя 2⋅N-разрядный универсальный регистр с параллельной загрузкой и способностью к последовательному сдвигу влево в сторону старших разрядов, каждая из N-разрядных частей которого способна независимо осуществлять сдвиг вправо в сторону младших разрядов. Выход полного сумматора вычитателя 9 соединен со старшим разрядом регистра остатка 3, в то же время младший разряд регистра делителя 2 через цифровой коммутатор 1 соединен со своим старшим разрядом так, что в результате N сдвигов вправо регистра делителя 2 и регистра остатка 3 в последнем будет содержаться разность его первоначального содержимого и значения в регистре делителя 2, тогда как регистр делителя 2 опишет полный циклический сдвиг и его значение не изменяется.

К N выводам регистра делителя 2 и к N выводам регистра остатка 3 подключен параллельно N-разрядный троичный цифровой компаратор 4, сравнивающий их значения и выдающий блоку логики контроля, управления сдвигом и суммированием/вычитанием 13 сигналы, свидетельствующие о том, что значение делителя 2 в качестве вычитаемого меньше или равно значению уменьшаемой части делимого, находящегося в регистре остатка 3.

Блок логики контроля, управления сдвигом и суммированием/вычитанием 13 на основе этих сигналов принимает решение о разрешении или запрещении текущей операции вычитания, которая, безусловно, разрешается, если вычитаемое значение делителя меньше значения уменьшаемой части делимого. В этом случае, подав N импульсов управления сдвигом вправо («Сдвиг вправо А» и «Сдвиг влево В») регистрам делителя 2 и остатка 3, блок логики контроля сигналом «ТАКТ» увеличивает значение счетчика циклов вычитаний до двух 10, и если цикл первый, то устанавливает сигналом «Уст. Пред.» значение подключенного к нему триггера 12, хранящего результат предыдущей операции вычитания. Если же цикл вычитания второй, то блок логики контроля 13, проанализировав значения подключенных к нему счетчика циклов вычитаний до двух 10 и триггера 12, выставляет в подключенный к нему младший разряд регистра делимого 11 очередную цифру частного по линии «Уст. ЧАСТНОГО», и выдает регистру делимого 11 и регистру остатка 3 сигналы разрешения сдвига влево («Сдвиг влево С» и «Сдвиг влево В»), в сторону старших разрядов, по которым очередная цифра частного заносится в регистр делимого 11 со стороны младших разрядов, а его старший разряд через цифровой коммутатор 8 поступает в младший разряд регистра остатка 3, образуя новое значение уменьшаемого для делителя 2.

Блок логики контроля, управления сдвигом и суммированием/вычитанием 13 подключен также по линии управления выбором операции вычитания или сложения («выч./сумм.») к трем цифровым коммутаторам 1, 6, 8 и управляющему входу полного одноразрядного сумматора вычитателя 9, так что инверсия этого сигнала логическим инвертором 5 запирает троичный логический вентиль «МАХ» 6, и он выдает на соответствующий вход полного одноразрядного сумматора-вычитателя логический уровень «+1», что необходимо для заключительного цикла коррекции результата деления согласно реализуемому устройством алгоритму деления троичных целых чисел.

Последовательный делитель целых троичных чисел работает следующим образом. Перед началом процедуры деления цифровая вычислительная система, в состав которой входит заявляемый делитель, заносит параллельно в троичный N-разрядный регистр делителя А 2 значение положительного троичного делителя, а в троичный N-разрядный универсальный регистр С 11 - значение положительного троичного делимого, троичный N-разрядный универсальный регистр остатка В 3 инициализируется нулевым значением. Счетчик циклов вычитаний до двух 10 устанавливается в состояние логической «-1», и триггер 12, хранящий результат предыдущей операции вычитания, также инициализируется значением «1». Здесь и далее значения логических сигналов приводятся в алфавите троичной симметричной системы счисления, согласно которому троичному логическому значению «1» соответствует логический «0» двоичной системы счисления, троичному логическому значению «+1» соответствует логическая «1» двоичной системы счисления, а троичному логическому значению «0» соответствует потенциал половины питающего напряжения. Таким образом, алфавит двоичной логики является подмножеством троичного, и двоичные логические элементы могут использоваться в троичной схемотехнике в тех случаях, когда они оперируют лишь значениями и «-1» троичной логики.

В начале операции деления блок логики контроля, управления сдвигом и суммированием/вычитанием 13 выставляет активный управляющий сигнал разрешения операции вычитания («выч./сумм.»), по которому полный одноразрядный сумматор вычитатель 9 переключается в режим вычитания, цифровой коммутатор 1 закольцовывает троичный N-разрядный регистр делителя А 2 в режим циклического сдвига, цифровой коммутатор 6 подключает младший разряд регистра остатка В 3 к входу полного одноразрядного сумматора-вычитателя 9, цифровой коммутатор 8 соединяет старший разряд троичного N-разрядного регистра делимого С 11 с младшим разрядом троичного N-разрядного универсального регистра остатка В 3, позволяя таким образом осуществлять одновременный сдвиг этих регистров влево, как единого 2⋅N-разрядного последовательного регистра сдвига. Инверсия управляющего сигнала разрешения операции вычитания «выч./сумм.» с выхода логического инвертора 5 открывает троичный логический вентиль «МАХ» 7, пропускающий сигнал с младшего разряда троичного N-разрядного универсального регистра делителя А 2 на второй вход полного одноразрядного сумматора-вычитателя 8, позволяя таким образом осуществлять операцию поразрядного вычитания значения делителя из значения старших разрядов делимого, сдвинутых к началу операции вычитания в регистр остатка В 3. При одновременном сдвиге регистров делителя А 2 и регистра остатка В 3 по сигналам управления сдвигом вправо «Сдвиг вправо А» и «Сдвиг вправо В» от блока логики контроля 13 результат вычитания потритно поступает с выхода полного одноразрядного сумматора-вычитателя 9 в старший разряд регистр остатка В 3, где после N импульсов управления сдвигом формируется N-разрядная разность значения старших разрядов делимого и значения делителя.

Поскольку в начале операции деления регистр остатка В 3 содержит нулевое значение, а значение в регистре делителя А 2 больше нуля, N-разрядный цифровой компаратор 4, сравнив их значения, выдает блоку логики контроля, управления сдвигом и суммированием/вычитанием 13 сигналы, свидетельствующие о том, что значение делителя 2 в качестве вычитаемого больше значения уменьшаемой части делимого, находящегося в регистре остатка 3. Блок логики контроля, управления сдвигом и суммированием/вычитанием 13 блокирует текущую операцию вычитания, сигналом «Цикл» увеличивает значение счетчика циклов вычитаний до двух 10, оставляя без изменения содержимое триггера 12, переходит ко второму циклу вычитания. Поскольку значения в регистре делителя 2 и в регистре остатка 3 не изменились, N-разрядный цифровой компаратор 4, сравнив их значения, вновь выдает блоку логики контроля и управления сдвигом и суммированием/вычитанием 13 сигналы, свидетельствующие о том, что значение делителя 2 в качестве вычитаемого больше значения уменьшаемой части делимого, находящегося в регистре остатка 3.

По завершению двух циклов вычитания по счетчику циклов вычитаний до двух 10, вне зависимости от того, были разрешены операции вычитания или нет, блок логики контроля, управления сдвигом и суммированием/вычитанием 13 формирует по выходу «Уст. ЧАСТНОГО» значение очередной цифры частного, которая вдвигается в регистр делимого С 11 со стороны младших разрядов после подачи сигналов разрешения сдвига влево 18 «Сдвиг влево С» и 17 «Сдвиг влево В»), старший разряд регистра делимого С 11 через цифровой коммутатор 8 поступает в младший разряд регистра остатка В 3, образуя новое значение уменьшаемого для делителя 2.

В связи с особенностью троичной симметричной системы счисления, заключающейся в том, что значение цифры в отдельном разряде числа зависит от цифр в старших разрядах (к примеру, число 2 выглядит как +1 в старшем разряде и 1 - в младшем, т.е. 3 1=2), при формирований очередной цифры частного блок логики контроля, управления сдвигом и суммированием/вычитанием 13 реализует оригинальный алгоритм, заключающийся в том, что цифры частного заносятся в регистр делимого С 11 в алфавите троичной несимметричной системы «0», «1», «2», что соответствует «-1», «0», «+1» троичной симметричной системы счисления. Алгоритм позволяет упростить схемотехнику троичного делителя, поскольку исключает при сдвиге влево операцию коррекции значений старших разрядов частного в регистре делимого С 11 при возникновении такой необходимости, но при этом каждый разряд частного записывается в сдвиговый регистр на единицу меньшим своего истинного значения, что требует заключительного цикла коррекции результата поразрядным сложением всех тритов со значением «+1», во время которого будут выполнены все необходимые для троичной симметричной системы счисления межразрядные переносы.

При реализации данного алгоритма блок логики контроля, управления сдвигом и суммированием/вычитанием 13 оперирует следующими логическими соотношениями:

• если результат вычитания на первом такте, сохраняемый на выходе триггера 12, равен «+1», и вычитание на втором такте было разрешено (цифровой компаратор 4 выдал сигналы, свидетельствующие о том, что значение в регистре делителя А 2 не больше уменьшаемого в регистре остатка В 3), то в частное вдвигается «+1» («2» в троичной несимметричной системе счисления);

• если результат вычитания на первом такте, сохраняемый на выходе триггера 12, равен «+1», а вычитание на втором такте было заблокировано по сигналам цифрового компаратора 4, то в частное вдвигается «0» («1» в троичной несимметричной системе счисления);

• если оба перечисленных выше условия не выполняются, то в частное вдвигается «-1» («0» в троичной несимметричной системе счисления).

Следует отметить, что в том случае, когда цифровой компаратор 4 выдает сигнал о равенстве значений в регистре делителя А 2 и в регистре остатка В 3, блок логики контроля, управления сдвигом и суммированием/вычитанием 13 тестирует старшие разряды регистра делимого С 11 с целью проверки, не образуется ли при сдвиге в регистр остатка В 3 отрицательное уменьшаемое на следующем цикле вычитания. В таком случае операция вычитания также блокируется.

После того как вдвигаемый разряд частного определен согласно приведенному выше алгоритму, блок логики контроля, управления сдвигом и суммированием/вычитанием 13 выдает сигналы разрешения сдвига влево («Сдвиг влево В» «сдвиг влево С»), старший разряд регистра делимого С 11 через цифровой коммутатор 8 поступает в младший разряд регистра остатка С 3, образуя новое значение уменьшаемого для делителя А 2. Управляющим сигналом «Цикл» значение счетчика циклов вычитаний до двух 10 устанавливается равным «1», а по сигналу «Уст. Пред.» триггер 12, хранивший результат предыдущей операции вычитания, также сбрасывается в «-1». Последовательный делитель целых троичных чисел готов к следующему этапу из предполагаемых двух циклов вычитаний.

Если N-разрядный цифровой компаратор 4, сравнив значения в регистрах делителя А 2 и остатка В 3, выдает блоку логики контроля и управления сдвигом и суммированием/вычитанием 13 сигналы, свидетельствующие о том, что значение делителя в регистре А 2 в качестве вычитаемого меньше значения уменьшаемой части делимого, находящегося в регистре остатка В 3, блок логики контроля, управления сдвигом и суммированием/вычитанием 13 разрешает текущую операцию вычитания, сигналами управления сдвигом вправо «Сдвиг вправо А» и «Сдвиг вправо В» осуществляя сдвиг регистров делителя А 2 и регистра остатка В 3, производя тем самым операцию вычитания посредством одноразрядного сумматора вычитателя 9 и занося результат вычитания потритно в старший разряд регистра остатка В 3, где после N импульсов управления сдвигом формируется N-разрядная разность значения старших разрядов делимого и значения делителя. Сигналом «Цикл» блок логики контроля 13 увеличивает значение счетчика циклов вычитаний до двух 10, фиксируя факт первого цикла вычитания, и по сигналу «Уст. Пред.» записывает значение «+1» в триггер 12, запоминая результат первого цикла вычитания, после чего переходит ко второму циклу вычитания.

Если же N-разрядный цифровой компаратор 4, сравнив значения в регистрах делителя А 2 и остатка В 3, выдает блоку логики контроля и управления сдвигом и суммированием/вычитанием 13 сигналы, свидетельствующие о том, что значение делителя в регистре А 2 в качестве вычитаемого превышает значение уменьшаемой части делимого, находящегося в регистре остатка В 3, цикл вычитания блокируется, сигналом «Цикл» значение счетчика циклов вычитаний до двух 10 увеличивается, но в триггере 12 записанное ранее значение «-1» не изменяется.

Во втором цикле N-разрядный цифровой компаратор 4, сравнив значения в регистрах делителя А 2 и остатка В 3, вновь выдает блоку логики контроля, управления сдвигом и суммированием/вычитанием 13 сигналы, свидетельствующие об их соотношении, в результате чего блок логики контроля, управления сдвигом и суммированием/вычитанием 13 либо разрешает текущую операцию вычитания, проведя ее аналогично тому, как это было сделано в первом цикле, либо запрещает ее. Но, так или иначе, завершив второй цикл, блок логики контроля 13 формирует по выходу «Уст. ЧАСТНОГО» значение очередной цифры частного, которая вдвигается в регистр делимого С 11 со стороны младших разрядов после подачи сигналов разрешения сдвига влево «Сдвиг влево В» и «Сдвиг влево С», старший разряд регистра делимого С 11 через цифровой коммутатор 8 поступает в младший разряд регистра остатка 3, образуя новое значение уменьшаемого для делителя 2.

Таким образом, после N сдвигов 2⋅N-разрядного последовательного регистра сдвига, состоящего из регистров делимого С 11 и остатка В 3, в регистре делимого С 11 формируется значение частного от деления, но в алфавите троичной несимметричной системы счисления «0», «1», «2», а в регистре В 3 - значение остатка от деления. В этот момент блок логики контроля, управления сдвигом и суммированием/вычитанием 13 изменяет управляющий сигнал разрешения операции вычитания «выч./сум.» на разрешение операции сложения. Инверсия этого сигнала с выхода логического инвертора 5 закрывает троичный логический вентиль «МАХ» 7, в результате чего он подает сигнал логической «+1» на второй вход полного одноразрядного сумматора вычитателя 9, переключенного сигналом «выч./сум.» в режим сложения. Этот же сигнал переключает цифровые коммутаторы 1, 6, 8, вследствие чего младший разряд регистра остатка В 3 цифровым коммутатором 6 отключается от входа полного одноразрядного сумматора вычитателя 9, а младший разряд регистра делимого С 11, в котором находится частное от деления в алфавите троичной несимметричной системы счисления «0», «1», «2» подключается к этому входу полного одноразрядного сумматора вычитателя 9. Младший же разряд регистра делителя А 2 цифровым коммутатором 8 подключается к старшему разряду регистра делимого С 11, а к старшему разряду регистра делителя А 2 цифровым коммутатором 1 подключается выход полного одноразрядного сумматора-вычитателя 9.

После произведенных коммутаций блок логики контроля, управления сдвигом и суммированием/вычитанием 13 выдает сигналы разрешения сдвига вправо регистру делителя А 2 и регистру делимого С 11 («Сдвиг вправо А» и «Сдвиг вправо С »), осуществляя сдвиг регистров делителя А 2 и регистра делимого С 11, выполняя тем самым поразрядную операцию сложения посредством одноразрядного сумматора-вычитателя 9 разрядов регистра делимого С 11 со значением «+1» и занося результат сложения потритно в старший разряд регистра делителя А 2, где после N импульсов управления сдвигом формируется скорректированное значение N-разрядного частного в троичной симметричной системе счисления, а значение N-разрядного делителя из регистра А 2 без изменения сдвигается в регистр делимого С 11, на чем операция последовательного деления целых троичных чисел завершается.

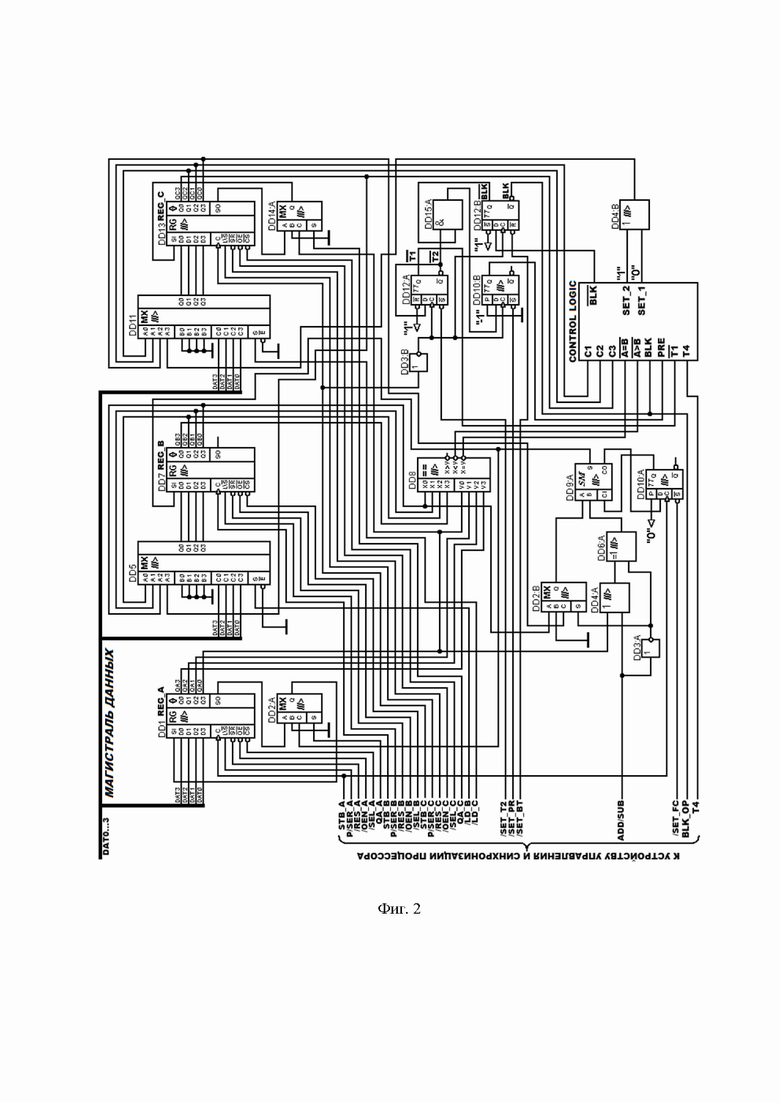

С целью апробирования заявляемого технического решения в программном пакете САПР был разработан проект четырехразрядного последовательного делителя целых троичных чисел на основе цифровых моделей троичных логических элементов (Семенов А.А., Дронкин А.С. Модели троичных логических элементов и их применение в схемотехнике процессоров // Взаимодействие сверхвысокочастотного, терагерцового и оптического излучения с полупроводниковыми микро- и наноструктурами, метаматерналами и биообъектами: Сборник статей девятой Всероссийской научной школы-семинара / под ред. проф. Ал.В. Скрипаля - Саратов: Изд-во «Саратовский источник», 2021. С. 31-36.), принципиальная электрическая схема которого представлена на фиг. 2.

Схема делителя включает в свой состав как троичные логические элементы, модели которых были разработаны авторами, так и обычные двоичные логические элементы там, где их функциональности достаточно. Троичные логические элементы обозначены на схеме знаком «III>», что соответствует «ГОСТ 2.743-91 ЕСКД Обозначения условные графические в схемах. Элементы цифровой техники. (http://docs.cntd.ru/document/gost-2-743-91-eskd)» - римская цифра «III» со стороны входов свидетельствует о том, что элементы работают с входными сигналами троичной логики, а стилизованная стрелка «>», указывающая на выходы элемента, подчеркивает тот факт, что выходные сигналы также троичные.

Четырехразрядный последовательный делитель целых троичных чисел был сконструирован как составная часть разрабатываемого авторами четырехразрядного троичного процессора, поэтому в схеме задействованы сигналы его микропрограммного устройства управления и синхронизации (УУС), причем акцент делался на то, чтобы микропрограмма была по возможности циклически повторяемой.

На схеме делителя фиг. 2 приняты следующие обозначения сигналов:

«STB_А» - Strobe А, тактовый сигнал (строб) регистра А;

«P/SER_A» - Parallel /Serial А, режим регистра А: параллельная загрузка /последовательный сдвиг (здесь и далее символ « / » обозначает низкий активный уровень сигнала);

«/RES_A» - /Reset А, начальная инициализация (сброс) регистра А;

«/OEN_А» - /Output Enable А, разрешение работы выходов регистра А;

«/SEL_А» - /Select А, выбор регистра А;

«QA_A» - выход Q соединен с входом А у мультиплексора, подключенного к регистру А;

«STB_В» - Strobe В, тактовый сигнал (строб) регистра В;

«Р/SER_В» - Parallel /Serial В, режим регистра В: параллельная загрузка /последовательный сдвиг;

«/RES_B» - /Reset В, начальная инициализация (сброс) регистра В;

«/OEN_В» - /Output Enable В, разрешение работы выходов регистра В;

«/SEL_B» - /Select В, выбор регистра В;

«STB_С» - Strobe С, тактовый сигнал (строб) регистра С;

«Р/SER_С» - Parallel /Serial С, режим регистра С: параллельная загрузка /последовательный сдвиг;

«/RES_C» - /Reset С, начальная инициализация (сброс) регистра С;

«/OEN_С» - /Output Enable С, разрешение работы выходов регистра С;

«/SEL_С» - /Select С, выбор регистра С;

«QA_C» - выход Q соединен с входом А у мультиплексора, подключенного к регистру С;

«/LD_B» - /Load В, переключить мультиплексор на параллельную передачу информации с магистрали данных на входы регистра В;

«/LD_C» - /Load С, переключить мультиплексор на параллельную передачу информации с магистрали данных на входы регистра С;

«/SET_Т2» - /Set Time 2, установить счетчик циклов вычитаний на второй цикл;

«/SET_PR» - /Set Previous, установить начальное значение триггера, хранящего предыдущий результат вычитания;

«/SET_ВТ» - /Set Block Trigger, установить начальное значение вспомогательного триггера, хранящего признак блокировки операции вычитания в текущем цикле;

«ADD/SUB» - Add /Subtract, управляющий сигнал сложения/вычитания;

«/SET_FC» - /Set Flag Carry, установить начальное нулевое значение триггера флага переноса полного однотритного сумматора вычитателя;

«BLK_ОР» - Block Operation, признак блокировки операции вычитания в текущем цикле (входной сигнал для УУС);

«Т4» - Tact 4, сигнал четвертого такта операции вычитания;

«/T1» - /Time 1, сигнал первого цикла операции вычитания;

«/T2» - /Time 2, сигнал второго цикла операции вычитания;

«BLK» - Block, сохраняемый признак блокировки операции вычитания в текущем цикле;

«/BLK» - /Block, инвертированный сохраняемый признак блокировки операции вычитания в текущем цикле;

«DAT0…DAT3» - D AT АО…DAT A3, линии данных магистрали данных по старшинству: от младшего разряда - к старшему;

«QA0…QA3» - QUIT AO…QUIT A3, выходные сигналы регистра делителя А по старшинству: от младшего разряда - к старшему;

«QB0…QB3» - QUIT_B0…QUIT B3, выходные сигналы регистра остатка В по старшинству: от младшего разряда - к старшему;

«QC0…QC3» - QUIT_СО…QUIT_С3, выходные сигналы регистра делимого С по старшинству: от младшего разряда - к старшему.

Элементы DD6.A, DD9.A, DD10.A образуют управляемый полный одноразрядный троичный сумматор вычитатель 8. Собственно, элемент DD9. А - полный одноразрядный троичный сумматор, D-триггер DD10.A - триггера флага переноса для следующего разряда, а троичный элемент XOR - DD6.A - является управляемым инвертором, инвертирующим входной сигнал и переключающим все устройство в режим вычитания по сигналу логической поступающему от УУС по линии «ADD/SUB», и в режим сложения - по сигналу Ко второму входу троичного элемента XOR подключен выход логического элемента DD4.A - троичного логического вентиля «МАХ» 6, управляемого инвертированным сигналом «ADD/SUB» через элемент DD3.A - логический инвертор 9. В режиме вычитания вентиль DD4.A пропускает вычитаемый сигнал без изменения, а в режиме сложения - выдает на соответствующий вход управляемого инвертора DD6.A логический уровень причем сам инвертор в этом режиме пропускает данный сигнал без изменения, в то время как в режиме вычитания он инвертирует сигнал с выхода вентиля «МАХ» 6 - DD4.А.

Троичный четырехразрядный универсальный регистр DD1 с параллельной загрузкой и способностью к последовательному сдвигу вправо, в сторону младших разрядов, выступает в роли регистра А 2 (Reg_А), содержащего значение четырехразрядного делителя. Своим младшим разрядом QA0 регистр подключен к входу элемента DD4.A - троичного логического вентиля «МАХ» 6, и для полного одноразрядного сумматора-вычитателя 8 он содержит вычитаемое число. Во время операции вычитания регистр DD1 закольцовывается через цифровой коммутатор 1, роль которого в схеме играет троичный мультиплексор DD2.A. В этом случае мультиплексор DD2.A соединяет последовательный выход SO («Serial Out» регистра DD1 с его последовательным входом SI («Serial In») по управляющему сигналу «QA_А», равному «+1» на входе S мультиплексора.

Троичный четырехразрядный универсальный регистр DD7 с параллельной загрузкой и способностью к последовательному сдвигу вправо, в сторону младших разрядов, в совокупности с четырехразрядным троичным мультиплексором DD5 образует регистр В 3 (Reg_В), содержащий значение четырехразрядного остатка. Мультиплексор DD5 в зависимости от управляющего сигнала «/LD_B» по входу S обеспечивает регистру DD7 возможность параллельной загрузки с магистрали данных по линиям Dat3…Dat0 или же последовательный сдвиг влево, в сторону старших разрядов, соединяя выходы QB2…QB0 регистра DD7 с его входами D0…D2, смещая таким образом записанное в регистре число влево и вводя через вход D3 новое значение младшего трита.

В режиме последовательного вычитания младший разряд QB0 регистра DD7 через цифровой коммутатор 5, роль которого в схеме играет троичный мультиплексор DD2.B, поступает на вход полного одноразрядного сумматора DD9.A, при этом значение в регистре DD7 выступает в качестве уменьшаемого. Выход полного одноразрядного сумматора DD9.A соединяется с последовательным входом SI («Serial In») регистра DD7, таким образом формируя в нем поразрядно значение разности при одновременном сдвиге регистров DD7 и DD1 вправо, в сторону младших разрядов.

Троичный четырехразрядный универсальный регистр DD13 с параллельной загрузкой и способностью к последовательному сдвигу вправо, в сторону младших разрядов, в совокупности с четырехразрядным троичным мультиплексором DD11 образует регистр С 11 (Reg_С), содержащий в начале операции деления значение четырехразрядного делимого, а по мере выполнения операции в этом регистре поразрядно накапливается значение четырехразрядного частного в алфавите троичной несимметричной системы счисления «0», «1», «2». Мультиплексор DD11 в зависимости от управляющего сигнала «/LD_С» по входу S обеспечивает регистру DD13 возможность параллельной загрузки с магистрали данных по линиям Dat3…Dat0 или же последовательный сдвиг влево, в сторону старших разрядов, соединяя выходы QC2…QC0 регистра DD13 с его входами DO…D2, смещая таким образом записанное в регистре число влево и вводя через вход D3 новое значение младшего трита с выхода логического вентиля «МАХ» DD4.B, входящего в состав блока логики контроля, управления сдвигом и суммированием/вычитанием 13, формирующего на выходе элемента DD4.B сигнал «Уст. частного». Старший разряд QC3 регистра DD13 подключен к входу A3 мультиплексора DD5, и при одновременном сдвиге регистров DD13 и DD7 влево значение разряд QC3 заносится в регистр DD7 через мультиплексор DD5 по входу D0 - со стороны младших разрядов. В момент одновременного сдвига четырехразрядных регистров DD13 и DD7 влево они работают как единый восьмиразрядный сдвиговый регистр.

Цифровой коммутатор 7, роль которого в схеме играет троичный мультиплексор DD14.А, в заключительном цикле коррекции частного поразрядным сложением всех тритов со значением «+1», во время которого выполняются все необходимые для троичной симметричной системы счисления межразрядные переносы, по управляющему сигналу «QA_C», равному «-1» на входе S мультиплексор DD14.A соединяет младший разряд QA0 регистра DD1 (Reg_A) с последовательным входом SI («Serial In») регистра DD13 (Reg_С). В то же время троичный мультиплексор DD2.B по сигналу логической «+1», поступающему от УУС по линии «ADD/SUB», соединяет выход младшего разряда QC0 регистра DD13 (Reg_С) с входом полного одноразрядного сумматора DD9.A, организуя таким образом тракт для поразрядного суммирования значения регистра DD13 (Reg_C) со значением на втором входе сумматора DD9.A.

По управляющему сигналу «QA_C» на входе S, равному мультиплексор DD14.A соединяет последовательный выход SO («Serial Out» регистра DD13 с его последовательным входом SI («Serial In»).

Четырехразрядный троичный цифровой компаратор 4, представленный на схеме как DD8, входами X3…X0 подключен к выходам QB3…QB0 регистра DD7 (Reg_B), а входами Y3…Y0 - к выходам QA3…QA0 регистра DD1 (Reg_A). Компаратор, как устройство комбинационной логики, непрерывно сравнивает значения, записанные в этих регистрах, и выдает блоку логики контроля, управления сдвигом и суммированием/вычитанием 13, сигналы «X<Y» и «X=Y», активные низким уровнем в случае выполнения указанных условий. Поскольку к входам компаратора X3…X0 подключены выходы регистра В, а к входам Y3…Y0 подключены выходы регистра А, блок логики контроля, обозначенный на схеме как "CONTROL LOGIC", интерпретирует данные входные сигналы как «А>В» и «А=В» - вычитаемое меньше уменьшаемого и вычитаемое равно уменьшаемому.

Счетчик циклов вычитаний до двух 10 выполнен на D-триггере двоичной логики DD12.А, инверсный выход /Q которого соединен с входом D, образуя счетный триггер. Функциональности двоичного триггера при счете циклов вычитаний до двух в данном случае вполне достаточно. Выходы Q и /Q счетчика выдают сигналы «/Т1» и «/Т2», активные низким уровнем, которые трактуются блоком логики контроля как признаки первого и второго циклов операции вычитания.

В качестве триггера с динамическим управлением «ТТ» 12, хранящего результат предыдущей операции вычитания, в схеме применен троичный D-триггер DD10.B с записью по фронту тактового сигнала.

В состав блока логики контроля, управления сдвигом и суммированием/вычитанием 13, входит блок комбинационной логики, обозначенный на схеме как "CONTROL LOGIC", в задачу которого входит принятие решений о блокировке очередного цикла вычитания на основе состояния входных сигналов и выдаче сигнала блокировки /BLK низкого уровня, а также формирование очередного трита частного выдачей логических сигналов SET_2 и SET1 уровней и «0» соответственно, из которых логический элемент «МАХ» DD4.B, также входящий в состав блока логики контроля 13, формирует на своем выходе сигнал «Уст. частного» уровней «-1», «0» и «+1», соответствующих значениям «0», «1», «2» в алфавите троичной несимметричной системы счисления.

В состав блока логики контроля, управления сдвигом и суммированием/вычитанием 13, входит также D-триггер двоичной логики DD12.B, сохраняющий на своих выходах признак разрешения операции вычитания (инвертированные сигналы «BLK» и «/BLK») на время цикла этой операции. Это необходимо, поскольку во время последовательной операции вычитания сигналы на входах X3…X0 и Y3…Y0 троичного цифрового компаратора DD8 непрерывно меняются, и это может вызвать ложные срабатывания блока логики контроля "CONTROL LOGIC" по недостоверным сигналам «X<Y» и «X=Y», которые он анализирует корректно лишь по завершении операции вычитания в четвертом такте.

Логический элемент И двоичной логики DD15.А также является частью блока логики контроля, управления сдвигом и суммированием/вычитанием 13. Он принимает решение о предварительном результате вычитания по следующей логике: "если окончен первый цикл вычитания И он не был заблокирован", то в триггер 12 (DD10.B), хранящий результат предыдущей операции вычитания, следует записать логическое значение «+1», или «1» - в противном случае.

Четырехразрядный последовательный делитель целых троичных чисел работает следующим образом. По включению питания происходит начальная инициализация регистров DD1 (Reg_A), DD7 (Reg_B), DD13 (Reg_C) сигналами УУС «/RES_A», «/RES_В», «/RES_С» соответственно. Также УУС устанавливает начальные значения остальным элементам комбинационной логики в схеме. Сигналом «/SET_FC» устанавливается начальное нулевое значение триггера флага переноса DD10.A полного однотритного сумматора-вычитателя, чем обеспечивается корректное проведение последующей операции вычитания. Триггер DD10.B, хранящий предыдущий результат вычитания, сигналом «/SET_PR» устанавливается в логическое состояние «-1», счетчик циклов вычитаний DD12.A сигналом «/SET_Т2» устанавливается в логическое состояние, соответствующее второму циклу, а вспомогательный триггер DD12.B, хранящий признак блокирования цикла вычитания, сигналом «/SET_BT» устанавливается в состояние блокирования, поскольку по логике работы схемы делителя априори известно, что первый цикл вычитания будет заблокирован.

Делитель работает аппаратно с беззнаковыми модулями чисел, то есть с целыми положительными троичными значениями, а вопросы знака результата и предотвращения деления на ноль решаются в таком случае отдельно.

Сигналом «/SEL_C» УУС переводит регистр DD13 (Reg_C) в активное состояние, сигналом «Р/SER_С» высокого уровня переводит его в режим параллельной загрузки, сигналом «/LD_С» переключает мультиплексор DD11 на параллельную передачу информации с магистрали данных «DAT0…DAT3» на входы данных регистра С. По стробирующему сигналу «STB_C» от УУС данные, соответствующие значению делимого, заносятся в регистр С DD13.

Сигналом «/SEL_А» УУС переводит регистр DD1 (Reg_А) в активное состояние, сигналом «Р/SER_A» высокого уровня переводит его в режим параллельной загрузки. По стробирующему сигналу «STB_A» от УУС данные с линий «DAT0…DAT3» магистрали данных, соответствующие значению делителя, заносятся в регистр A DD1.

Сигналом «/SEL_В» УУС переводит регистр DD7 (Reg_В) в активное состояние, сигналом «Р/SER_B» высокого уровня переводит его в режим параллельной загрузки, сигналом «/LD_В» переключает мультиплексор DD5 на параллельную передачу информации с магистрали данных «DAT0…DAT3» на входы данных регистра В. По стробирующему сигналу «STB_B» от УУС с магистрали данных в регистр остатка В DD7 заносится нулевое значение, это, собственно, и определяет тот факт, что первый цикл вычитания будет блокирован, поскольку значение в регистре А априори больше значения в регистре В.

По сигналам УУС «/LD_B» и «/LD_C» высокого уровня мультиплексоры DD5 и DD11 переключаются, выполняя соединение входов данных регистров DD7 и DD13 так, чтобы при последующем стробе параллельной записи в эти регистры осуществлялся последовательный сдвиг влево, в сторону старших разрядов.

Для начала операции аппаратного деления, суть которой сводится к многочисленным операциям вычитания делителя из делимого, в том случае, если такие операции не блокируются, УУС сигналом «QA_A» высокого уровня по входу S мультиплексора DD2.A закольцовывает регистр DD1 для операции последовательного сдвига вправо к входу полного одноразрядного сумматора вычитателя 8. По сигналу УУС «QA_С» высокого уровня, поданному на вход S мультиплексора DD14.A, регистр DD13 также закольцовывается лишь для определенности логического состояния на его последовательном входе SI («Serial In»), поскольку во время операции вычитания его сдвиг вправо алгоритмом деления не предусмотрен. По сигналу УУС «ADD/SUB» низкого уровня мультиплексор DD2.B по входу S через инвертор DD3.A переключается на подачу сигнала младшего разряда QB0 регистра В DD7 на вход полного троичного сумматора DD9.A. Этот же сигнал с выхода элемента DD3.A включает вентиль XOR DD6.A в режим инверсии входного сигнала, что принуждает полный троичный сумматор DD9.A к выполнению операции вычитания. Сигнал УУС «ADD/SUB» низкого уровня устанавливается на входе троичного логического вентиля «МАХ» DD4.A, в результате чего он пропускает на вход вентиля XOR DD6.A сигнал QA0 младшего разряда регистра A DD1, что в итоге приведет к поразрядному вычитанию значения в регистре делимого А DD1 из значения, записанного в регистр остатка В DD7. Чтобы дальнейшие операции были возможны, УУС выдает активные сигналы «/OEN_А», «/OEN_В», «/OEN_С» регистрам A DD1, В DD7 и С DD13 соответственно, разрешая подачу записанных в них значений на их выходы, находящиеся до этого момента в высокоимпедансном состоянии.

Цифровой компаратор 4 (DD8) сравнивает значения, записанные в регистрах A DD1, В DD7, и выдает блоку логики контроля, управления сдвигом и суммированием/вычитанием 13, сигналы «X<Y» и «X=Y», свидетельствующие о том, что «А>В» и «А≠В» - вычитаемое больше уменьшаемого и оно не равно уменьшаемому. Поскольку это было известно заранее, и сигнал «BLK_ОР» установлен активным с выхода триггера DD12.В, УУС выдает блоку логики контроля сигнал четвертого такта операции вычитания «Т4», во время которого блок логики принимает решения о значении трита, сдвигаемого в частное, и о последующей возможности цикла вычитания.

На входе блока логики активны следующие сигналы: выход счетчика циклов вычитаний DD12.A высоким уровнем по входу «/Т1» свидетельствует о том, что заканчивается второй цикл вычитания, сигнал «BLK» высокого уровня свидетельствует о том, что этот цикл был заблокирован, то есть вычитания делителя не производилось. Сигнал низкого уровня на входе «PRE» с выхода триггера DD10.B, хранящего предыдущий результат вычитания, свидетельствует о том, что в предыдущем цикле вычитание также не проводилось. На основании этих данных блок логики контроля, управления сдвигом и суммированием/вычитанием 13 не может выставить активным ни сигнал «SET_1», так как не было первого успешного цикла вычитания, ни сигнал «SET_2», так как не было также и второго успешного цикла вычитания. В этом случае сигналы «SET_1» и «SET_2» остаются в низком уровне (логическое состояние «-1»), а логический элемент «МАХ» DD4.B, также входящий в состав блока логики контроля 13, формирует на своем выходе сигнал «Уст. частного» низкого уровня «1», что соответствует значению «0» в алфавите троичной несимметричной системы счисления. Логический элемент «МАХ» в троичной логике назван так именно по той причине, что выставляет на своем выходе большее из двух значений на входах, но в данном случае на обоих входах сигналы низкого уровня «-1».

УУС тактовыми сигналами «STB_B» и «STB_C», поданными одновременно, вдвигает значение сигнала «Уст. частного» низкого уровня «1» в регистр С DD13, а в регистр В DD7 - старший разряд регистра С DD13. Следует отметить, что этот разряд частного со значением «-1» является фиктивным и в итоге будет утерян, поскольку так осуществляется выравнивание значащих разрядов делимого на значащие разряды делителя, поскольку предварительно эта информация неизвестна.

Цифровой компаратор 4 (DD8) вновь сравнивает значения, записанные в регистрах A DD1, В DD7, и вновь выдает блоку логики контроля, управления сдвигом и суммированием/вычитанием 13, сигналы «X<Y» и «X=Y». Предположим, что они вновь свидетельствуют о том, что «А>В» и «А≠В» - вычитаемое больше уменьшаемого и оно не равно уменьшаемому.

В этом случае практически повторяются все действия, описанные ранее: триггер DD10.B, хранящий предыдущий результат вычитания, устанавливается в логическое состояние «1», счетчик циклов вычитаний DD12.A устанавливается в логическое состояние, соответствующее второму циклу, а вспомогательный триггер DD12.B, хранящий признак блокирования цикла вычитания, сигналом «/SET_BT» устанавливается в состояние блокирования. Блок логики контроля, управления сдвигом и суммированием/вычитанием 13 вновь вынужден сформировать на выходе логического элемента «МАХ» DD4.B, сигнал «Уст. частного» низкого уровня «-1», что соответствует значению «0» в алфавите троичной несимметричной системы счисления. По тактовым сигналам УУС «STB_В» и «STB_С», поданным одновременно, значение сигнала «Уст. частного» низкого уровня «-1» вдвигается в регистр С DD13, а в регистр В DD7 вдвигается старший разряд регистра С DD13. Этот разряд частного со значением «-1» уже является значащим, поскольку предварительно уже был выполнен сдвиг в регистр В DD7 старшего значащего разряда регистра С DD13.

Цифровой компаратор 4 (DD8) снова сравнивает значения, записанные в регистрах A DD1, В DD7, и снова выдает блоку логики контроля, управления сдвигом и суммированием/вычитанием 13, сигналы «X<Y» и «X=Y». Предположим, что в этот раз «А<В» и «А≠В» - вычитаемое меньше уменьшаемого и оно не равно уменьшаемому. Блок логики контроля, управления сдвигом и суммированием/вычитанием 13, проанализировав входные сигналы, снимает на выходе /BLK активный сигнал блокировки цикла вычитания, и он фиксируется вспомогательным триггером DD12.В по спаду тактового сигнала «STB_C», инвертированного элементом DD3.B, этот же сигнал переключает счетчик циклов вычитаний DD12.A в логическое состояние, соответствующее первому циклу.

Поскольку цикл вычитания разрешен сигналом «ВЬКОР», УУС переключает регистр остатка В DD7 сигналом «Р/SER_В» низкого уровня в режим последовательного сдвига вправо, в сторону младших разрядов. По тактовым сигналам УУС «STB_А» и «STB_B», подаваемым одновременно, регистры A DD1 и В DD7 последовательно сдвигаются, а полный одноразрядный сумматор-вычитатель 8, работающий в режиме вычитания, формирует на своем выходе их поразрядную разность, которая после четырех тактов сдвига группируется в регистре остатка В DD7. Регистр делителя A DD1 закольцован, поэтому в нем после четырех тактов сдвига восстановится его исходное значение.

В первом цикле вычитания запись в регистр частного С DD13 не предполагается, поэтому УУС деактивирует его, сняв «/SEL_С», но выдает активный строб «STB_С», и предупреждает блок логики контроля, управления сдвигом и суммированием/вычитанием 13 о необходимости принятия решения о возможности следующего цикла вычитания активным сигналом четвертого такта операции вычитания «Т4».

По стробу «STB_C», прошедшему через инвертор DD3.B, в регистре предварительного результата DD12.В фиксируется значение «+1», сформированное логическим элементом И DD15.А согласно логическому утверждению: "если окончен первый цикл вычитания И он не был заблокирован".

В этот же момент во время активного сигнала «Т4» цифровой компаратор 4 (DD8) сравнивает значения, записанные в регистрах A DD1, В DD7, и выдает блоку логики контроля, управления сдвигом и суммированием/вычитанием 13 сигналы «X<Y» и «X=Y». Предположим, что в этот раз «А=В» - вычитаемое равно уменьшаемому. Блок логики контроля, управления сдвигом и суммированием/вычитанием 13 при этом дополнительно анализирует входные сигналы старших разрядов регистра делимого С DD13 с входов С3, С2, С1, поскольку если известно, что в следующем цикле вычитания «А=В», то в регистре остатка В DD7 окажется нулевой результат, и при сдвиге следующего разряда регистра делимого С DD13 число в регистре остатка В DD7 может принять отрицательное значение. В этом случае операция вычитания блокируется во втором цикле и разрешается сдвиг очередного старшего разряда из регистра делимого С DD13.

Если же после первого цикла вычитания цифровой компаратор 4 (DD8) сигналами со своих выходов свидетельствует о том, что «А<В» и «А≠В» - вычитаемое меньше уменьшаемого и оно не равно уменьшаемому, то блок логики контроля 13 устанавливает на выходе /BLK сигнал разрешения цикла вычитания, и он фиксируется вспомогательным триггером DD12.B также по спаду тактового сигнала «STB_С», инвертированного элементом DD3.B, этот же сигнал переключает счетчик циклов вычитаний DD12.A в логическое состояние, соответствующее второму циклу.

Поскольку часть блока логики контроля 13, обозначенная на схеме как "CONTROL LOGIC", является устройством комбинационного типа, какие-то значения сигналов по выходам «SET_1» и «SET_2» будут им сформированы, и логический элемент «МАХ» DD4.B, выдаст на своем выходе какое-то значение сигнала «Уст. частного», но в данном случае этот сигнал не имеет значения, поскольку регистр делимого С DD13 деактивирован УУС сигналом «/SEL_C» высокого уровня, который в дальнейшем будет переключен УУС в низкий уровень в начале второго разрешенного цикла вычитания.

Второй цикл последовательного вычитания значения делителя в регистре A DD1 из значения, записанного в регистре В DD7, происходит так же, как уже было описано выше для первого цикла.

После того, как второй цикл вычитания завершается, УУС активирует сигнал «Т4», и блок логики контроля, управления сдвигом и суммированием/вычитанием 13 вновь формирует на выходе логического элемента «МАХ» DD4.B, сигнал «Уст. частного», исходя из следующих соотношений: сигнал высокого уровня на входе «PRE» с выхода триггера DD10.B, хранящего предыдущий результат вычитания, свидетельствует о том, что в предыдущем цикле вычитание закончилось успешно. Счетчик циклов вычитаний DD12.A высоким уровнем по входу «ЛТ» свидетельствует о том, что закончен второй цикл вычитания, а вспомогательный триггер DD12.B, хранящий признак блокирования цикла вычитания, сигналом по входу «BLK» подтверждает, что второй цикл вычитания был разрешен, и, следовательно, вычитание было проведено дважды. Согласно этой логике блок 13 "БЛОК ЛОГИКИ" выставляет сигнал «+1» по выходу «SET_2», что соответствует значению «2» в алфавите троичной несимметричной системы счисления. Сигнал «SET_1» при этом не активен, на его выходе удерживается логический сигнал «-1», поэтому логический элемент 6 «МАХ» DD4.B, выдаст на своем выходе значение сигнала «Уст. частного» равным «+1», как наибольшее из двух, поданных на его входы.

По тактовым сигналам УУС «STB_В» и «STB_С», поданным одновременно, сигнал «Уст. частного» высокого уровня «+1» вдвигается в регистр С DD13, как значащий разряд частного, а в регистр В DD7 вновь вдвигается старший разряд регистра С DD13.

Рассмотренная выше последовательность действий повторяется до тех пор, пока все четыре значащих разряда делителя из регистра С DD13 не окажутся сдвинутыми в регистр В DD7, в этом случае УУС по завершению последнего цикла вычитания изменяет последовательность подачи управляющих сигналов в такте «Т4». Поскольку в регистре В DD7 уже содержится истинное значение остатка от деления, сигнал УУС «STB_B» не подается, а по сигналу «STB_С» в регистр С DD13 вдвигается последнее значение сигнала «Уст. частного» с выхода элемента 6 «МАХ» DD4.B, при этом фиктивное значение «-1», записанное в самом первом цикле и достигшее старшего разряда регистра С DD13, теряется. После этого в регистре С DD13 содержится истинное значение частного от деления, но в кодировке троичной несимметричной системы счисления, что требует заключительного цикла коррекции результата деления.

С этой целью УУС сигналом «QA_A» низкого уровня по входу S мультиплексора DD2.A соединяет последовательный вход SI («Serial In») регистра A DD1 с выходом полного однотритного сумматора DD9.A, сигналом «QA_C» низкого уровня, поданного на вход S мультиплексора DD14.A последовательный вход SI («Serial In») регистра С DD13 соединяется с младшим разрядом QA0 регистра A DD1. И, наконец, по сигналу УУС «ADD/SUB» высокого уровня мультиплексор DD2.B по входу S через инвертор DD3.A переключается на подачу сигнала QC0 младшего разряда регистра С DD13 на вход полного троичного сумматора DD9.A. Этот же сигнал с выхода элемента DD3.A переключает вентиль XOR DD6.A в режим пропускания входного сигнала, что принуждает полный троичный сумматор DD9.A к выполнению операции сложения. В то же время сигнал УУС «ADD/SUB» высокого уровня на входе троичного логического вентиля «МАХ» DD4.A запрещает пропускать на вход вентиля XOR DD6.A сигнал QA0 младшего разряда регистра A DD1, и принудительно подает сигнал высокого уровня «+1», что в итоге приведет к поразрядному сложению значения частного в регистре делимого с «+1», в чем, собственно, и заключается итоговая коррекция результата деления к троичной симметричной системе счисления.

Сигналом «Р/SER_C» низкого уровня УУС переводит регистр С DD13 в режим последовательного сдвига вправо, в сторону младших разрядов. Поскольку регистр A DD1 уже был включен в режим последовательного сдвига вправо, то после одновременной подачи УУС четырех стробирующих сигналов «STB А» и «STB_С» в регистре A DD1 оказывается скорректированное поразрядным сложением с значение частного в троичной симметричной системе счисления, а в регистр С DD13 переносится значение делителя. С учетом того, что в процессорах аккумуляторной организации регистр А является привилегированным регистром результата, процесс деления на этом вполне логично заканчивается.

Подводя итог подробному описанию принципа работы четырехразрядного последовательного делителя целых троичных чисел, можно кратко сформулировать алгоритм его работы. Операция аппаратного деления сводится к многократным операциям вычитания делителя из старших разрядов делимого со сдвигом последнего в сторону старших разрядов. Вычитание выполняется последовательно поразрядным сдвигом уменьшаемого и вычитаемого в сторону младших разрядов через одноразрядный полный троичный сумматор-вычитатель, что упрощает схемотехнику устройства. Операция вычитания делителя из каждого отдельного значения старших разрядов делимого может быть выполнена дважды. Вычитание блокируется в том случае, когда значение делителя больше значения старших разрядов делимого, что может привести к отрицательному значению промежуточного остатка. Вычитание также блокируется в том случае, когда в результате его получается нулевое значение промежуточного остатка, но сдвиг следующих старших разрядов делимого сформирует отрицательное значение.

Формирование очередной цифры частного осуществляется в алфавите троичной несимметричной системы счисления «0», «1», «2» (этим цифрам соответствуют логические значения «0» и для того, чтобы избежать сложностей, связанных с взаимодействием разрядов частного в троичной симметричной системе счисления, и подчиняется простому правилу:

• если из старших разрядов делимого в текущем цикле произведено два вычитания делителя, то в очередной разряд частного вдвигается «2» (логическое значение

• если из старших разрядов делимого в текущем цикле произведено одно вычитание делителя, то в очередной разряд частного вдвигается «1» (логическое значение «0»);

• если оба перечисленных выше условия не выполняются, а, следовательно, не было произведено ни одного вычитания делителя из старших разрядов делимого, то в частное вдвигается «0» (логическое значение «1»).

Циклы вычитаний заканчиваются после того как в сторону старших разрядов сдвинуты все триты делимого, и в итоге они замещены тритами частного. Но поскольку каждый разряд частного в алфавите троичной несимметричной системы счисления «0», «1», «2» на единицу меньше своего истинного значения в троичной симметричной системе счисления, проводится заключительный цикл коррекции результата последовательным поразрядным сложением с посредством одноразрядного полного троичного сумматора вычитателя.

Реализация логических операций сравнения троичных чисел известна из современного уровня техники (Design of Reversible / Quantum Ternary Comparator Circuits: https://www.engineeringletters.com/issues_v16/issue_2/EL_16_2_01.pdf; Standard Ternary Logic: https://homepage.cs.uiowa.edu/~dwjones/ternary/logic.shtml), по этой причине схемотехника узла сравнения не описана подробно, поскольку не является предметом патентной заявки.

Возможности разработанного четырехразрядного троичного последовательного делителя значительно шире, чем у его ближайшего двоичного аналога. Он способен работать с числами в диапазоне от 0 до 40 в десятичной системе счисления, тогда как аналогичная схема четырехразрядного двоичного делителя способна делить числа без знака в диапазоне лишь от 0 до 15.

Схемотехнически разработанный вариант делителя более прост, поскольку для выполнения операции в нем используется лишь один полный сумматор-вычитатель.

Статистически в диапазоне рабочих значений делимого и делителя четырехразрядный троичный последовательный делитель, благодаря оригинальному алгоритму блокирования циклов вычитания, выполняет операцию деления в 90% случаев не более чем за 28 тактов и практически в 50% случаев - за 24 такта.

Аппаратная реализация операции деления в составе процессора повышает его быстродействие в целом, поскольку исключает циклы извлечения из памяти кодов операций и позволяет выполнить процедуру деления как единый процесс.

Аппаратно четырехразрядный троичный последовательный делитель в значительной мере унифицирован со схемой последовательного троичного умножителя, предложенной авторами ранее (Дронкин А.С., Семенов А.А. Троичный последовательный умножитель // Взаимодействие сверхвысокочастотного, терагерцового и оптического излучения с полупроводниковыми микро- и наноструктурами, метаматериалами и биообъектами: Сборник статей девятой Всероссийской научной школы-семинара / под ред. проф. Ал.В. Скрипаля - Саратов: Изд-во «Саратовский источник», 2022. С. 62-67.), что может позволить разработать в дальнейшем комбинированное троичное устройство умножения-деления.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Устройство для деления | 1989 |

|

SU1709301A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

Изобретение относится к автоматике, к цифровой вычислительной технике и предназначено для повышения функциональности, а также производительности цифровых вычислительных систем. Техническим результатом изобретения является аппаратное упрощение схемы беззнакового делителя, способного выполнять функцию деления целых троичных чисел в симметричной троичной системе счисления. Последовательный делитель троичных целых чисел содержит блок логики контроля, управления сдвигом и суммированием/вычитанием 13, управляемый полный сумматор–вычитатель 8, делитель 2, 2⋅N-разрядные универсальные регистры 3, 11 делимого с параллельной загрузкой и способностью к последовательному сдвигу влево, в сторону старших разрядов, в младших разрядах которого в результате процедуры деления сформируется частное, а в старших – остаток, N-разрядный цифровой компаратор 4, счетчик циклов вычитания до двух 10, инвертор управляющего сигнала вычитания–сложения 9, троичный логический элемент «MAX» 6, триггер, хранящий результат предыдущей операции вычитания 12, и цифровые коммутаторы троичных логических сигналов 1, 5, 7. Все элементы выполнены на основе троичной логики. 2 ил.

Последовательный делитель троичных целых чисел, характеризующийся тем, что содержит блок логики контроля, управления сдвигом и суммированием/вычитанием 13, управляемый полный сумматор-вычитатель 9, к входам «слагаемого/вычитаемого» которого подключен параллельный регистр делителя 2, а к выходам старшими разрядами - 2⋅N-разрядные универсальные регистры 3, 11 делимого с параллельной загрузкой и способностью к последовательному сдвигу влево, в сторону старших разрядов, в младших разрядах которого в результате процедуры деления сформируется частное, а в старших - остаток, при этом все элементы выполнены на основе троичной логики, полный сумматор-вычитатель 9 выполнен одноразрядным, регистр делителя 2 - с параллельной загрузкой и способностью к последовательному сдвигу вправо, в сторону младших разрядов, а 2⋅N-разрядный универсальные регистры 3, 11 делимого - наряду с параллельной загрузкой и способностью к последовательному сдвигу влево обладает способностью к последовательному сдвигу вправо, при этом вычитание выполняется последовательно, сдвигом вправо регистров делителя 2 и остатка 3 через сумматор-вычитатель 9, N-разрядный цифровой компаратор 4, счетчик циклов вычитания до двух 10, инвертор управляющего сигнала вычитания сложения 5, троичный логический элемент «МАХ» 7, триггер, хранящий результат предыдущей операции вычитания 12, и цифровые коммутаторы троичных логических сигналов 1, 6, 8, позволяющие в совокупности блоку логики контроля, управления сдвигом и суммированием/вычитанием 13 осуществлять алгоритм деления троичных целых чисел.

| ТРОИЧНЫЙ ПОРАЗРЯДНЫЙ УМНОЖИТЕЛЬ | 2016 |

|

RU2631166C1 |

| ДРОНКИН А.С., СЕМЁНОВ А.А | |||