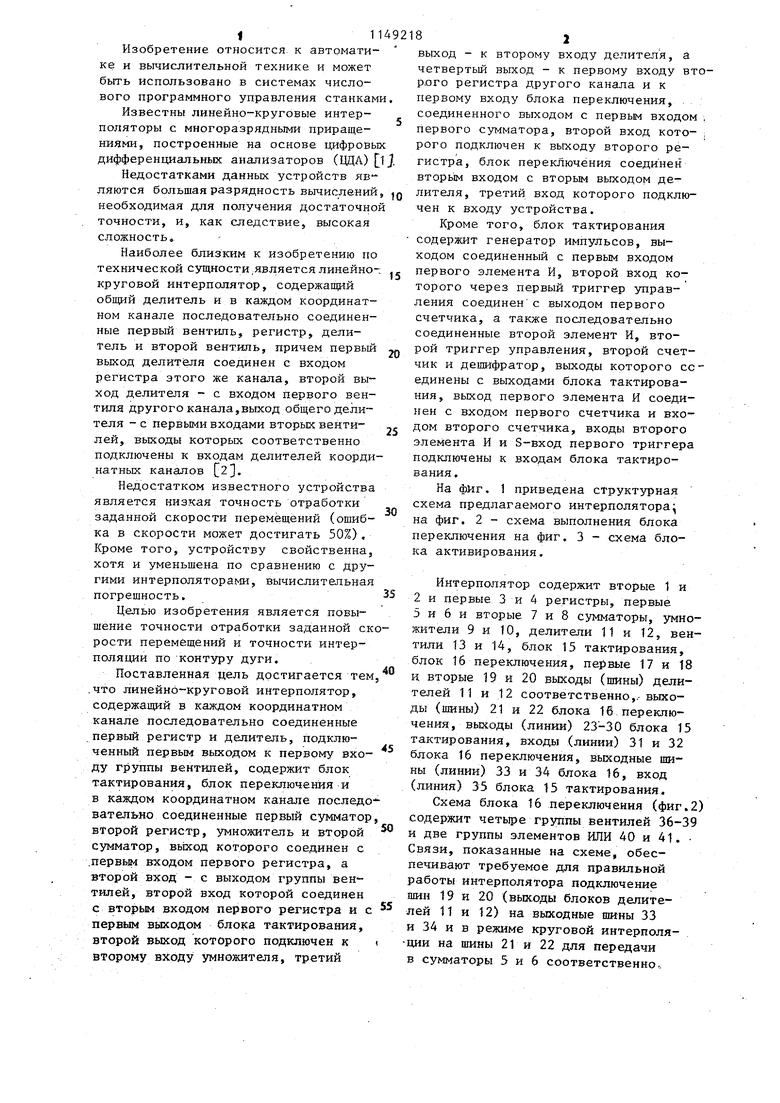

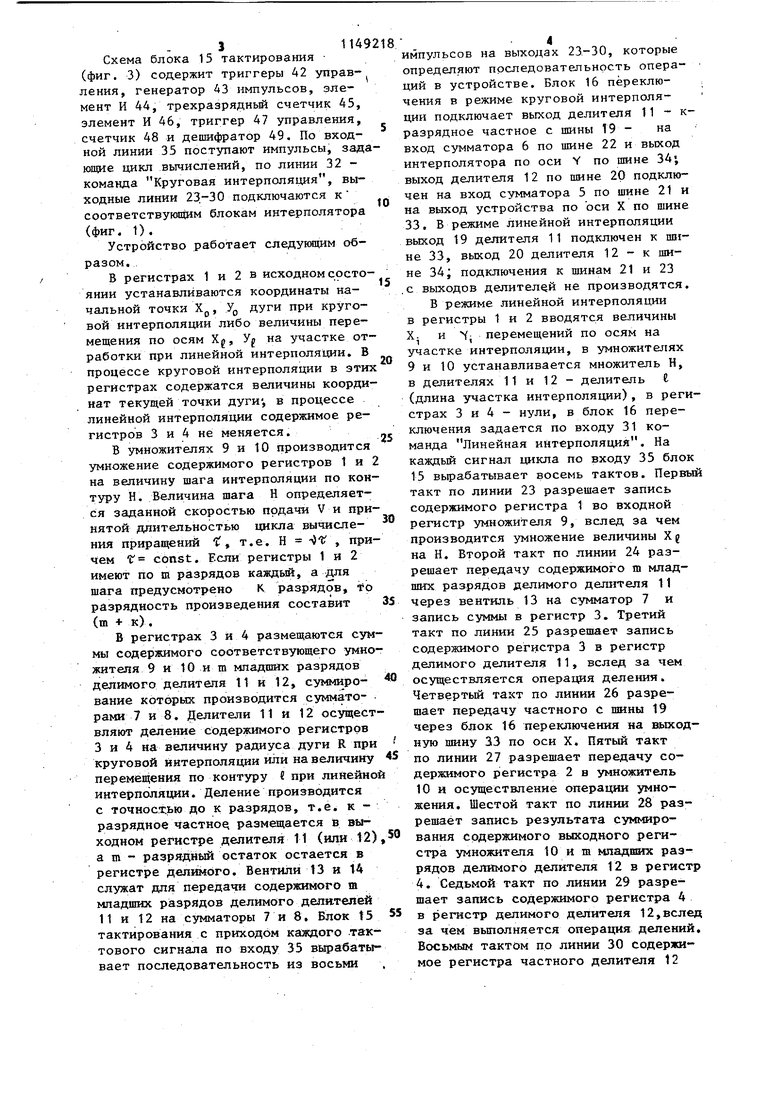

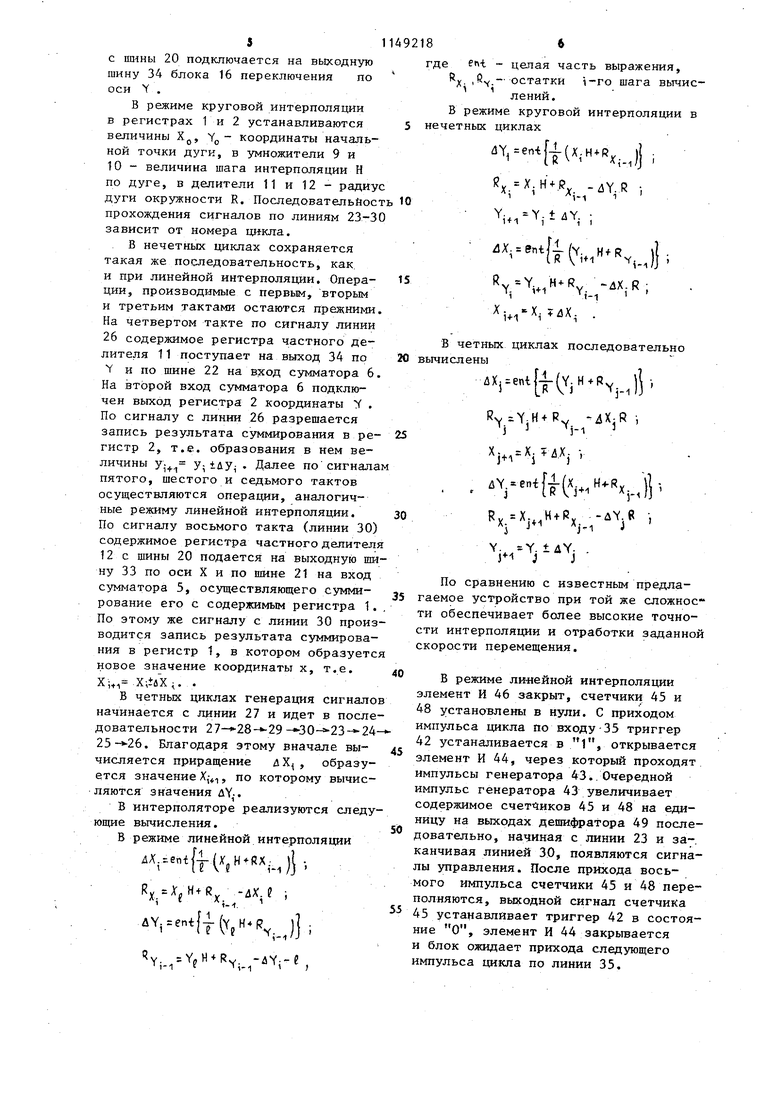

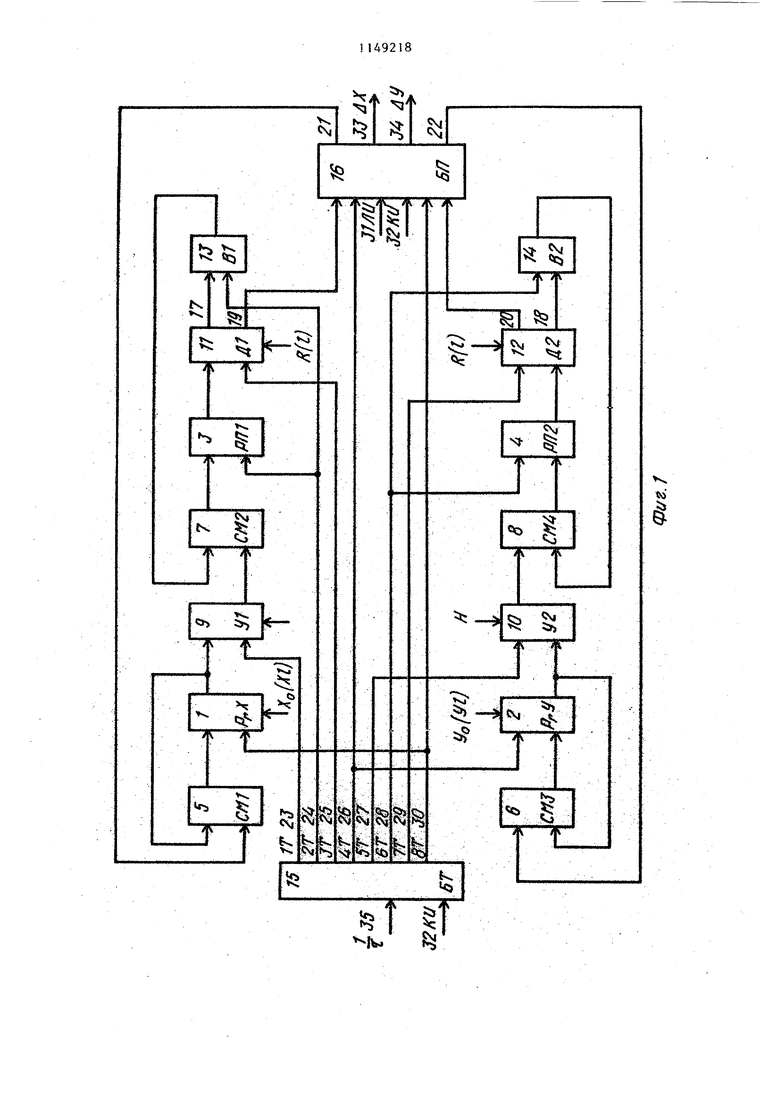

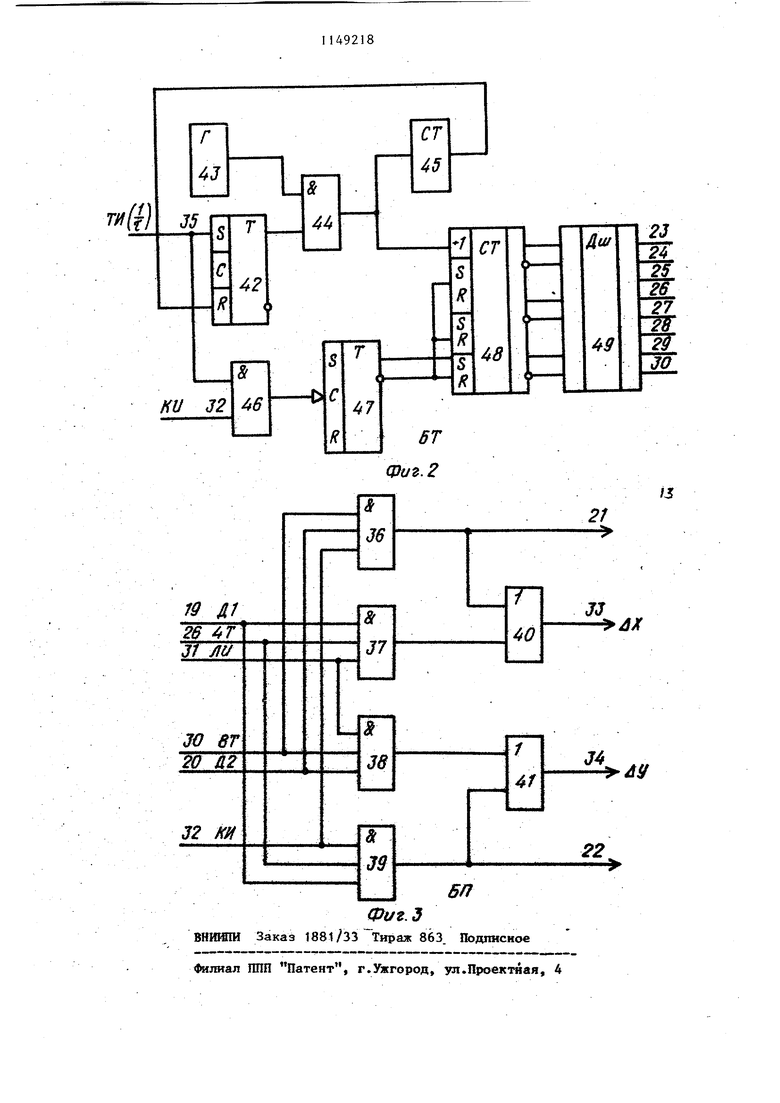

11 Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах числового программного управления станкам Известны линейно-круговые интерполяторы с многоразрядными приращениями, построенные на основе цифровы дифференциальных анализаторов (ЦДЛ) Недостатками данных устройств яв ляются большая разрядность вычислений необходимая для получения достаточно точности, и, как следствие, высокая сложность. Наиболее близким к изобретению по технической сущности,является линейнокруговой интерполятор, содержащий общий делитель и в каждом координатном канале последовательно соединенные первый вентиль, регистр, делитель и второй вентиль, причем первый выход делителя соединен с входом регистра этого же канала, второй выход делителя - с входом первого вентиля другого канала,выход общего делителя - с первыми входами вторых вентилей, вькоды которых соответственно подключены к входам делителей коорди натных каналов L2j. Недостатком известного устройства является низкая точность отработки заданной скорости перемещений (ошибка в скорости может достигать 50%). Кроме того, устройству свойственна, хотя и уменьшена по сравнению с другими интерполяторами, вычислительная погрешность. Целью изобретения является повышение точности отработки заданной ск рости перемещений и точности интерполяции по контуру дуги, Поставленная цель достигается тем .что линейно-круговой интерполятор, содержащий в каждом координатном канале последовательно соединенные первый регистр и делитель, подключенный первым выходом к первому входу группы вентштей, содержит блок тактирования, блок переключения и в каждом координатном канале последо вательно соединенные первый сумматор второй регистр, умножитель и второй сумматор, вьтход которого соединен с .первым входом первого регистра, а второй вход - с выходом группы вентилей, второй вход которой соединен с вторым входом первого регистра и с первым выходом блока тактирования, второй выход которого подключен к второму входу умножителя, третий 8J выход - к второму входу делителя, а четвертый выход - к первому входу втоР.ОГО регистра другого канала и к первому входу блока переключения, соединенного выходом с первым входом . первого сумматора, второй вход кото- : рого подключен к выходу второго регистра, блок переключения соединен BTOpbiM входом с вторым выходом делителя, третий вход которого подключен к входу устройства. Кроме того, блок тактирования содержит генератор импульсов, выходом соединенный с первым входом первого элемента И, второй вход которого через первый триггер управления соединенс выходом первого счетчика, а также последовательно соединенные второй элемент И, второй триггер управления, второй счетчик и дешифратор, выходы которого соединены с выходами блока тактирования, выход первого элемента И соединен с входом первого счетчика и входом второго счетчика, входы второго элемента И и S-вкод первого триггера подключены к входам блока тактирования. На фиг. 1 приведена структурная схема предлагаемого интерполятора на фиг, 2 - схема выполнения блока переключения на фиг, 3 - схема блока активирования. Интерполятор содержит вторые 1 и 2 и первые 3 и 4 регистры, первые 5 и 6 и вторые 7 и 8 сумматоры, умножители 9 и 10, делители 11 и 12, вентили 13 и 14, блок 15 тактирования, блок 16 переключения, первые 17 и 18 н вторые 19 и 20 выходы (шины) делителей 11 и 12 соответственно,.- выходы (шины) 21 и 22 блока 16 переключения, выходы (линии) 23-30 блока 15 тактирования, входы (линии) 31 и 32 блока 16 переключения, выходные шины (линии) 33 и 34 блока 16, вход (линия) 35 блока 15 тактирования. Схема блока 16 переключения (фиг.2) содержит четыре группы вентилей 36-39 и две группы элементов ИЛИ 40 и 41, Связи, показанные на схеме, обеспечивают требуемое для правильной работы интерполятора подключение шин 19 и 20 (выходы блоков делителей 11 и 12) на выходные пшны 33 и 34 и в режиме круговой интерполядии на шины 21 и 22 для передачи в сумматоры 5 и 6 соответственно. 31149 Схема блока 15 тактирования (фиг. 3) содержит триггеры 42 управления, генератор 43 импульсов, элемент И 44, трехразрядньй счетчик 45, элемент И 46, триггер 47 управления, счетчик 48 и дешифратор 49. По входной линии 35 поступают импульсы, зада ющие цикл вычислений, по линии 32 команда Круговая интерполяция, выходные линии 23.-3О подключаются к соответствующим блокам интерполятора (фиг. 1). Устройство работает следующим образом. В регистрах 1 и 2 в исходном состоянии устанавливаются координаты начальной точки Хр, Уд дуги при круговой интерполяции либо величины перемещения по осям Х, У на участке отработки при линейной интерполяции, В процессе круговой интерполяции в этих регистрах содержатся величины координат текущей точки дуги; в процессе линейной интерполяции содержимое регистров 3 и 4 не меняется. В умножителях 9 и 10 производится умножение содержимого регистров 1 и 2 на величину шага интерполяции по контуру Н. Величина шага Н определяется заданной скоростью подачи V и принятой длительностью цикла вычисления приращений , т.е. Н , причем const. Если регистры 1 и 2 имеют по ш разрядов каждый, а для шага предусмотрено К разрядов, to разрядность произведения составит (т + к). В регистрах 3 и 4 размещаются сум мы содержимого соответствующего умно жителя 9 и 10 и m младших разрядов делимого делителя 11 и 12, суммированне которых производится сумматорами 7 и 8. Делители 11 и 12 осущест вляют деление содержимого регистров 3 и 4 на величину радиуса дуги R при круговой интерполяции или на величину перемещения по контуру t при линейно интерпсшяции. Деление производится с точнос-сью до к разрядов, т.е. к разрядное частно размещается в выходном регистре делителя 11 (или 12) am- разрядный остаток остается в регистре делимого. Вентили 13 и 14 служат для передачи содержимого m младших разрядов делимого делнтелей 11 и 12 на сумматоры 7 и 8, Блок 15 тактирования с приходом каждого тактового сигнала по входу 35 вьфабатывает последовательность из восьми импульсов на выходах 23-30, которые определяют последовательность опера- ций в устройстве. Блок 16 переключения в режиме круговой интерполяции подключает выход делителя 11 - кразрядное частное с шины 19 - на вход сумматора 6 по шине 22 и выход интерполятора по оси Y по щине 34; выход делителя 12 по шине 20 подключен на вход сумматора 5 по шине 21 и на выход устройства по оси X по шине 33, В режиме линейной интерполяции выход 19 делителя 11 подключен к miHe 33, вькод 20 делителя 12 - к шине 34; подключения к шинам 21 и 23 с выходов делителей не производятся. В режиме линейной интерполяции в регистры 1 и 2 вводятся величины X. и ; перемещений по осям на участке интерполяции, в умножителях 9и 10 устанавливается множитель Н, в делителях 11 и 12 - делитель (длина участка интерполяции), в регистрах 3 и 4 - нули, в блок 16 переключения задается по входу 31 команда Линейная интерполяция. На каждьй сигнал цикла по входу 35 блок 15 вырабатывает восемь тактов. Первый такт по линии 23 разрешает запись содержимого регистра 1 во входной регистр умножителя 9, вслед за чем производится умножение величины Xg на Н. Второй такт по линии 24 разрешает передачу содержимого m младших раарядов делимого делителя 11 через вентиль 13 на сумматор 7 и запись суммы в регистр 3. Третий такт по линии 25 разрешает запись содержимого регистра 3 в регистр делимого делителя 11, вслед за чем осуществляется операция деления. Четвертый такт по линии 26 разрешает передачу частного с шины 19 через блок 16 переключения на выходную шину 33 по оси X. Пятый такт по линии 27 разрешает передачу содержимого регистра 2 в умножитель 10и осуществление операции умножения. Шестой такт по линии 28 разрешает запись результата сумю1рования содержимого выходного регистра умножителя 10 и m младшга разрядов делимого делителя 12 в регистр 4. Седьмой такт по линии 29 разрешает запись содержимого регистра 4 в регистр делимого делителя 12,вслед за чем вьтолняется операция делений. Восьмью тактом по линии 30 содержимое регистра частного делителя 12 с пмны 20 подключается на выходную шину 34 блока 16 переключения по оси Y . В режиме круговой интерполяции в регистрах 1 и 2 устанавливаются величины XQ, YO- координаты начальной точки дуги, в умножители 9 и 10 - величина шага интерполяции Н по дуге, в делители 11 и 12 - радиус дуги окружности R. Последовательйост прохождения сигналов по линиям 23-30 зависит от номера цикла. В нечетных циклах сохраняется такая же последовательность, как и при линейной интерполяции. Операдни, производимые с первьв4, вторым и третьим тактами остаются прежними. На четвертом такте по сигналу линии 26 содержимое регистра частного делителя 11 поступает на выход 34 по Y и по шине 22 на вход сумматора 6. На второй вход сумматора 6 подключен выход регистра 2 координаты . По сигналу с линии 26 разрешается запись результата суммирования в регистр 2, т.е. образования в кем величины у,- Yi 4ду,- . Далее посигнала пятого, шестого и седьмого тактов осуществляются операции, аналогичные режиму линейной интерполяции. По сигналу восьмого такта (линии 30) содержимое регистра частного делителя 12 с шины 20 подается на выходную ши ну 33 по оси X и по шине 21 на вход сумматора 5, осуществляющего суммирование его с содержимым регистра 1. По этому же сигналу с линии 30 произ водится запись результата суммирования в регистр 1, в котором образуетс новое значение координаты х, т.е. X ;+1 ( В четньк циклах генерация сигнало начинается с линии 27 и идет в после довательности . Благодаря этому вначале вычисляется приращение ДХ, образуется значение Х,-+,, по которому вычисляются значения дУ,-. В интерполяторе реализуются следу ющие вычисления. В режиме линейной интерполяции .X..enifl-.(..j5 .Ry Jr.H+R i . lj( JлУ: епv. V.H + R. -&.-i , t-1 t1-1 1 8 - целая часть выражения, Х- остатки i-го шага вьтчис лений. В режиме круговой интерполяции в нечетных циклах Y,(x. ,X. HM., -dY.R Y-taY. .jj iflX. ent r%.V. Xj.-X. 4X. . Б четных циклах последовательно ычислены Ki 4JiйХ,еп1 RV Y.H+PV 4X:R , i ,. 3 Xj., X.X. .Y.(x. u. J+-1 X x. VV.. j.i i По сравнению с известным предлагаемое устройство при той же сложное ти обеспечивает более высокие точности интерполяции и отработки заданной скорости перемещения. В режиме ли-нейной интерполяции элемент И 46 закрыт, счетчики 45 и 48 установлены в нули. С приходом импульса цикла по входу-35 триггер 42 устаналивается в 1, открывается элемент И 44, через который проходят импульсы генератора 43.. Очередной импульс генератора 43 увеличивает содержимое счет иков 45 и 48 на единицу на выходах дешифратора 49 последовательно, начиная с линии 23 и заканчивая линией 30, появляются сигналы управления. После прихода восьмого импульса счетчики 45 и 48 переполняются, выходной сигнал счетчика 45 устанавливает триггер 42 в состояние О, элемент И 44 закрьгеается и блок ожидает прихода следующего импульса цикла по линии 35. 7 В режиме круговой интерполяции по линии 32 открывается элемент И 46, через который проходят на триггер 47 импульсы цикла. Если начальная установка триггера 47 О, то с приходом каждого нечетного импульса цикла счетчик 48 сбрасывается в нуль и порядок прохождения сигналов на вы ходах дешифратора 49 остается таким же, как в режиме линейной интерполяции. С приходом каждого четного импульса цикла выходной сигнал тригге.ра 47 устанавливает третий разряд счетчика 48 в 1 (состояние счетчика 100), что определяет последовательность прохождения сигналов на выходах дешифратора в порядке 27-2829-30-23-24-25-26 при прохождении восьми импульсов генератора 43, Благодаря чередованию циклов мето дическая ошибка интерполяции носит периодический характер с амплитудой ..«,,, . При линейной интерполяции методическая ошибка не превосходит одной дискретности. В предлагаемом устройстве все вычисления ведутся с целыми числами округлений нет и вычислительные погрешности не появляются Кроме того уменьшается разрядность блоков. Так если регистры 3 и 4 имеют по m разрядов, а множитель Н - к-разрядов, то регистры умножителей 9 и 10 должны иметь по (т + к) разрядов, регистры произведения умножителей 9 и 10 и регистры делимого делителей 188 11 и 12 - по (тп + к) разрядов, регистры частного делителей - по к разрядов, сумматоры 5 и 6 при параллельном суммировании - по (к + 1) разрядов, сумматоры 7 и 8 - по (т + 1) разрядов. Типичные значения т 20-24, . Тогда максимальнаяразрядность регистров не превысит 34. При использовании интегр ирования с дробными числами, что обычно делается в ЦЦА, вычисления ведутся с точностью , что соответствует максимальной разрядности чисел 44-48 при практически такой же функ1 нональной сложности устройства. Высокая точность вычислений приращений дХ и йУ обеспечивает высокую точность отработки заданной скорости перемещений, так как в устройстве со ставляющие скорости по осям V Y Г и скорость подачи по контуру v., а величина , участвующая в вычислениях приращений, задается точно, По сравнению с известным предпагаемое устройство позволяет повысить скорость вычерчивания на координатографе при контроле геометрии деталей до 40м/мин (т.е. в 20 раз) и скорость записи программ на магнитную ленту до 800 мм/с (т.е. в 16 раз).

to

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейно-круговой интерполятор | 1984 |

|

SU1215090A2 |

| Линейно-круговой интерполятор | 1985 |

|

SU1302241A2 |

| Линейно-круговой интерполятор | 1983 |

|

SU1265700A2 |

| Цифровой интерполятор | 1984 |

|

SU1238033A1 |

| Линейно-круговой интерполятор | 1985 |

|

SU1259218A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Устройство для управления многокоординатным оборудованием | 1987 |

|

SU1427334A1 |

| Устройство для задания скорости в системах числового программного управления | 1986 |

|

SU1381430A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

1. ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР, содержащий в каждом координатном канале последовательно соединенные первый регистр и делитель., подключенный первым выходом к первому входу группы вентилей, о т л ич а ю щ и и с я тем, что, с целью повышения ТОЧНОСТИ отработки заданной скорости перемещений и точности интерполяции по контуру дуги, он содержит блок тактирования, блок переключения и в каждом координатном канале последовательно соединенные первый сумматор, второй регистр, умножитель и второй сумматор, выход которого соединен с первьм входом первого регистра, а второй вход - с выходом группы вентилей, второй вход которой соединен с вторым входом первого регистра и с первым выходом блока тактирования, второй выход которого подключен к второму входу умножителя, третий выход - к второму входу делителя, а четвертый выход к первому входу второго регистра другого канала и к первому входу блока переключения, соединенного выходом с первьм входом первого сумматора, второй вход которого подключен к выходу второго регистра, блок переключения соединен вторым входом с вторым выходом делителя, третий вход которого подключен к входу устройства. i 2. Интерполятор по п. 1, о т л ичающийс тем, что блок такти(Л С рования содержит генератор импульсов, выходом соединенный с первым входом первого элемента И, второй вход которого через первый триггер соединен с выходом первого счетчика, а также последовательно соединенные второй элемент И, второй триггер, второй счетчик и дешифратор, выходы 4 со которого соединены с.выходами блока iтактирования, выход первого элемента tc |И соединен с входом первого счетчика и входом второго счетчика, входы оо второго элемента И и S-вход первого триггера подключены к входам блока тактирования.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Линейно-круговой интерполятор | 1974 |

|

SU500518A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Линейно-круговой интерполятор | 1977 |

|

SU732818A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-04-07—Публикация

1982-12-20—Подача