Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах.

Известно устройство для деления двоичных чисел, содержащее регистр делимого, регистр делителя, регистр частного, сумматор, блок управления, элемент ИЛИ, реверсивный счетчик, дешифратор нуля и блок сравнения кодов.

Известно устройство для деления двоичных чисел, содержащее регистр делимого, регистр делителя, регистр частного, сумматор, блок сравнения, блок преобразования кода, элемент НЕ, счетчик, блок управления, триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, демультиплексор, блок элементов ИЛИ.

Недостатком указанных устройств для деления двоичных чисел является низкое быстродействие выполнения деления двоичных чисел.

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для деления двоичных чисел, содержащее регистры делимого, делителя и частного, два сумматора1, два блока вычисления логарифмов, два коммутатора, блок преобразования кода делителя, элемент НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, триггер, группу элементов ИЛИ и блок управления, содержащий генератор тактовых импульсов, элемент И, счетХ|00

СО

сл ю о

чик циклов, элемент НЕ и два триггера, при этом выходы разрядов с первого по (п+1)-й регистра делимого соединены с входом первого блока вычисления логарифмов и с первыми информационными входами разрядов с второго по(п+2)-й первого сумматора, первый информационный вход первого разряда которого соединен с входом логического нуля устройства, выход суммы первого сумматора соединен с информационным входом регистра делимого, выходы первого и второго блоков вычисления логарифмов соединены с первым и вторым информационными входами второго сумматора, вход переноса которого соединен с входом логической еди- ницы устройства, выход суммы второго сумматора соединен с управляющими входами первого и второго коммутаторов, информационный вход первого коммутатора соединен с выходом регистра делителя и с входом второго блока вычисления логарифмов, выход первого коммутатора соединен с информационным входом блока преобразования кода делителя, выходы которого соединены с вторыми информационными входами пер- вых (n-И) разрядов первого сумматора, вход переноса и второй информационный вход (п+2)-го разряда которого соединены с yn- равляющим входом блока преобразова- ния кода делителя и выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом триггера, информационный вход которого соединен с информационным входом второго коммутатора и с выходом элемента НЕ, вход которо- го соединен с выходом знакового разряда первого сумматора, выход первого разряда второго коммутатора соединен с информационным входом первого разряда регистра частного, информационные входы разрядов с второго по m-й которого соединены с вы-0 ходами элементов ИЛИ группы, первые вхо- ды которых соединены с выходами разрядов с второго по m-й соответственно второго коммутатора, вторые входы э лемен- тов ИЛИ группы соединены с выходами разрядов с первого по (т-1)-й регистра частного, синхровход которого соединен с синхровходами триггера, регистра делимого, первого триггера блока управления, вхо- дом счетчика циклов и выходом элемента И, первый вход которого соединен с выходом генератора тактовых импульсов, второй вход элемента И соединен с выходом элемента НЕ блока управления, вход которого соединен с выходом счетчика циклов, информационный вход первого триггера блока управления соединен с инверсным выходом второго триггера, информационный вход которого соединен с входом логической еди

0 5 0 5 , g g п Q

5

ницы устройства, выход первого триггера блока управления соединен с синхровходом второго триггера и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

Недостатком данного устройства для деления двоичных чисел является низкое быстродействие выполнения операции деления. Это обусловлено тем. что число циклов определения цифр целой части частного, определяющее время выполнения операции деления, не зависит от величины частного, а является постоянной величиной, равной разрядности операндов делимого и делителя.

Время выполнения операции деления двух двоичных чисел с точностью вычисления частного до дробной части определяется зависимостью

Тдел A|/B| предел.цифр5 Ттакт X (п + с),

где предел ЦИФР - время определения цифр частного;

traia - длительность цикла определения одной цифры частного (период тактовой частоты, в течение которого определяется од- на цифра частного);

п - число разрядов операндов делимого и делителя, равное числу разрядов целой части операнда частного;

с - число разрядов дробной части частного, выбираемое из условия требуемой точности вычисления частного (контакта устройства).

Целью изобретения является повышение быстродействия устройства.

Пусть п-разрядность операндов делимого и делителя, AI - делимое, В| - делитель - конкретные двоичные числа, над которыми производится операция деления, Величина AI представляется двоичным кодом, содержащим apt разрядов, величина Bi представляется двоичным кодом, содержащим bpt разрядов.

Перед началом операции определения цифр частного, которая выполняется в виде операции деления со сдвигом остатка и его автоматическим восстановлением, производится нормализация кода делителя. Она заключается в том, что по исходным кодам делимого AI и делителя В вычисляется показатель Ki степени множителя нормализации:

92 А,- ЈГ IOQ2 В 1.(1)

Если вычисленное значение показателя Ki степени множителя нормализации является

величиной, меньшей или равной нулю, то код делителя является нормализованным относительно кода делимого, т.е. код делителя установлен относительно кода делимого в положение, когда удовлетворяются условия нормализации

(2) 10

и разрешается осуществлять операцию определения цифр частного. Если вычисленное значение показателя К| степени множителя нормализации больше или равно единице, то производится нормализация кода делителя: код делителя В| умножают на множитель нормализации 2к (код делителя сдвигают в сторону старшего разряда на К{ разрядов) и устанавливают его тем самым в положение, когда условия нормализации (2) удовлетворяются.

Сдвиг кода делителя на соответствующее число разрядов осуществляется с помощью коммутатора и не требует времени на циклы последовательного сдвига.

При этом вычисляемое перед началом операции деления в соответствии с зависимостью (1) для каждой пары двоичных чисел значение показателя Ki степени множителя нормализации определяет не только число разрядов, некоторое необходимо сдвинуть код делителя для его нормализации, но и максимальное для данной пары двоичных чисел, исходя из разрядности их конкретных значений, число циклов, которое необходимо выполнить в процессе деления для определения цифр целой части частного.

Вычисляемое значение показателя К| степени множителя нормализации запоминается перед началом операции определения цифр частного в счетчике циклов и определяет количество циклов, которое будет проведено в процессе деления для определения цифр целой части частного.

Если частное требуется вычислять с точностью до дробной части, то вычисленное значение показателя Ki степени множителя нормализации суммируется с числом, равным требуемой разрядности дробной части частного - с, и результат запоминается в счетчике циклов.

Время выполнения операции деления двух двоичных чисел с точностью вычисления частного до дробной части определяется зависимостью

т.делА|/В| - 1такт (К| + с)

traKT

..целая часть

Iog2 AI 0

5

0

5

0

5

0

5

0

5

- чЦаестаьЯ 2В +1) + с1Повышение быстродействия предлагаемого устройства для деления двоичных чисел по сравнению с прототипом осуществляется за счет того, что для каждой пары двоичных чисел перед началом операции определения цифр частного вычисляется конкретное значение показателя Kt степени множителя нормализации, которое определяет конкретное для данной пары двоичных чисел число циклов, необходимое для данной пары двоичных чисел число циклов, необходимое для вычисения цифр целой части частного, и которое для всех допустимых значений делимого и делителя, кроме случая, когда величина делимого ляется максимальной (api равно п. а делитель равен единице, т.е. bpi равно 1), является величиной меньшей, чем разрядность операндов делимого и делителя, т.е. меньшей п, величина которой определяет в прототипе число циклов определения цифр целой части частного.

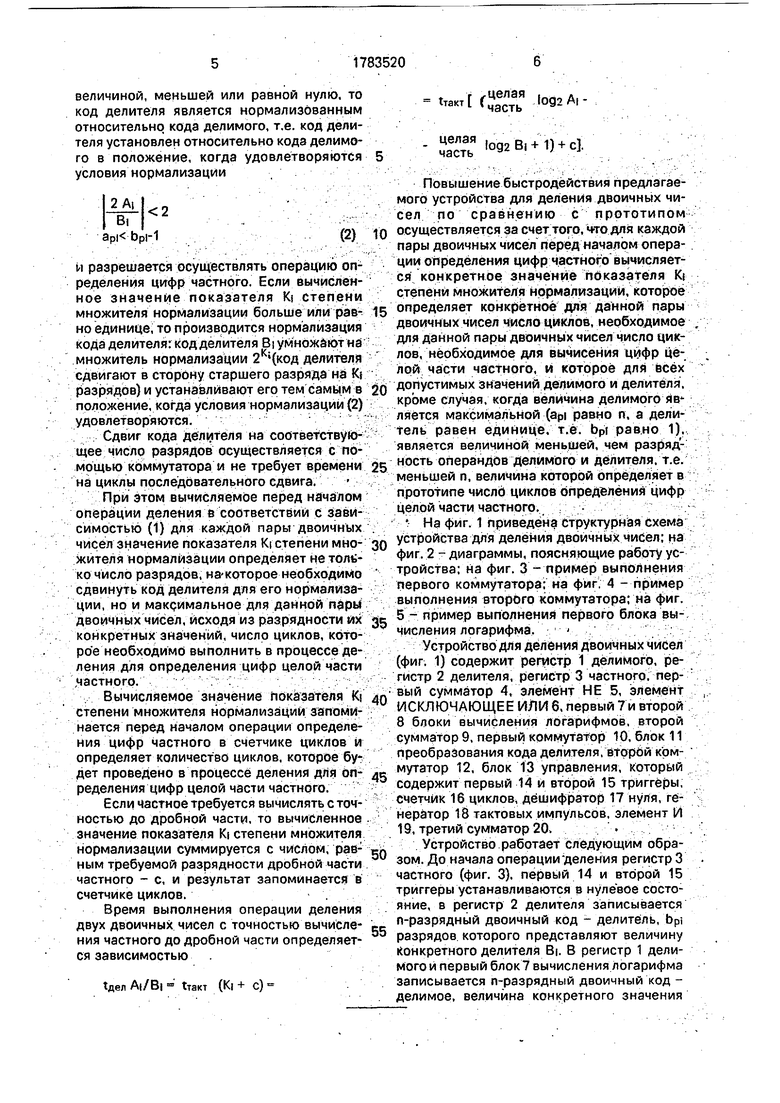

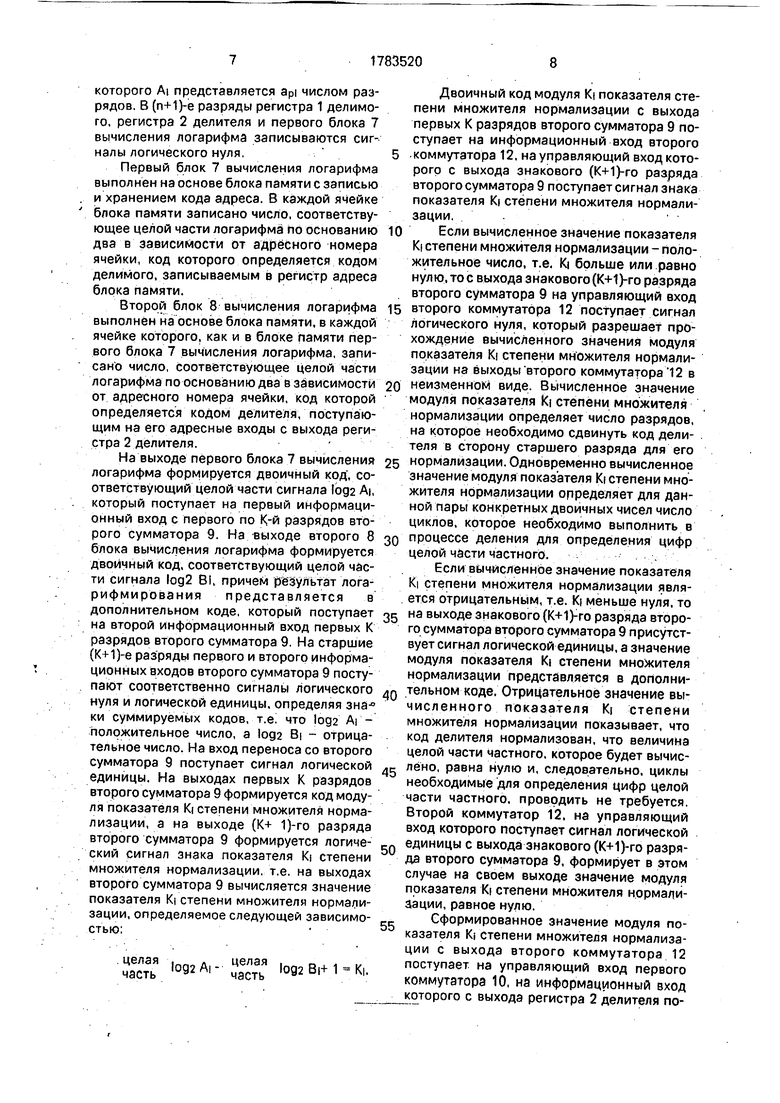

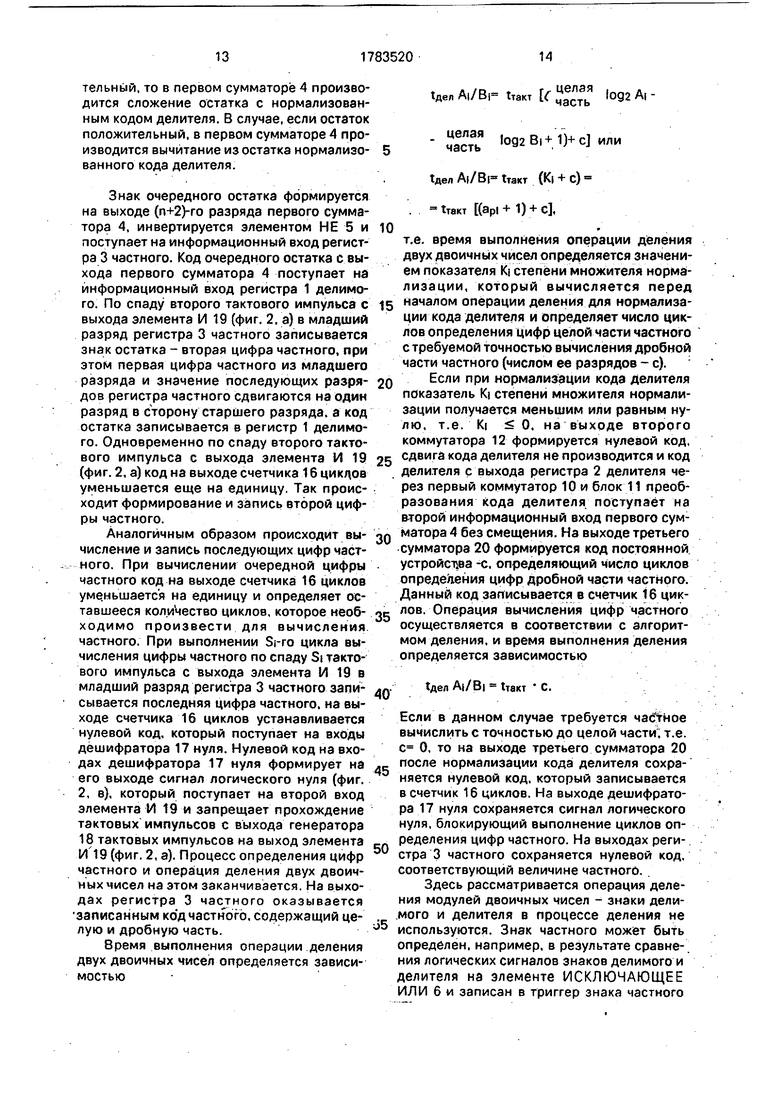

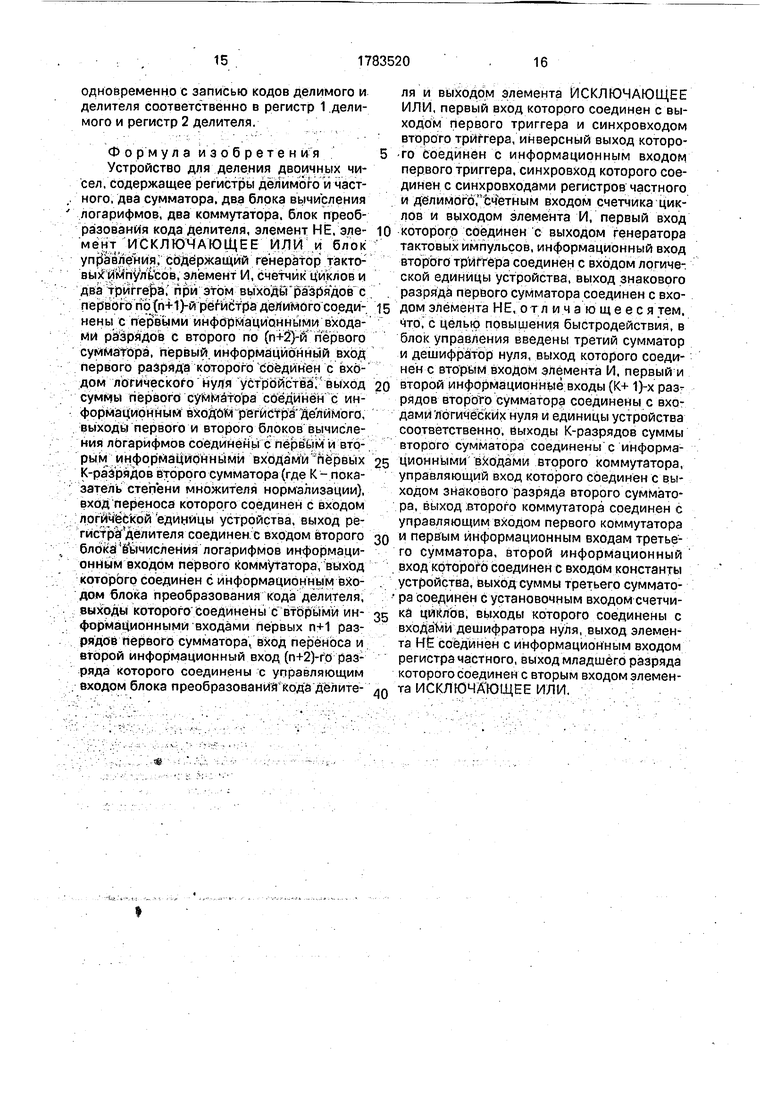

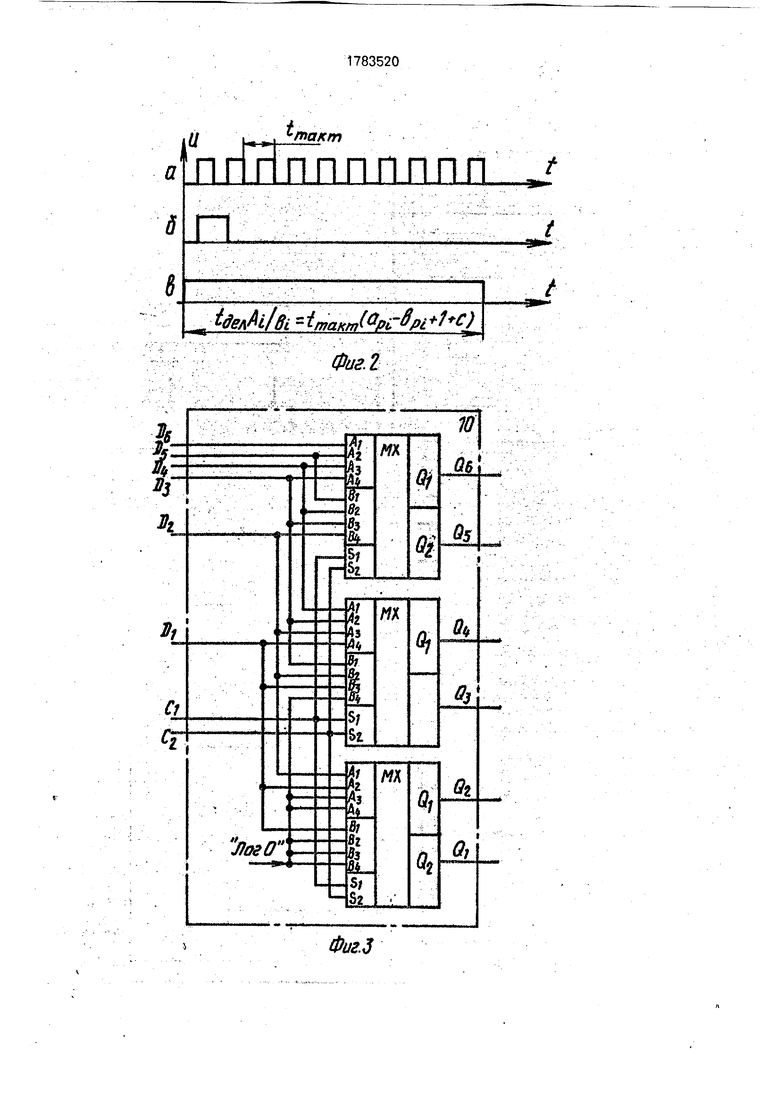

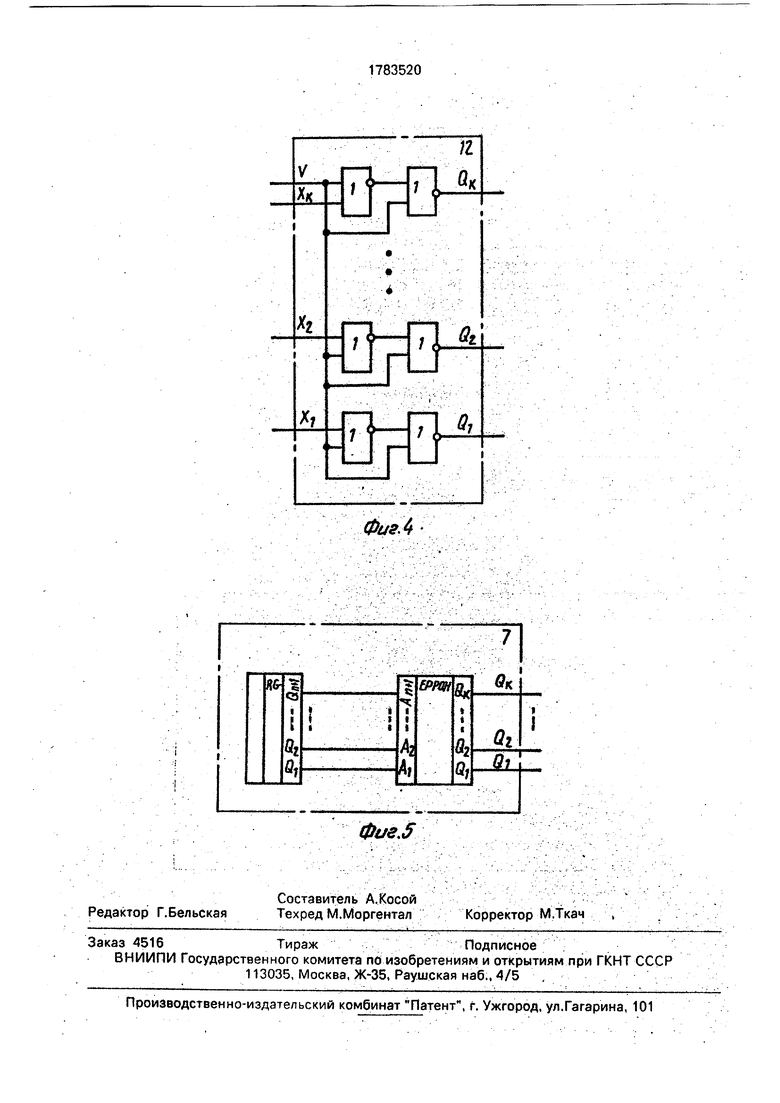

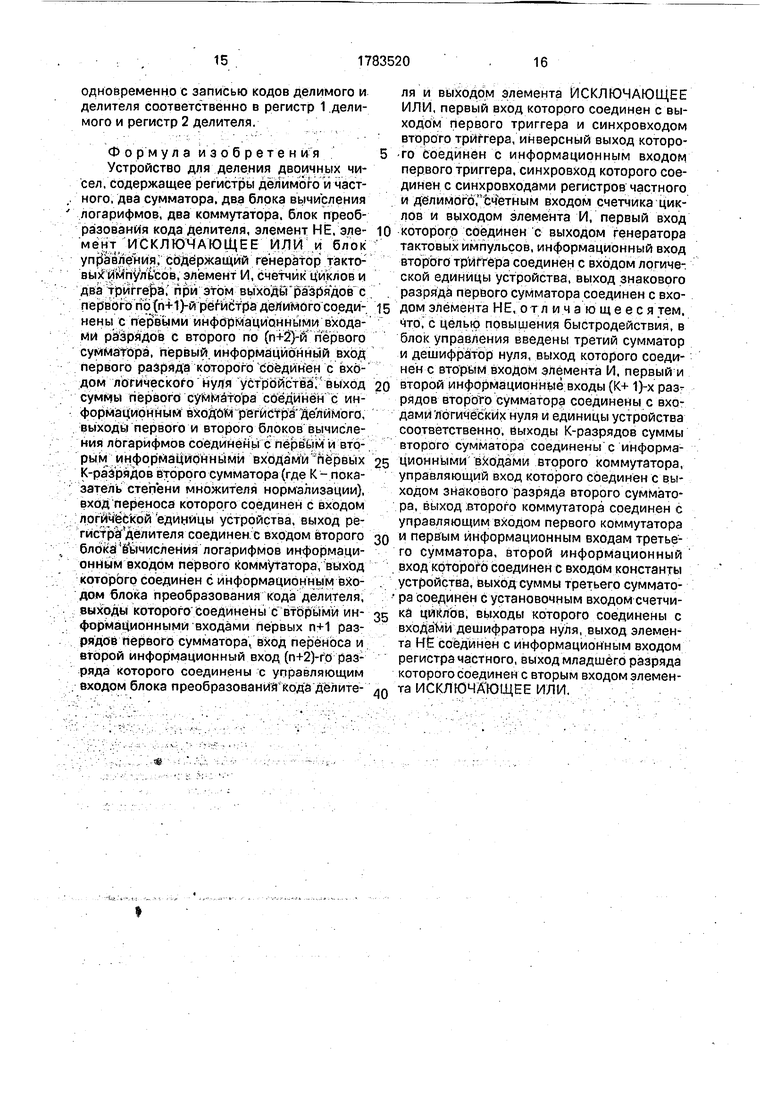

На фиг. 1 приведена структурная схема устройства для деления двоичных чисел; на фиг. 2 - диаграммы, поясняющие работу устройства; на фиг. 3 - пример выполнения первого коммутатора; на фиг. 4 - пример выполнения второго коммутатора; на фиг. 5 - пример выполнения первого блока вычисления логарифма. j

Устройство для деления двоичных чисел (фиг. 1) содержит регистр 1 делимого, регистр 2 делителя, регистр 3 частного, первый сумматор 4, элемент НЕ 5, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6, первый 7 и второй 8 блоки вычисления логарифмов, второй сумматор 9, первый коммутатор 10, блок 11 преобразования кода делителя, второй коммутатор 12, блок 13 управления, который содержит первый 14 и второй 15 триггеры, счетчик 16 циклов, дешифратор 17 нуля, генератор 18 тактовых импульсов, элемент И 19, третий сумматор 20,

Устройство работает следующим образом. До начала операции деления регистр 3 частного (фиг. 3), первый 14 и второй 15 триггеры устанавливаются в нулевое состояние, в регистр 2 делителя записывается n-разрядный двоичный код - делитель, bpi разрядов которого представляют величину конкретного делителя BI. В регистр 1 делимого и первый блок 7 вычисления логарифма записывается n-разрядный двоичный код - делимое, величина конкретного значения

которого Ai представляется api числом разрядов. В (п+1)-е разряды регистра 1 делимого, регистра 2 делителя и первого блока 7 вычисления логарифма записываются сигналы логического нуля.5

Первый блок 7 вычисления логарифма выполнен на основе блока памяти с записью и хранением кода адреса. В каждой ячейке блока памяти записано число, соответствующее целой части логарифма по основанию 10 два в зависимости от адресного номера ячейки, код которого определяется кодом делимого, записываемым в регистр адреса блока памяти.

Второй блок 8 вычисления логарифма 15 выполнен на основе блока памяти, в каждой ячейке которого, как и в блоке памяти первого блока 7 вычисления логарифма, записано число, соответствующее целой части логарифма по основанию два в зависимости 20 от адресного номера ячейки, код которой определяется кодом делителя, поступающим на его адресные входы с выхода регистра 2 делителя.

На выходе первого блока 7 вычисления 25 логарифма формируется двоичный код, соответствующий целой части сигнала Iog2 AI, который поступает на первый информационный вход с первого по К-й разрядов второго сумматора 9. На выходе второго 8 зо блока вычисления логарифма формируется двоичный код, соответствующий целой части сигнала Iog2 Bi, причем результат логарифмирования представляется в дополнительном коде, который поступает 35 на второй информационный вход первых К разрядов второго сумматора 9. На старшие (К+1)-е разряды первого и второго информационных входов второго сумматора 9 поступают соответственно сигналы логического Q нуля и логической единицы, определяя зна-0 ки суммируемых кодов, т.е. что Iog2 Ai - положительное число, a Iog2 BI - отрицательное число. На вход переноса со второго сумматора 9 поступает сигнал логической -Е единицы. На выходах первых К разрядов второго сумматора 9 формируется код модуля показателя Ki степени множителя нормализации, а на выходе (К+ 1)-го разряда второго сумматора 9 формируется логический сигнал знака показателя Ki степени множителя нормализации, т.е. на выходах второго сумматора 9 вычисляется значение показателя Ki степени множителя нормализации, определяемое следующей зависимостью:

целая Юд2А,- целая log2Bi+1 K, часть у часть у

50

55

0

5 0

5 о 5 Q Е

0

5

Двоичный код модуля KI показателя степени множителя нормализации с выхода первых К разрядов второго сумматора 9 поступает на информационный вход второго коммутатора 12, на управляющий вход которого с выхода знакового (К+1)-го разряда второго сумматора 9 поступает сигнал знака показателя Ki степени множителя нормализации.

Если вычисленное значение показателя Ki степени множителя нормализации - положительное число, т.е. KI больше или равно нулю, то с выхода знакового (К+1)-го разряда второго сумматора 9 на управляющий вход второго коммутатора 12 поступает сигнал логического нуля, который разрешает прохождение вычисленного значения модуля показателя KI степени множителя нормализации на выходы второго коммутатора 12 в неизменном виде. Вычисленное значение модуля показателя KI степени множителя нормализации определяет число разрядов, на которое необходимо сдвинуть код делителя в сторону старшего разряда для его нормализации. Одновременно вычисленное значение модуля показателя Ki степени множителя нормализации определяет для данной пары конкретных двоичных чисел число циклов, которое необходимо выполнить в процессе деления для определения цифр целой части частного.

Если вычисленное значение показателя Ki степени множителя нормализации является отрицательным, т.е. KI меньше нуля, то на выходе знакового (К+1)-го разряда второго сумматора второго сумматора 9 присутствует сигнал логической единицы, а значение модуля показателя Ki степени множителя нормализации представляется в дополнительном коде. Отрицательное значение вычисленного показателя KI степени множителя нормализации показывает, что код делителя нормализован, что величина целой части частного, которое будет вычислено, равна нулю и, следовательно, циклы необходимые для определения цифр целой части частного, проводить не требуется. Второй коммутатор 12, на управляющий вход которого поступает сигнал логической единицы с выхода знакового (К+1)-го разряда второго сумматора 9, формирует в этом случае на своем выходе значение модуля показателя Ki степени множителя нормализации, равное нулю.

Сформированное значение модуля показателя Ki степени множителя нормализации с выхода второго коммутатора 12 поступает на управляющий вход первого коммутатора 10, на информационный вход которого с выхода регистра 2 делителя поступает код делителя - Bi. В соответствии с управляющим кодом код делителя с информационных входов второго коммутатора 10 поступает на его выходы в виде В 2 , т.е. умноженным на множитель нормализации 2К (т.е. код делителя на выходе второго коммутатора Доказывается сдвинутым относительно своего положения на информационных входах второго коммутатора 10 на KI разрядов в сторону старшего разряда). На выходе второго коммутатора

10оказывается сформированным нормали- зованный код делителя -В 2К , который поступает на информационный вход блока

11преобразования кода делителя.

Сформированное значение модуля показателя KI степени множителя нормализации с выхода второго коммутатора 10 поступает также на первый информационный вход третьего сумматора 20, на второй информационный вход которого поступает двоичный код константы с, определяющий число разрядов дробной части частного. На выходе третьего сумматора 20 формируется двоичный код суммы -Si, определяющий число циклов определяния цифр целой и дробной части частного, т.е. код числа циклов определения цифр частного:

Si KI + с.

Вычисленное значение числа циклов Si определения цифр частного с выхода третьего сумматора 20 поступает на установочный вход счетчика 16 циклов и устанавливается на его разрядных выходах. Код числа циклов Si определения цифр частного, отличный от нуля, с выхода счетчика 16 циклов поступает на входы дешифратора 17 нуля. На выходе дешифратора 17 нуля формируется сигнал логической единицы (фиг. 2, в), который поступает на второй вход элемента И 19 и разрешает прохождение тактовых импульсов с выхода генератора 18 тактовых импульсов через первый вход элемента И 19 на его выход (фиг. 2, а).

Начинается пошаговый процесс определения цифр частного в соответствии с алгоритмом деления, согласно которому код делимого из регистра 1 делимого со сдвигом на один разряд в сторону старшего разряда подается на первый информационный вход разрядов первого сумматора 4, при этом на его первый информационный вход первого

разряда подается сигнал логического нуля. Код делителя из регистра 2 делителя, нормализованный с помощью первого 10 и второго 12 коммутаторов, через блок 11

5 0

5

0 5

0

5 о 5

Q

5

преобразования кода делителя поступает на второй информационный вход первого сумматора А в дополнительном коде. В первом сумматоре 4 производится вычитание нормализованного кода делителя из кода делимого. Результат вычитания определяется по логическому сигналу с выхода (п+2)-го разряда первого сумматора 4, сигнал с которого инвертируется элементом НЕ 5 и поступает на информационный вход регистра 3 частного. Остаток с выхода первого сумматора 4 поступает на информационный вход регистра 1 делимого. В младший разряд регистра 3 частного записывают цифру частного, одновременно с этим остаток с выхода первого сумматора 4 записывают в регистр 1 делимого, а значет йе кода на выходе счетчика 16 циклов уменьшается при этом на единицу. Логический сигнал с выхода младшего разряда регистра 3 частного, в котором записана цифра частного, поступает через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6 на управляющий вход блока 11 преобразования кода делителя, на вход переноса и второй информационный вход (п+2)-го разряда первого сумматора 4 и управляет передачей нормализованного кода делителя на второй информационный вход первого сумматора 4 в следующем такте определения цифр частного. Далее процесс повторяется: код остатка с выхода регистра 1 делимого поступает на первый информационный вход первого сумматора 4 сдвинутым на один разряд в сторону старшего разряда. Если в младший разряд регистра 3 частного в предыдущем цикле был записан сигнал логической единицы, соответствующий положительному остатку, то нормализованный код делителя подается на второй информационный вход первого сумматора 4 в дополнительном коде и в,первом сумматоре 4 производится вычитание нормализованного кода делителя из кода остатка. Если в младший разряд регистра 3 частного е предыдущем цикле определения цифр частного был записан сигнал логического нуля, соответствующий отрицательному остатку, но нормализованный код делителя подается на второй информационный вход первого сумматора 4 в прямом коде и в первом сумматоре 4 производится сложение кода остатка с нормализованным кодом делителя. Сигнал с выхода (п+2)-го знакового разряда первого сумматора 4 инвертируется элементом НЕ 5 и записывается в младший разряд регистра 3 частного, предыдущая цифра частного и содержание остальных разрядов регистра 3 частного сдвигается при этом на один раз- ояд в сторону старшего разряда Значение

кода на выходе счетчика 16 циклов уменьшается еще на единицу. Далее процесс повторяется.

В соответствии с алгоритмом деление импульсы (фиг. 2, а) с выхода генератора 18 тактовых импульсов через элемент И 19 поступают на счетный вход счетчика 16 циклов, который включен в режим вычитания, на синхровходы первого 14 триггера, регистра 3 частного и регистра 1 делимого. Первый 14 и второй 15 триггеры образуют схему формирования импульса (фиг. 2, 6), фронт которого совпадает с фронтом первого тактового импульса с выхода элемента И 19 (фиг. 2, а), а спад импульса (фиг. 2, б) совпадает с фронтом второго тактового импульса с выхода элемента И 19 (фиг. 2, а). Импульс логической единицы с выхода первого триггера 14 поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6, на втором входе которого в исходном положении присутствует сигнал логического нуля с выхода младшего разряда регистра 3 частного. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 формируется сигнал логической единицы, который поступает на вход управления блока 11 преобразования кода делителя, на вход переноса и второй информационный вход (п+2)-го разряда первого сумматора 4. Код нормализованного делителя с выхода первого коммутатора 10 инвертируется блоком 11 преобразования кода делителя и поступает на второй информационный вход разрядов с первого по (п+1)-й первого сумматора 4. На второй информационном входе первого сумматора. 4 значение нормализованного кода делителя представляется в дополнительном коде. На первый информационный вход первого сумматора 4 подается сдвинутый на один разряд в сторону старшего разряда прямой код. делимого с выхода регистра 1 делимого, причем на первый информационный вход первого разряда первого сумматора 4 подается сигнал логического нуля.

В первом сумматоре 4 производится вычитание нормализованного кода делителя, из кода делимого (в первом цикле определения цифр частного вычитание является обязательным в силу данного алгоритма деления). На первых (п+ -разрядных выходах первого сумматора 4 фор- мируется код остатка. Знак остатка формируется на выходе (п+ 2)-го разряда первого сумматора 4 и соответствует сигналу логического нуля, если остаток положительный, или сигналу логической единицы, если остаток отрицательный. Соответственно, в первом случае в регистр 3 частного в качестве цифры частного необходимо записать сигнал логической единицы, а во втором случае - сигнал логического нуля. Сигнал знака остатка с выхода (п+2)-го знакового разряда первого сумматора 4 инвертируется элементом НЕ 5 и поступает на информационный вход регистра 3 частного. Код остатка с выхода первого сумматора 4 поступает на информационный вход регистра 1 делимого.

0 По спаду первого тактового импульса с выхода элемента И 19 (фиг. 2, а) сигнал с выхода элемента НЕ 5 записывается в младший разряд регистра 3 частного, а код остэт- ка с выхода первого сумматора 4

5 записывается в регистр 1 делимого. Одновременно по спаду первого тактового импульса, поступающего на счетный вход счетчика 16 циклов, значение кода на его выходах, определяющее число циклов опре0 деления цифр частного, уменьшается ма единицу. Этим заканчивается цикл определения первой цифры частного.

После окончания формирования первой цифры частного на выходе первого триггера

5 14 устанавливается сигнал логического нул (фиг. 2, б), который поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 и сохраняется на нем до конца операции деления. Сигнал на выходе элемента ИСКЛЮ0 ЧАЮЩЕЕ ИЛИ 6 в последующих циклах определения цифр частного повторяет сигнал на своем втором входе, т.е. сигнал с выхода младшего разряда регистра 3 част- ного - значение цифры частного, записан5 ной в предыдущем цикле. После окончания формирования первой цифры частного на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 устанавливается логический сигнал первой цифры частного, который поступает на вход

Q управления блока 11 преобразования кода делителя, на вход переноса и второй информационный вход (п+2)-го разряда первого сумматора 4. Если остаток при формировании первой цифры частного был отрицатель5 ный, то в младший разряд регистра 3 частного записана первая цифра частного - логический ноль, который разрешает прохождение нормализованного кода делителя на второй информационный вход первого

0 сумматора 4 в прямом коде. Если остаток при формировании первой цифры частного был положительный, то в младший разряд регистра 3 частного записана первая цифра частного в виде логической единицы, которая переводит нормализованный код

5

делителя, поступающий на второй информационный вход первого сумматора 4, в дополнительный код.

Таким образом, если остаток при формировании первой цифры частного отрицэтельный, то в первом сумматоре 4 производится сложение остатка с нормализованным кодом делителя. В случае, если остаток положительный, в первом сумматоре 4 производится вычитание из остатка нормализованного кода делителя.

Знак очередного остатка формируется на выходе (п+2)-го разряда первого сумматора 4, инвертируется элементом НЕ 5 и поступает на информационный вход регистра 3 частного. Код очередного остатка с выхода первого сумматора 4 поступает на информационный вход регистра 1 делимого. По спаду второго тактового импульса с выхода элемента И 19 (фиг. 2, а) в младший разряд регистра 3 частного записывается знак остатка - вторая цифра частного, при этом первая цифра частного из младшего разряда и значение последующих разрядов регистра частного сдвигаются на один разряд в сторону старшего разряда, а код остатка записывается в регистр 1 делимого. Одновременно по спаду второго тактового импульса с выхода элемента И 19 (фиг. 2, а) код на выходе счетчика 16 цикдов уменьшается еще на единицу Так происходит формирование и запись второй цифры частного.

Аналогичным образом происходит вычисление и запись последующих цифр частного. При вычислении очередной цифры частного код на выходе счетчика 16 циклов уменьшается на единицу и определяет оставшееся количество циклов, которое необходимо произвести для вычисления частного. При выполнении Srro цикла вычисления цифры частного по спаду Si тактового импульса с выхода элемента И 19 в младший разряд регистра 3 частного записывается последняя цифра частного, на выходе счетчика 16 циклов устанавливается нулевой код, который поступает на входы дешифратора 17 нуля. Нулевой код на входах дешифратора 17 нуля формирует на его выходе сигнал логического нуля (фиг. 2, в}, который поступает на второй вход элемента И 19 и запрещает прохождение тактовых импульсов с выхода генератора 18 тактовых импульсов на выход элемента И 19 (фиг. 2, а). Процесс определения цифр частного и операция деления двух двоичных чисел на этом заканчивается. На выходах регистра 3 частного оказывается записанным код частного, содержащий целую и дробную часть.

Время выполнения операции деления двух двоичных чисел определяется зависимостью

tfte-Al/Br 1такт стТ °92А|

5 092 В,+ 1)+с или

Тдел А|/В| Т.такт (К| + С)

1такт (Эр| + 1) + С,

т.е. время выполнения операции деления двух двоичных чисел определяется значением показателя К| степени множителя норма- лиэации, который вычисляется перед началом операции деления для нормализации кода делителя и определяет число циклов определения цифр целой части частного с требуемой точностью вычисления дробной части частного (числом ее разрядов - с), Если при нормализации кода делителя показатель К) степени множителя нормализации получается меньшим или равным нулю, т.е. К 0, на выходе второго коммутатора 12 формируется нулевой код, сдвига кода делителя не производится и код делителя с выхода регистра 2 делителя через первый коммутатор 10 и блок 11 преобразования кода делителя поступает на второй информационный вход первого сум- матора 4 без смещения. На выходе третьего сумматора 20 формируется код постоянной устройства -с, определяющий число циклов определения цифр дробной части частного. Данный код записывается в счетчик 16 циклов. Операция вычисления цифр частного осуществляется в соответствии с алгоритмом деления, и время выполнения деления определяется зависимостью

40

tAen Ai/B| tiaia С.

5

Если в данном случае требуется частное вычислить с точностью до целой части, т.е. с 0, то на выходе третьего сумматора 20 после нормализации кода делителя сохраняется нулевой код, который записывается в счетчик 16 циклов. На выходе дешифратора 17 нуля сохраняется сигнал логического нуля, блокирующий выполнение циклов оп- ределения цифр частного. На выходах реги0 стра 3 частного сохраняется нулевой код, соответствующий величине частного.

Здесь рассматривается операция деления модулей двоичных чисел - знаки делимого и делителя в процессе деления не

5 используются. Знак частного может быть определен, например, в результате сравнения логических сигналов знаков делимого и делителя на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 6 и записан в триггер знака частного

одновременно с записью кодов делимого и делителя соответственно в регистр 1 делимого и регистр 2 делителя.

Формула изобретения Устройство для деления двоичных чисел, содержащее регистры делимого и частного, два сумматора, два блока вычисления логарифмов, два коммутатора, блок преобразования кода делителя, элемент НЕ. элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и блок упр авлетния. содержащий генератор такто- вых им пуЦ сов, элемент И, счетчик циклов и два триггера, при этом выходы разрядов с первого по(п+1)-й регистра делимого соединены с первыми информационными входами разрядов с второго по (п+2)-й первого сумматора, первый информационный вход первого разряда которого соединен с входом логического нуля устройства выход суммы первого сумматора соединен с информационным входом регистра делимого, выходы первого и второго блоков вычисления логарифмов соединены с перв ым и вторым информационными входами первых К-разрядов второго сумматора (где К - показатель степени множителя нормализации), вход переноса которого соединен с входом логйч ес кой единицы устройства, выход ре- гистра Делителя соединен с входом второго блока1 вычисления логарифмов информационным входом первого коммутатора, выход которого соединен с информационным входом блока преобразования кода делителя, выходы которого соединены с вторыми информационными входами первых п+1 разрядов первого сумматора, вход переноса и второй информационный вход (п+2)-го разряда которого соединены с управляющим входом блока преобразования кода делите0

5

ля и выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом первого триггера и синхровходом второго триггера, инверсный выход которого соединен с информационным входом первого триггера, синхровход которого соединен с синхровходами регистров частного и делимого, сччетным входом счетчика циклов и выходом элемента И, первый вход которого соединен с выходом генератора тактовых импульсов, информационный вход второго триггера соединен с входом логической единицы устройства, выход знакового разряда первого сумматора соединен с входом элемента НЕ, отличающееся тем. что, с целью повышения быстродействия, в блок управления введены третий сумматор и дешифратор нуля, выход которого соединен с вторым входом элемента И, первый и второй информационные входы (К+ 1)-х разрядов второго сумматора соединены с входами логических нуля и единицы устройства соответственно, выходы К-разрядов суммы второго сумматора соединены с информационными входами второго коммутатора, управляющий вход которого соединен с выходом знакового разряда второго сумматора, выход второго коммутатора соединен с управляющим входом первого коммутатора и первым информационным входам третьего сумматора, второй информационный вход которого соединен с входом константы устройства, выход суммы третьего сумматора соединен с установочным входом счетчика циклов, выходы которого соединены с входами дешифратора нуля, выход элемента НЕ соединен с информационным входом регистра частного, выход младшего разряда которого соединен с вторым входом элемен- 0 та ИСКЛЮЧАЮЩЕЕ ИЛИ.

0

5

0

5

ФигЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| Устройство для деления | 1991 |

|

SU1783523A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для деления | 1985 |

|

SU1322264A1 |

| Устройство для деления | 1986 |

|

SU1357947A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах. Цель изобретения - повышение быстродействия устройства. Для вычисления цифр целой части частного устанавливается число циклов определения цифр частного, равное предполагаемой разрядности величины частного, которая вычисляется по исходным кодам делимого и делителя перед йачалом операции деления и которая для всех допустимых значений делимого и делителя является величиной, меньшей или равной разрядности операндов делимого и делителя. Устройство для деления двоичных чисел содержит регистр делимого, регистр делителя, регистр частного, два сумматора, элемент НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два блока вычисления логарифмов, два коммутатора, блок преобразования кода делителя, блок управления, состоящий из двух триггеров, счетчика1 циклов, дешифратора, нуля, генератора тактовых импульсов элемента И, сумматора. 5 ил. сл С

| Устройство для деления двоичных чисел | 1982 |

|

SU1103224A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1492508 | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

Авторы

Даты

1992-12-23—Публикация

1990-10-01—Подача