1

Изобретение относится к контрольно-иэмеритепьнэ;й технике, может, в частности, быть использовано при функционально-ютати- ческол1 контроле цифровых интегральных схем и узлов,

При контроле нараметров гштегральных схем, логических узлоВ; постооенных на их базе, важнейшей задачей является подача на нх входы заданных уровней сигналов нуль я единица. При этом особенностью контроля является малый ток от входных сигналов, если входной сигнал ра- вен логической единице, и большой ток, втекающий в источник входных сигналов, если входной сигнал равен логическому ну ,пю,

Известен формирователь имнульсоВ} содержащий операционный или дифференциальный усилитель, цепь обратной связи с аъткода операциоршого усилителя на его инвертирующий вход, в которых входное напряжение, подводимое к неш вертирующему входу операционного (дифференциального) уси- лнтелЯз в точности повторяется на его вы- коце 3-J .

В этой схеме выходной сигнал, равный входному, ноявляется на нагрузке, когда включается цець обратной связи, для чего схема содержит ключевой элемент на униполярном или биполярном транзисторе.

Однако акая схема расходует большую мощность источников питания при выходном напряжении, равном логической единице.

Наиболее близок к предлагаемому формирователь импульсов, содержащий операционный усилитель с двумя входами, к ьыХОД5 которого подключен выходной транзистор, цепь нагрузки из параллельно соещшенных транзистора и резистора один из выводов которой подключен к эмиттеру выходного транзистора, KoivtMyTaTOp опорных на- , содержащий два транзистора, эми-ттеры которых подключены к неинвертирующему входу операционного усштнтеля, ifflBepTop, входную и выходную клеммы 2..

Однако такой формирователь импульсов не обеспечивает достаточной точности уроьней логических сигналов.

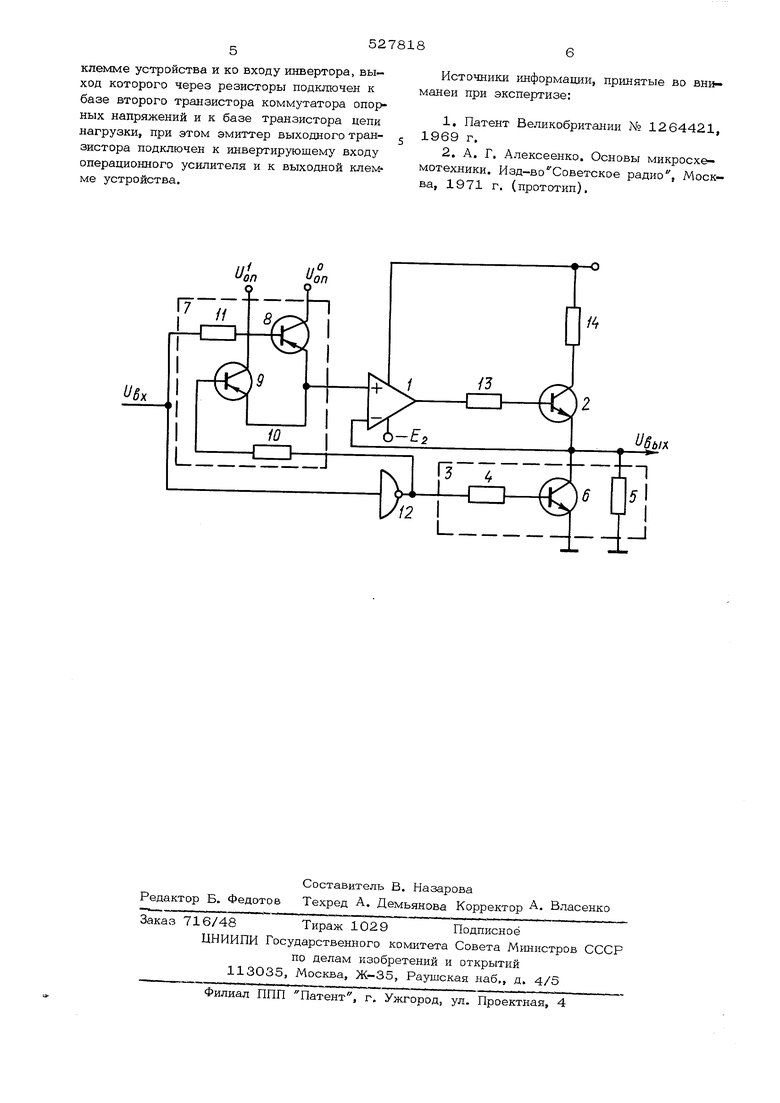

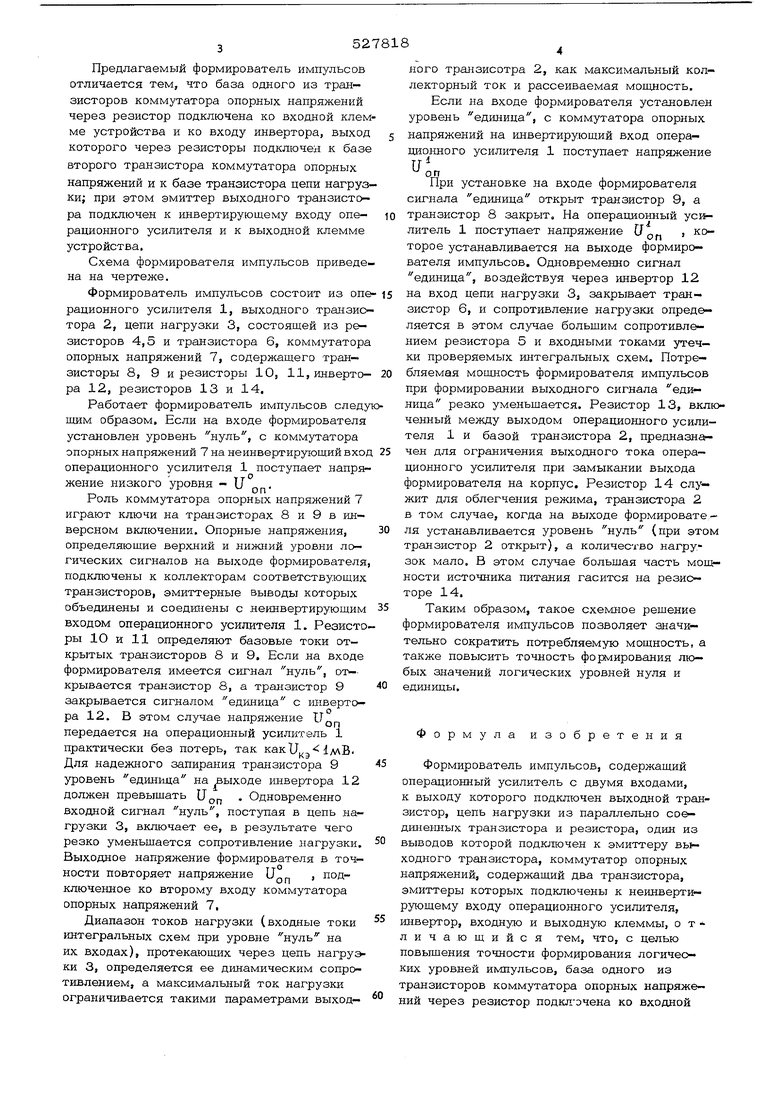

Цель изобретения - повышение точности формирования логических уровней импульсов Предлагаемый формирователь импульсов отличается тем, что база одного из транзисторов коммутатора опорных напряжений через резистор подключена ко входной клем ме устройства и ко входу инвертора, выход которого через резисторы подключен к базе второго транзистора коммутатора опорных напряжений и к базе транзистора пени нагруз ки; при этом эмиттер выходного транзистора подключен к инвертирующему входу oneрационного усилителя и к выходной клемме устройства. Схема формирователя импульсов приведе на на чертеже. Формирователь импульсов состоит из one рационного усилителя 1, выходного транзистора 2, цепи нагрузки 3, состоящей из резисторов 4,5 и транзистора 6, коммутатора опорных напряжений 7, содержащего транзисторы 8, 9 и резисторы 10, 11, инвертора 12, резисторов 13 и 14. Работает формирователь импульсов следу щим образом. Если на входе формирователя установлен уровень нуль, с коммутатора опорных напряжений 7 на неинвертирующий вхо операционного усилителя 1 поступает напряжение низкого уровня - и ,-,„. Роль коммутатора опорных напряжений 7 играют ключи на транзисторах 8 и 9 в инверсном включении. Опорные напряжения, определяющие верхний и нижний уровни логических сигналов на выходе формирователя подключены к коллекторам соответствующих транзисторов, эмиттерные выводы которых объединены и соединены с неинвертирующим входом операционного усилителя 1. Резисто ры Ю и 11 определяют базовые токи открытых транзисторов 8 и 9, Если на входе формирователя имеется сигнал нуль, oi крывается транзистор 8, а транзистор 9 закрывается сигналом единица с инвертора 12. В этом случае напряжение U передается на операционный усилитель 1 практически без потерь, так каки 1ллВ. Для надежного запирания транзистора 9 уровень единица на выходе инвертора 12 должен превыщать Up Одновременно входной сигнал нуль, поступая в цепь нагрузки 3, включает ее, в результате чего резко уменьщается сопротивление нагрузки. Выходное напряжение формирователя в точности повторяет напряжение U , подключенное ко второму входу коммутатора опорных напряжений 7, Диапазон токов нагрузки (входные токи интегральных схем при уровне нуль на их входах), протекающих через цепь нагруэки 3, определяется ее динамическим сопротивлением, а максимальный ток нагрузки ограничивается такими параметрами выход- ного транзисотра 2, как максимальный коллекторный ток и рассеиваемая мощность. Если на входе формирователя установлен уровень единица, с коммутатора опорных напряжений на шiвepтиpyющий вход операционного усилителя 1 поступает напряжение При установке на входе формирователя сигнала единица открыт транзистор 9, а транзистор 8 закрыт. На операционный усилитель 1 поступает напряжение UQ., , которое устанавливается на выходе формирователя импульсов. Одновременно сигнал единица, воздействуя через инвертор 12 на вход цепи нагрузки 3, закрывает транзистор 6, и сопротивление нагрузки определяется в этом случае большим сопротивлением резистора 5 и входными токами утечки проверяемых интегральных схем. Потребляемая мощность формирователя импульсов при формировании выходного сигнала единица резко уменьшается. Резистор 13, включенный между выходом операционного усилителя 1 и базой транзистора 2, предназначен для ограничения выходного тока операционного усилителя при замыкании выхода формирователя на корпус. Резистор 14 служит для облегчения режима, транзистора 2 в том случае, когда на выходе формирователя устанавливается уровень нуль (при этом транзистор 2 открыт), а количество нагрузок мало. В этом случае большая часть мощности источника питания гасится па резисторе 14, Таким образом, такое схемное решение формирователя импульсов позволяет значительно сократить потребляемую мощность, а также повысить точность формирования любых значений логических уровней нуля и единицы. Формула изобретения Формирователь импульсов, содержащий операционный усилитель с двумя входами, к выходу которого подключен выходной транзистор, цепь нагрузки из параллельно соединенных транзистора и резистора, один из выводов которой подключен к эмиттеру выходного транзистора, коммутатор опорных напряжений, содержащий два транзистора, эмиттеры которых подключены к неинверти- руюшему входу операционного усилителя, инвертор, входную и выходную клеммы, отличающийся тем, что, с целью повыщения точности формирования логичеоких уровней импульсов, база одного из транзисторов коммутатора опорных напряжений через резистор подклэчена ко входной

клемме устройства и ко входу инвертора, выход которого через резисторы подключен к базе второго транзистора коммутатора опорных напряжений и к базе транзистора цепи нагрузки, при этом эмиттер выходного транзистора подключен к инвертирующему входу операционного усилителя и к выходной клемме устройства.

Источники информации, принятые во вн№манеи при экспертизе:

1.Патент Великобритании № 1264421, 1969 г.

2.А. Г. Алексеенко. Основы микросхемотехники. Изд-во Советское радио, Москва, 1971 г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1980 |

|

SU884100A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Устройство для ускоренного заряда аккумуляторной батареи | 1988 |

|

SU1557630A2 |

| Стабилизированный преобразователь напряжения постоянного тока | 2024 |

|

RU2822294C1 |

| ПРЕОБРАЗОВАТЕЛЬ МОЩНОСТИ В ЧАСТОТУ | 1992 |

|

RU2057349C1 |

| Транзисторный ключ | 1987 |

|

SU1471297A1 |

| Устройство для контроля цифровых схем | 1986 |

|

SU1522130A1 |

| Стабилизированный преобразователь постоянного напряжения | 1989 |

|

SU1700539A1 |

| Устройство для моделирования электромагнитных процессов в асинхронных машинах | 1989 |

|

SU1681315A1 |

| УСТРОЙСТВО ТОКОВОЙ ЗАЩИТЫ ЭЛЕКТРОУСТАНОВКИ | 1993 |

|

RU2114496C1 |

Авторы

Даты

1976-09-05—Публикация

1975-05-04—Подача