вания 9, а через инвертор 13- с вторым входом первой схемы И 10.

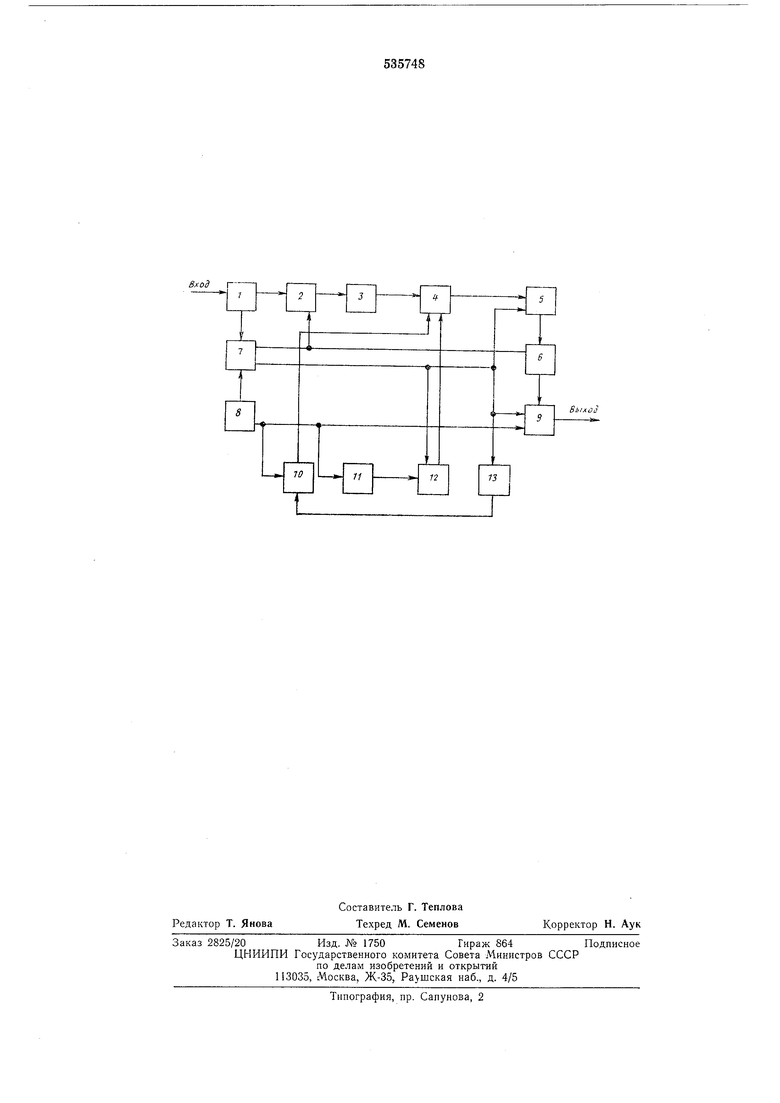

Устройство работает следующим образом.

Сигнал с входа устройства после входного узла 1 поступает на фазовый детектор 2, где он сравнивается с онорным напряжением, вырабатываемым в формирователе б. Форма опорного напряжения такова, что при сравнивании его с сигналом с выхода узла 1 обеснечивавается дискриминационная характеристика, позволяющая с нужной точностью определить границы пачек импульсов. Период опорного напряжения равен периоду следования начек импульсов, что обеспечивается за счет запуска формирователя b импульсами с выхода делителя 5, находящегося под контролем унравляющего элемента 4.

При рассогласовании фаз сигналов сигналы ошибки с фазового детектора 2 после усреднения в усреднителе 3 поступают на управляющий элемент 4 и обеспечивают корректирование делителя 5 в сторону уменьшения фазового рассогласования. Коррекция продолжается до обеспечения правильного фазирования. Наличие правильного фазирования, а также его отсутствие индицируется индикатором 7 фазирования.

При вхождении в синхронизм на вход делителя о через управляющий элемент 4 поступают тактовые импульсы с выхода источника 8 через схему И 10, которая открыта для прохождения тактовых импульсов сигналом отсутствия фазирования с индикатора 7, прошедшим через инвертор 13. Соответственно в режиме вхождения в синхронизм устранение рассогласования происходит с шагом, равным периоду следования тактовых импульсов.

jcS результате устранения рассогласования фаз входного и онорного сигналов индикатор / выдает сигнал правильного фазирования, по которому осуществляются следующие операции: изменяется коэффициент деления делителя о (он становится в п раз больше), закрывается схема И 10, на которую с инвертора 13 поступает запрещающий сигнал, на делитель 5 через управляющий элемент 4 разрешается прохождение импульсов с частотой следования в п раз выще тактовой, которые формируются в умножителе 11. Прохождение этих импульсов к управляющему элементу 4 обеспечивается за счет поступления на схему И 12 разрешающего сигнала с индикатора 7.

Таким образом, корректирование делтеля 5 в режиме поддержания синхронизма обеспечивается с шагом в п раз меньше периода тактовой частоты.

Импульсы, соответствующие границам пачек импульсов входного сигнала, поступают на выход устройства через блок стробироваиия 9, на который в установившемся режиме поддержания синхронизма поступают разрешающии сигнал с индикатора 7, подставки с формирователя 6 и тактовые импульсы с выхода источника 8, в результате чего на выход устройства в режиме поддержания синхронизма ностунают тактовые импульсы, соответствующие границам пачек импульсов входного сигнала, причем временное положение этих импульсов при отдельных корректировках делителя 5 не изменяется.

Формула изобретения

Устройство дискретного фазирования, содержащее последовательно соединенные входной узел, фазовый детектор, усреднитель, управляющии элемент, делитель частоты и формирователь опорного напряжения, выход которого подключен к второму входу фазового детектора и к входу индикатора фазирования, подключенного к выходу входного узла и к

выходу источника тактовой частоты, отличающееся тем, что, с целью уменьшения флуктуации фазы опорного напряжения в установившемся режиме при большом уровне помех, к выходу формирователя опорного напряжения подключен блок стробирования, источник тактовой частоты подключен к дополнительпому входу управляющего элемента через первую схему И и через последовательно соединенные умножитель тактовой частоты и

вторую схему И, а к блоку стробирования - непосредственно, нри этом выход индикатора фазирования непосредственно соединен с вторым входом делителя частоты, вторым входом второй схемы И и третьим входом блока стробирования, а через инвертор - с вторым входом первой схемы И.

Источники информации, принятые во внимание при экспертизе изобретения: 1. Мартынов Е. М. Синхронизация в системах передачи дискретных сообщений, М., «Связь, 1972 г., стр. 151-158 (прототип).

г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство дискретного фазирования по периодически следующим пачкам импульсов | 1973 |

|

SU534880A1 |

| Устройство фазирования регенераторов цифрового сигнала | 1978 |

|

SU786036A1 |

| Устройство синхронизации | 1982 |

|

SU1107312A1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| ВСЕСОЮаНАЯ i | 1973 |

|

SU372717A1 |

| Устройство фазирования | 1979 |

|

SU788410A1 |

| УСТРОЙСТВО для ПРИЕМА ШИРОКОБАЗОВЫХ СИГНАЛОВ | 1973 |

|

SU363183A1 |

| Устройство выделения тактовых импульсов | 1986 |

|

SU1425864A2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ ШИРОКОПОЛОСНЫХ ШУМОПОДОБНЫХ СИГНАЛОВ | 1979 |

|

SU1840109A1 |

| Устройство приема зондирующего сигнала | 1987 |

|

SU1566495A1 |

Авторы

Даты

1976-11-15—Публикация

1973-04-13—Подача