1

Изобретение относится к автоматике, телемеханике, вычиспительной технике и связи,может использоваться в различных системах передачи и хранения дискретной информации в условиях, когда необходимо кодировать информацию с помощью корректирующего кода, обеспечивающего исправление многократных ошибок.

Известно устройство для кодирования корректирующих кодов, позволяющее исправлять многократные ощибки, содержащее коммутатор и регистр сдвига со встроенными или вынесенными сумматорами по модулю два. Кодирование выполняется путем деления на порождающий или проверочный многочлен Основание кода равно двум. Код является циклическим 1.

Однакэ такое устройство имеет сравнительно низкое быстродействие, связанное с тем, что двоичная информация обрабатывается поразрядно.

Известно также кодирующее устройство корректирующего кода, содержащее блок вычисления контрольных чисел и блок утфавления C2j.

2

Однако это устройство действует медленно, так как после подачи в него всех информационных символов необходимо еще 2 & тактов сдвига (второй и третий этапы), прежде чем начнут выдаваться контрольные символы. (Здесь S - количество контрольных символов).

Цель изобретения - повышение быстродействия устройства.

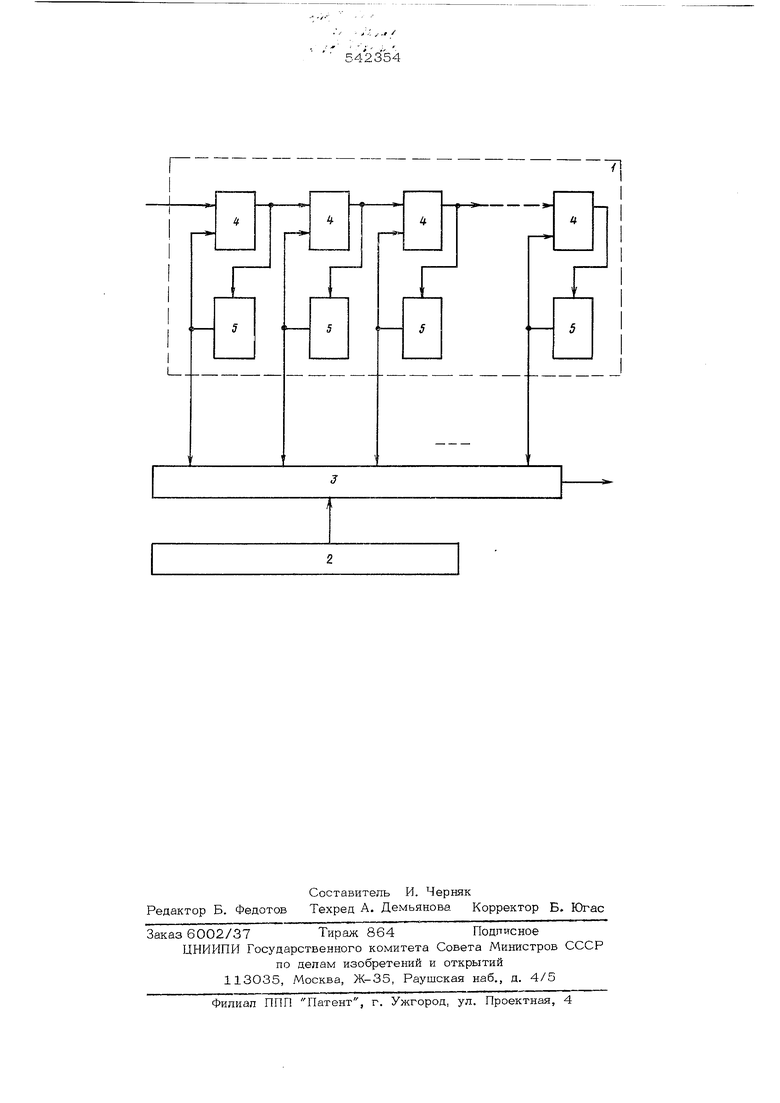

Для этого Б кодирующее устройство кор ректирующего кода, содержащее блок вычисления контрольных чисел и блок управления, введен преобразователь число-код, к управляющему входу которого подключен выход блока управления, а к информационным входам подсоединены соответствующие выходы разрядов блока вычисления контрольных чисел. Блок вычисления контрольных чисел выполнен в виде последовательно соединенных ячеек, каждая из которых состоит из последовательно соединенных комбинационного сумматора по модулю числа, равного степени два, а регистр хранения конт рольного числа, выход которого является выходом соответствующего разряда блока вычисления контрольных чисел. На чертеже приведена структурная электрическая схема кодирующего устройства корректирующего кода. Устройство содержит блок вычисления контрольных чисел 1, блок управления 2 и преобразователь число-код 3. К управляющему входу преобразователя число-код подключен выход блока управления 2, а к информационным входам подсоединены соответствующие выходы разрядов блока вычисления контрольных чисел 1, выполненного в виде последовательно соединенных ячеек, каждая из которых состоит из последовательно соединенных комбинационного сумма тора 4 по модулю числа, равного степени два, и регистра хранения контрольного числа 5, выход которого является выходом соответствующего разряда блока 1. Кодирование происходит в два этапа. В течение первого этапа в блоке 1 вычисляются по информационным символам контрольные числа. На втором этапе преобразователь число-код 3 преобразует эти в контрольные символы, которые передаются на выход устройства. Перед началом работы устройства регист ры 5 всех разрядов блока 1 обнуляются. Затем на вход устройства последовательно (начиная с символа CL,) поступают С ичные информационные символы к Каждый информационный символ может принимать одно из значений 0,1,..., ( - 1 При выполнении устройства на двоичных элементах каждый информационный символ представляет собой W -разрядное число, записанное в двоичной системе счисле ния. Блок 1 вычисляет контрольные числа за к шагов. На каждом шаге обрабатывается один информационный символ (на первом символ С( 1 , на втором 0( и т.д.). Резуль таты обработки записываются в регистры хранения контролируемых чисел 5. Обозначим через Б число, записанное в i -тый регистр 5 после (У-того щага. Тогда работу блока 1 на ( У + 1)-вом шаге можно описать следующим образом. Информационный символ а к-о- поступает в первый сумматор 4, где складывается с содержимым первого регистра 5 (т.е. с числом В ). Полученная сумма а .J +BI представляет собой число записывается в первый регистр 5 как результат нового шага. Одновременно сумма .+Bi i, поступает во второй сумматор 4, где складывается с содержимым второго резистра 5 (т.е. с числом В, ). Полученная сумма В представляет собой число ) 2И записывается во второй регистр 5 как результат нового шага. Одновременно сумма поступает в третий сумматор 4, где складывается с содержимым третьего регистра 5 (т.е. с числом BVv/ 3 ) И т.д. Работа сумматоров 4 и регистров 5. формирование импульсов, тактирующих запись в регистры 5, синхронизируются блоком управления 2 (соответствующие связи на чер теже не показаны). Поскольку все сумматоры 4 комбинационные, каждый шаг работы блока 1 в принципе может происходить между двумя информационными символами. По окончании к-того щага работы блока 1 в регистры 5 записаны соответственно числа В/«, , .... В, Они и являются искомыми контрольными числами. Вычислением контрольных чисел заканчивается работа блока 1 на первом этапе. Преобразователь число-код 3 на этом этапе не включается. На втором этапе контрольные числа в соответствии с управляющими сигналами, поступающими на управляющий вход преобразователя 3, нроходят из регистров 5 блока 1 на соответствующие информационные входы преобразователя число-код 3, где каждое контрольное число В- преобразуется в соответствующую ему f -тую группу контрольных символов, в преобразователе 3 образуется наименьший неотрицательный вычет tj. числа ао модулю N , представляющему собой степень двойки, причем образование вычета t); сводится к отбрасыванию старщих разрядов соответствующего контрольного числа Б . При этом отбрастарщих разрядов и обсывается тп- - п разуется п -разрядное двоичное число 13 - . Разделяя это число на подблоки по W двоичных разрядов в каждом, преобразователь 3 формирует 1 -тую группу контрольных символов, так как такое разделение есть не что иное, как формирование (J, ичиой записи числа В преобразователе число-код 3 формируются S групп контрольных символов (из каждого контрольного числа формируется группа контрольных символов). Эти группы проходят на выход устройства. На вход устройства на втором этапе работы информационные символы не подаются. Роль блока 1 на втором этапе заключается в хранении в регистрах 5 вычисленных на первом этапе контрольных чисел. Формированием групп контрольных симвс лов и выдачей их на выход устройства процесс кодирования завершается. Контрольные символы вычисляются в уст ройстве таким образом, что любые две кодовые последовательности отличаются друг от друга по крайней мере в Ь позициях Это значит, что минимальное кодовое расстояние равно S -v 1 , и в информации, закодированной с помощью предлагаемого уст ройства, можно исправить S/2 ошибок. При выполнении устройства на двоичных элементах и работе с двоичным каналом связи каждый информационный и каждый контрольный символы представляют собой (/ -разрядное двоичное число, а каждое контрольное число В является -разрядным двоичным числом. в предлагаемом устройстве контрольные символы начинают выдаваться сразу же по окончании поступления в устройство инфор мационных символов. Таким образом, быстродействие предлагаемого устройства превышает быстродействие известных. В предлагаемом устройстве содержатся только сумматоры 4 по модулю числа, равного степени двойки. Вычет некоторой величины по такому модулю сводится к отбра сыванию старших разрядов ее двоичного представления. Поэтому сумматоры по модулю числа, равного степени двойки, сущес венно прош.е сумматоров по модулю просто го числа. В результате в предлагаемом устройстве сокращено количество оборудования. Предлагаемое устройство кодирует информацию таким образом, что при декодировании необходимо выполнять только операции в поле рациональных чисел, т.е. обы ные машинные операции. Для реализации одной операции в поле рациональных чисел на универсальной вычислительной машине требуется, как правило, одна машинная команда. В результате декодирования информации, закодированной с помощью предлагаемого устройства, проще декодирования информации, закодированной с помощью известных устройств. Формула изобретения 1.Кодирующее устройство корректирующего кода, содержащее блок вычисления контрольных чисел и блок управления, о тличающееся тем, что, с целью повышения быстродействия, в него введен преобразователь число-код, к его управляющему входу подключен выход блока управления, а к информационным входам подсоединены соответствующие выходы разрядов блока вычисления контрольных чисел. 2.Устройство ПОП.1, отлича ющ е е с я тем, что блок вычисления контрольных чисел выполнен в виде последовательно соединенных ячеек, каждая из которых состоит из последовательно соединенных комбинационного сумматора по модулю числа, равного степени два, и регистра хранения контрольного числа, выход которого является выходом соответствующего разряда блока вычисления контрольных чисел. Источники информации, принятые во внимание при экспертизе: 1.Берлекэмп Э. Алгебраическая теория кодирования, Мир, М., 1971, стр. 134, 138-142. 2.Авторское свидетельство СССР № 443389, Q 06 F 11/10, 14.11Л2 ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодирующее устройство линейного корректирующего кода | 1972 |

|

SU443389A1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2259638C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ОТ ЧИСЛА | 2000 |

|

RU2209460C2 |

| Устройство для формирования информативных признаков при распознавании изображений | 1986 |

|

SU1361591A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1989 |

|

SU1793546A1 |

| Устройство для кодирования кода рида-соломона над простым полем | 1977 |

|

SU744576A1 |

| Устройство для вычисления коэффициентов уолша | 1977 |

|

SU693380A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

Авторы

Даты

1977-01-05—Публикация

1975-03-04—Подача