(54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения одиночного импульса | 1978 |

|

SU744935A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU898601A1 |

| Устройство для моделирования сетевых графов | 1987 |

|

SU1462346A1 |

| Устройство для синхронизации импульсов | 1980 |

|

SU942253A1 |

| Устройство для свертки по модулю три | 1989 |

|

SU1674130A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Цифровой частотный дискриминатор | 1980 |

|

SU907793A1 |

| Устройство для задержки импульсов | 1979 |

|

SU805483A1 |

| Устройство для блокировки импульса | 1982 |

|

SU1023642A1 |

1

Изобретение относится к импульсной технике и может быть использовано в различных устройствах преобразования, обработки и передачи информации,

Известное устройство содержит триггеры, логические элементы И-НЕ и формирователи импульсов l.

Недостатком данного устройства является сложность схемы и, как следствие, невысокое быстродействие.

Наиболее близким техническим решением к данному изобретению является устройство тактовой синхронизации, содержащее два яоследовательно соединенных триггера, элемент И-НЕ, первый вход которого подключен к тактовому входу первого триггера, второй вход элемента И-НЕ соединен с единичным выходом первого триггера 2 .

Однако, кроме основного импульса, на вы ходе этого устройства вьщеляется часть второго импульса (помеха), по длительности раного времени срабатывания второго триггера, что приводит к ложному срабатыванию последующих устройств.

Целью изобретения является повышение ломехоустойчивости устройства.

Для этого в устройстве тактовой синхронзации, содержащем два последовательно соединенных триггера, элемент И-НЕ, первый вход которого подключен к тактовому входу первого триггера, второй вход элемента ИНЕ соединен с единичным выходом первого триггера, нулевой выход первого триггера подключен к информационному входу второго триггера, тактовый вход которого соединен с вьлсодом элемента И-НЕ, а единичньш выход второго триггера подключен к третьему входу элемента И-НЕ.

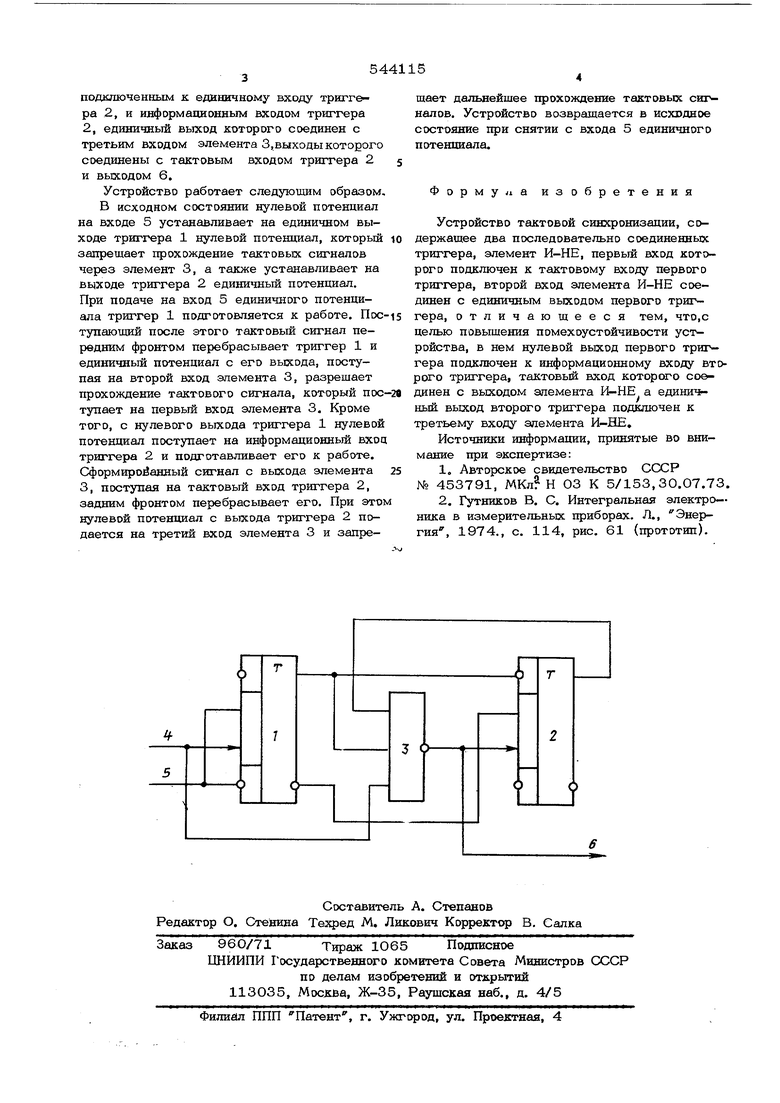

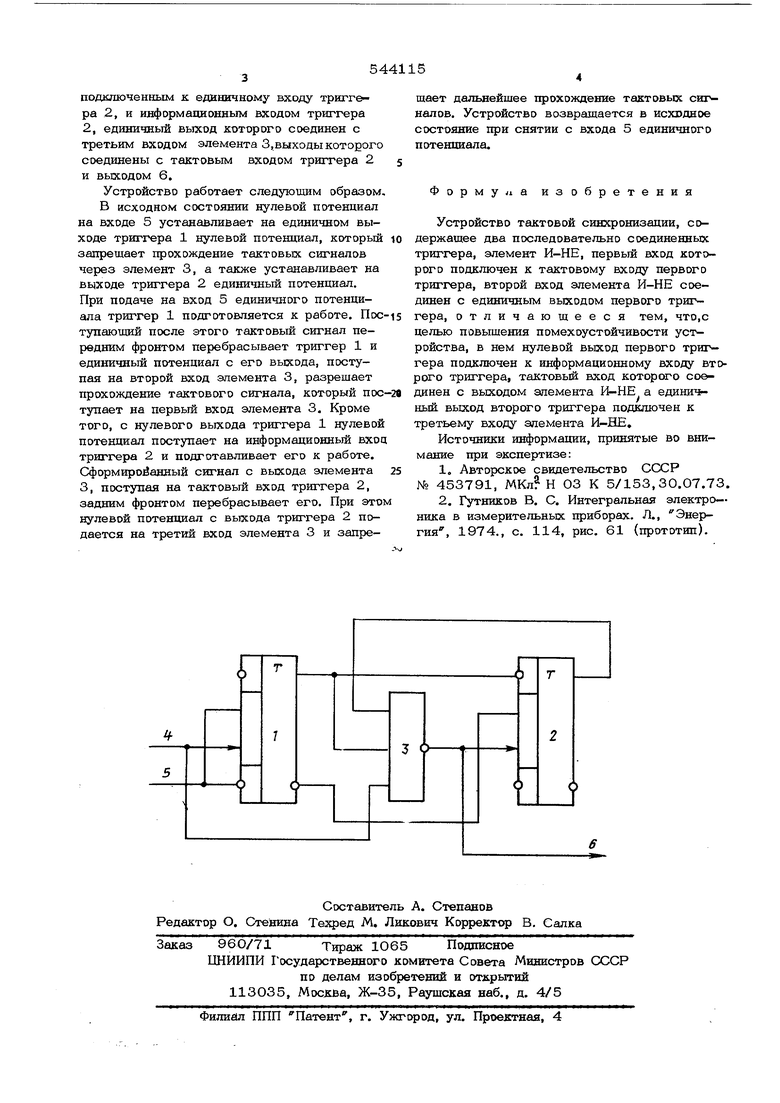

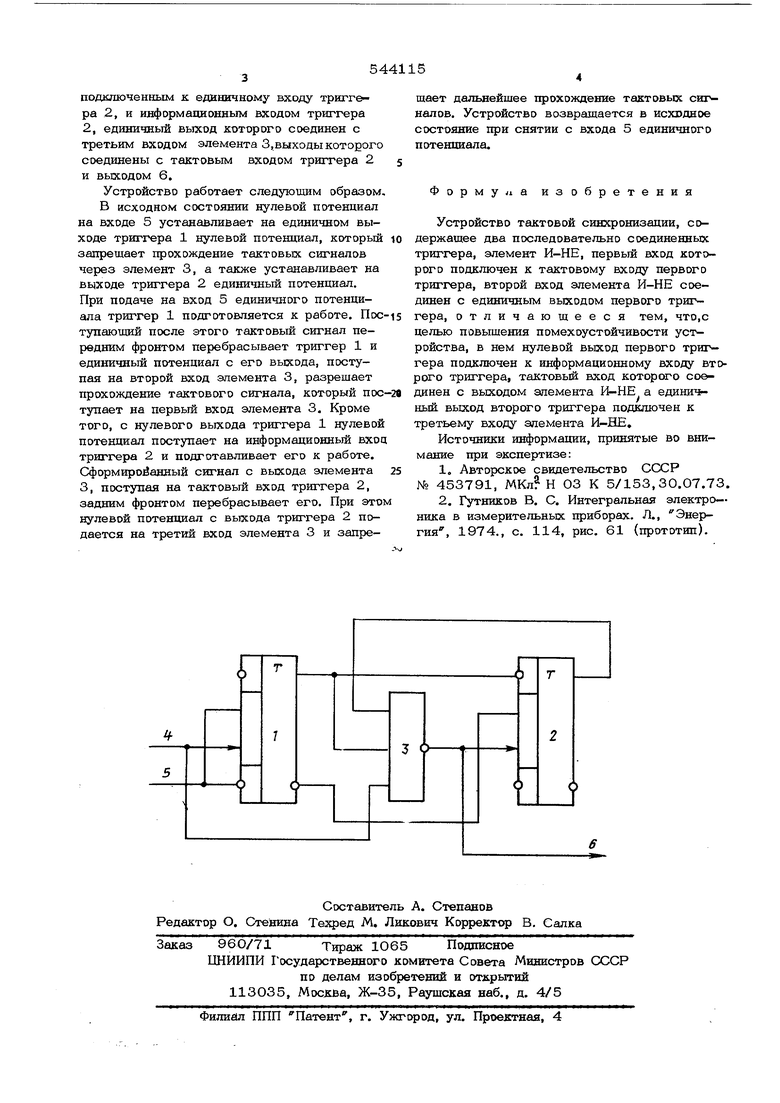

На чертеже приведена схема устройства.

Устройство тактовой синхронизации содержит триггеры 1 и 2, элемент И-НЕ 3, тактовый вход 4, управляющий вход 5 и выход 6, причем входы 4 и 5 подключены соответственно к тактовому входу триггера 1, соединенному с первым входом элемента 3, и нулевому входу триггера 1, соединенному с его информационным входом, единичный и нулевой выходы триггера 1 соединены соответственно с вторым входом элемента 3 подключенным к единичному входу триггера 2, и информационным входом триггера 2,едшгачный выход которого соединен с третьим входом элемента 3,выходы которого соединены с тактовьш входом триггера 2 и выходом 6. Устройство работает следующим образом, В исходном состоянии нулевой потенциал на входе 5 устанавливает на единичном выходе триггера 1 нулевой потенциал, который запрещает прохождение тактовых сигналов через элемент 3, а также устанавливает на выходе триггера 2 единичный потенциал. При подаче на вход 5 единичного потенциала триггер 1 подготовляется к работе. FIocтупающий после этого тактовый сигнал передним фронтом перебрасывает триггер 1 и единичный потенциал с его выхода, поступая на второй вход элемента 3, разрешает прохождение тактового сигнала, который поступает на первый вход элемента 3. Кроме того, с нулевого выхода триггера 1 нулевой потенциал поступает на информационный вход триггера 2 и подготавливает его к работе. Сформированный сигнал с выхода элемента 3,поступая на тактовый вход триггера 2, задним фронтом перебрасывает его. При этом нулевой потенхщал с выхода триггера 2 подается на третий вход элемента 3 и запреt

t щает дальнейшее прохождение тактовых сигналов. Устройство возвращается в исходное стютояние при снятии с входа 5 единичного потенциала. Формула изобретения Устройство тактовой синхронизадии, содержащее два последовательно соединенных триггера, элемент И-НЕ, первый вход которого подключен к тактовому входу первого триггера, второй вход элемента И-НЕ соединен с единичным выходом первого триггера, отличающееся тем, что,с целью повышения помехоустойчивости устройства, в нем нулевой выход первого триггера подключен к информационному входу второго триггера, тактовый вход которого соединен с выходом элемента И-НЕ а единичный выход второго триггера подключен к третьему входу элемента И-НЕ, Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 453791, МКл Н 03 К 5/153,30.07.73. 2.Гутников В. С. Интегральная электроника в измерительных приборах. Л., Энергия, 1974., с. 114, рис. 61 (прототип).

Авторы

Даты

1977-01-25—Публикация

1975-07-14—Подача