Изобретение относится к вычислительной технике и может быть использовано для поиска перемежающихся отказов в микропроцессорных системах в реальном масштабе времени.

Известно устройство для отладки микропроцессорных систем (1), содержащее мультиплексоры адреса и данных, первый счетчик, триггер, формирователь короткого импульса, мультиплексор магистралей, элемент ИЛИ, дешифратор, блоки буферной памяти адреса и данных, вычитающий счетчик импульсов, схему сравнения, первый и второй регистры, первый и второй селекторы, регистр длительности трассы, блок буферной памяти состояния шины управления, формирователь сигнала записи, формирователь сигнала чтения, второй счетчик.

Данное устройство позволяет в принципе "отловить" перемежающийся сбой при отлаживании микропроцессорной системы, работающей в реальном масштабе времени на рабочей скорости. Принцип действия устройства основан на том, что при появлении сбоя микропроцессорная система начнет беспорядочное блуждание по памяти, рассматривая числовые массивы как цепочки команд, а команды как данные или адреса. Устройство позволяет фактически проследить трассу на каждом контролируемом участке циклической программы и, анализируя состояние адресной шины, шины данных, шины управления, выявить адекватность реального функционирования программ отлаживаемой микропроцессорной системы ожидаемому и точно обнаружить момент и характер сбоя в ходе циклической программы.

Недостатком данного устройства является высокая трудоемкость подготовительной работы.

Известно устройство для поиска перемежающихся неисправностей в микропроцессорных системах (2), выбранное в качестве прототипа, содержащее дешифратор, мультиплексор магистралей, двоичный счетчик, блок буферной памяти эталона, мультиплексора адреса, регистр запуска, мультиплексор данных, шесть триггеров, две схемы сравнения, семь элементов И, три элемента ИЛИ, два формирователя сигнала записи, два формирователя сигнала чтения, блок буферной памяти текущего цикла, регистр адреса, формирователь короткого импульса, селектор, регистр управления, вычитающий счетчик импульсов.

Принцип действия устройства основан на том, что всякая микропроцессорная система, отработав программу инициализации и тестовых проверок неотъемлемого оборудования, выходит на циклическую обработку рабочей программы. При постоянной совокупности внешних обрабатываемых сигналов, что достигается на стенде, микропроцессорная система "крутит" фактически один и тот же цикл обработки. Местом "привязки" в этом цикле служит совокупность P сигналов запуска, поступающих из контролируемой микропроцессорной системы и определяемых предварительно из анализа рабочей программы. После появления заданного количества P условий запуска устройство сформирует эталонный массив информации, поступающей параллельно из N контрольных точек отлаживаемой микропроцессорной системы. Сформированный массив эталонной информации сравнивается потактно с массивом информации, поступающим из N контрольных точек после каждого последующего появления совокупности P сигналов запуска. При появлении несовпадения этих массивов инициируется в отлаживающей ЭВМ (персональном компьютере) программа обработки режима анализа устройства.

Недостатком данного устройства является невозможность обнаружения перемежающихся отказов в микропроцессорных системах с обслуживанием процедур прерывания, поскольку каждый текущий массив информации обработки рабочей программы отличается от эталонного массива из-за асинхронного обслуживания процедур прерывания.

Технической задачей изобретения является расширение функциональных возможностей устройства за счет возможности контроля микропроцессорных систем с обслуживанием процедур прерывания при поиске перемежающихся отказов в микропроцессорных системах.

Технический результат достигается тем, что в устройстве для поиска перемежающихся отказов в микропроцессорных системах, содержащем дешифратор, мультиплексор магистралей, двоичный счетчик, блок буферной памяти эталона, мультиплексор адреса, регистр запуска, мультиплексор данных, шесть триггеров, формирователь короткого импульса, селектор, регистр управления, две схемы сравнения, вычитающий счетчик импульсов, два формирователя сигнала чтения, два формирователя сигнала записи, блок буферной памяти текущего цикла, регистр адреса, семь элементов И, три элемента ИЛИ, причем адресный вход устройства для подключения к шине адреса отлаживающей ЭВМ соединен с первым информационным входом дешифратора, второй информационный вход которого соединен с входом управления устройства для подключения к шине управления отлаживающей ЭВМ, информационный вход-выход устройства для подключения к шине данных отлаживающей ЭВМ соединен с информационным выходом мультиплексора магистралей, с информационными входами регистра управления, регистра запуска, регистра адреса и вычитающего счетчика импульсов, первый выход дешифратора соединен с первым управляющим входом мультиплексора магистралей и с входом первого формирователя сигнала чтения, второй выход дешифратора соединен со вторым управляющим входом мультиплексора магистралей, третий выход дешифратора соединен через формирователь короткого импульса с единичным входом первого триггера, вход начальной установки устройства соединен с нулевыми входами первого, третьего, пятого и шестого триггеров, с обнуляющим входом двоичного счетчика и со вторым входом второго элемента ИЛИ, выход которого соединено нулевыми входами второго и четвертого триггеров, информационный вход первого триггера соединен с шиной нулевого потенциала устройства, выход первого триггера является первым выходом синхронизации устройства для подключения к входу ожидания отлаживаемой микропроцессорной системы, четвертый, пятый, шестой и седьмой выходы дешифратора соединены, соответственно, с входами разрешения регистра управления, регистра запуска, вычитающего счетчика импульсов и регистра адреса, первый информационный выход мультиплексора данных соединен с информационным входом блока буферной памяти эталона, информационный выход блока буферной памяти эталона соединен с первым информационным входом мультиплексора магистралей, выход регистра управления соединен с входом управления селектора, выход регистра запуска соединен с первым входом первой схемы сравнения, выход первого формирователя сигнала записи соединен с входом записи блока буферной памяти эталона, информационный выход мультиплексора адреса соединен с адресным входом блока буферной памяти эталона, первый информационный вход устройства для подключения к контрольным точкам отлаживаемой микропроцессорной системы соединен с информационным входом мультиплексора данных, второй информационный вход устройства для подключения к тактирующим сигналам отлаживаемой микропроцессорной системы соединен с информационным входом селектора, третий информационный вход устройства для подключения к сигналам запуска отлаживаемой микропроцессорной системы соединен со вторым входом первой схемы сравнения, информационный выход блока буферной памяти эталона соединен с первым входом второй схемы сравнения, второй информационный выход мультиплексора данных соединен с информационным входом блока буферной памяти текущего цикла и со вторым входом втором схемы сравнения, инверсный выход которой соединен с первым входом первого элемента И, информационный выход мультиплексора адреса соединен с адресным входом блока буферной памяти текущего цикла, информационный выход которого соединен с вторым информационным входом мультиплексора магистралей, информационный выход двоичного счетчика соединен с первым информационным входом мультиплексора адреса, второй информационный вход которого соединен с выходом регистра адреса, выход первой схемы сравнения соединен с первыми входами второго и третьего элементов И, выход второго элемента И соединен со счетным входом вычитающего счетчика импульсов, выход обнуления которого соединен с единичным входом второго триггера, выход второго триггера соединен с первым управляющим входом мультиплексора данных, с первым входом четвертого элемента И, с первым входом первого элемента ИЛИ и с тактовым входом третьего триггера, информационный вход которого соединен с шиной единичного потенциала устройства, прямой выход третьего триггера соединен со вторым входом третьего элемента И, выход которого соединен с единичным входом четвертого триггера, инверсный выход третьего триггера соединен со вторым входом второго элемента И, выход селектора соединен с первым входом пятого элемента И, выход четвертого триггера соединен со вторым управляющим входом мультиплексора данных, вторым входом первого элемента И, с первым входом шестого элемента И и со вторым входом первого элемента ИЛИ, выход которого соединен со вторым входом пятого элемента И, выход пятого элемента И соединен со счетным входом двоичного счетчика, с третьим входом первого элемента И, со вторым входом четвертого элемента И и со вторым входом шестого элемента И, выход первого элемента И соединен с единичным входом пятого триггера, выход которого соединен с первым входом седьмого элемента И, выход переполнения двоичного счетчика соединен с первым входом второго элемента ИЛИ и со вторым входом седьмого элемента И, выход которого соединен с единичным входом шестого триггера, прямой выход шестого триггера со единен с первым управляющим входом мультиплексора адреса, с тактовым входом первого триггера и со вторым выходом синхронизации устройства для подключения к входу маскируемого прерывания отлаживающей ЭВМ, инверсный выход шестого триггера соединен со вторым управляющим входом мультиплексора адреса, выход шестого элемента И соединен с входом второго формирователя сигнала записи, выход которого соединен с первым входом третьего элемента ИЛИ и с входом записи блока буферной памяти текущего цикла, второй выход дешифратора соединен с входом второго формирователя сигнала чтения, выход которого соединен с входом чтения блока буферной памяти текущего цикла, выход первого формирователя сигнала чтения соединен со вторым входом третьего элемента ИЛИ, выход которого соединен с входом чтения блока буферной памяти эталона, выход четвертого элемента И соединен с входом первого формирователя сигнала записи, введены регистр возврата, третья схема сравнения, седьмой триггер, восьмой элемент И, четвертый элемент ИЛИ, причем восьмой выход дешифратора соединен с входом разрешения регистра возврата, информационный вход которого соединен с информационным входом выходом устройства для подключения к шине данных отлаживающей ЭВМ, выход регистра возврата соединен с первым входом третьей схемы сравнения, второй вход которой соединен с четвертым информационным входом устройства для подключения к шине данных отлаживаемой микропроцессорной системы, первый вход восьмого элемента И является первым входом синхронизации устройства для подключения к выходу выборки кода команды отлаживаемой микропроцессорной системы, прямой выход третьей схемы сравнения соединен со вторым входом восьмого элемента И, прямой выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с входом начальной установки устройства, выход четвертого элемента ИЛИ соединен с единичным входом седьмого триггера, нулевой вход седьмого триггера является вторым входом синхронизации для подключения к выходу подтверждения прерывания отлаживаемой микропроцессорной системы, прямой выход седьмого триггера соединен с третьим входом пятого элемента И.

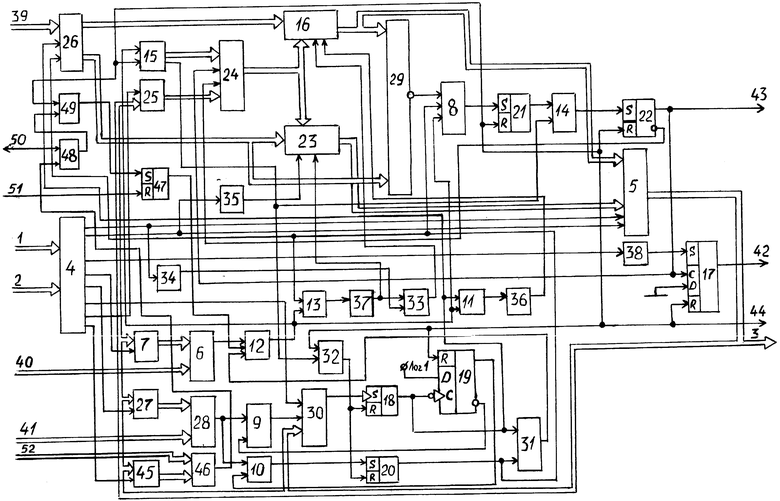

На чертеже представлена структурная схема устройства для поиска перемежающихся неисправностей в микропроцессорных системах.

Устройство содержит адресный вход 1, вход управления 2, информационный вход выход 3, дешифратор 4, мультиплексор магистралей 5, селектор 6, регистр управления 7, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И 8-14 соответственно, двоичный счетчик 15, блок буферной памяти эталона 16, первый, второй, третий, четвертый, пятый и шестой триггеры 17-22 соответственно, блок буферной памяти текущего цикла 23, мультиплексор адреса 24, регистр адреса 25, мультиплексор данных 26, регистр запуска 27, первая 28 и вторая 29 схемы сравнения, вычитающий счетчик импульсов 30, первый, второй и третий элементы ИЛИ 31-33 соответственно, первый 34 и второй 35 формирователи сигнала чтения, первый 36 и второй 37 формирователи сигнала записи, формирователь короткого импульса 38, первый, второй и третий информационные входы 39-41 соответственно, первый 42 и второй 43 выходы синхронизации устройства, вход начальной установки 44 устройства, регистр возврата 45, третью схему сравнения 46, седьмой триггер 47, восьмой элемент И 48, четвертый элемент ИЛИ 49, первый 50 и второй 51 входы синхронизации устройства, четвертый информационный вход 52 устройства.

При включении питания (или при аппаратном сбросе) одиночный импульс с входа 44 начальной установки поступает на обнуляющий вход двоичного счетчика 15, на нулевые входы (R-входы) триггеров 17, 19, 21, 22, через один из входов элемента ИЛИ 32 на нулевые входы триггеров 18,20, устанавливая их в нулевое состояние, через один из входов элемента ИЛИ 49 на единичный вход триггера 47, устанавливая его в единичное состояние, триггер 17 формирует нулевой сигнал, поступающий через первый выход 42 синхронизации устройства в отлаживаемую микропроцессорную систему в виде сигнала "WAIT" (ожидать).

На первый информационный вход дешифратора 4 через адресный вход 1 устройства поступают разряды адресной шины отлаживающей ЭВМ. Через вход управления 2 устройства на второй вход дешифратора 4 поступают сигналы шины управления отлаживающей ЭВМ. При поступлении на дешифратор 4 совокупности сигналов разрядов адреса, сигналов управления "Запись" и "Чтение" в зависимости от кода, поступившего на вход дешифратора 4, возбуждается один из выходов дешифратора 4.

Поступающий код на входе дешифратора 4 может быть восьми типов в соответствии с работой устройства для поиска перемежающихся неисправностей в микропроцессорных системах. Обозначим каждый из кодов символами: a, b, c, d, e, f, g, h. При поступлении на входы дешифратора 4 кодов a и b возбуждаются, соответственно, первый и второй выходы дешифратора 4, причем первый выход дешифратора 4 соединен с первым управляющим входом мультиплексора магистралей 5 и с входом первого формирователя сигнала чтения 34, а второй выход дешифратора 4 соединен со вторым управляющим входом мультиплексора магистралей 5 и с входом второго формирователя сигнала чтения 35. При наличии кодов a и b на входах дешифратора 4 мультиплексор магистралей 5 обеспечивает коммутацию информации соответственно с информационных выходов блока буферной памяти эталона 16 и блока буферной памяти текущего цикла 23 на информационный вход

выход 3 устройства. Код с возбуждает третий выход дешифратора 4, который соединен с входом формирователя 38 короткого импульса. Код c, запуская формирователь 38 короткого импульса, переводит триггер 17 по установочному (единичному) входу (S-вход) в единичное состояние, снимая тем самым сигнал "WAIT" с первого выхода 42 синхронизации устройства для отлаживаемой микропроцессорной системы и осуществляя запуск отлаживаемой микропроцессорной системы после останова. Коды d, e, f, g, h возбуждают, соответственно, четвертый, пятый, шестой, седьмой и восьмой выходы дешифратора 4, которые подключены к входам разрешения, соответственно, регистра управления 7, регистра запуска 27, вычитающего счетчика импульсов 30, регистра адреса 25 и регистра возврата 45. При наличии кодов d, e, f, g, h на входах дешифратора 4 последний сигналами на четвертом, пятом, шестом, седьмом и восьмом своих выходах разрешает запись информации с информационного входа выхода 3 устройства соответственно в регистр управления 7, в регистр запуска 27, на установочный вход вычитающего счетчика импульсов 30, в регистр адреса 25 и в регистр возврата 45.

Регистр управления 7 предназначен для задания режима работы селектора 6.

Под воздействием комбинации сигналов, хранящихся в регистре управления 7, селектор 6 пропускает только один определенный тактовый сигнал из M возможных тактовых сигналов отлаживаемой микропроцессорной системы, например "Чтение памяти" или сигнал первого цикла команды, с второго информационного входа 40 устройства через первый вход элемента И 12 на счетный вход двоичного счетчика 15 (при наличии единичного сигнала с выхода элемента ИЛИ 31 на втором входе элемента И 12).

Двоичный счетчик 15 при поступлении на счетный вход тактовых импульсов из отлаживаемой микропроцессорной системы (с выхода элемента И 12) вырабатывает на своем выходе текущий адрес заполняемых ячеек памяти в блоке буферной памяти эталона 16 или в блоке буферной памяти текущего цикла 23 в режиме контроля.

Мультиплексор адреса 24 обеспечивает передачу адресного кода на адресные входы блока буферной памяти эталона 16 и блока буферной памяти текущего цикла 23 или с выхода двоичного счетчика 15 (в режиме контроля), или выхода регистра адреса 25 (в режиме анализа).

Регистр запуска 27 хранит код информации, который поступает на первый вход первой схемы сравнения 23. При поступлении на второй вход первой схемы сравнения 23 с третьего информационного входа 41 устройства из отлаживаемой микропроцессорной системы одновременно совокупности P сигналов запуска, равной коду информации, хранимому в регистре запуска 27, первая схема сравнения 28, выработает единичный сигнал, который поступает на один из входов элемента И 9, при наличии единичного сигнала на другом входе элемента И 9, поступающего с инверсного выхода триггера 19, пройдет на счетный вход вычитающего счетчика импульсов 30. Кодом информации с информационного входа выхода 3 устройства по установочному входу вычитающий счетчик 30 импульсов настраивается на подсчет определенного числа импульсов при поступлении сигнала с шестого выхода дешифратора 4 на вход разрешения вычитающего счетчика импульсов 30, задавая тем самым количество появлений совокупности P сигналов запуска из отлаживаемой микропроцессорной системы на третьем информационном входе 41 устройства, прежде чем начнется формирование массива эталонной информации, поступающей через мультиплексор данных 26 с первого информационного входа 39 устройства из N контрольных точек отлаживаемой микропроцессорной системы, в блоке буферной памяти эталона 16, поскольку сигнал с выхода обнуления вычитающего счетчика 30 импульсов, поступая на единичный вход триггера 18, перебрасывает триггер 18 в единичное состояние, сигнал с выхода которого, поступая на первый управляющий вход мультиплексора данных 26, разрешает прохождение информации из М контрольных точек отлаживаемой микропроцессорной системы с первого информационного входа 39 устройства через мультиплексор данных 26 на информационный вход блока буферной памяти 16 эталона.

На информационный вход (D-вход) триггера 19 подается логическая единица. При поступлении единичного сигнала с выхода триггера 18 на синхронизирующий вход (C-вход) триггера 19 последний устанавливается в нулевое состояние на инверсном выходе и в единичное состояние на прямом выходе. Нулевой сигнал с инверсного выхода триггера 19 блокирует прохождение сигналов через элемент И 9 с выхода первой схемы сравнения 28 на счетный вход вычитающего счетчика импульсов 30. Одновременно единичный сигнал с прямого выхода триггера 19 разрешает прохождение сигналов через элемент И 10 с выхода первой схемы сравнения 28 на единичный вход триггера 20.

Триггер 18 фактически разрешает занесение информации с первого информационного входа 39 устройства через мультиплексор данных 26 в блок буферной памяти 16 при эталонном проходе циклической программы в отлаживаемой микропроцессорной системе.

Единичный сигнал с выхода элемента И 10 (при наличии на его входах единичного сигнала с выхода первой схемы сравнения 28 и единичного сигнала с прямого выхода триггера 19) перебрасывает триггер 20 по его единичному входу в единичное состояние.

Единичный сигнал с выхода триггера 20 разрешает прохождение информации с первого информационного входа 39 устройства через мультиплексор данных 39 в блок буферной памяти 23 текущего цикла. Кроме того, единичные сигналы с выходов триггеров 18 и 20, поступая на входы элемента ИЛИ 31, возбуждают на выходе элемента ИЛИ 31 единичный сигнал, поступающий на второй вход элемента И 12, разрешая тем самым прохождение тактовых сигналов с выхода селектора 6 через первый вход элемента И 12 на его выход. Прохождение тактовых сигналов с выхода селектора 6 через первый вход элемента И 12 на его выход блокируется также нулевым сигналом с прямого выхода триггера 47, поступающим на третий вход элемента И 12.

Триггер 47 по своему нулевому входу (R-входу) устанавливается в нулевое состояние единичным сигналом подтверждения прерывания "INTA", поступающим с второго входа синхронизации 51 устройства из отлаживаемой микропроцессорной системы.

Каждая подпрограмма обработки прерывания завершается специальной командой "RET", код ее заносится в регистр возврата 45. Код информации из регистра возврата 45 поступает на первый вход третьей схемы сравнения 46. При поступлении на второй вход третьей схемы сравнения 46 с четвертого информационного входа 52 устройства с шины данных отлаживаемой микропроцессорной системы кода информации, равному коду команды "RET", третья схема сравнения 46 выработает единичный сигнал, который поступает на один из входов элемента И 48. При наличии одновременно на другом входе элемента И 48 единичного сигнала выборки кода команды "M1" с первого входа синхронизации 50 устройства с выхода выборки кода команды отлаживаемой микропроцессорной системы элемент И 48 возбудит на своем выходе единичный сигнал, который через один из входов элемента ИЛИ 49 поступает на единичный вход (S-вход) триггера 47 и перебрасывает последний в единичное состояние. Триггер 47 исключает влияние обслуживания асинхронных процедур прерывания на формирование эталонного и каждого последующего текущего массивов информации обработки контролируемого циклического тела рабочей программы.

Блоки буферной памяти 16 эталона, буферной памяти 23 текущего цикла обеспечивают сохранение массивов информации о состоянии контрольных точек отлаживаемой микропроцессорной системы при эталонном проходе фрагмента циклической программы и текущего прохода того же фрагмента циклической программы и выдачу этих массивов информации после фиксации сбоя в текущем цикле.

Триггеры 18 и 20 по их нулевым входам (R-входам) перебрасываются в нулевое состояние единичным сигналом с выхода элемента ИЛИ 32, единичные сигналы на вход которого поступают с входа начальной установки 44 устройства или с выхода переполнения двоичного счетчика 15.

Вторая схема сравнения 29 сравнивает коды информации, поступающие с информационного выхода блока буферной памяти эталона 16 и на информационный вход блока буферной памяти 23. При несовпадении кодов на входах второй схемы сравнения 29 последняя возбуждает на своем инверсном выходе единичный сигнал, который поступает на первый вход элемента И 8, на второй вход которого поступает единичный сигнал с выхода триггера 20 при контроле текущего цикла и на третий вход элемента И 8 поступают тактовые сигналы с выхода элемента И 12. При наличии одновременно на выходе элемента И 8 единичного сигнала несовпадения с выхода второй схемы сравнения 29, единичного сигнала с выхода триггера 20 о контроле текущего цикла и единичного тактового сигнала с выхода элемента И 12 на выходе элемента И 8 возбуждается единичный сигнал, который перебрасывает триггер 21 в единичное состояние.

Единичный сигнал с выхода триггера 21 поступает на один из входов элемента И14, другой вход которого соединен с выходом переполнения двоичного счетчика 15. Единичный сигнал с выхода триггера 21, указывающий на возникновение сбоя, пройдет через элемент И14 на единичный вход триггера 22 только при поступлении на вход элемента И14 единичного сигнала с выхода переполнения двоичного счетчика 15, то есть в конце текущего цикла контроля.

Единичный сигнал с выхода элемента И14 перебрасывает триггер 22 в единичное состояние на его прямом выходе и в нулевое состояние на его инверсном выходе. Единичный сигнал с прямого выхода триггера 22 поступает на синхронизирующий (тактовый) вход триггера 17 и на первый управляющий вход мультиплексора адреса 24, подается в виде маскируемого сигнала прерывания "INT" для отлаживающей ЭВМ через второй выход 43 синхронизации устройства.

При поступлении единичного сигнала на синхронизирующий вход (C-вход) триггера 17 последний устанавливается в нулевое состояние и вырабатывает сигнал "WAIT" (ожидать) для отлаживаемой микропроцессорной системы на первом выходе 42 синхронизации устройства.

Формирователь сигнала чтения 34 вырабатывает импульс заданной формы и длительности, поступающий через элемент ИЛИ 33 на вход записи блока буферной памяти эталона 16 и необходимый для чтения информации из последнего.

Формирователь сигнала чтения 35 вырабатывает импульс заданной формы и длительности, необходимый для чтения информации из блока буферной памяти текущего цикла 23.

Формирователь сигнала записи 36 вырабатывает импульс заданной формы и длительности, необходимый для записи информации в блок буферной памяти эталона 16.

Формирователь сигнала записи 37 вырабатывает импульс заданной формы и длительности, необходимый для записи информации в блок буферной памяти текущего цикла 23 и, поступая через элемент ИЛИ 33, необходимый для чтения информации из блока буферной памяти эталона 16.

Регистр адреса 25 служит для хранения адреса выбираемых ячеек блоков буферной памяти эталона 16 и блока буферной памяти текущего цикла 23 в режиме анализа.

Элемент И13 пропускает на свой выход тактовые импульсы с выхода элемента И12, поступающие на один из входов элемента И13, только при наличии единичного сигнала с выхода триггера 20 на другом входе элемента И13. Поскольку выход элемента И13 соединен с входом второго формирователя сигнала записи 37, второй формирователь сигнала записи 37 формирует сигналы записи для блока буферной памяти текущего цикла 23 только на период текущего цикла контроля отлаживаемой микропроцессорной системы.

Триггер 19 в единичном состоянии запоминает тот факт, что формирование эталонного массива информации в блоке буферной памяти 16 произошло, то есть единичное состояние триггера 19 сохраняется и после эталонного прохода цикловой программы, в отличие от состояния триггера 18, единичное состояние которого сохраняется только на период эталонного прохода, поскольку триггер 18 перебрасывается в исходное нулевое состояние по R-входу сигналом переполнения с двоичного счетчика 15.

Нулевой сигнал с инверсного выхода триггера 19 блокирует прохождение сигналов с выхода первой схемы сравнения 28 через элемент И9 на счетный вход вычитающего счетчика импульсов 30, единичный сигнал с прямого выхода триггера 19 разрешает прохождение импульсов с выхода схемы сравнения 28 через элемент И10 на единичный вход триггера 20, единичное состояние которого сохраняется на весь период текущего цикла контроля.

При наличии единичного сигнала с выхода триггера 18 (во время эталонного прохода) на одном из входов элемента И11 последний пропускает через свой другой вход тактовые импульсы с выхода элемента И12 на вход первого формирователя сигнала записи 36.

Для поиска перемежающихся неисправностей в микропроцессорных системах к устройству подсоединяются отлаживающая ЭВМ и отлаживаемая микропроцессорная система следующим образом.

Адресная шина отлаживающей ЭВМ подсоединяется к адресному входу 1 устройства, шина управления к входу управления 2 устройства, шина данных к информационному входу выходу 3 устройства, линия сигнала на маскируемый запрос прерывания "INT" к выходу 43 синхронизации устройства.

N контрольных точек отлаживаемой микропроцессорной системы подсоединяются к первому информационному входу 39 устройства, M линий возможных тактирующих сигналов отлаживаемой микропроцессорной системы к второму информационному входу 40 устройства, P линии сигналов запуска из отлаживаемой микропроцессорной системы к третьему информационному входу 41 устройства, линия сигнала ожидания "WAIT" к первому выходу 42 синхронизации устройства, линия сигнала выборки кода команды "M1" к первому входу синхронизации 50 устройства, линия сигнала подтверждения прерывания "INTA" к второму входу синхронизации 51 устройства, шина данных отлаживаемой микропроцессорной системы к четвертому информационному входу 52 устройства.

Принцип работы устройства заключается в следующем.

Эксплуатация микропроцессорных систем управления промышленного назначения характеризуется тяжелыми условиями (высокая влажность, вибрация, наличие агрессивных веществ в воздушной среде, высокая температура). Указанные факторы ведут к случайному нарушению контактных паяных соединений, металлизации переходных отверстий, периодическому случайному нарушению паяных соединении установочных элементов на печатных проводниках, случайным микроскопическим замыканиям соседних печатных проводников и т.д.

Внешне такие нарушения ведут к случайным перемежающимся отказам всей микропроцессорной системы управления, в том числе к "зависаниям" и перезапускам без выхода на рабочую программу.

Возникает задача "отловить" момент и место сбоя в отлаживаемой (контролируемой) микропроцессорной системе. Задача облегчается тем, что всякая микропроцессорная система, отработав программу инициализации и тестовых проверок неотъемлемого оборудования, выходит на циклическую обработку рабочей программы. Причем при постоянной совокупности внешних обрабатываемых сигналов, что достигается на стенде, микропроцессорная система "крутит" фактически один и тот же цикл обработки, отвлекаясь только на обработку возникающих асинхронных процедур прерывания. Поскольку процедуры прерывания возникают произвольно по времени в цикле обработки рабочей программы, то необходимо устранить их влияние на формирование текущего массива информации обработки этого цикла.

Местом привязки в этом цикле обработки служит совокупность P сигналов запуска, поступающих из отлаживаемой микропроцессорной системы и определяемых предварительно из анализа рабочей программы. Причем чтобы пропустить обработку программы инициализации и тестовых проверок, при которых возможно появление определенного числа раз совокупности P сигналов запуска, устройство настраивается на пропуск заданного числа раз совокупности P сигналов запуска в отлаживаемой микропроцессорной системе, прежде чем устройство начнет формирование эталонного массива информации в блоке буферной памяти эталона 16, причем информация поступает параллельно из M контрольных точек отлаживаемой микропроцессорной системы и записывается соответственно тактовым импульсам, пропускаемым селектором 6 с одной из M возможных линий тактовых сигналов в отлаживаемой микропроцессорной системе, в зависимости от глубины и точности контроля, например тактовые сигналы обращения к памяти или начала каждого машинного цикла, или выборки команды, или каждого машинного такта и т.д.

Сформированный таким образом массив эталонной информации сравнивается потактно с массивом информации, поступающим на первый информационный вход 39 устройства после каждого последующего появления совокупности P сигналов запуска, причем одновременно формируется массив текущего цикла контроля в блоке буферной памяти 23 текущего цикла.

Объем массива информации в блоках буферной памяти эталона 16 и блока буферной памяти текущего цикла 23 задается разрядностью информационного выхода двоичного счетчика 15, то есть адресный вход блоков буферной памяти эталона 16 и блока буферной памяти текущего цикла 23 должен иметь разрядность не меньшую, чем разрядность информационного выхода двоичного счетчика 15.

При отсутствии сбоя в текущем цикле контроля устройство ожидает каждого последующего появления совокупности P сигналов запуска из отлаживаемой микропроцессорной системы для формирования каждого последующего текущего массива информации в блоке буферной памяти 23 текущего цикла.

При появлении сбоя в текущем цикле контроля устанавливается в единичное состояние триггер 21, однако формирование массива информации текущего цикла в блоке буферной памяти 23 текущего цикла продолжается вплоть до переполнения двоичного счетчика 15. Это позволяет проследить развитие аварийной ситуации в других контрольных точках с момента появления сбоя. И только при наличии единичных сигналов с выхода триггера 21 и выхода переполнения двоичного счетчика 15 на входах элемента И 14 возбуждается единичный сигнал на S-единичном входе триггера 22, перебрасывая последний в единичное состояние на своем прямом выходе и в нулевое состояние на своем инверсном выходе. Единичный сигнал с прямого выхода триггера 22 перебросит по тактирующему входу триггера 17 последний в нулевое состояние и поступит на второй управляющий вход мультиплексора адреса 24, переключая его на передачу информации с регистра адреса 25 на адресные входы блоков буферной памяти эталона 16 и буферной памяти текущего цикла 23 и подготавливая тем самым устройство к режиму анализа. Нулевой сигнал с выхода триггера 17 поступает через первый выход синхронизации 42 устройства на линию сигнала "WAIT" отлаживаемой микропроцессорной системы и останавливает последнюю. Единичный сигнал с прямого выхода триггера 22 поступает также через второй выход синхронизации 43 устройства на линию сигнала маскируемого прерывания "INT" и в отлаживающую ЭВМ (персональный компьютер) для инициирования программы обработки режима анализа устройства.

Устройство работает следующим образом.

Отлаживающая ЭВМ в соответствии с организацией своего интерфейса подсоединяется адресной шиной к адресному входу 1 устройства, шиной управления к входу управления 2 устройства, шиной данных к информационному входу - выходу 3 устройства, линией сигнала маскируемого прерывания "INT" к второму выходу 43 синхронизации устройства.

Отлаживаемая микропроцессорная система подсоединяется своими N контрольными точками к первому информационному входу 39 устройства, N линиями своих тактирующих сигналов к второму информационному 40 входу устройства, P линиями сигналов запуска к третьему информационному 41 входу устройства. Первый выход 42 синхронизации устройства является линией сигнала ожидания "WAIT" для отлаживаемой микропроцессорной системы, линия сигнала выборки кода команды "M1" подсоединяется к первому входу синхронизации 50 устройства, линия сигнала подтверждения прерывания "INTA" к второму входу синхронизации 51 устройства, шина данных отлаживаемой микропроцессорной системы к четвертому информационному входу 52 устройства.

Работа устройства для поиска перемежающихся неисправностей в микропроцессорных системах начинается с того, что при включении питания или при аппаратном сбросе с входа начальной установки 44 устройства поступает единичный импульс на нулевой вход (R-вход) триггера 17, на нулевой вход триггера 22, на нулевой вход триггера 19, на нулевой вход триггера 21, через элемент ИЛИ 32 на нулевые входы триггеров 18 и 20, на обнуляющий вход двоичного счетчика 15, устанавливая их в нулевое состояние, и через элемент ИЛИ 49 на единичный вход триггера 47, устанавливая его в единичное состояние.

С выхода триггера 17 нулевой сигнал поступает через первый 42 выход синхронизации устройства на линию сигнала "WAIT" отлаживаемой микропроцессорной системы.

При последующем включении питания в отлаживаемой микропроцессорной системе последняя остановится в начале первого машинного цикла обработки нулевой ячейки отлаживаемой программы, так как на первом выходе 42 синхронизации устройства присутствует сигнал "WAIT" к моменту начальной установки.

Отлаживающая ЭВМ в начале своей программы подготавливает устройство для поиска перемежающихся отказов в микропроцессорных системах к прогону контролируемой программы отлаживаемой микропроцессорной системы. Для этого отлаживающая ЭВМ выставляет по адресному входу 1 устройства и входу управления 2 устройства на вход дешифратора 4 код e, который возбуждает сигнал на пятом выходе дешифратора 4, разрешая занести с информационного выхода 3 устройства в регистр запуска 27 код информации, определяющий необходимую совокупность P сигналов запуска.

Затем отлаживающая ЭВМ выставляет по адресному входу 1 устройства и входу управления 2 устройства на вход дешифратора 4 код f, который возбуждает шестой выход дешифратора 4, сигнал с выхода которого, воздействуя на вход разрешения вычитающего счетчика 30 импульсов, разрешает запись двоичного кода на установочный вход вычитающего счетчика 30 импульсов с информационного входа выхода 3 устройства. Двоичный код равен ожидаемому количеству появлений заданной регистром запуска 27 совокупности P сигналов запуска на третьем информационном входе 41 устройства, прежде чем начнется формирование эталонного массива информации в блоке буферной памяти эталона 16.

Затем отлаживающая ЭВМ выставляет по адресному входу 1 устройства и входу управления 2 устройства на входы дешифратора 4 код d, который возбуждает на четвертом выходе дешифратора 4 сигнал, разрешающий занести с информационного входа выхода 3 устройства в регистр управления 7 код информации, определяющий режим работы селектора 6 и, соответственно, выбор сигнальной линии из M линии тактовых сигналов отлаживаемой микропроцессорной системы с второго информационного 40 входа устройства, задающий тем самым глубину достоверного контроля функционирования аппаратно-программных средств отлаживаемой микропроцессорной системы при прогоне рабочей программы (например за счет формирования ячеек массивов эталонного прохода и текущего цикла контроля при каждом обращении к памяти, или на каждом машинном цикле, или в каждом машинном такте).

Затем отлаживающая ЭВМ выставляет по адресному входу 1 устройства и входу управления 2 устройства на входы дешифратора 4 код h, который возбуждает на восьмом выходе дешифратора 4 сигнал, разрешающий занести с информационного входа выхода 3 устройства в регистр возврата 45 код специальной команды возврата "RET", которой завершается каждая подпрограмма обслуживания процедуры прерывания.

Завершая подготовку к прогону рабочей программы, отлаживающая ЭВМ выставляет по адресному входу 1 устройства и входу управления 2 устройства на входе дешифратора 4 код с, который возбуждает третий выход дешифратора 4, воздействующий на формирователь короткого импульса 38, последний вырабатывает импульс, перебрасывающий триггер 17 по единичному входу (S-входу) в единичное состояние, снимая тем самым сигнал "WAIT" с первого выхода синхронизации 42 устройства. Кроме того, отлаживающая ЭВМ снимает маску с маскируемого запроса на прерывание "INT".

Отлаживаемая микропроцессорная система приступает к прогону контролируемой рабочей программы на рабочей скорости.

Тактовые импульсы с выбранной селектором 6 сигнальной линии из тактовых линии отлаживаемой микропроцессорной системы (второй информационный вход 40 устройства) поступают на первый вход элемента И 12, но не проходят на его выход, так как на втором входе элемента И 12 присутствует нулевой сигнал с выхода элемента ИЛИ 31, поскольку в свою очередь на входы элемента ИЛИ 31 поступают нулевые сигналы соответственно с выходов триггеров 18 и 20.

На третий информационный вход 41 устройства поступают сигналы запуска из P сигнальных линий запуска отлаживаемой микропроцессорной системы. При равенстве поступившей совокупности P сигналов запуска с третьего информационного входа 41 устройства коду информации, хранящемуся в регистре запуска 27, первая схема сравнения 28 на своем выходе выбрасывает единичный сигнал, который поступает на первый вход элемента И 9. Поскольку на втором входе элемента И 9 присутствует единичный сигнал с инверсного выхода триггера 19, данный единичный и каждый последующий сигнал с выхода первой схемы сравнения 28 проходит на выход элемента И 9 и поступает на счетный вход вычитающего счетчика импульсов 30. Одновременно единичные сигналы с выхода первой схемы сравнения 28 поступают на первый вход элемента И 10, на второй вход которого поступает нулевой сигнал с прямого выхода триггера 19. Поэтому единичные сигналы с выхода первой схемы сравнения 28 не проходят на выход элемента И 10.

При достижении на счетном входе вычитающего счетчика импульсов 30 определенного количества импульсов (появления совокупности P сигналов на третьем информационном входе 41 устройства), заданного кодом, занесенным на установочный вход вычитающего счетчика 30 импульсов, последний вырабатывает единичный сигнал, который поступает на единичный прямой динамический вход (S-вход) триггера 18 и перебрасывает последний в единичное состояние.

Единичный сигнал с выхода триггера 18 поступает на первый управляющий вход мультиплексора данных 26, обеспечивая передачу информации из N контрольных точек отлаживаемой микропроцессорной системы через первый информационный вход 39 устройства на информационный вход блока буферной памяти 16 эталона, поступает через первый вход элемента ИЛИ 31 на второй вход элемента И 12, обеспечивая прохождение тактовых импульсов с выхода селектора 6 на выход элемента И 12, поступает на второй вход элемента И 11, обеспечивая прохождение тактовых импульсов с выхода элемента И 12 через первый вход элемента И 11 на вход первого формирователя 36 сигнала записи, и поступает на динамический инверсный синхронизирующий вход (C-вход) триггера 19.

Тактовые сигналы с выхода элемента И 12 поступают на счетный вход двоичного счетчика 15 и через второй вход элемента И 11 (на первом входе элемента И 11 присутствует единичный сигнал с выхода триггера 18) поступают на вход первого формирователя сигнала 36 записи. При этом двоичный счетчик 15 с поступлением первого и каждого последующего тактовых импульсов на свой счетный вход формирует на выходе нарастающий двоичный код, который воздействует одновременно через мультиплексор адреса 24 на адресные входы блоков буферной памяти 16 эталона и буферной памяти 23 текущего цикла.

Мультиплексор адреса 24 по своему первому управляющему входу единичным сигналом с инверсного выхода триггера 22 настраивается на передачу информации с выхода двоичного счетчика 15 на адресные входы блоков буферной памяти эталона 16 и буферной памяти 23 текущего цикла.

Сигналы с выхода первого формирователя 36 сигнала записи воздействуют на вход записи блока буферной памяти 16 эталона, обеспечивая потактно занесение информации из N контрольных точек отлаживаемой микропроцессорной системы с первого информационного входа 39 устройства в последовательные ячейки блока буферной памяти 16 эталона.

При появлении единичного сигнала на выходе переполнения двоичного счетчика 15 (при заполнении всего заданного разрядностью двоичного счетчика 15 массива ячеек блока буферной памяти эталона 16 информацией о состоянии N контрольных точек отлаживаемой микропроцессорной системы), поступающего через первый вход элемента ИЛИ 32 на нулевой вход триггера 18, триггер 18 перебрасывается в нулевое состояние, задним фронтом сигнала с выхода триггера 18 триггер 19 по своему инверсному динамическому тактовому входу (C-входу) устанавливается в единичное состояние, поскольку информационный вход (D-вход) триггера 19 соединен с шиной единичного потенциала устройства. Нулевой сигнал с инверсного выхода триггера 19, поступая на второй вход элемента И 9, блокирует прохождение импульсов с выхода первой схемы сравнения 28 через элемент И 9 на счетный вход вычитающего счетчика импульсов 30, единичный сигнал с прямого выхода триггера 19, поступая на второй вход элемента И 10, разрешая прохождение импульсов с выхода первой схемы сравнения 28 через первый вход элемента И 10 на единичный (установочный) вход (S-вход) триггера 20.

Кроме того, нулевой сигнал с выхода триггера 18 запрещает прохождение по первому управляющему входу мультиплексора данных 26 информации с первого информационного входа 39 устройства через мультиплексор данных 26 на информационный вход блока буферной памяти эталона 16, блокирует прохождение тактовых импульсов с выхода элемента И 12 через элемент И 11 на вход первого формирователя сигнала записи 36. Совокупность нулевых сигналов с выходов триггеров 18 и 20, поступая на входы элемента ИЛИ 31, возбуждает на выходе элемента ИЛИ 31 нулевой сигнал, который, поступая на вход элемента И 12, блокирует прохождение тактовых импульсов с выхода селектора 6 по первому входу элемента И 12 на его выход.

Такая ситуация сохраняется до того момента, пока в процессе обработки цикловой рабочей программы отлаживаемой микропроцессорной системы в последней не появится в очередной раз заданная совокупность P сигналов запуска на третьем информационном входе 41 устройства. Первая схема сравнения 28 возбудит на своем выходе единичный сигнал "Равно", который, пройдя через элемент И 10 на единичный вход триггера 20, перебросит последний в единичное состояние.

Единичный сигнал с выхода триггера 20, поступая на второй управляющий вход мультиплексора данных 26, разрешает прохождение информации с первого информационного входа 39 устройства через мультиплексор данных 26 на информационный вход блока буферной памяти 23 текущего цикла и на второй вход второй схемы сравнения 29. Кроме того, единичный сигнал с выхода триггера 20, поступая на первый вход элемента И 13, разрешает прохождение тактовых импульсов с выхода элемента И 12 через второй вход элемента И 13 на вход второго формирователя сигнала записи 37. Единичный сигнал с выхода триггера 20 поступает также через элемент ИЛИ 31 на второй вход элемента И12, разрешая прохождение тактовых импульсов с выхода селектора 6 по первому входу элемента И 12 на его выход, и поступает на один из входов элемента И8.

Тактовые импульсы с выхода элемента И12 вновь начнут поступать на счетный вход двоичного счетчика 15 с поступлением первого и каждого последующего тактовых импульсов на свой счетный вход формирует на выходе нарастающий двоичный код, который воздействует одновременно через мультиплексор адреса 24 на адресные входы блоков буферной памяти 16 эталона и буферной памяти 23 текущего цикла. Тактовые сигналы о выхода элемента И12 также начнут поступать на один из входов элемента И8 и через второй вход элемента И13 (на первом входе элемента И13 присутствует единичный сигнал с выхода триггера 20) поступают на вход второго формирователя сигнала записи 37.

Сигналы с выхода второго формирователя записи 37 воздействуют на вход записи блока буферной памяти 23 текущего цикла, обеспечивая потактно занесение информации из N контрольных точек отлаживаемой микропроцессорной системы с первого информационного входа 39 устройства в последовательные ячейки блока буферной памяти 23 текущего цикла. Кроме того, сигналы с выхода второго формирователя записи 37, поступая через первый вход элемента ИЛИ 33 на вход чтения блока буферной памяти 16 эталона, обеспечивая на соответствующем такте контроля извлечение эталонного кода информации из блока буферной памяти эталона 16.

Формирование эталонного и каждого последующего текущего массивов информации прекращается на период обработки каждой возникающей процедуры прерывания. Триггер 47 по своему нулевому (R-входу) сигналом подтверждения прерывания "INTA" с второго входа синхронизации 51 устройства из отлаживаемой микропроцессорной системы устанавливается в нулевое состояние и блокирует через элемент И 12 прохождение тактовых импульсов. Каждая подпрограмма обработки процедуры прерывания завершается специальной командой "RET", а код ее заносится в регистр возврата 45. При наличии этого кода "RET" на четвертом информационном входе 52 устройства с шины данных отлаживаемой микропроцессорной системы и сигнала выборки кода команды "M1" на первом входе синхронизации 50 устройства с линии сигнала выборки кода команды отлаживаемой микропроцессорной системы на выходе элемента И 48 появится единичный сигнал, перебрасывающий триггер 47 по единичному входу в единичное состояние. Единичный сигнал с выхода триггера 47 разрешает дальнейшее прохождение через элемент И 12 тактовых импульсов.

Поскольку момент временной "привязки" начала формирования эталонного массива информации в блоке буферной памяти эталона 16 и текущего массива информации в блоке буферной памяти 23 текущего цикла один и тот же появление заданной совокупности P сигналов запуска, то при нормальной работе отлаживаемой микропроцессорной системы код информации, поступающий на вход блока буферной памяти 23 текущего цикла и на второй вход второй схемы сравнения 29, идентичен коду информации, извлекаемому на этом же такте из блока буферной памяти эталона 16 и поступающему на первый вход второй схемы сравнения 29. Поэтому во время действия тактовых импульсов на инверсном выходе второй схемы сравнения 29 при нормальной работе отлаживаемой микропроцессорной системы всегда будет присутствовать нулевой сигнал "Равно".

При заполнении заданного разрядностью информационного выхода двоичного счетчика 15 массива ячеек блока буферной памяти 23 текущего цикла на выходе переполнения двоичного счетчика 15 возбуждается единичный сигнал, который, поступая через элемент ИЛИ 32 на нулевые входы (R-входы) триггеров 18 и 20, подтверждает нулевое состояние триггера 18 и перебрасывает в нулевое состояние триггер 20. Совокупность нулевых сигналов на входах элемента ИЛИ 31 возбуждает на выходе последнего нулевой сигнал, блокирующий прохождение тактовых импульсов через элемент И 12.

Для того чтобы не было искажения массивов информации в блоках буферной памяти эталона 16 и блока буферной памяти 23 текущего за счет наложения последующего цикла контроля на предыдущий, разрядность информационного выхода двоичного счетчика 15 выбирается не большей, чем разрядность адресного входа блоков буферной памяти 16 эталона и блока буферной памяти текущего цикла 23.

При появлении в очередной раз заданной совокупности P сигналов запуска на третьем информационном входе 41 устройства первая схема сравнения 28 возбудит на своем выходе единичный сигнал "Равно", который, пройдя через элемент И 10 на единичный вход триггера 20, перебросит последний в единичное состояние, разрешая очередной цикл контроля, как описано выше.

При нормальной работе отлаживаемой микропроцессорной системы происходит циклическое обновление информации в блоке буферной памяти 23 текущего цикла.

При появлении сбоя в функционировании аппаратно-программных средств отлаживаемой микропроцессорной системы в очередном цикле контроля на каком-либо такте (внутри цикла контроля) вторая схема сравнения 29 на своем инверсном выходе возбудит единичный сигнал "Не равно", который поступит на первый вход элемента И 8, на втором и третьем входах которого присутствуют соответственно единичный сигнал с выхода триггера 20 и тактовый единичный сигнал с выхода элемента И 12. При наличии вышеуказанных единичных сигналов на входах элемента И 8 последний возбудит на своем выходе единичный сигнал, который, поступая на единичный вход (S-вход) триггера 21, перебросит последний в единичное состояние. Единичный сигнал с выхода триггера 21 поступает на первый вход элемента И 14. Занесение информации в блок буферной памяти 23 текущего цикла продолжается, протоколируя процесс развития аварийной ситуации, отображаемого потактным состоянием N контрольных точек отлаживаемой микропроцессорной системы в текущем цикле контроля.

По завершении текущего цикла контроля на выходе переполнения двоичного счетчика 15 появится единичный сигнал, который поступит на второй вход элемента И 14. На выходе элемента И 14 возбудится единичный сигнал, который, поступая на единичный вход триггера 22, перебросит последний в единичное состояние. Единичный сигнал с прямого выхода триггера 22 поступает на второй выход синхронизации 43 устройства на линию запроса маскируемого прерывания "INT" в отлаживающую ЭВМ и поступает на синхронизирующий вход триггера 17, перебрасывает последний в нулевое состояние (поскольку информационный вход триггера 17 подключен к шине нулевого потенциала устройства). На первом выходе синхронизации 42 устройства появляется нулевой сигнал "WAIT", останавливающий работу отлаживаемой микропроцессорной системы. Кроме того, единичный сигнал с прямого выхода триггера 22 поступает на первый управляющий вход мультиплексора адреса 24, разрешая прохождение информации с выхода регистра адреса 25 через мультиплексор адреса 24 на адресные входы блоков буферной памяти 16 эталона и буферной памяти 23 текущего цикла.

Выполняя программу обработки прерывания "RET", отлаживающая ЭВМ выставляет вначале по адресному входу 1 устройства и входу управления 2 устройства на входах дешифратора 4 код g, который возбуждает сигнал на седьмом выходе дешифратора 4, разрешая запись двоичного кода, соответствующего адресу первой ячейки в блоках буферной памяти 16 эталона и буферной памяти 23 текущего цикла, в регистр адреса 25 с информационного входа выхода 3 устройства. Затем отлаживающая ЭВМ выставляет по адресному входу 1 устройства и входу управления 2 устройства на первый и второй входы дешифратора 4 код g, возбуждающий на первом выходе дешифратора 4 единичный сигнал, который поступает на первый управляющий вход мультиплексора магистралей 5 и на вход первого формирователя сигнала чтения 34. Первый формирователь сигнала чтения 34 вырабатывает сигнал, воздействующий на вход чтения блока буферной памяти 16 эталона. Мультиплексор магистралей 5 единичным сигналом на своем первом управляющем входе настраивается на коммутацию информации с информационного выхода блока буферной памяти 16 эталона на информационный вход выход 3 устройства. Содержимое первой ячейки блока буферной памяти 16 эталона поступает по информационному входу выходу 3 устройства в отлаживающую ЭВМ для запоминания и последующего анализа. Затем отлаживающая ЭВМ выставляет по адресному входу 1 устройства и входу управления 2 устройства на первый и второй входы дешифратора 4 код b, возбуждающий на втором выходе дешифратора 4 единичный сигнал, который поступает на второй управляющий вход мультиплексора магистралей 5 и на вход второго формирователя 35 сигнала чтения. Мультиплексор магистралей 5 единичным сигналом на своем втором управляющем входе настраивается на коммутацию информации с информационного выхода блока буферной памяти 23 текущего цикла на информационный вход выход 3 устройства. Содержимое первой ячейки блока буферной памяти 23 текущего цикла поступает по информационному входу выходу 3 устройства в отлаживающую ЭВМ для запоминания и последующего анализа. Описанный процесс циклически повторяется до тех пор, пока вся необходимая информация из ячеек блоков буферной памяти эталона 16 и буферной памяти 23 текущего цикла не будет "перекачана" в отлаживающую ЭВМ для запоминания и последующего анализа возникновения и развития перемежающегося сбоя.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1996 |

|

RU2110833C1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| Устройство для отладки программ | 1988 |

|

SU1624460A1 |

| МОДУЛЬ МАТРИЧНОЙ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2168755C1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

Изобретение относится к вычислительной технике и может быть использовано для поиска перемежающихся отказов в микропроцессорных системах в реальном масштабе времени. Технической задачей изобретения является расширение функциональных возможностей устройства за счет возможности контроля микропроцессорных систем с обслуживанием процедур прерывания при поиске перемежающихся отказов в микропроцессорных системах. Устройство содержит дешифратор, мультиплексор магистралей, двоичный счетчик, блок буферной памяти эталона, мультиплексор адреса, регистр запуска, мультиплексор данных, семь триггеров, формирователь короткого импульса, селектор, регистр управления, три схемы сравнения, вычитающий счетчик импульсов, два формирователя сигнала чтения, два формирователя сигнала записи, блок буферной памяти текущего цикла, регистр адреса, восемь элементов И, четыре элемента ИЛИ, регистр возврата. 1 ил.

Устройство для поиска перемежающихся отказов в микропроцессорных системах, содержащее дешифратор, мультиплексор магистралей, двоичный счетчик, блок буферной памяти эталона, мультиплексор адреса, регистр запуска, мультиплексор данных, шесть триггеров, формирователь короткого импульса, селектор, регистр управления, две схемы сравнения, вычитающий счетчик импульсов, два формирователя сигнала чтения, два формирователя сигнала записи, блок буферной памяти текущего цикла, регистр адреса, семь элементов И, три элемента ИЛИ, причем адресный вход устройства для подключения к шине адреса отлаживающей ЭВМ соединен с первым информационным входом дешифратора, второй информационный вход которого соединен с входом управления устройства для подключения к шине управления отлаживающей ЭВМ, информационный вход-выход устройства для подключения к шине данных отлаживающей ЭВМ соединен с информационным выходом мультиплексора магистралей, с информационными входами регистра управления, регистра запуска, регистра адреса и вычитающего счетчика импульсов, первый выход дешифратора соединен с первым управляющим входом мультиплексора магистралей и с входом первого формирователя сигнала чтения, второй выход дешифратора соединен с вторым управляющим входом мультиплексора магистралей, третий выход дешифратора соединен через формирователь короткого импульса с единичным входом первого триггера, вход начальной установки устройства соединен с нулевыми входами первого, третьего, пятого и шестого триггеров, с обнуляющим входом двоичного счетчика и с вторым входом второго элемента ИЛИ, выход которого соединен с нулевыми входами второго и четвертого триггеров, информационный вход первого триггера соединен с шиной нулевого потенциала устройства, выход первого триггера является первым выходом синхронизации устройства для подключения к входу ожидания отлаживаемой микропроцессорной системы, четвертый, пятый, шестой и седьмой выходы дешифратора соединены соответственно с входами разрешения регистра управления, регистра запуска, вычитающего счетчика импульсов и регистра адреса, первый информационный выход мультиплексора данных соединен с информационным входом блока буферной памяти эталона, информационный выход блока буферной памяти эталона соединен с первым информационным входом мультиплексора магистралей, выход регистра управления соединен с входом управления селектора, выход регистра запуска соединен с первым входом первой схемы сравнения, выход первого формирователя сигнала записи соединен с входом записи блока буферной памяти эталона, информационный выход мультиплексора адреса соединен с адресным входом блока буферной памяти эталона, первый информационный вход устройства для подключения к контрольным точкам отлаживаемой микропроцессорной системы соединен с информационным входом мультиплексора данных, второй информационный вход устройства для подключения к тактирующим сигналам отлаживаемой микропроцессорной системы соединен с информационным входом селектора, третий информационный вход устройства для подключения к сигналам запуска отлаживаемой микропроцессорной системы соединен с вторым входом первой схемы сравнения, информационный выход блока буферной памяти эталона соединен с первым входом второй схемы сравнения, второй информационный выход мультиплексора данных соединен с информационным входом блока буферной памяти текущего цикла и с вторым входом второй схемы сравнения, инверсный выход которой соединен с первым входом первого элемента И, информационный выход мультиплексора адреса соединен с адресным входом блока буферной памяти текущего цикла, информационный выход которого соединен с вторым информационным входом мультиплексора магистралей, информационный выход двоичного счетчика соединен с первым информационным входом мультиплексора адреса, второй информационный вход которого соединен с выходом регистра адреса, выход первой схемы сравнения соединен с первыми входами второго и третьего элементов И, выход второго элемента И соединен со счетным входом вычитающего счетчика импульсов, выход обнуления которого соединен с единичным входом второго триггера, выход второго триггера соединен с первым управляющим входом мультиплексора данных, с первым входом четвертого элемента И, с первым входом первого элемента ИЛИ и с тактовым входом третьего триггера, информационный вход которого соединен с шиной единичного потенциала устройства, прямой выход третьего триггера соединен с вторым входом третьего элемента И, выход которого соединен с единичным входом четвертого триггера, инверсный выход третьего триггера соединен с вторым входом второго элемента И, выход селектора соединен с первым входом пятого элемента И, выход четвертого триггера соединен с вторым управляющим входом мультиплексора данных, вторым входом первого элемента И, с первым входом шестого элемента И и с вторым входом первого элемента ИЛИ, выход которого соединен с вторым входом пятого элемента И, выход пятого элемента И соединен со счетным входом двоичного счетчика, с третьим входом первого элемента И, с вторым входом четвертого элемента И и с вторым входом шестого элемента И, выход первого элемента И соединен с единичным входом пятого триггера, выход которого соединен с первым входом седьмого элемента И, выход переполнения двоичного счетчика соединен с первым входом второго элемента ИЛИ и с вторым входом седьмого элемента И, выход которого соединен с единичным входом шестого триггера, прямой выход шестого триггера соединен с первым управляющим входом мультиплексора адреса, с тактовым входом первого триггера и с вторым выходом синхронизации устройства для подключения к входу маскируемого прерывания отлаживающей ЭВМ, инверсный выход шестого триггера соединен с вторым управляющим входом мультиплексора адреса, выход шестого элемента И соединен с входом второго формирователя сигнала записи, выход которого соединен с первым входом третьего элемента ИЛИ и с входом записи блока буферной памяти текущего цикла, второй выход дешифратора соединен с входом второго формирователя сигнала чтения, выход которого соединен с входом чтения блока буферной памяти текущего цикла, выход первого формирователя сигнала чтения соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с входом чтения блока буферной памяти эталона, выход четвертого элемента И соединен с входом первого формирователя сигнала записи, отличающееся тем, что в устройство введены регистр возврата, третья схема сравнения, седьмой триггер, восьмой элемент И, четвертый элемент ИЛИ, причем восьмой выход дешифратора соединен с входом разрешения регистра возврата, информационный вход которого соединен с информационным входом-выходом устройства для подключения к шине данных отлаживающей ЭВМ, выход возврата соединен с первым входом третьей схемы сравнения, второй вход которой соединен с четвертым информационным входом устройства для подключения к шине данных отлаживаемой микропроцессорной системы, первый вход восьмого элемента И является первым входом синхронизации устройства для подключения к выходу выборки кода команды отлаживаемой микропроцессорной системы, прямой выход третьей схемы сравнения соединен с вторым входом восьмого элемента И, прямой выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с входом начальной установки устройства, выход четвертого элемента ИЛИ соединен с единичным входом седьмого триггера, нулевой вход седьмого триггера является вторым входом синхронизации для подключения к выходу подтверждения прерывания отлаживаемой микропроцессорной системы, прямой выход седьмого триггера соединен с третьим входом пятого элемента И.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| SU, авторское свидетельство, 1672455, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| RU, патент, 2030784, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1997-12-20—Публикация

1996-03-28—Подача