1

Изобретение относится к импульсной технике, в частности к устройствам определения величины и знака разности частот независимых во времени импульсных последовательностей, и может быть использовано в частотных системах обработки информации и системах автоподстройки частоты.

Известен цифровой частотшай дискриминатор, содержащий злемент И и триггеры CQ

Однако данное устройство не позволяет проводить обработку частот более двух импульсных последовательностей одновременно.

Наиболее близким по технической сущности к изобретению является цифровой частотный дискриминатор, содержащий генератор тактовых импульсов, два блока синхронизации и три триггера 12 .

Этот цирфовой частотный дискриминатор не позволяет производить дискриминирование более двух импульсных последовательностей одновременно, в то время как нередко возникает необходимость в сравнении разности и знака двух частот с третьей частотой, например, при фор-мировании частот, изменяющихся относительно опорной частоты в заданном диапазоне . В таких случаях приходится использовать два последовательно соединенных дискриминатора, что значительно усложняет устройство, ухудшает его быстродейс твие и надежное ть.

Цель изобретения - расширение функциональных возможностей за счет увеличения числа одновременно дискриминируемых частот импульсных последоватепьно.стей.

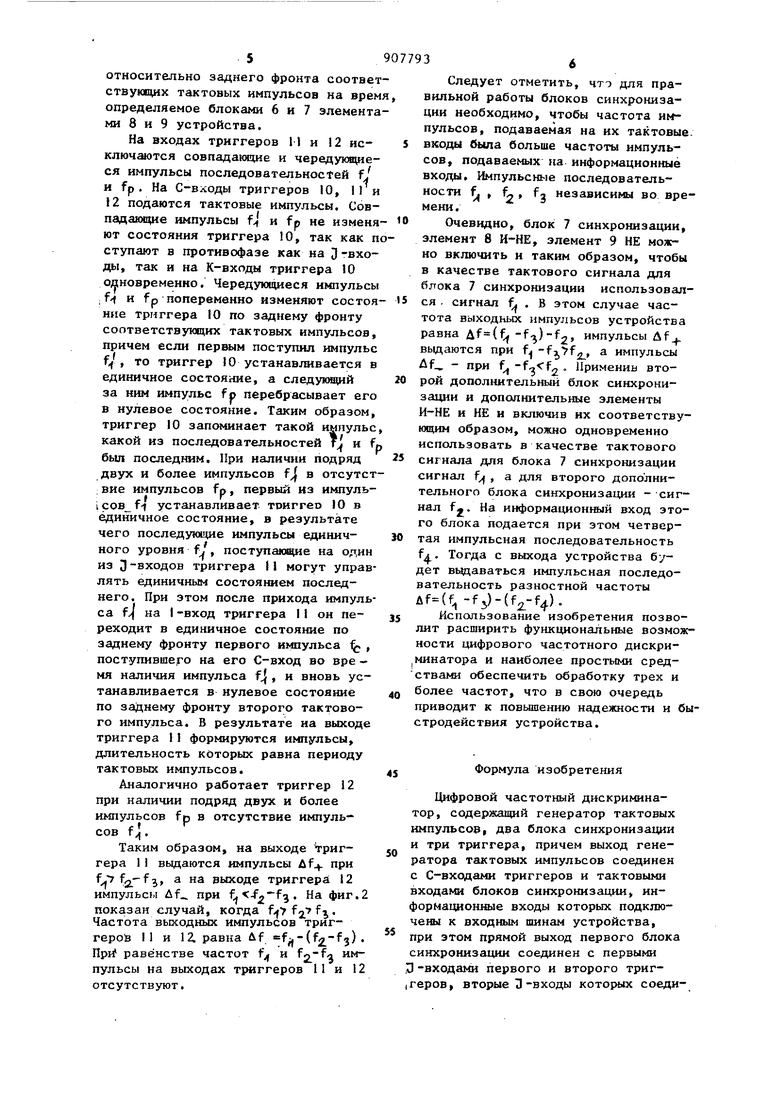

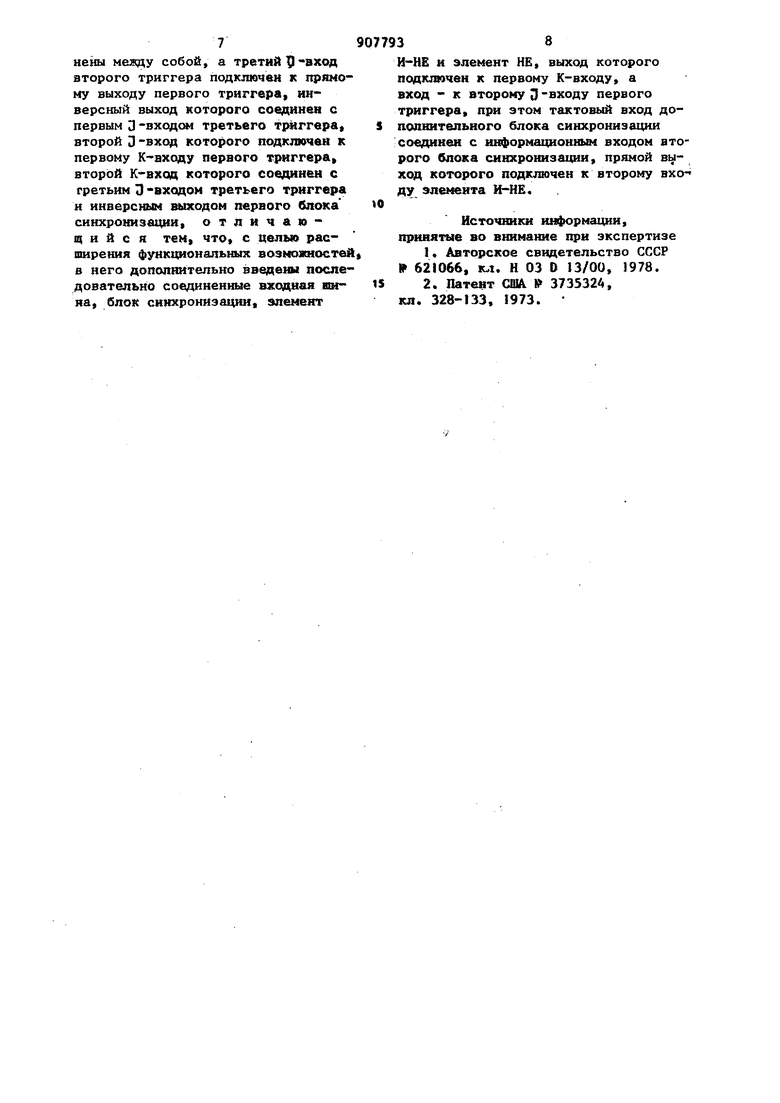

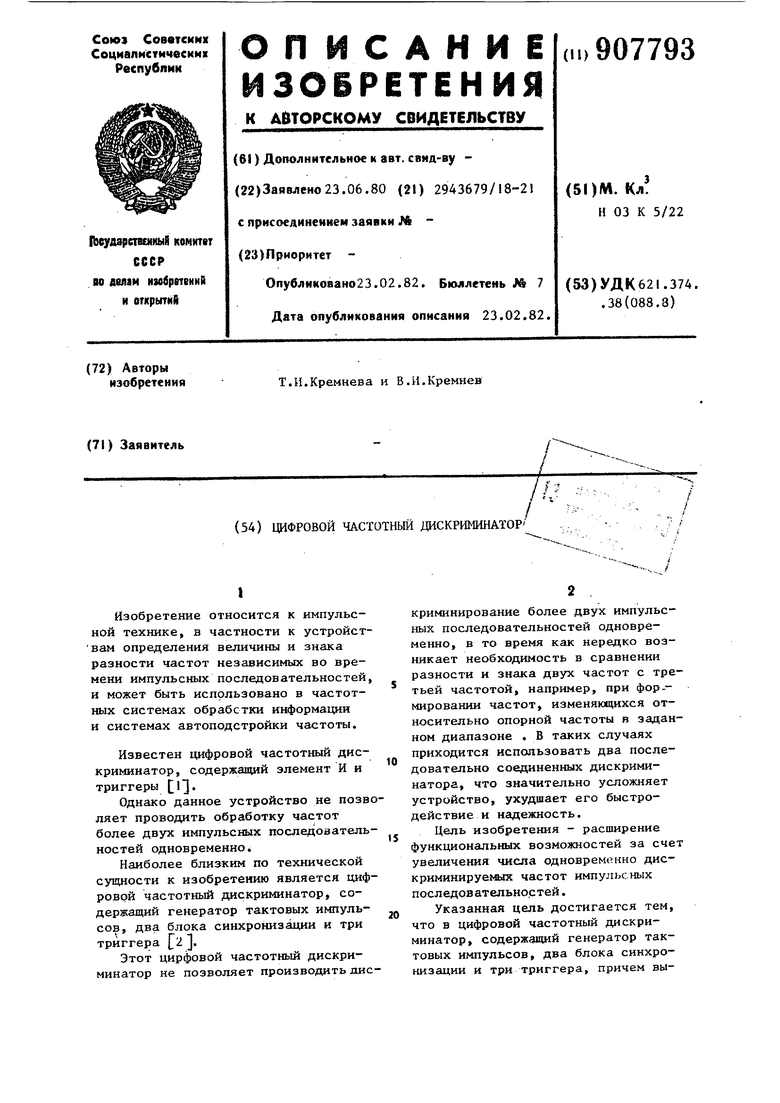

Указанная цель достигается тем, что в цифровой частотный дискриминатор, содержащий генератор тактовых импульсов, два блока синхронизации и три триггера, причем выход генератора тактовых импульсов соединен с С-входами триггеров и тактовыми входами блоков синхро низации, информационные входы которых подключены к входным пшнам устройства, при этом прямой выход первого блока синхронизации соединен с первыми Э-входами первого и второго триггеров, вторые 3-входы которых соединены между собой, а третий 3-вход второго триггера подключен к прямому выходу первого три гера, инверсный выход которого соединен с первым Г7-ВХОДОМ третьего триггера, второй 5-вход которого по ключен к первому К-входу первого «триггера, второй К-вход которого со динен с третьим 3-входом третьего триггера и инверсным выходом первого блока синхронизации, дополнитель но введены последовательно соединен ные входная шина, блок синхронизации, элемент И-НЕ и элемент НЕ, вых которого подключен к первому К-входу, а вход - к второму D-входу первого триггера, при этом тактовый вход дополнительного блока синхроiнизации соединен с информационным входом второго блока синхронизации, прямой выход которого подключен к второму входу элемента И-НЕ. На фиг. I приведена структурная схема цифрового частотного дискриминатора на фиг. 2 - временные цааграммы, пояснякж е работу предлагаемого дискршщнатора. Устройство содержит входные шины э 2 и 3,генератор 4 тактовых им пульсов, основные 5 и 6 и дополнительный 7 блоки синхронизации, элемент 8 И-НЕ, элемент 9 НЕ и триггеры 10, Пи 12. Устройство работает следухшщм об разом. Импульсы первой последовательности f с шины 1 поступают на инфо мационный вход блока синхронизации 5. На тактовый вход э-вого блока подаются импульсы f от генератора 4 тактовых импульсов. На выходах блок синхронизации 5 формируются импульсы, длительность которых равна пери оду тактовых импульсов, а частота частоте сигнала t« Импульсы с прямого выхода имеют единичные уровни, а с инверсного - нулевые. На фиг, 2 доказаны импульсы , снимаегше с прямого выхода блока 5 и привязанные к заднему фронту соответствующих импульсов f(, , Импульсы f. задержаны относительно заднего фронта тактовых импульсов на время, определяемое элементами блока 5, и подйются на первые О-входы триггеров 10 и II, а импульсы f с инверсного выхода блока 5 подаются на второй К-вход и третий 3-вход соответственно триггеров 10 и 12. Импульсы второй последовательности fj, с шины 2 подаются на информационный вход блока 6, на тактовый вход которого подаются импульсы f На прямс выходе блока 6 формируются импульсы f, длительность которых так же равна периоду тактовых импульсов, а частота - частоте сигнала fjj. Импульсы fa привязаш к заднему фронту соответствутацих импульсов ff-, и подаются на первый вход элемента 8 И-НЕ. Импульсы второй последовательности 2. подаются также на тактовый вход блока 7, на информационный вход которого подаются импульсы третьей последовательности f с шины 3. Блок 7 идентичен блокам 5 и 6. С инверсного выхода этого блока выдаются импульсы нулевого уровня fi, длительность которых; равна периоду сигнала %, а частота - частоте сигнала fn. Импульсы f (фиг, 2) формируются по заднему фронту импульсов tj и пода19ТСЯ на второй вход элемента 8 И-НЕ, который ввдает на выходе сигнал нулевого уровня при подаче ui его входы сигналов единичного уровня, поэтому казвдый импульс нулевого уровня f запрещает прохождение на выход элемента 8 одного импульса единичного уровня последовательности fL. С выхода элемента 8 И-НЕ выдаются импульсы нулевого уровня fp , длительность которых равна периоду сигнала ff-,,a частота - разностной частоте импульсных последовательностей f f.(Задержки, вносимые элементами устройства, на фиг. 2 условно не показаны для упрощения изложения принципа ее работыЛ Импульсы fp подаются на 3 входы триггеров 10 и 11 и на вход элемента 9 НЕ. С выхода элемента 9 НЕ выдаются импульсы единичного уровня fр, которые поступают на один из К-входов триггера 10 и на один из -входов триггера 12. Импульсы fp задержаны . 59 относительно заднего фронта соответствующих тактовых импульсов на время определяемое блоками 6 и 7 элементами 8 и 9 устройства. На входах триггеров 11 и 12 исключаются совпадающие и чередующиеся импульсы последовательностей и tp. На С-влоды триггеров 10, 1 Г и подаются тактовые импульсы. Совпадающие импульсы fj и fp ие иэменяют состояния триггера 10, так как по ступают в противофазе как на jj -входы, так и на К-входы триггера 10 одновременно. Чередующиеся импульсы . f- и fp попеременно изменяют состояние триггера 10 по заднему фронту соответствующих тактовых импульсов, причем если першям поступил импульс f, то триггер 10 устанавливается в единичное состояние, а следующий за ним импульс fp перебрасывает его в нулевое состояние. Таким образом, триггер 10 запоминает такой импульс, какой из последовательностей г и fp был последним. При наличии подряд двух и более импульсов f в отсутствие импульсов fр, первый из импульiсов f устанавливает тоиггео 10 в единичное состояние, в результате чего последующие импульсы единичного уровня fj , поступаищие на один из 3-входов триггера 11 могут управлять единичным состоянием последнего. При этом после прихода импульса f на I-вход триггера I1 ои переходит в единичное состояние по заднему фронту первого имшульса , поступившего на его С-вход во аре мя наличия импульса f , и вновь устанавливается в нулевое состояние по заднему фронту второго тактового импульса. В результате на выходе триггера I1 формируются иьшульсы, длительность которых равна периоду тактовых импульсов.

Аналогично работает триггер 12 при наличии подряд двух и более импульсов fp в отсутствие импульсов .

Таким образом, на выходе триггера 1 I выдаются импульсы Af. при f., а на выходе триггера 12 импульсы Af при f -f2f3« фиг.2 показан случай, когда , Частота выходных импульсов тригII и 12: равна uf. f;,-(f2-f3) .

герой

fo-f ИМnprf равенстве частот fjj и

11 И 12

пульсы на выходах триггеров

отсутствуют.

тельного блока синхронизации - сигнал fjj. На информационшай вход этого блока подается при этом четвертая импульсная последовательность ff,- Тогда с выхода устройства будет ввдаваться импульсная последовательность разностной частоты

uf(f -f5)-().

Использование изобретения позволит расширить функциональные возможности цифрового частотного дискри|Минатора и наиболее простыми средствами обеспечить обработку трех и более частот, что в свою очередь приводит к повышению надежности и быстродействия устройства.

Формула изобретения

Цифровой частотный дискригданатор, содержащий генератор тактовых импульсов, два блока синхронизации и три триггера, причем выход генератора тактошлх импульсов соединен с С-входами триггеров и тактовыми входами блоков синхронизации, информациошше входы которых подключешл к входным шинам устройства, при этом прямой выход первого блока синхронизации соединен с первыми iD -входами первого и второго триг|Геров, вторые П-входы которых соеди3Следует отметить, что для правильной работы блоков синхронизации необходимо, чтобы частота импульсов, подаваемая на их тактовые, вкоды была больше частоты импульсов, подаваемых на информацнонные входы. РЫпульсные последовательfy f 3 независимы во вреностимени. Очевидно, блок 7 синхронизации, злемент 8 И-НЕ, элемент 9 НЕ можно включить и таким образом, чтобы в качестве тактового сигнала для блока 7 синхронизации использовался . сигнал . В этом случае частота выходньгх импульсов устройства равна Af( мпульсы Af выдаются при f . импульсы uf-. - при f ° применив второй дополнительный блок синхронизации и дополнительные элементы И-НЕ и НЕ и включив их соответствующим образом, можно одновременно использовать в качестве тактового сигнала для блока 7 синхронизации сигнал f , а для второго дополнийены между собой, а третий 9-вход второго триггера подключен к прямому выходу первого триггера, инверсный выход которого соединен с первым 3-входсж третьего триггера второй которого подключен к первому К-входу первого триггера второй К-вход которого соединен с третьим D входои третьего триггера и инверсным выходом первого блока синхронизации отличающийся тем, что с целью расширения функциональных возможностей в него дополнительно введены последовательно соединенные входная шияа блок синхронизации элемент

И-НЕ и элемент КБ выход которого подкшочен к первому К-входу а вход - к второму JJ -входу первого триггера при этом тактовый вход дополнительного блока синхронна а1щи ;соединен с информационным входом второго блока синхронизации прямой Bidход которого подключен к второму вхо ду элемента ii-HE.

Источники информации, принятые во вннмание при экспертизе

1 Авторское свидетельство СССР 9 621066 К.1. Н 03 D 13/00 1978.

2. Патент СИЛ В 373532А кл. Г973.

и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации импульсов | 1985 |

|

SU1325677A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1070694A1 |

| Устройство для умножения частоты на код | 1987 |

|

SU1522202A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| Устройство для измерения отношения частот последовательностей импульсов | 1988 |

|

SU1599793A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Цифровой нуль-орган | 1980 |

|

SU941998A1 |

| Устройство тактовой синхронизации | 1983 |

|

SU1099403A1 |

| Цифровой электропривод | 1983 |

|

SU1102002A1 |

| Электропривод постоянного тока | 1981 |

|

SU995247A1 |

г Са «9% с

aSs 1 CJ ;ikc )

«S

Wi

-( I

S

S

е

«

-м ч

ua

45

4j г

.

ч

« ;

Авторы

Даты

1982-02-23—Публикация

1980-06-23—Подача