1

Изобретение относится к области вычислительной и измерительной техники и может быть использовано для построения управляющих автоматов и автоматов обработки измерительной информации высокой производительности.

Известно устройство 1, состоящее из логической схемы (автомат без памяти) i автомата с памятью, в который входят элементы памяти (например, триггеры, образующие регистр), определяющие объем внутренней памяти автомата. На вход автомата с памятью поступают сигналы изменения состояния, а его выход подключен к логической схеме. Входные сигналы иодаются на логическую схему, а с ее выхода сннмаются выходные сигналы.

Проектирование таких устройств при больщом числе входных сигиалов, что имеет место при контроле, практически невозможно, оно нолучается с большим числом недоонределенных состояний, громоздким ио конструкции, а уиификация исключается.

Из известиых устройств, наиболее близким по технической сущности к изобретению, является устройство 2, содержащее дещифратор комаид, выходом подключенный к выходу устройства и к управляющему входу измерительного блока, информационный выход которого соединен с информационным входом устройства, выход - с входом дешифратора состояний.

Однако синтез такого устройства довольно и минимизация структуры сопряжена с рядом трудностей, поскольку она зависит от особенностей объекта, алгоритма его функционнровання и т. д.

Структурные схемы матрицы внутренних микроопераций и регистров микрокоманд, соединенных между собой матрицей формирования кода следующей микрокоманды, имеют свою специфику построення, характерную только для заданцого объекта, и не пригодны для другого. В связи с этим структурные схемы указанных функциональных узлов, не могут быть унифнцированы, а следовательно, и трудно поддаются микроминиатюризации.

Больщое число функциональных узлов, входящих в схему, и логических элемеитов с памятью ц без памяти делает устройство сложным и громоздким ио конструкции, а прп увеличении числа управляющпх команд значптельно усложняется регистр и деплпфратор.

Перестройка устройства для работы с другим изделием ирактически невозможна, поскольку структура не унифицирована.

Цель изобретения - повышение коэффициента использования оборудовання н упрощение перестройки.

Это достигается тем, что в устройство введена однородная кодирующая структура, входы которой соединены с соответствующнмн выходамн деошфратора состояний, управляющий вход подключен к управляюп1,е.1у входу устройства, выходы - к соответствуюии1м входам дешифратора команд, одпородная кодирующая структура содержит ячейки ио числу команд, каждая пз которых включает пары последовательно соединенных элементов ИЛИ, И но числу разрядов, и триггер. Единичный вход трнггера и объединенные входы элементов И нодключены к управляюп1,ему входу однородной кодируюи1ей структуры, входы и выходы которой соед1И ены соответственно с входами элементов ИЛИ и выходамн элементов И, едииичиый выход триггера - с одиим пз входов элемента ИЛИ нулевого разряда, а его нулевой выход - с одиим пз входов элемеита И нервого разряда. Пулевой вход триггера подключен к выходу элемента ИЛИ первого разряда.

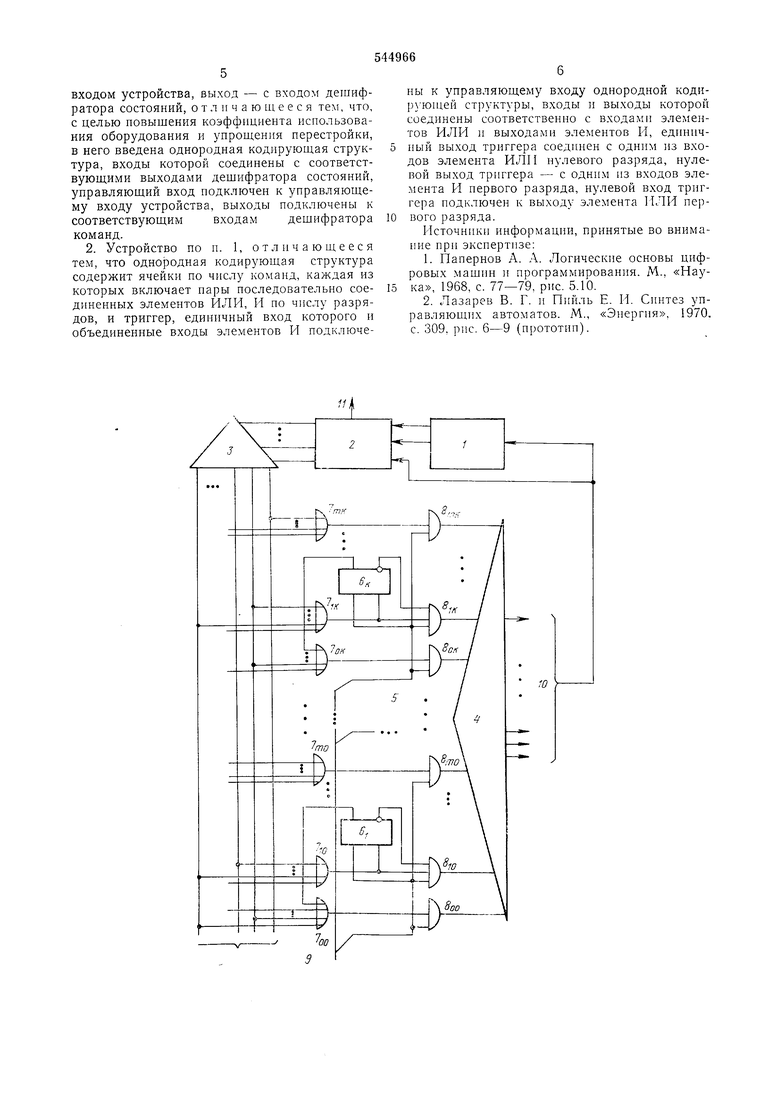

Структурная схема устройства для мнкропрограммного управления системами контроля иредставлена иа чертел е.

Устройство, иодключенное к контролируемой радноапиаратуре 1 и измерительному блоку 2, содержит дешифратор 3 состояннй, дешифратор 4 команд, однородную кодирующую структуру .5. Однородная кодирующая структура состоит пз отдельных ячеек, число которых равно к - числу задаюи1пх комаид управлеиия X. Принцип ностроенпя каждой ячейки одинаков. Б нее входит равное число логических элементов И, ИЛИ и одии элемент с памятью, например триггер с раздельпымп входами. Иа чертеже показаны триггеры 6i-6ft, элементы ИЛИ 7оо-7mh, элементы И 8оо-8,7,ft вход 9 устройства, выход 10 ден1ифратора команд, выход 11 устройства.

Работает устройство для микропрограммного управлення енстемами коитроля следующим образом.

Совокупность /п-выходов каждой ячейки одпородной коднрующей структуры, например Yok, Yih, , Ymh дает полный набор всех Y, соответствующих заданному состоянню выходов нзмерптельного блока до, q, ..., qn, определяющих соетояппя выходов деищфратора состояний Q в каждый момент автоматного временн.

Устройство прнБодится в началпьое состояние, когда Х 0, У 0, Q 0. Подается одна нз команд управлеппя на вход устройства, панрнмер X - . При этом включается к-я ячейка однородной кодируюн1ей структуры и запускается триггер этой ячейки. С единичиого выхода триггера через элемент ИЛИ нулевого разряда на вход элемента И того же разряда нодается еднница и на его выходе появляется управляющий сигнал Уо). Все остальные --. Ymk 0, в результате чего на выходе к-й ячейкп образуется первая микрокомаида 00...001, которая вызывает появления управляющей команды на выходе дешифратора команд в виде заданной комбинаЦПН YO, У), ..., YmНеобходимые команды } ностунают на вход ко1ггролнруемой радноаннаратуры, а другая их часть У --- непосредствеино на нзмерителы1ый блок 2, в который входят элемеитарные автоматы с памятью, сравнивающие устройства и связанные с ними электронные аналоговые преобразователи.

Команды У н У заставляют радиоаппаратуру работать в задапном режиме п выдавать на эле1мепты памяти, сравниваюн1,ие устройства п апалоговыс преобразователи аналоговую п дискретную информапню.

В процессе сравненпя и обработки нифорЛ1ацип элементы памяти измерительиого блока приходят в такое состояние, что на его выходе ноявляется комбинатия 170, ь , Яп, соответствуюп1ая па выходе дешифратора 3 состояний, например, епгпалу Q,v (остальные ..- QA-I O). Сигнал QK возбулсдает вход элемента Р1ЛР1 нервого разряда и вызывает опрокидывание триггера. В результате этого на всех трех входах и

выходе элемента И нервого разряда паявляются едпппчные спгналы, а на входах элементов ИЛИ нулевого и других разрядов все входные величины равны пулю. Па выходе к-й ячейкп возппкает новая мнкрокоманда 00...010,

преобразуемая деп1ифратором 4 в следующую выходную команду УО, УЬ ..., Ут- Эта команда заставляет отрабатывать радиоаииаратуру и измер11тельпый блок 2 следующий этап алгоритма управления. В результате блок 2

ириходпт в состояиие, что вызывает появление новой микрокоманды 00...011 н т. д. В дальнейшей работе ячейкп трпггер не нринимает участия. По окончаппп обработки комапды Х, как

правило все Кол, , , Ymk нриннмают значенне единицы. Эта команда обычно заканчивает этан управлепия и с выхода измерительного блока 2 выводится аналоговая или дискретиая ииформация о зиачении контролнруемой величппы для дальиейп1ей обработки или регистрации.

Задание входных комаид может осуществляться в десятичном п двоичном коде. В первом случае при иоступлеппп команды

включается одна ячейка, во втором число включенных ячеек ои)еделяется двоичным кодом.

Перестройка устройства обеспечивается нереключеиием связей выходов дешифратора 3

состояппй п входов элементов ИЛИ всех ячеек, а также пзмеиеппем внутренних связей входов и выходов депшфратора 4.

Ф о р м у :i а изобретения

1. Устройство для микроирограммного управлеппя системами коитроля, содержащее депшфратор комаид, выход которого подключен к выходу устройства п к управляющему входу пзмер ггельного блока, ннформацпонный выход которого сосдппен с ппформационным

входом устройства, выход - с входом дешифратора состояний, отличаю ш е е с я тем, что, с целью повышения коэффициента использования оборудования и упрош,ения перестройки, в него введена однородная кодируюш,ая структура, входы которой соединены с соответствующими выходами дешифратора состояний, управляющий вход подключен к управляющему входу устройства, выходы подключены к соответствующим входам дешифратора команд.

2. Устройство по п. 1, о т л и ч а ю ш, е е с я тем, что однородная кодирующая структура содержит ячейки по числу команд, каждая из которых включает пары последовательно соединенных элементов ИЛИ, И по числу разрядов, и триггер, единичный вход которого и объединенные входы элементов PI подключены к управляющему входу однородной кодирующей структуры, входы и выходы которой соединены соответственно с входами элементов ИЛИ и выходами элементов И, единичный выход триггера соединен с одним 1з входов элемента ИЛИ нулевого разряда, нулевой выход триггера - с одним из входов элемента И первого разряда, нулевой вход триггера подключен к выходу элемента ИЛИ первого разряда.

Источники информации, принятые во внимание при эксиертизе:

1.Папернов А. А. Логические основы цифровых машин и программирования. М.. «Иаука, 1968, с. 77-79, рис. 5.10.

2.Лазарев В. Г. и Пийль Е. И. Синтез управляюпщх автоматов. М., «Энергия, 1970. с. 309. рис. 6-9 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммногоупРАВлЕНия | 1978 |

|

SU798835A1 |

| Цифровая электронная вычислительная машина последовательного действия | 1975 |

|

SU532295A1 |

| Устройство для микропрограммного управления | 1978 |

|

SU763899A1 |

| Устройство управления цифровой вычислительной машины | 1975 |

|

SU598076A1 |

| Устройство многопрограммногоупРАВлЕНия | 1978 |

|

SU830381A1 |

| Устройство синтаксически управляемого перевода | 1989 |

|

SU1651298A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2049347C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2042189C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046395C1 |

Авторы

Даты

1977-01-30—Публикация

1974-08-02—Подача