(54) УСТРОЙСТВО УПРАВЛЕНИЯ МАШИНЫ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ

НИИ при приходе «иустых команд, необходимых для органнзацпи возможных персход.ов между адресами лри применении «соееднего кодирования кодов команд программы.

Ы.ель изобретения - повыпюние быс гроденствия устройства.

Это достигается тем. что в предлагаемое устройство введен логический блок, информационный вход которого подключен к выходу дешифратора номера разрядов, уиравляюпип вход подключен к управляющему выходу регистра гр пи команд, а выход логического блока подключен ко входу регистра команд.

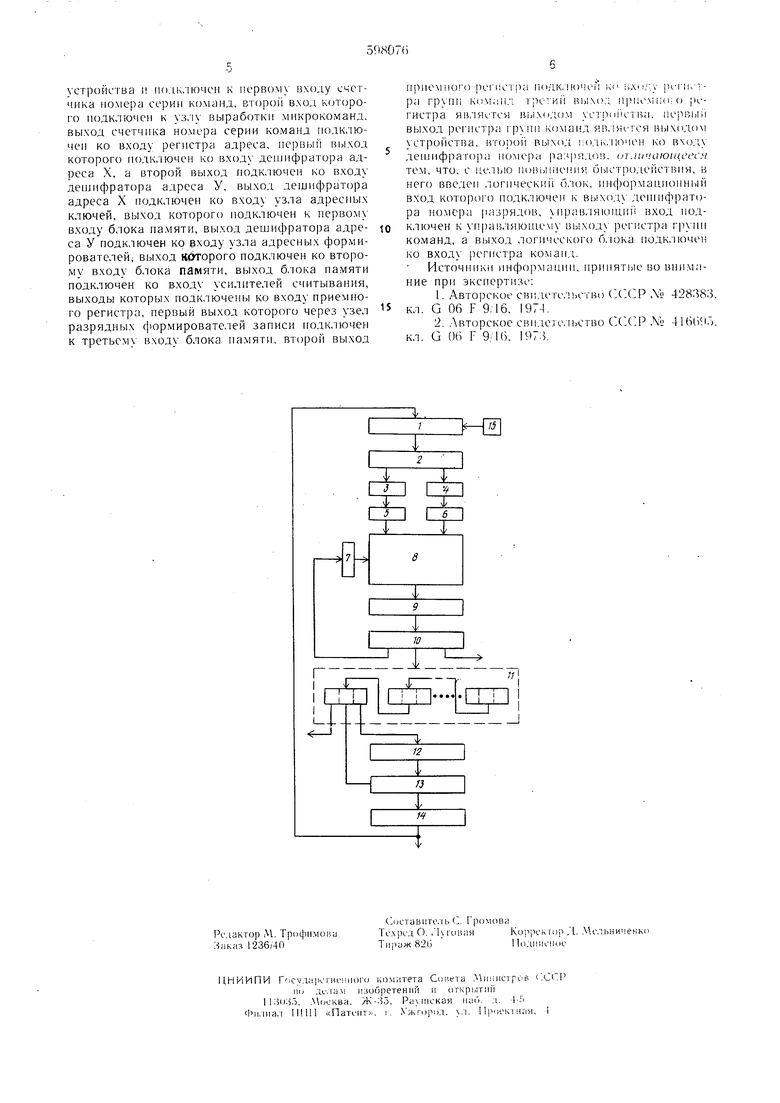

На чертеже представлена функцнональпая блок-схема предлагаемого устройства.

Устройство управления цифровой вычислительной машины состоит из счетчика ио.мера серии команд, регистра 2 адреса, дешифратора 3 адреса X, дешифратора 4 адреса У, узла 5 адресных- ключей, узла 6 адресных формирователей, узла 7 разрядных формирователей записи, блока 8 памяти, узла 9 усилителей считывания, приемного регистра 10, регистра 11 групп команд, дешифратора 12 номера, разрядов,логического блока 13, регистра 14 команд, узла 15 выработки микрокоманд.

Устройство работает следующим образом.

Перед записью npoi-раммы в блок памяти коды команд програм.мы кодируются с кодовыми расстояниями равными «1 и «К 1, где К- заданная разрядность кода. При кодировании допускается введение «пустых команд, необходимых д,чя соблюдения иринятого закона кодирования, при поступлении которых ЦВМ не выполняет операций по реализации програ.мм. Кодирование кода адреса и кода операции происходит аналогичным образом. принцип работы устройства рассматривается иа примере одной из указанных частей кода команды (например кода адреса).

На каждом очередно.м цикле код предыдущей команды записывается в регистр команд 14.

Код номера серии команд с выхода счетчика 1 подается на вход регистра 2, а к содержимо.му счетчика 1 но си1налу, иостуиаюшему с узла выработки микрокоманд 15, прибавляется единица. Выходы младших и стари1их разрядов кода адреса расшифровываются соответственио ден1ифраторами 3 и 4, определяющими местоположение ячейки памяти (в координатах X и У) в блоке 8, соответствующее Э1о.му коду. Выходные сигналы дешифраторов 3 и 4 поступают на входы узлов 5 и 6, вырабатывающих ток считывания в выбранной ячейке блока 8, хранящей код серии команд. Выходные сигналы блока 8 усиливаются в узле 9 и пос1упают на вход регистра 10. Далее записанный в регистре 10 код регенерируется в ту же ячейку блока 8 с помощью узла разрядных формирователей записи 7. Одновременно записанный в регистре 10 код подается на вход регистра групп И, состоящего из групп триггеров по числу команд в серии.

Регистр групп 11 осуц;ествляет преобразование кода, записанного в параллельной форме в регистре 10, в параллельно-последовательную форму и передает для дальнейп ей обработКН. Киждаягруппа триггеров состоит из трех частей: код первой части указывает помер изме}1яемого разряда в коде операции, код второй части указывает на то, какой код- ирямой или обратный дешифратора 12 до,1жен складываться ио моду.1ю 2 с содержимым регистра команд 14, код третьей части указ1 1вает номер нз.меняемого разряда в коде адреса.

Код третьей части первой группы триггеров регистра групп 11 переписывается в денрифратор номера разрядов 12. Код второй части поступает в лошческнй блок 13. а кг)д первой части на выход устройства.

Выходные сигналы де1нифратора 12 указывают номер разряда кода адреса в коде предыдущей команды, который необходимо изMeiiUTi), чтобы получить код адреса иос.чедующей команды.

Логичес кий блок 13 реализует функцию Z Д. где а-можно интернретирсвать, как логическую иеременную на управ.чяющем входе, а /J - как логическую переменную иа информационном входе .iorH4ecKor(j блока 13, Если на уирав;1яюн1ий вход логического блока 13 иостунает из регистра групп 11 логическая «1, а на информационный вход логического блока ноступает код с дешифратора 12, то этот код передается без изменения на выход логического блока, а если на унравляюиии вход логического блока иоступает ,1огический «О, а на информационный вход логического блока 13 иоступает код с дешифратора 12, то иа выходе логического блока получаем обратный КО.1, который .ммируетсн по .модулю 2 с содержимым регистра команд 14.

После выполнения нервой команды начинается формирование второй и т. д., каждой очередной команды данной серии. Для этого содержимое всех групп триггеров регистра 11 сдвигается на одну группу влево. Далее происходит расшифровка, формирование и выполнение каждой очередной ко.манды способо.м, аналогичным описанному выше. После формирования и вьпюлнения всех команд данной серии начинается обработка следующей серии команд, адрес- которой содержится в счетчике 1.

Введение логического блока с указанными связями позволяет увеличить число переходов от любого адреса к адресу и уменьшить ограничения при кодировании, что, в свою очередь, иозволяет исключить или сократить количество «пустых комаид. Это позволило увеличить быстродействие устройства иа время выборки и фор.мироваиия пск.поченной части «пустых коанд.

Формула изобретения

Устройство управления цифровой вычислиельной машины, содержащее счетчик номера ерии команд, узе, выработки микрокоманд, егистр адреса, дептифратор адреса X, дешифатор адреса У, узел адресных ключей, узел адесных формирователей, узел разрядных форирователей записи, блок памяти, усилители читывания, приемный регистр, регистр групп оманд, дешифратор номера разрядов, регистр оманд, выход которого является выходом устройства и подключен к первому входу счетчика номера серин команд, второй вход которого подключен к узлу выработки микрокоманд, выход счетчика номера серии команд подключен ко входу регистра адреса, первый в|,1ход которого подключен ко входу деп пфратора адреса X, а второй выход подключен ко входу деи.1ифратора адреса У, выход дешифратора адреса X подключен ко входу узла адресных ключей, выход которого подключен к первому входу блока намяти, выход дешифратора адреса У подключен ко входу узла адресных формирователей; выход которого подключен ко второму входу блока памяти, выход б,тока памяти подключен ко входу усилителей считывания, выходы KOTOpijix подключены ко входу приемного регистра, первый выход которого через узел разрядных формирователей записи подключен к третьему входу блока намятн, второй выход нрнемпого регистра полк.-цочен кс ).v porii --ра KoMaii.i т Х-ги| | выход приемного регистра яв.тястся Bijixo.iOM устгкичтва, перрлл выход регистра групп команд яв.пнтся выходом устройства, BT(jpoii выход 1;одк,1К1чен ко ден ифратора номера разрядов. (ji.iuu ioiiieec.4 тем, что, с целью 11()Вь нен1-;$ б1 1стродействпя, в него введен логнческш б.чок, ннформацнонный вход KOTOpoio подк,1ючен к выходу дешифратора номера разрядов, иравляющ ; вход подключен к управляющему выходу групп команд, а выход логического б.юка нодк.иочен ко входу регистра команд. Иеточннки информации, при11ят151е во вни.мание при экспертизе: 1.Авторекое еви.1ете, ((,СР Л 428383. кл. G Об F 9; 16, 197-1. 2..Авторское сви.1е.1е,1ьство (ХСЛ- ,М 416()i). кл. G 06 F 9/16, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Программируемое устройство для контроля цифровых систем | 1986 |

|

SU1439588A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

Авторы

Даты

1978-03-15—Публикация

1975-10-21—Подача