Изобретение относится к вычислительной технике и может быть использовано при построении систем управления объектов новой техники и в составе сложных систем управления ЭВМ различных классов.

Цель изобретения повышение достоверности функционирования за счет запоминания состояний устройства при сбое и возвратов к ошибочно выполненным командам для многократно вложенных последовательностей команд.

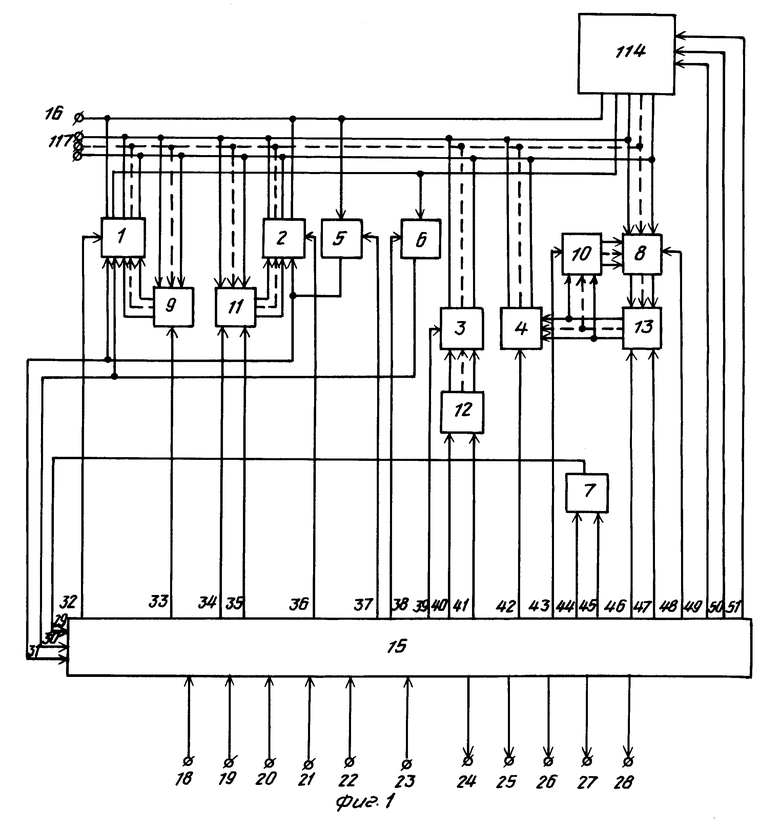

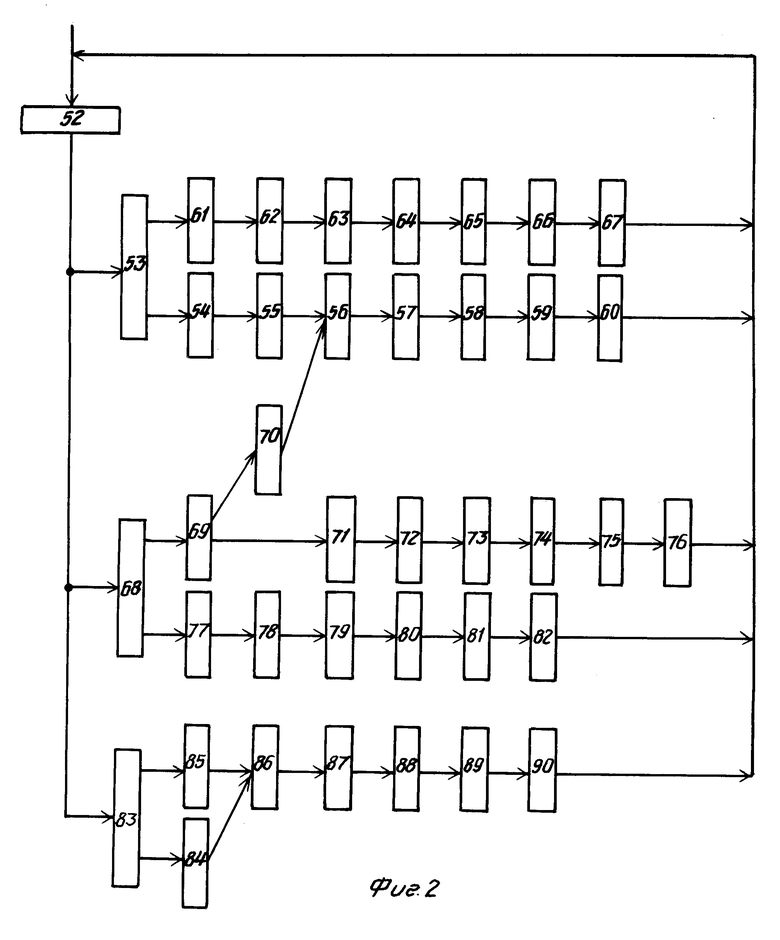

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 показан пример блок-схемы микропрограммы работы устройства.

Устройство содержит четыре группы 1-4 элементов И, триггеры 5 режима, 6 признака последнего кода и 7 записи, мультиплексор 8 информации, регистры 9 информации и 10 вершины магазина, счетчики 11 индекса, 12 магазина и 13 базы, блок 14 памяти информации, микропрограммный автомат 15 внутреннего управления, вход-выход 16 режима восстановления ошибочной команды устройства, входы-выходы 17 информации устройства, входы логических условий 18 подтверждения выдачи операции, 19 подтверждения индикации завершения цикла, 20 приема операции, 21 требования выдачи операции, 22 запрета выдачи операции, вход 23 тактовых импульсов устройства, выходы индикации 24 приема кода операции, 25 приема признаков выдачи операции, 26 выдачи операции, правильного 27 и неправильного 28 завершения цикла управления, выход 29 триггера записи, выход 30 триггера признака последнего кода, выход 31 триггера режима, выходы 32-51 микропрограммного автомата 15.

Блок-схема микропрограммы работы устройства содержит микрокоманду 52 начального состояния ожидания и анализа сигнала с входа 20, 21 или 22, микропрограмму 53-60 выдачи информации на входы-выходы 17, признака режима на вход-выход 16, сигналов 24 индикации приема кода операции, 26 выдачи операции и ожидания логического условия с входа 18, микропрограмму 53, 61-67 повторной выдачи на входы-выходы 17 ранее неправильно выполненной команды, признака режима на вход-выход 16, сигналов 24 индикации приема кода операции, 26 выдачи операции и ожидания логического условия с входа 18, микропрограмму 68-70, 56-60 выдачи при "нулевом" признаке режима на входы-выходы 17 одной (включая последнюю) операции последовательности, определенной ранее принятым входным кодом операции, сигналов на выход 25 индикации приема признаков выдачи операции и на выходы 26 индикации выдачи операции, а также ожидания логического условия с входа 18, микропрограмму 68, 69, 71-76 успешного окончания формирования последовательности выходных управляющих кодов формирование сигналов на выходах 25, 27 и ожидание поступления сигнала с входа 19, микропрограмму 68, 77-82 реакции устройства на правильное выполнение ранее неправильно выполненной операции формирование сигналов на выходах 25, 27 и ожидание сигнала входа 19, микропрограмму 83, 85-90 неуспешного окончания формирования последовательности выходных управляющих кодов формирование сигналов на выходах 25, 28 и ожидание сигналов с входа 19, микропрограмму 83, 84, 86-90 неуспешного окончания повторной выдачи операции (ранее запомненной неправильно выполненной операции) формирование сигналов на выходах 25, 28 и ожидание сигнала с входа 19.

Входы-выходы 17 устройства и вход-выход 16 режима выполнены как многоразрядная общая шина. Выходы групп 1-4 элементов И и выходы блока 14 памяти подключены к общей шине по схеме ПРОВОДНОЕ ИЛИ.

В блоке 14 памяти по младшим адресам массивами записаны значения выходных управляющих кодов, адрес начального элемента каждого массива определяется кодом входного задания плюс "единица", размерность каждого массива допускается переменной (это соответствует переменной длине последовательности выходных управляющих кодов). Старшее адресное пространство блока 14 памяти используется для оперативного запоминания текущей информации устройства.

Микропрограммный автомат 15 внутреннего управления может реализовать блок-схему алгоритма, представленную на фиг. 2, различными съемными средствами. Ряд вариантов структур внутреннего автомата 15 управления представлен на фиг. 3-6.

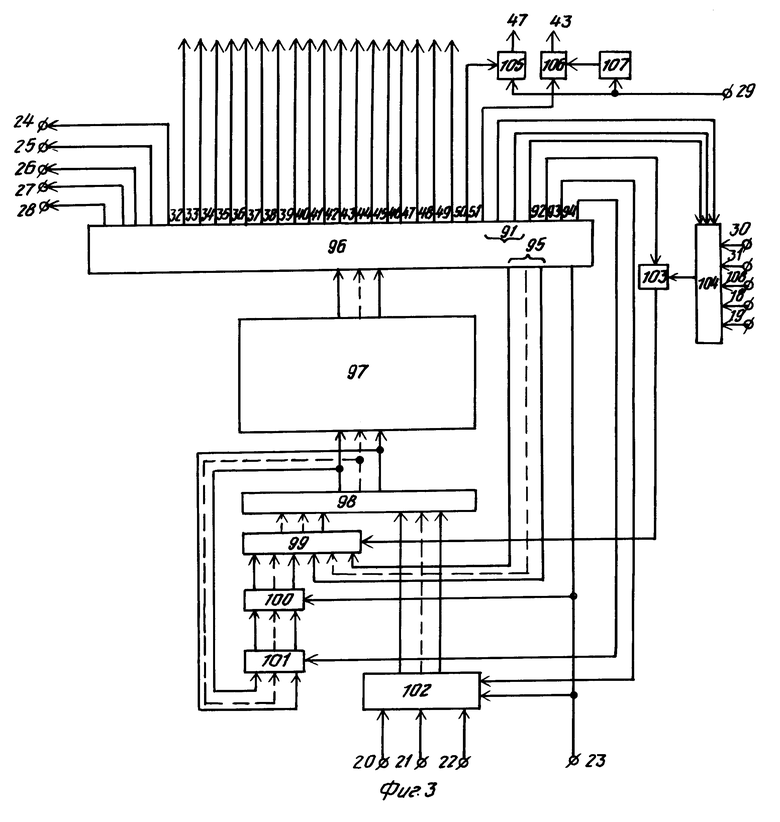

На фиг. 3 представлен автомат микропрограммного типа с естественным следованием микрокоманд, безусловными, условными переходами и ветвлением. Он содержит регистр 96 микрокоманд, блок 97 памяти микрокоманд, группу 98 элементов ИЛИ, мультиплексор 99 адреса, регистр 100 адреса микрокоманд, сумматор ("+1") 101, регистр 102 условий, элементы И 103, 105, 106, мультиплексор 104 условий, элемент НЕ 107, вход 108 логической "1", микроприказы 91 управления мультиплексором 104, 92 выбора источника адреса микрокоманд, 93 чтения кода регистра 102 условий, 94 "+1" к коду адреса предыдущей микрокоманды, 95 поле адреса безусловного перехода.

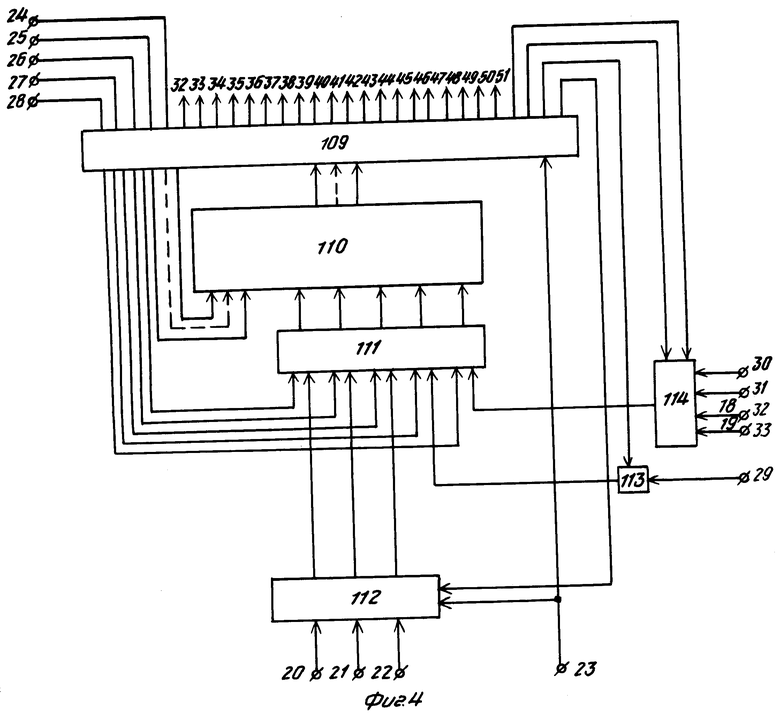

На фиг. 4 представлен автомат микропрограммного типа с безусловными переходами и ветвлением. Он содержит регистр 109 микрокоманд, блок 110 памяти микрокоманд, группу 111 элементов ИЛИ, регистр 112 условий, элемент И 113, мультиплексор 114 условий.

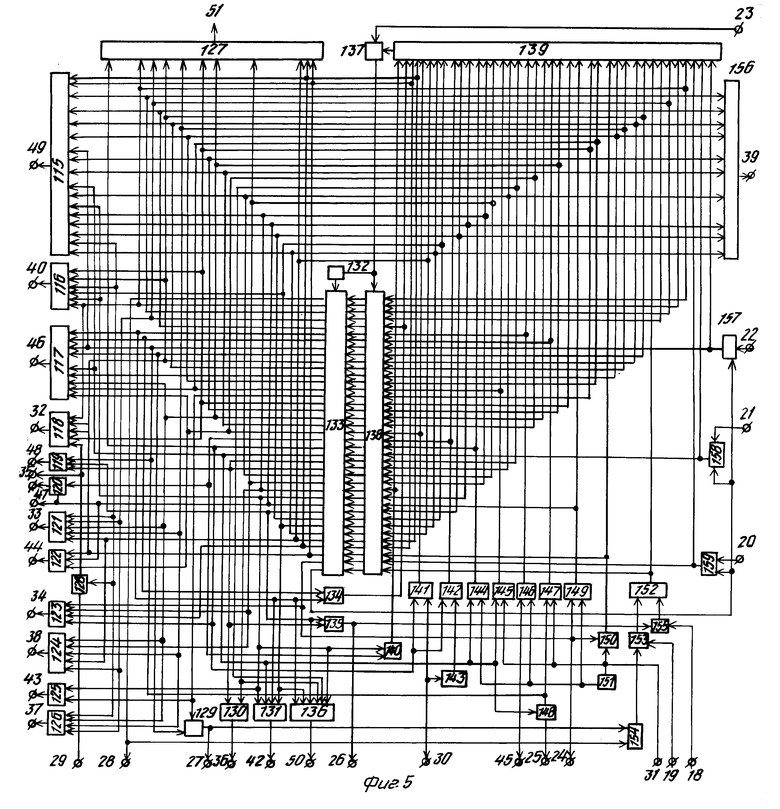

На фиг. 5 представлен автомат регистрового типа, который содержит элементы ИЛИ 115-127, 129-131, 134-136, 139, 140, 148, 152, 154, 156, элементы И 128, 137, 141, 142, 144-147, 149, 150, 153, 155, 157-159, элементы НЕ 132, 143, 151, регистры 133, 138.

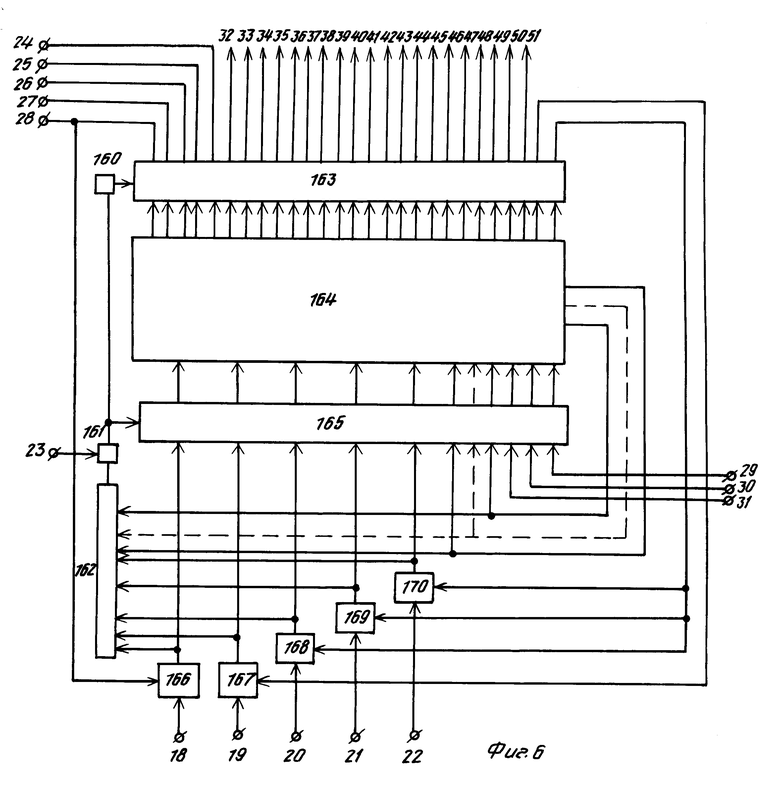

На фиг. 6 представлен автомат микропрограммного типа с безусловными и условными переходами. Он содержит элемент НЕ 160, элемент И 161, элемент ИЛИ 162, регистр 163, блок 164 памяти микрокоманд, регистр 165, элементы И 166-170.

Рассмотрим работу устройства в соответствии с блок-схемой алгоритма, представленной на фиг. 2. В начальном состоянии (при выполнении микрокоманды 52) устройство может находится сколь угодно долго, ожидая появления одного из инициативных сигналов логических условий с входа 20, 21 или 22. Микрокоманда 52 содержит для реализации автомата 15 в соответствии с функциональной схемой, представленной на фиг. 3, "нулевой" код поля 95 адреса регистра 96, "единичные" микроприказы 93, 94, остальные микроприказы пассивные.

До появления сигнала с входа 20, 21 или 22 "нулевой" выходной сигнал элемента И 103 подключает через мультиплексор 99 к входам элементов ИЛИ 98 код ("нулевой") поля 95 микрокоманды 52, и каждый тактовый сигнал с входа 23 записывает в регистр 96 микрокоманду 52, а в регистр 100 код 0 01 (на "единицу" младшего разряда больший выходного кода группы 98 элементов ИЛИ). Логическое условие с входа 20, 21 или 22 передним фронтом тактового сигнала записывается в регистр 102, одновременно с этим повторяется запись (в регистр 96) микрокоманды 52. Передний фронт следующего тактового сигнала записывает в регистр 96 микрокоманду, определяемую кодом условия, а в регистр 100 код, на "единицу" больший кода регистра 102. Пусть, например, условия закреплены за регистром 102 следующим образом: 22 младший разряд (первый), 21 средний (третий), 20 старший (четвертый). Тем самым выполняется ветвление по коду регистра 102 в зависимости от кода регистра 102 может быть осуществлен переход к одной из микрокоманд 53, 68, 83.

Микрокоманда 52 содержит для реализации автомата 15 в соответствии с функциональной схемой, представленной на фиг. 4, код 0 011 поля адреса регистра 109, подключенного к первым входам элементов ИЛИ 111, и "единичный" микроприказ чтения регистра 112, остальные микроприказы пассивные. До появления сигнала с входа 20, 21 или 22 код адреса блока 110 памяти остается равным 0 011 два младших разряда поля адреса маскируют выходы элемента И 113 и мультиплексора 114, обеспечивая ветвление по коду регистра 112 независимо от сигналов условий на входах 18, 19, 20-31.

Для реализации автомата 15 в соответствии с функциональной схемой, представленной на фиг. 5, микрокоманде 52 соответствует первое состояние регистров 133, 138, формирующее только сигнал на первых входах элементов И 157-159. С приходом одного из условий на вход 20, 21 или 22 осуществляется переход в соответствующее состояние регистров 133, 138.

Для реализации автомата 15 в соответствии с функциональной схемой, представленной на фиг. 6, микрокоманда 52 содержит "единицу" только в разряде, подключенном к первым входам элементов И 168-170. После прихода одного из сигналов на вход 20, 21 или 22 осуществляется переход к соответствующей микрокоманде 53, 68 или 83.

Сигнал, приходящий на вход 20, сопровождает задание, поступающее на входы-выходы 17, и переводит устройство из состояния выполнения микрокоманды 52 к микрокоманде 53. При выполнении микрокоманды 53 на соответствующем выходе устройства формируется сигнал 24 подтверждения приема задания с входов-выходов 17, микроприказы 49, 33, 34 управляют записью кода задания в регистр адреса блока 14 памяти, в регистр 9 и в счетчик 11, микроприказ 37 управляет записью признака режима с входа-выхода 16 в триггер 5, микроприказ 40 уменьшает на "единицу" код счетчика 12 (в начальном состоянии счетчик в "нуле"), микроприказ 46 управляет записью кода регистра 10 в счетчик 13 (при этом микроприказ 48 управляет подключением выходов регистра 10 к входам счетчика 13 через мультиплексор 8). Пусть, например, в исходном состоянии регистр 10 содержит "нулевой" код, кроме того, микрокоманда 53 анализирует состояние триггера 5 режима.

Для реализации автомата 15 в соответствии с функциональной схемой, представленной на фиг. 3, "единичный" выход 31 триггера 5 через мультиплексор 104 поступает на второй вход элемента И 103, на первом входе которого установлен "единичный" микроприказ 92. С выхода элемента И 103 значение признака режима управляет мультиплексором 99, определяя источник адреса следующей микрокоманды.

Для реализации автомата 15 в соответствии с функциональной схемой, представленной на фиг. 4, "единичный" выход 31 триггера 5 через мультиплексор 114 поступает на второй вход элемента ИЛИ младшего разряда группы 111 элементов ИЛИ, на первый вход которого с соответствующего выхода регистра 109 подается "нулевое" значение младшего бита адреса. Таким образом, в зависимости от значения признака режима устанавливается четный или нечетный адрес следующей микрокоманды.

Для реализации автомата 15 в соответствии с функциональной схемой, представленной на фиг. 5, сигнал "единичного" выхода разряда регистра 103, соответствующего микрокоманде 53, в зависимости от значения признака режима 31 проходит через элемент И 149 или 150, определяя следующее состояние регистра 138 и затем регистра 133.

Для реализации автомата 15 в соответствии с функциональной схемой, представленной на фиг. 6, значение сигнала "единичного" выхода 31 триггера 5 определяет значение одного разряда регистра 165 и тем самым тот или иной код следующей микрокоманды.

В зависимости от значения признака режима осуществляется переход к микрокоманде 54 ("нулевой" режим) или 61 ("единичный" режим). При выполнении микрокоманды 54 микроприказ 35 увеличивает на единицу код счетчика 11, микроприказ 47 увеличивает на единицу код счетчика 13, микроприказ 44 устанавливает в "ноль" триггер 7, микроприказ 39 управляет подключением выходов счетчика 12 через группу 3 элементов И к входам-выходам 17, а микроприказ 49 управляет записью этого кода в регистр адреса блока 14. Адрес следующей микрокоманды 55 формируется безусловно, например, для структуры автомата 15 в соответствии с фиг. 3 по коду регистра 100 или, например, по коду адресного поля 95 микрокоманды 54. В последнем случае микрокоманда 54 содержит "единичный" микроприказ 92 и код (010) поля 91, определяющий выбор логической "1" вход 108 мультиплексора 104. Передний фронт очередного тактового сигнала записывает в регистр 96 код микрокоманды 55 и в регистр 100 код адреса следующей микрокоманды 56 (адрес микрокоманды 55, увеличенный в сумматоре 101 на единицу).

При выполнении микрокоманды 55 микроприказ 43 управляет записью кода счетчика 13 в регистр 10, микроприказ 40 уменьшает на единицу код счетчика 12, микроприказ 42 управляет передачей содержимого счетчика 13 на входы-выходы 17, микроприказ 50 управляет записью кода входов-выходов 17 в блок 14 памяти по адресу, записанному предыдущей микрокомандой 54 в регистр адреса этого блока 14 памяти, а микроприказ 49 управляет записью кода входов-выходов 17 в регистр адреса блока 14 памяти. При выполнении микрокоманды 56 микроприказ 36 разрешает подключение через группу 2 элементов И выходного кода счетчика 11 к входам-выходам 17, 16, а микроприказы 50 и 49 управляют записью этого кода в блок 14 памяти (по адресу, установленному микрокомандой 55) и в регистр адреса блока 14 памяти. При выполнении микрокоманды 57 микроприказ 51 управляет чтением содержимого ячейки блока 14 памяти, адрес которой записан предыдущей микрокомандой 56, микроприказ 34 управляет записью этого кода (М разрядов) в счетчик 11, а микроприказ 38 бита (М + 1)-го в триггер 6. При выполнении микрокоманды 58 код счетчика 12 передается под управлением микроприказа 39 через группу 3 элементов И на входы-выходы 17, а микроприказ 49 управляет записью этого кода в регистр адреса блока 14 памяти. При выполнении микрокоманды 59 микроприказ 32 разрешает подключение через группу 1 элементов И выходов (М-разрядных) регистра 9 и "единичных" выходов триггеров 5 и 6 к входам-выходам блока 14 памяти, а микроприказ 50 управляет записью этого кода в ячейку блока 14 памяти по ранее принятому адресу. При выполнении микрокоманды 60 микроприказ 36 подключает через группу 2 элементов И выходы счетчика 11 и выход триггера 5 соответственно к входам-выходам 17 (тем самым формируется выходной управляющий код) и к входу-выходу 16 (признак режима), а также на выходе 26 признак выдачи операции. Кроме того, микрокоманда 60 определяет значения сигнала на входе 18 устройства. До тех пор, пока этот сигнал не станет "единичным", устройство находится в состоянии выполнения микрокоманды 60. Если на входе 18 установлен "единичный" сигнал, то осуществляется возврат к микрокоманде 52. Устройство опять ожидает поступления одного из инициативных сигналов (с входа 20, 21 или 22).

Если опять приходит (при "нулевом" признаке режима на входе 16) сигнал на вход 20 (сопровождая новое задание, вложенное в предыдущее), то устройство опять выполняет микропрограмму 53-60, работая аналогично описанному за исключением того, что при выполнении микрокоманды 53 микроприказ 46 не изменяет содержимое счетчика 13 (не переписывает в него код регистра 10), так как триггер 7 находится в "нулевом" состоянии (он установлен в "ноль" микрокомандой 54 в предыдущем цикле выполнения микропрограммы 53-60).

Новые задания могут поступать произвольное число раз, их количество ограничено только разрядностью соответствующих регистров 9, 10 и счетчиков 11, 12, 13 и объемом блока 14 памяти.

В случае "единичного" режима после микрокоманды 53 осуществляется переход к микрокоманде 61. При ее выполнении микроприказ 51 управляет чтением ячейки блока 14 памяти, адрес которой определен предыдущей микрокомандой 53, микроприказ 49 управляет записью считанной информации в регистр адреса блока 14 памяти, микроприказ 48 подключает через мультиплексор 8 выходы блока 14 памяти к входам счетчика 13, а микроприказ 46 управляет записью считанной информации в счетчик 13. Кроме того, микроприказ 44 устанавливает в "ноль" триггер 7. При выполнении микрокоманды 62 микроприказ 51 управляет чтением информации с блока 14 памяти, микроприказ 34 управляет записью считанной информации в счетчик 11, а микроприказ 49 управляет записью считанного кода в регистр адрес блока 14 памяти. При выполнении микрокоманды 63 микроприказ 51 управляет чтением содержимого ячейки блока 14 памяти, адрес которой определен микрокомандой 62, а микроприказы 33 и 38 управляют записью считанного кода соответственно в регистр 9 (М разрядов) и в триггер 6 (признак последнего кода). При выполнении микрокоманды 64 микроприказ 39 открывает группу 3 элементов И, подключая выходы счетчика 12 к входам-выходам 17, а микроприказ 49 управляет записью этого кода в регистр адреса блока 14 памяти. При выполнении микрокоманды 65 микроприказ 42 подключает выходы счетчика 13 к входам-выходам 17, микроприказ 50 управляет записью кода счетчика 13 в ячейку блока 14 памяти, адрес которой определен предыдущей микрокомандой, а микроприказ 40 уменьшает на единицу код счетчика 12. При выполнении микрокоманды 66 микроприказ 39 подключает через группу 3 элементов И выходы счетчика 12 к входам-выходам 17, микроприказ 49 управляет записью кода счетчика 12 в регистр адреса блока 14 памяти. При выполнении микрокоманды 67 микроприказ 32 открывает группу 1 элементов И, подключая выходы регистра 9 к входам-выходам 17 устройства (тем самым формируя выходной М-разрядный управляющий код), триггера 5 к входу-выходу 16 (формируя выходной признак режима) и триггера 6 к (М + 1)-му входу-выходу блока 14 памяти. Микроприказ 50 управляет записью кода регистра 9 и триггеров 5 и 6 в ячейку памяти блока 14 по адресу, определенному предыдущей микрокомандой, микроприказ 26 формирует на соответствующем выходе устройства признак выдачи операции. Микрокоманда 67 удерживается (аналогично описанному для микрокоманды 60) на выходе автомата 15 сколько угодно долго до прихода сигнала на вход 18, после чего устройство возвращается к выполнению микрокоманды 52.

Сигнал, приходящий на вход 21 (аналогично сигналу с входа 20), переводит устройство в состояние выполнения микрокоманды 68. При выполнении микрокоманды 68 на соответствующем выходе устройства формируется сигнал 25 индикации приема признаков выдачи операции, микроприказ 41 увеличивает на единицу код счетчика 12, микроприказ 42 открывает группу 4 элементов И, подключая выходы счетчика 13 к входам-выходам 17 устройства, а микроприказ 49 управляет записью этого кода в регистр адреса блока 14 памяти. Кроме того, микрокоманда 68 (аналогично микрокоманде 53) выполняет анализ состояния триггера 5. В зависимости от значения режима осуществляется переход к микрокоманде 69 ("нулевой" режим) или 77 ("единичный" режим).

В случае "нулевого" режима автомат 15 формирует код микрокоманды 69. При выполнении микрокоманды 69 микроприказ 51 управляет чтением ячейки блока 14 памяти, а микроприказ 34 записью этого кода в счетчик 11. Кроме того, при выполнении микрокоманды 69 анализируется состояние триггера 6. Если триггер 6 находится в "нулевом" состоянии (это означает, что предыдущий выходной управляющий код не был последним), то осуществляется переход к микрокоманде 70. Если триггер 6 находится в "единичном" состоянии (это означает, что предыдущий выходной управляющий код был последним), то осуществляется переход к микрокоманде 71. При выполнении микрокоманды 70 микроприказ 35 увеличивает код счетчика 11 на единицу, микроприказ 40 уменьшает на единицу код счетчика 12. После этого осуществляется безусловный переход к микрокоманде 56 и затем устройство работает аналогично описанному, формируя очередной выходной управляющий код.

При выполнении микрокоманды 71 микроприказ 41 увеличивает на единицу код счетчика 12, микроприказ 44 устанавливает в "ноль" триггер 7. При выполнении микрокоманды 72 микроприказ 39 открывает группу 3 элементов И, подключая выходы счетчика 12 к входам-выходам 17, а микроприказ 49 управляет записью этого кода счетчика 12 в регистр адреса блока 14 памяти. При выполнении микрокоманды 73 микроприказ 41 увеличивает на единицу код счетчика 12, микроприказ 51 управляет чтением содержимого ячейки блока 14 памяти, адрес которой был сформирован и записан предыдущей микрокомандой, микроприказ 33 управляет записью считанного кода с входов-выходов 17 в регистр 9, микроприказы 37 и 38 записывают значения соответствующих признаков в триггеры 5 и 6. При выполнении микрокоманды 74 микроприказ 39 открывает группу 3 элементов И, подключая выходы счетчика 12 к входам-выходам 17, а микроприказ 49 управляет записью этого кода в регистр адреса блока 14 памяти. При выполнении микрокоманды 75 микроприказ 48 подключает выходы блока 14 памяти через мультиплексор 8 к входам счетчика 13, микроприказ 51 управляет чтением информации из блока 14 памяти, микроприказ 46 управляет записью считанного кода в счетчик 13, а микроприказ 40 уменьшает на единицу код счетчика 12. При выполнении микрокоманды 76 микроприказ 27 формирует на соответствующем выходе устройства признак правильного завершения цикла управления, микроприказ 43 управляет записью кода счетчика 13 в регистр 10. Устройство анализирует значения сигнала на выходе 19 устройства. До тех пор, пока этот сигнал не станет "единичным", устройство находится в состоянии выполнения микрокоманды 76. Если на входе 19 установлен "единичный" сигнал, то осуществляется возврат к микрокоманде 52. Устройство опять ожидает поступления одного из инициативных сигналов (с входа 20, 21 или 22).

В случае "единичного" режима осуществляется переход к микрокоманде 77, при выполнении которой микроприказ 41 увеличивает на единицу код счетчика 12. При выполнении микрокоманды 78 микроприказ 39 подключает выходы счетчика 12 к входам-выходам 17, микроприказ 49 записывает этот код в регистр адреса блока 14 памяти. При выполнении микрокоманды 79 микроприказ 41 увеличивает код счетчика 12 на единицу, микроприказ 51 управляет чтением информации из блока 14 памяти, а микроприказы 33, 37 и 38 ее записью соответственно в регистр 9 и триггеры 5 и 6. Пpи выполнении микрокоманды 80 микроприказы 39 и 49 управляют записью кода счетчика 12 в регистр адреса блока 14 памяти. При выполнении микрокоманды 81 микроприказ 40 уменьшает код счетчика 12 на единицу, микроприказ 46, 48 и 51 управляют записью в счетчик 13 кода, считанного из блока 14 памяти по адресу, установленному предыдущей микрокомандой. При выполнении микрокоманды 82 микроприказ 27 формирует на соответствующем выходе устройства признак правильного завершения цикла управления и устройство ожидает прихода сигнала на вход 19, после чего возвращается в начальное состояние 52.

Сигнал, приходящий на вход 22, переводит устройство в состояние выполнения микрокоманды 83. При выполнении микрокоманды 83 микроприказ 25 формирует на соответствующем выходе сигнал индикации приема признаков выдачи операции, микроприказ 45 устанавливает триггер 7 в "единицу", микроприказ 41 увеличивает на единицу код счетчика 12, а микроприказы 32 и 49 управляют записью кода регистра 9 и регистр адреса блока 14 памяти. Кроме того, микрокоманда 83 (аналогично микрокоманде 53) выполняет анализ состояния триггера 5. В зависимости от значения режима осуществляется переход к микрокоманде 84 ("единичный" режим) или 86 ("нулевой" режим).

В случае "нулевого" режима устройство переходит к микрокоманде 85, при выполнении которой микроприказ 42 открывает группу 4 элементов И, подключая выходы счетчика 13 к входам-выходам 17, микроприказ 50 управляет записью этого кода в блок 14 памяти, микроприказ 41 увеличивает код счетчика 12 на единицу. При выполнении микрокоманды 86 микроприказ 39 подключает выходы счетчика 12 через группу 3 элементов И к входам-выходам 17, а микроприказ 49 управляет записью этого кода в регистр адреса блока 14 памяти. При выполнении микрокоманды 87 микроприказ 42 увеличивает на единицу код счетчика 12, микроприказ 51 управляет чтением из блока 14 памяти содержимого ячейки, адрес которой определен предыдущей микрокомандой, микроприказ 33 управляет записью этого кода (М-разрядного) в регистр 9, а микроприказы 37 и 38 (М + 1)-го и (М + 2)-го в триггеры 5 и 6. При выполнении микрокоманды 88 микроприказ 39 открывает группу 3 элементов И, подключая выходы счетчика 12 к входам-выходам 17, а микроприказ 49 управляет записью этого кода в регистр адреса блока 14 памяти. При выполнении микрокоманды 89 микроприказ 40 вычитает единицу из кода счетчика 12, микроприказ 51 управляет чтением информации из блока 14 памяти, микроприказ 48 подключает выходы блока 14 памяти через мультиплексор 8 к входам счетчика 13, а микроприказ 46 управляет записью этого кода в счетчик 13. При выполнении микрокоманды 90 микроприказ 28 формирует на соответствующем выходе устройства признак неправильного завершения цикла управления. В состоянии выполнения микрокоманды 90 устройство может находиться сколь угодно долго до прихода сигнала на вход 19, после чего устройство аналогично описанному возвращается в начальное состояние 52.

В случае "единичного" признака режима устройство переходит к микрокоманде 84, при выполнении которой микроприказ 41 увеличивает на единицу код счетчика 12. По окончании микрокоманды 84 осуществляется переход к выполнению микрокоманды 86, и в дальнейшем устройство работает аналогично описанному.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042190C1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042188C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046395C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2049347C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046396C1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| Устройство микропрограммного управления | 1990 |

|

SU1815636A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении систем управления и в составе сложных систем управления ЭВМ различных классов. Целью изобретения является повышение достоверности функционирования за счет запоминания состояний устройства при сбое и возвратов к ошибочно выполненным командам для многократно вложенных последовательностей команд. Устройство содержит три триггера, четыре группы элементов И, два регистра, три счетчика, мультиплексор, блок памяти и микропрограммный автомат внутреннего управления. На каждый код входной информации (задания) устройство формирует последовательность выходных управляющих кодов. Устройство воспринимает и обрабатывает многократно вложенные задания, придерживаясь скобочной дисциплины. В режиме управления устройство идентифицирует и запоминает сбойное состояние управления, в режиме анализа восстанавливает сбойное состояние управления. Устройство обменивается информацией с устройством управления верхнего уровня и управляет исполнительным устройством в асинхронном режиме в принятом стандарте сопряжения. Отличительными особенностями структуры устройства являются использование одного блока памяти для хранения информации различного вида. 6 ил.

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее три группы элементов И, триггер признака последнего кода, триггер режима, регистр информации, счетчик индекса, блок памяти информации и микропрограммный автомат внутреннего управления, причем K-й разряд информационного входа-выхода блока памяти информации подключен соответственно к K-му разряду входа-выхода управляющей информации устройства, K-му разряду информационного входа регистра информации и выходу K-го элемента И первой группы (  где M разрядность входа-выхода управляющей информации устройства), (M + 1)-й информационный вход-выход блока памяти информации подключен к информационному входу триггера признака последнего кода, первый вход K-го элемента И первой группы подключен к выходу K-го разряда счетчика индекса, информационный вход триггера режима подключен к входу-выходу логического условия режима восстановления ошибочной команды устройства, тактовый вход и выходы логических условий с первого по седьмой микропрограммного автомата внутреннего управления подключены соответственно к тактовому входу устройства, к выходам триггера режима и триггера признака последнего кода, к входам логических условий подтверждения выдачи операции, подтверждения завершения цикла, приема кода операции, требования выдачи операции, запрета выдачи операции устройства, выходы с первого по четырнадцатый микропрограммного автомата внутреннего управления подключены соответственно к входу записи регистра информации, выходам "+1" и "Запись" счетчика индекса, к синхровходам триггеров режима и признака последнего кода, входу записи данных блока памяти информации, вторым входам элементов И первой, второй и третьей групп и выходам индикации приема признаков выдачи операции, индикации приема кода операции, индикации правильного завершения цикла управления, индикация неправильного завершения цикла управления и индикации выдачи операции устройства, отличающееся тем, что, с целью повышения достоверности функционирования за счет запоминания состояний устройства при сбое и возвратов к ошибочно выполненным командам для многократно вложенных последовательностей команд, в него введены триггер записи, четвертая группа элементов И, счетчик магазина, счетчик базы, регистр вершины магазина, мультиплексор информации, причем K-й разряд информационного входа-выхода блока памяти информации подключен к K-м разрядам информационного входа счетчика индекса и первого информационного входа мультиплексора информации, к выходам K-х элементов И второй, третьей и четвертой групп, (M + 1)-й разряд информационного входа-выхода блока памяти информации подключен к выходу (M + 1)-го элемента И второй группы, первый вход которого подключен к выходу триггера признака последнего кода, (M + 2)-й разряд информационного входа-выхода блока памяти информации подключен к входу-выходу логического условия режима восстановления ошибочной команды устройства, к выходам (M + 2)-го элемента И второй группы и (M + 1)-го элемента И первой группы, первые входы которых подключены к выходу триггера режима, первый вход K-го элемента И второй группы подключен к выходу K-го разряда регистра информации, выходы счетчика магазина подключены к первым входам элементов И третьей группы, выходы счетчика базы подключены к первым входам элементов И четвертой группы и информационным входам регистра вершины магазина, выходы которого подключены к второму информационному входу мультиплексора информации, выходы которого подключены к информационным входам счетчика базы, восьмой вход логических условий микропрограммного автомата внутреннего управления подключен к выходу триггера записи, выходы с пятнадцатого по двадцать шестой микропрограммного автомата внутреннего управления подключены соответственно к входам "+1" и "-1" счетчика магазина, вторым входам элементов И четвертой группы, входу записи регистра вершины магазина, к входам установки в "0" и в "1" триггера записи, входам "+1" и "Запись" счетчика базы, к управляющему входу мультиплексора информации и входам записи адреса и чтения блока памяти информации.

где M разрядность входа-выхода управляющей информации устройства), (M + 1)-й информационный вход-выход блока памяти информации подключен к информационному входу триггера признака последнего кода, первый вход K-го элемента И первой группы подключен к выходу K-го разряда счетчика индекса, информационный вход триггера режима подключен к входу-выходу логического условия режима восстановления ошибочной команды устройства, тактовый вход и выходы логических условий с первого по седьмой микропрограммного автомата внутреннего управления подключены соответственно к тактовому входу устройства, к выходам триггера режима и триггера признака последнего кода, к входам логических условий подтверждения выдачи операции, подтверждения завершения цикла, приема кода операции, требования выдачи операции, запрета выдачи операции устройства, выходы с первого по четырнадцатый микропрограммного автомата внутреннего управления подключены соответственно к входу записи регистра информации, выходам "+1" и "Запись" счетчика индекса, к синхровходам триггеров режима и признака последнего кода, входу записи данных блока памяти информации, вторым входам элементов И первой, второй и третьей групп и выходам индикации приема признаков выдачи операции, индикации приема кода операции, индикации правильного завершения цикла управления, индикация неправильного завершения цикла управления и индикации выдачи операции устройства, отличающееся тем, что, с целью повышения достоверности функционирования за счет запоминания состояний устройства при сбое и возвратов к ошибочно выполненным командам для многократно вложенных последовательностей команд, в него введены триггер записи, четвертая группа элементов И, счетчик магазина, счетчик базы, регистр вершины магазина, мультиплексор информации, причем K-й разряд информационного входа-выхода блока памяти информации подключен к K-м разрядам информационного входа счетчика индекса и первого информационного входа мультиплексора информации, к выходам K-х элементов И второй, третьей и четвертой групп, (M + 1)-й разряд информационного входа-выхода блока памяти информации подключен к выходу (M + 1)-го элемента И второй группы, первый вход которого подключен к выходу триггера признака последнего кода, (M + 2)-й разряд информационного входа-выхода блока памяти информации подключен к входу-выходу логического условия режима восстановления ошибочной команды устройства, к выходам (M + 2)-го элемента И второй группы и (M + 1)-го элемента И первой группы, первые входы которых подключены к выходу триггера режима, первый вход K-го элемента И второй группы подключен к выходу K-го разряда регистра информации, выходы счетчика магазина подключены к первым входам элементов И третьей группы, выходы счетчика базы подключены к первым входам элементов И четвертой группы и информационным входам регистра вершины магазина, выходы которого подключены к второму информационному входу мультиплексора информации, выходы которого подключены к информационным входам счетчика базы, восьмой вход логических условий микропрограммного автомата внутреннего управления подключен к выходу триггера записи, выходы с пятнадцатого по двадцать шестой микропрограммного автомата внутреннего управления подключены соответственно к входам "+1" и "-1" счетчика магазина, вторым входам элементов И четвертой группы, входу записи регистра вершины магазина, к входам установки в "0" и в "1" триггера записи, входам "+1" и "Запись" счетчика базы, к управляющему входу мультиплексора информации и входам записи адреса и чтения блока памяти информации.

| Авторское свидетельство СССР N 1424551, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-08-20—Публикация

1991-10-08—Подача