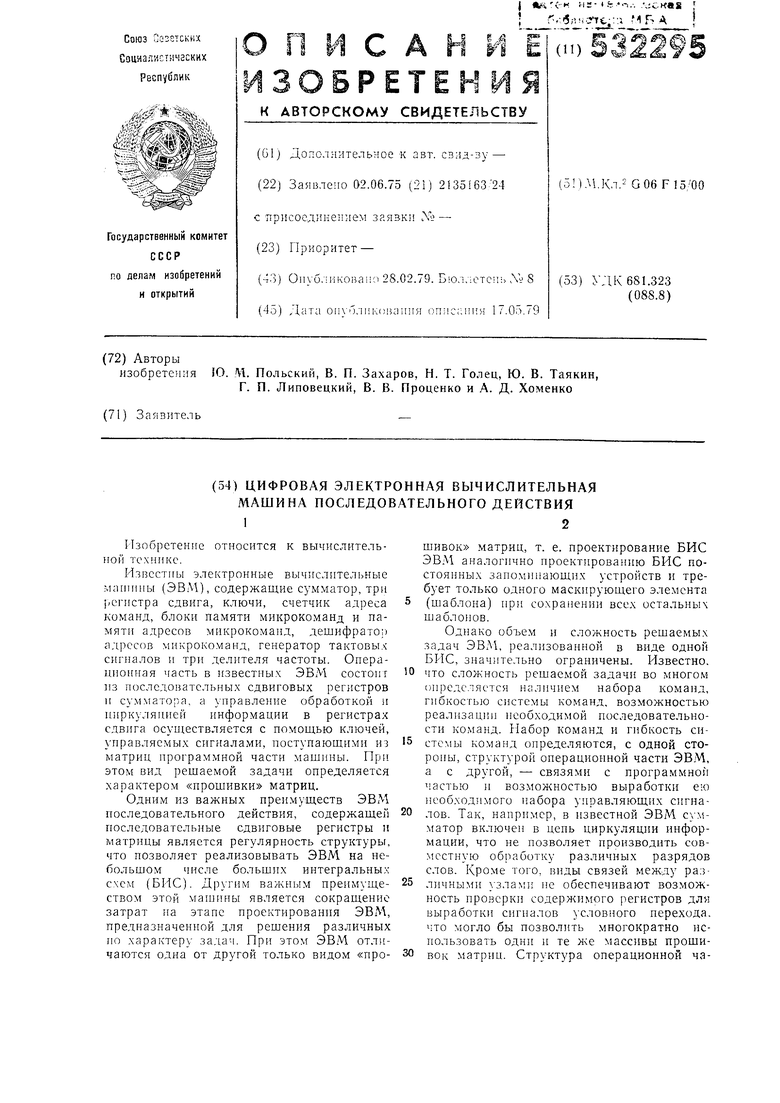

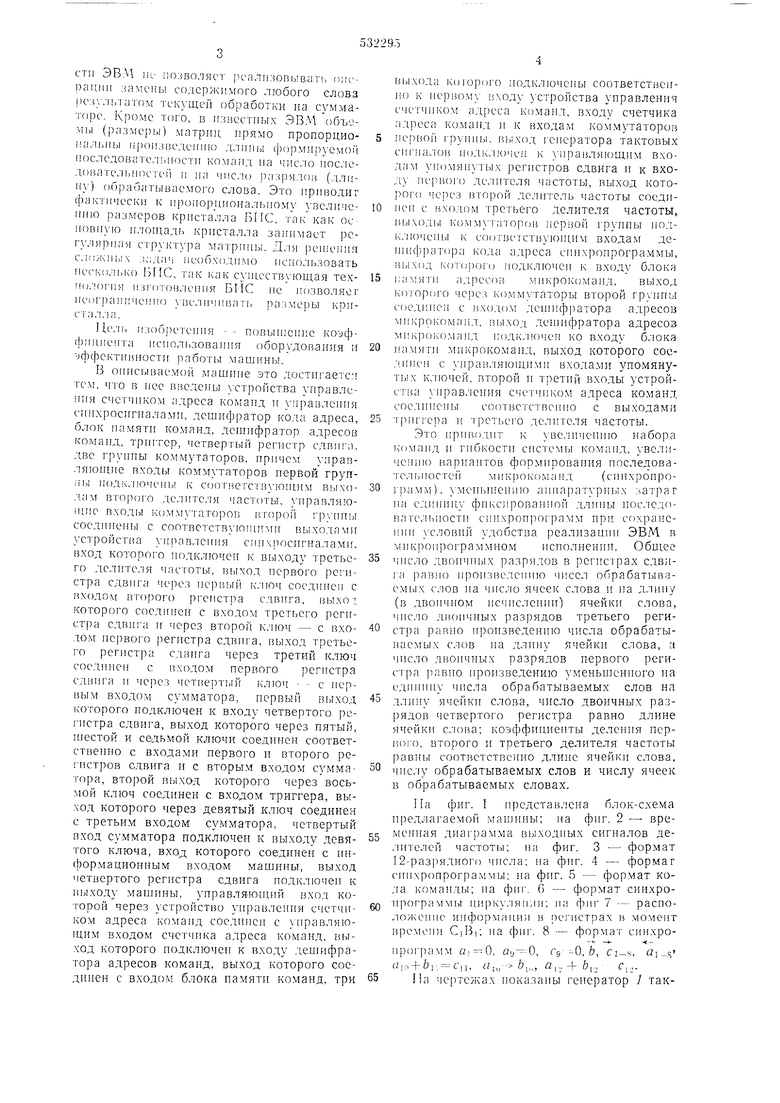

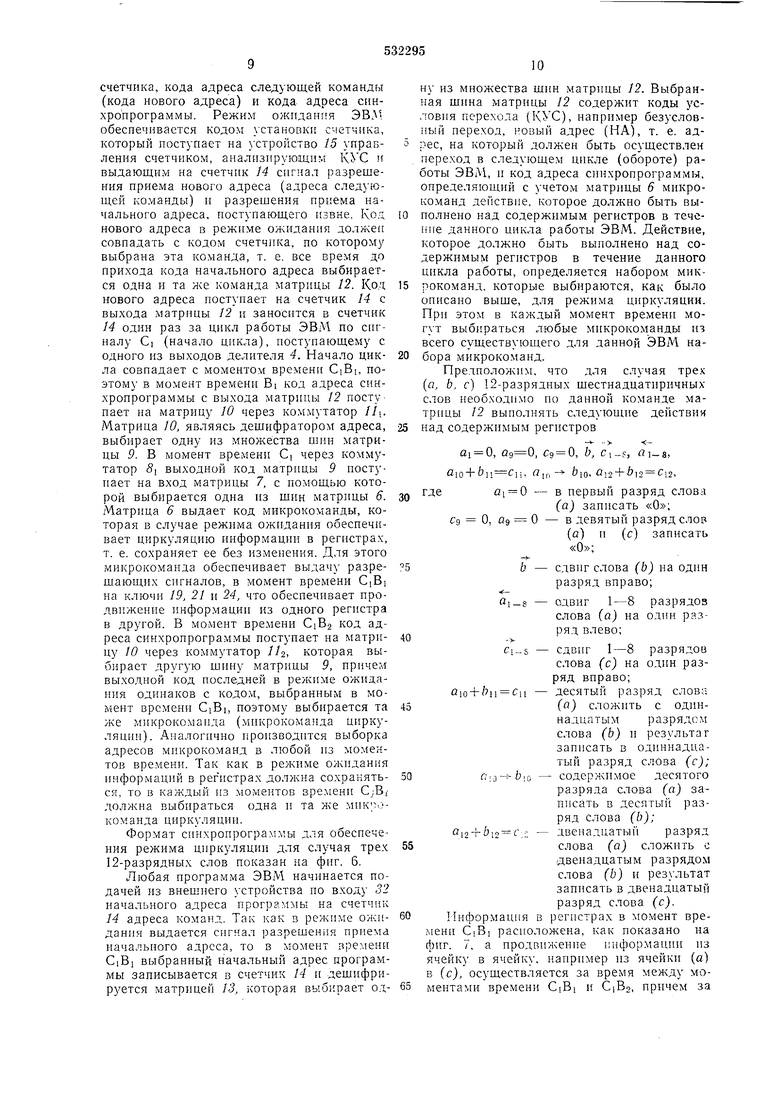

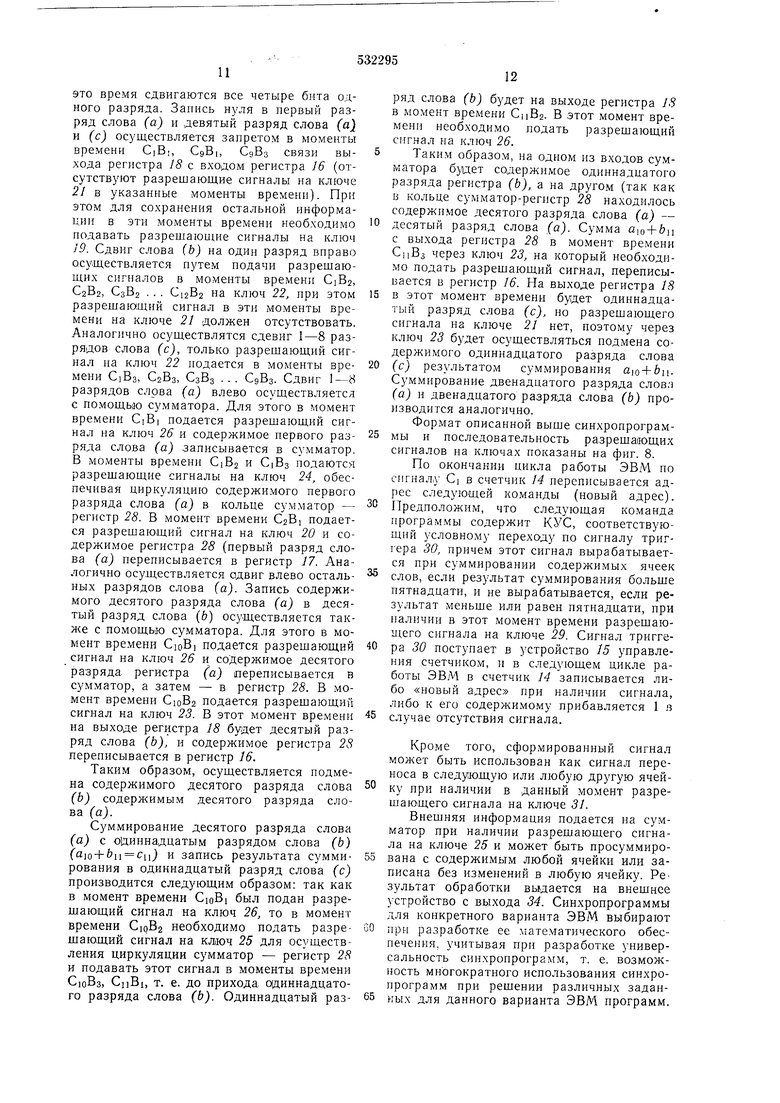

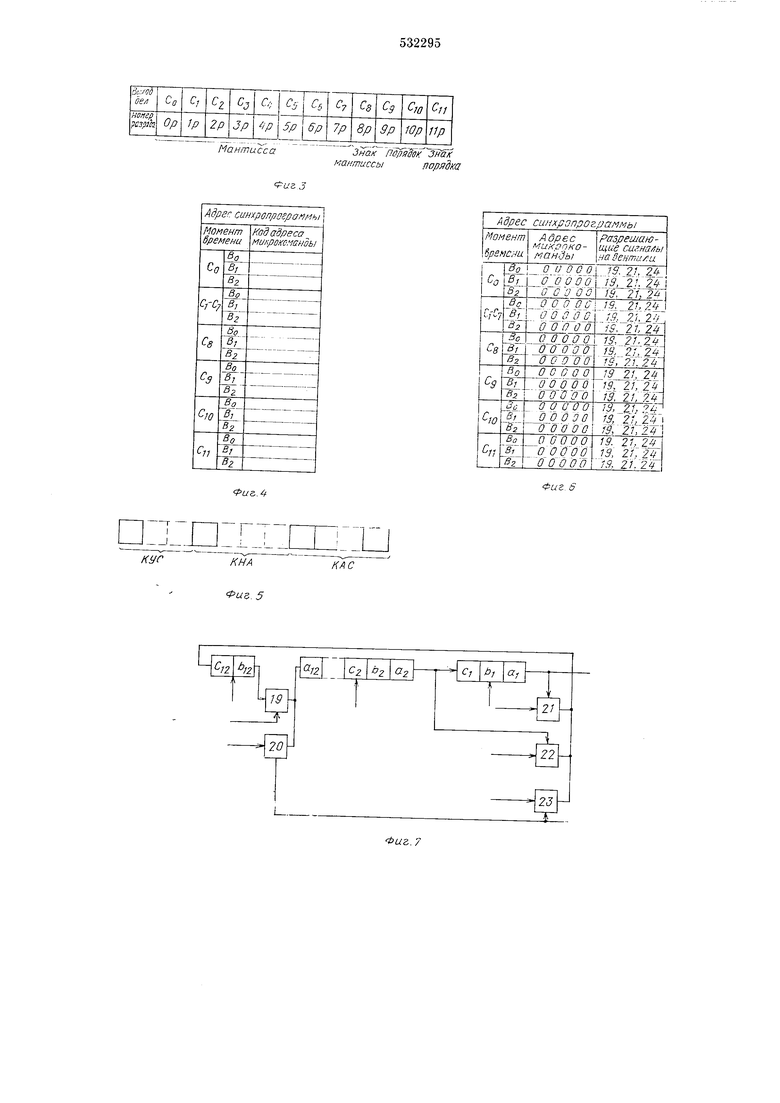

сти ЭВМ ПС- позволяет реализовывать опе рации замены содер 1 и гого любого слова |)ез льтатом текущей обработки на сумматоре. Кроме того, в извеетпых ЭВМ объемы (размеры) матриц прямо пропорциопа.тьиы произведсиию .тлииы (|)ормируемО 1 последовательности кодганд на число иоследовательиоете1 | и иа число разрядов (дли1 у) обрабатываемого слова. Это пршшдиг фактически к ироиорционалыю.му увеличению размеров кристалла БИС, так как основную илогцадь кристалла занимает регулярная структура матрнны. Для сл ; 1-:1П,1 задач необ.ходимо нсно:Н)ЗОвать нес -:олько БИС, так как сунюствующая те.хнология изгосов.тення БПС не нозволяег неограниченно у кличиват|, ра.з.меры кристалла. Целг, нзоб|)етеиия -- повыи СИ 1е коэф(jjHiuieHTa иснолг зования оборудования и эффективности работы машннв. В оиисывас.мой машине это достигаетс.ч те.м, что в нее введсиы устройства управления счетчиком адреса команд и у цтавлеиия синхросигналами, дешифратор кода адреса, блок намяти команд, дешифратор адресов команд, тригтср, четвертый регистр сдвига, две груииы коммутаторов, ирнчсм управ.тяюии1е входы коммутаторов нервой групiibi и()Д:.почеиы к соответствхчоншм вьгход.ам )го делителя чаетоты, дфавляюHUie входвт ком.м)таторов BTOpoii соедииены с соответствуюнппги выходами устройства унравлеиия еинхросигналами. вход которого иодключеп к выходу третьего делителя чаетоты, в)Гход первого регистра сдвига через первый к.тюч сосдине с входом вто)ого ргеистра , вв1хо7. которого еоединен с входом третьего регнстра сдвига и через второй ключ - с входом первого регистра сдвига, выход т)етьего регистра сдвига через третий ключ соедииен с входом первого регистра едвпга и через четвертый ключ - - с первым входом сумматора, первый выхо.а которого подключен к входу четвертого регистра сдвига, выход которого через пятый, шестой и седьмой ключи соедипсн соответствешю с входами первого и второго регистров сдвига и с вторым входом сумматора, второй выход которого через восьмой ключ соединен с входом триггера, выход которого через девятый ключ соединен е третьим входом сумматора, четвертый вход сумматора подключен к выходу девятого ключа, вход которого соедине с пп(})ормационпым входом машины, выход четвертого регистра сдвига иодключеп к выходу .мап1ппы, унрав,тяюп1ПЙ вход которой через устройство ун)авлення счетчиком адреса комаид соедппеи е управляющим входом счетчика адреса команд, выход которого подключен к входу дешифратора адресов команд, выход которого соединен с входом блока памяти команд, три вьгхода которого подключены соответетвеиио к iicpiiOMy входу устройства управления счетчиком ад)еса команд, входу счетчика адреса команд и к входа.м коммутаторов ие)вон груииы. в,1ход геисратора тактовых си1налов иодключс.ч к управляющим входам уномяиутьгх регистров сдвига и к входу нс|М)0|-о делителя чаетоты, выход котор01Ч) через 1 торой делитель частоты соедииси с iixo.-u)M третьего делителя частоты, В1)Гход1)1 комм таторов нерной груипы иодк,|ючен)1 к соогве ствуюн1;им входам деишфратора кода адреса сипхропрограммы, (д KOTopoio нодключеи к входу блока памяти адресо;5 микрокомаид, выход которого через коммутаторы второй груипы соедииен с входом деишфратора адресов макрокоманд, ден1пфратора адресов ()К()манд подключен ко входу блока памяти микрокоманд, выход которого соедииеи с уиравляюи1,им1 входами упомянутых ключей, второй и третий входы устройства ч1равления счетчиком адреса команд соедииены соотвстствеиио с выходами триггера и третьего делителя частоты. Это прпво/тпт i; уве.тичещпо набора 1чомаид и гпбкостп спстемы команд, увеличению вариа1ггов формпрования последовател) посте ii микрокоманд (сппхропрограмм), умепьп1еиию аппаратурных затраг па СД1ПП И фикснроваппой длппы иоеледователыюсти сннхропрограмм нрн сохранеиии тловий удобства реализаппп ЭВМ в микропрограммпом псполненин. O6ni.ee число двопчгплх разрядов в регистрах сдви1а равно иропз1 еде1ппо чисел обрабатываемых слов иа число ячеек слова и па длииу (в двоичиом исчисленпп) ячейкп слова, чнсло двоичных разрядов третьего регистра равно иронзведению числа обрабатываемых слов на длину ячейки слова, а число двоичных разрядов первого регистра равпо произведению уменыпенного на едииииу числа обрабатываемых слов на дднну ячейки слова, число двоичных разрядов четвертого регистра равно длине ячейкп с;1ова; коэффппиепты деленпя первого, второго и третьего делителя частоты равны соответственно д,тине ячейки слова, числу обрабатываемых слов и числу ячеек в обрабатываемых словах. Иа фиг. 1 иредетавлена блок-схема предлагаемой ман1ины; иа фиг. 2 - временная диаг1)амма выходиых сигналов де.тителей частоты; па фиг. 3 - фор.мат 12-разрядного числа; па фиг. 4 - формат сппхр(шрограммы; на фпг. 5 - формат кода команды; на фиг. 6 - формат синхроирограммы иирк лянии; иа фи1 7 -- расположение ннформаиии в регистрах в .момент времени C.Bi; ))а фиг. 8 - формат сиихро- -ьч-. нрограмм 0; 0, , Сд 0, b, С;-, fli-s b;i + bi; f|i, «,,,-- fe,,,, f i-jИа че1ггежах иоказапы генератор / тактовых сигналов, делители 2-4 частоты, устройство 5 управления синхросигналами, блок 6 памяти микрокоманд (матрица), дешифратор 7 адресов микрокоманд (матрица), коммутаторы , блок 9 памяти адресов микрокоманд (матрица), дешифратор 10 кода адреса (матрица), коммутаторы 11 -11к2, блок 12 памяти команд (матрица), дешифратор 13 адресов команд (матрица), счетчик 14 адреса команд, устройство 15 управления счетчиком адреса команд, регистры 16, 17 и 18 сдвига, ключи 19-26, сумматор 27, регистр 28 сдвига, ключ 29, триггер 30, ключ 31, входы 82 и 33 и выход 34 машины, выход 35 генератора 1; цифрами 36 -55кь 37 -57к2 и 38i- 38к2 обозначены выходы делителей. Синхронизация узлов ЭВМ осуществляется сигналами, вырабатываемыми на выходах делителей и . Число внутренних состояний делителя 2 (коэффициент деления Kl), на вход которого поступают сигналы генератора / тактовых сигналов, должно быть равно числу бит, необходимых для представления длины ячеек (букв) обрабатываемых ЭВМ слов. Так, например, для обработки чисел, представленных в двоично-десятичной системе исчисления, коэффициент делении равен 4. Выходной сигнал делителя 2 поступает на вход делителя 3, число внутренних состояний К2 которого должно быть равно числу одновременно обрабатываемых в ЭВМ слов. Делитель 3 имеет К2 выходов ,37,-57к2 (Bi, BZ ... -Sk-v). Каждому состоянию делителя 3 соответствует наличие сигнала только на одном его выходе. Число внутренних состояний делителя 4, вход которого соединен с одним из выходов делителя 3, должно быть равно числу ячеек (разрядов), содержащихся в одном обрабатываемом слове. Делитель 4 имеет КЗ выходов 38i- 55к:; (Ci, Сг . . . Cks), сигналы из которых соответствуют определенному состоянию делителя. На фиг. 2 показана временная диаграмма выходных сигналов делителей для случая обработки трех 12-разрядных двоично-десятичных слов. Так как выходные сигналы делителей определяют моменты выработки сигналов Ззлами ЭВМ, то моменты времени могут быть соотнесены с совокупностью состояний (наличию выходных сигналов) делителей. Минимально возможный временной интервал ЭВМ равен продолжительности нахождения делителя 2 в одном состоянии Рбш:ее число таких моментов времени в одном цикле работы ЭВМ равно ХКЗ. Регистр 16 сдвига, ключ 19, регистры /7 и 18 сдвига, ключ 21, регистр 16 сдвига образуют цепь циркуляции слов. Общее количество двоичных разрядов в этих ре истрах равно К1ХК2ХКЗ, при этом число во1 Ч1гых разрядов регистра J8 равно К2, а регистра 16 - К1Х(К2-1), т. е. в егггстре 18 циркулируют К2 ячейки слова, в регистре 16 - на одну ячейку меньше. исло двоичных разрядов регистра 28 раво К1. Сумматор 27, регистр 28 сдвига, люч 24, сумматор 27 могут образовывать торую цепь циркуляции одной ячейки слоа, поэтому чпсло двоичных разрядов в репстре 28 равно KI. Так, напрпмер, для случая обработки рех 12-разрядных двоично-десятичных слов общее количество разрядов регистров будет равно 4X3x12 144, а количество двоичных разрядов регистров 16, }8 и 28 соответственно равно 12, 8 и 4. Как видно на фиг. 1, сигналы тактового генератора поступают одновременно H:I вход делителя 2 и на правление сдвигом информации в регистрах. При общем числе двоичных разрядов регистров, указанном выше, осуществляется равенство периодов пиркуляпии слов в регистрах 16, 17, 18 и периода следования выходных сигналов делителя 4, а также происходит синхронный сдвиг ячеек слова в регистрах по отношению к выходным сигналам синхронизации. Кроме того, выбор указанного выше числа двоичных разрядов в регистрах 16, 18 и 28 позволяет осуществлять поячеечный сдвиг слова влево или вправо. Это дает возможность, с одной стороны, однозначно определять в любой момент времени положение ячеек слова в разрядах регистров сдвига, а с другой, - привести в соответствие выходные сигналы синхронизатора и ячейки слова на выходах регистров сдвига. Таким образом, синхронная циркуляция слов позволяет осуществлять принцпп; момент времени определяет адрес ячейки слова. Напрпмер. можпо заранее установить, что сигналу Cj соответствует первая ячейка слова, Cg - вторая и так далее. И в то же время наличие сигнала BI соответствует первому разряду слова (а), сигнала Ва - второму разряду слова (Ь) и т. д. Совокупность сигналов BjCj соответствует / разряду / слова. Сигналы управления поступают с выхода матрицы 6, причем время появления любого сигнала однозначно онределяет номер ячейки слова и номер слова, над которым производится действие. Совокупность разрешающих (логическая 1) и запрещающих (логический 0) сигналов управления ключами, поступающих с выхода матрицы 6 в момент времени BjCj, является микрокомандой ЭВМ. Набор необходимых микрокоманд определяется «прошивкой матрицы 6. Выборка микрокоманды осуществляется с помощью дешифратора (матрицы) 7 по коду адреса микрокоманды, поступающему с коммутаторов 8i-8п. Как указывалось выше, время выборки микрокоманды однозначно указывает адрес ячеек слова, над которыми производится действие, определяемое этой микрокомандой. Формирование адресов микрокоманд в определенные моменты времени осуществляется с помощью матриц 9 и /О и коммутаторов 8 и //.

Предварительно введем понятие «синхропрограмма, определяемое как пабор микрокоманд в интервале времени, равном одному циклу работы ЭВМ.

Таким образом, синхропрограмма определяет последовательность выполнения микрокоманд в моменты времени BjCj в одном цикле ЭВМ при изменении i от 1 до К2 и / от 1 до КЗ, т. е. определяет характер обработки всех ячеек всех слов в одном цикле работы ЭВМ.

Формирование микропрограммы осу иествляется с помощью матриц 9 н 10 и коммутаторов. При этом матрица 10 дешифрирует код адреса синхропрограммы, з результате чего в матрице 9 ироисходит выборка кодов адреса микрокоманд. Порядок выборки адресов микрокоманд определяется синхросигналами, поступающими на управляющие входы коммутаторов. Изменение кода адреса микрокоманды происходит как при иереключении коммутаторов // по сигналам делителя 5 путем изменения выборки входной шины матрицы 9, так и при переключении коммутаторов 8 по сигналам делителя 4 путем изменения выходных шин матрицы 9 при фиксированной выбранной шине.

Код адреса сиихропрограммы устанавливается па время, равное одному циклу работы ЭВМ. В момент времени BiCj код синхропрограммы через коммутатор /У поступает на дешифрацию, в результате чего выбирается одна из шин групповых входов матрицы 9. Считанные сигналы, соответствующие выбранной шине, с матрицы 9 поступают на коммутаторы 5i-5гг. Однако на вход матрицы 7 поступают сигналы (адрес микрокоманды) только с выхода коммутатора S. В следующий момент времени (B2Ci) выбирается другая шина матрицы 5, в результате чего на выходах коммутатора 8i вырабатывается другой адрес микрокоманды. Аналогично формируется ад1)ес микрокоманд для моментов времени ВзС . .. ВкаСь BiC2, В2С2 . .. Вк2С2, BiCs ... и т. д.

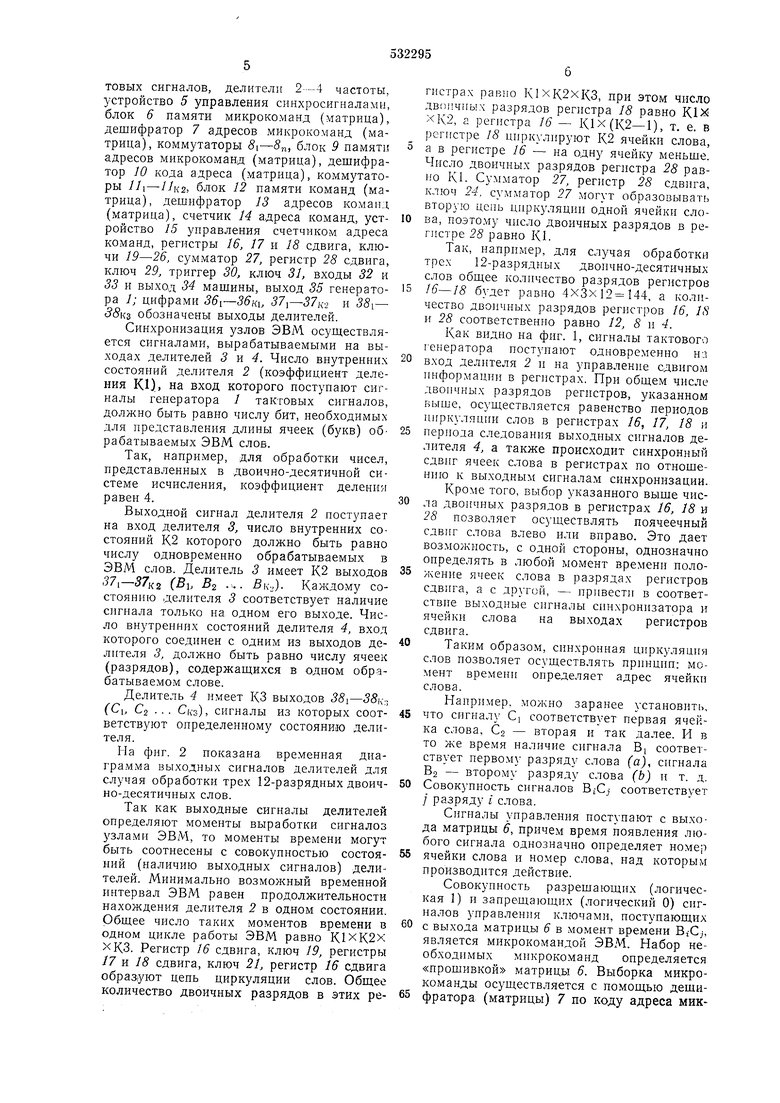

В общем случае в процессе составления программ работы ЭВМ необходимо в одном цикле иметь различные микрокоманды для каждой ячейки слова. Число коммутаторов должно быть равно числу обрабатываемых ячеек слова (КЗ). При этом управляющий вход каждого коммутатора должен быть соединен с соответствующим выходом делителя 4. Однако это приводит к увеличению аппаратурных затрат в результате увеличения числа коммутаторов п увеличения размеров матрицы 9. Очень часто, особенно при обработке цифровой информации, в программах решения задач

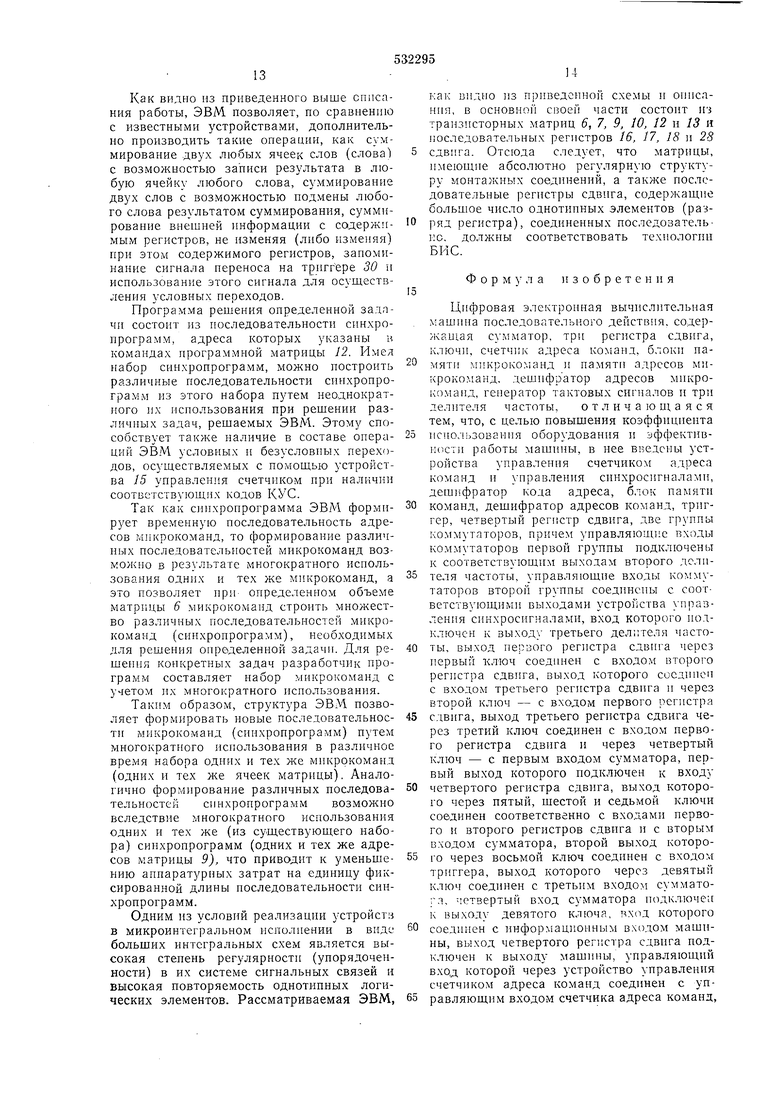

используются одни и те же микрокоманды для различных ячеек слова. Например, для формата 12-разрядного числа, показанного на фиг. 3, целесообразно для разрядов, соответствующих мантиссе числа, использовать одни и те же команды. В этом случае число коммутаторов 8 сокращается до шести (вместо 12) и соответственно пропорционально уменьшается матрица 9. При этом на коммутаторе 8, онределяющем момент

обработки мантиссы числа, поступает сигнал с выхода устройства 5 управления, получаемый в результате объединения по схеме ИЛИ соответствующих выходных сигналов делителя 4.

Па фиг. 4 представлен формат синхроирограммы для случая трех (а, Ь, с) 12-разрядных слов. Формирование адреса синхроирограммы осуществляется с помощью матриц 12 и 13, счетчика 14 адреса команд и

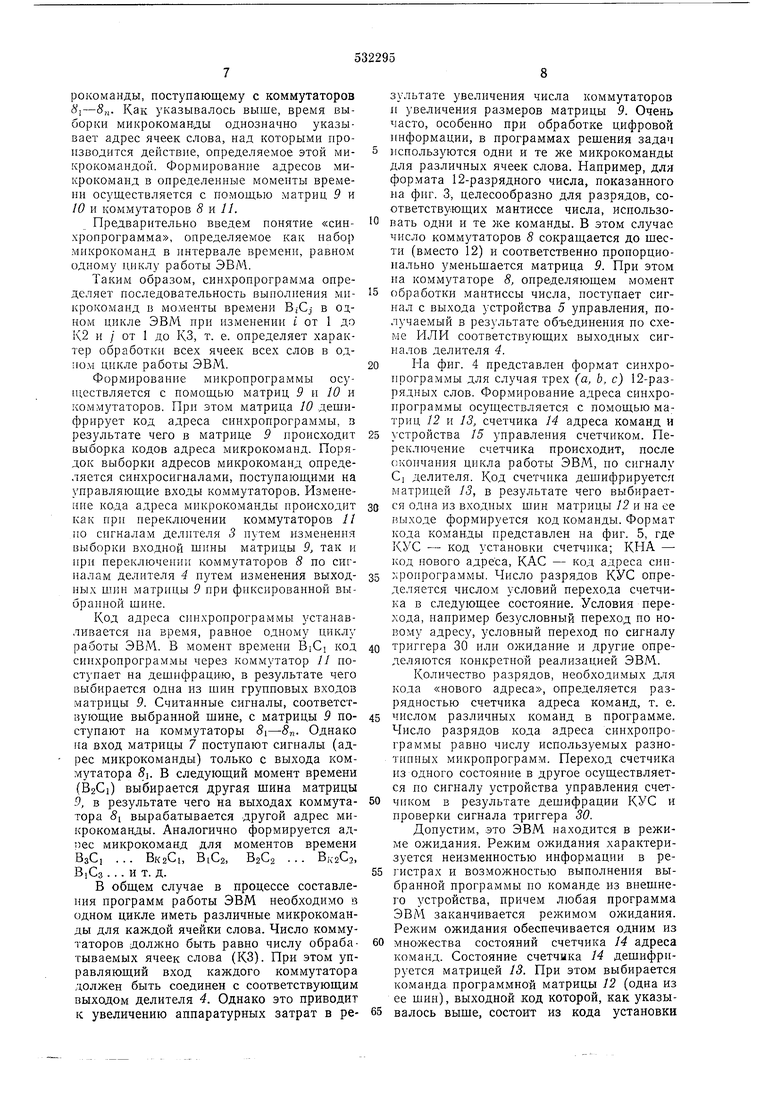

устройства 15 управления счетчиком. Переключение счетчика происходит, после окопчания цикла работы ЭВМ, по сигналу С делителя. Код счетчика дешифрируется матрицей 13, в результате чего выбирается одна из входных шин матрицы 12 и на ее выходе формируется код команды. Формат кода команды иредставлен на фиг. 5, где КУС - код установки счетчика; КПА - код нового адреса, КАС - код адреса синхропрограммы. Число разрядов КУС определяется числом условий перехода счетчика в следующее состояние. Условия перехода, например безусловный переход по новому адресу, условный переход по сигналу

триггера 30 или ожидание и другие определяются конкретной реализацией ЭВМ.

Количество разрядов, необходимых для кода «нового адреса, определяется разрядностью счетчика адреса команд, т. е.

числом различных команд в программе. Число разрядов кода адреса синхропрограммы равно числу используемых разнотипных микропрограмм. Переход счетчика из одного состояние в другое осуществляется по сигналу устройства управления счетчиком в результате дешифрации КУС и проверки сигнала триггера 30.

Допустим, это ЭВМ находится в режиме ожидания. Режим ожидания характеризуется неизменностью информации в регистрах и возможностью выполнения выбранной программы по команде из внешнего устройства, причем любая программа ЭВМ заканчивается режимом ожидания. Режим ожидания обеспечивается одним из

множества состояний счетчика 14 адреса команд. Состояние счетчика 14 дешифрируется матрицей 13. При этом выбирается команда программной матрицы 12 (одна из ее шин), выходной код которой, как указывалось выше, состоит из кода установки

счетчика, кода адреса следующей команды (кода нового адреса) и кода адреса сннхропрограммы. Режим ожидания ЭВД обеспечивается кодом установки счетчика, который поступает на устройство 15 управления счетчиком, анализирующим я выдающим на счетчнк 14 сигнал разрещения приема нового адреса (адреса следующей команды) и разрешения приема начального адреса, постуиающего извне. Код нового адреса в режиме ожидания долже1 совпадать с кодом счетчика, по которому выбрана эта команда, т. е. все время до прихода кода начального адреса выбирается одна и та же команда матрицы 12. Код нового адреса поступает на счетчик 14 с выхода матрипы 12 и заносится в счетчик 14 один раз за цикл работы ЭВМ по сигналу С| (начало цикла), ноступающему с одного из выходов делителя 4. Начало цикла совпадает с моментом времени CiBi, поэтому в момент времени Bi код адреса синхропрограммы с выхода матрицы 12 посту пает на матрицу 10 через коммутатор 11,. Матрица W, являясь дещифратором адреса, выбирает одну из множества шин матрицы 9. В момент времени С через коммутатор §1 выходной код матрицы 9 иостуиает на вход матрицы 7, с помощью которой выбирается одна из щин матрицы 6. Матрица 6 выдает код микрокоманды, которая в случае режима ожидания обеспечивает циркуляцию информации в регистрах, т. е. сохраняет ее без изменения. Для этого микрокоманда обеспечивает выдачу разрещающих сигналов, в момент времени CiBi на ключи 19, 21 и 24, что обеспечивает иродвнжение информации из одного регистра в другой. В момент времени CiBj код адреса синхропрограммы поступает на матрицу 10 через коммутатор llz, которая вы6iipaeT другую щину матрицы 9, причем выходной код последней в режиме ожидания одинаков с кодом, выбранным в момент времени CiBi, поэтому выбирается та же микрокомаида (микрокоманда циркуляции). Аналогично производится выборка адресов микрокоманд в любой из моментов времени. Так как в режиме ожидан11Я информации в регистрах должна сохраняться, то в каждый из моментов времени C;Bi должна выбираться одна и та же микр.команда циркуляции.

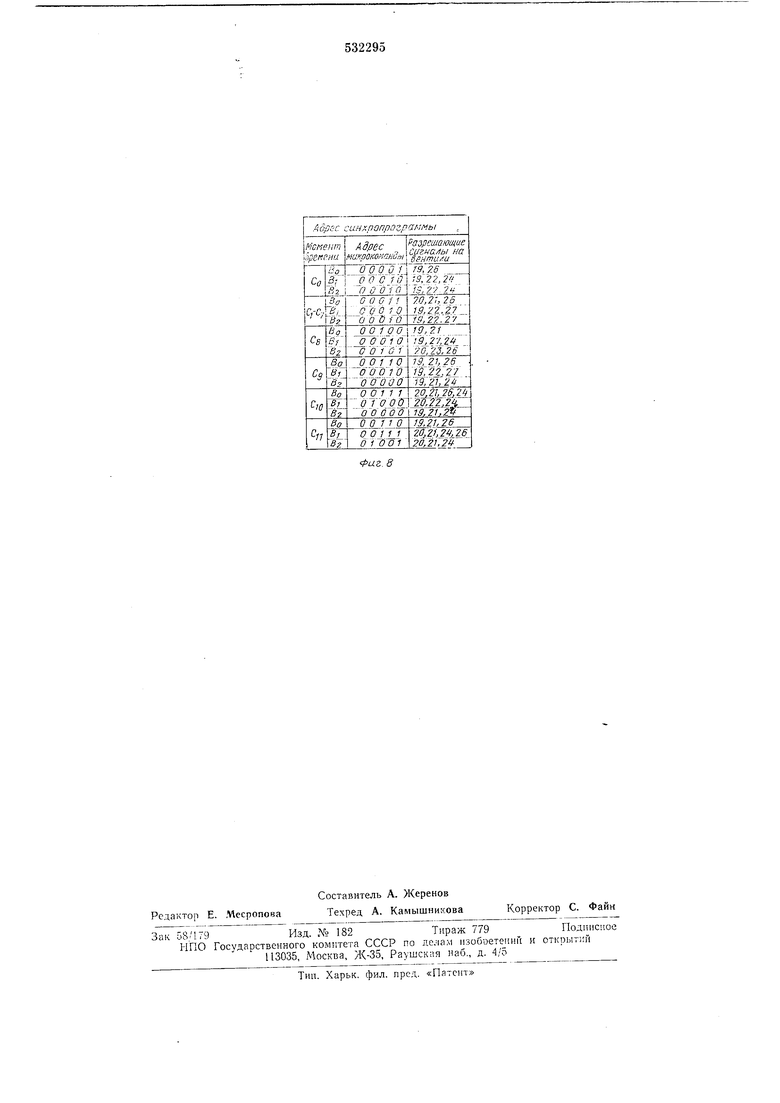

Формат синхроирограммы для обеспечения режима циркуляции для случая трех 12-разрядных слов показан на фиг. 6.

Любая программа ЭВМ начинается подачей из внещнего устройства по входу 32 начального адреса программы на счетчяк 14 адреса команд. Так как в режиме ожидания выдается сигнал разрешения приема начального адреса, то в момент времени CiBi выбранный начальный адрес программы записывается в счетчик 14 и дещифрируется матрицей 13, которая выбирает одну из множества щин матрицы 12. Выбранная щина матрицы 12 содержит коды условия перехода (КУС), например безусловный переход, новый адрес (НА), т. е. адрее, на который должен быть осуществлен переход в следующем цикле (обороте) работы ЭВМ, и код адреса синхропрограммы, определяющий с учетом матрицы 6 микрокоманд действие, которое долнчно быть выиолнено над содержимым регистров в течение данного цикла работы ЭВМ. Действие, которое должно быть выполнено над содержимым регистров в течение данного цикла работы, оиределяется набором микрокоманд. которые выбираются, как было онисано выще, для режима циркуляции. При этом в каждый момент времени могут выбираться любые микрокоманды из всего существующего для данной ЭВМ набора микрокомаид.

Предположим, что для случая тре.к (а, Ь, с) 12-разрядиых щестнадцатиричных слов необходимо ио данной команде матрицы 12 выполнять следующие действии

над содержимым регистров

- ai 0, , С9 0, Ь, Ci, л 1-8,

aiO+fll Cli. fl,,,- Ью- + 12 Ci2,

где Oi 0 - в первый разряд слова

(о) заппсать

Сд О, «9 О - в девятый разряд слор (а) п (с) записать

-

Ь - сдвиг слова (Ь) на один разряд вправо;

о, ....8 - одвиг 1-8 разрядов слова (и) на один разряд влево;

-

- сдвиг 1-8 разрядов слова (с) на один разряд вправо;

u(, + hi - десятый разряд слова (о) сложить с одиннадцатым разрядом слова (Ь) II результаг заппсать в одиннадцатый разряд слова (с);

fiio- bio - содержимое десятого

разряда слова (а) записать в десятый разряд слова (Ь);

Oi2-fbi2 r;; - двенадцатый разряд слова (о) сложить с

двенадцатым разрядом слова (Ь) и результат записать в двенадцатый разряд слова (с).

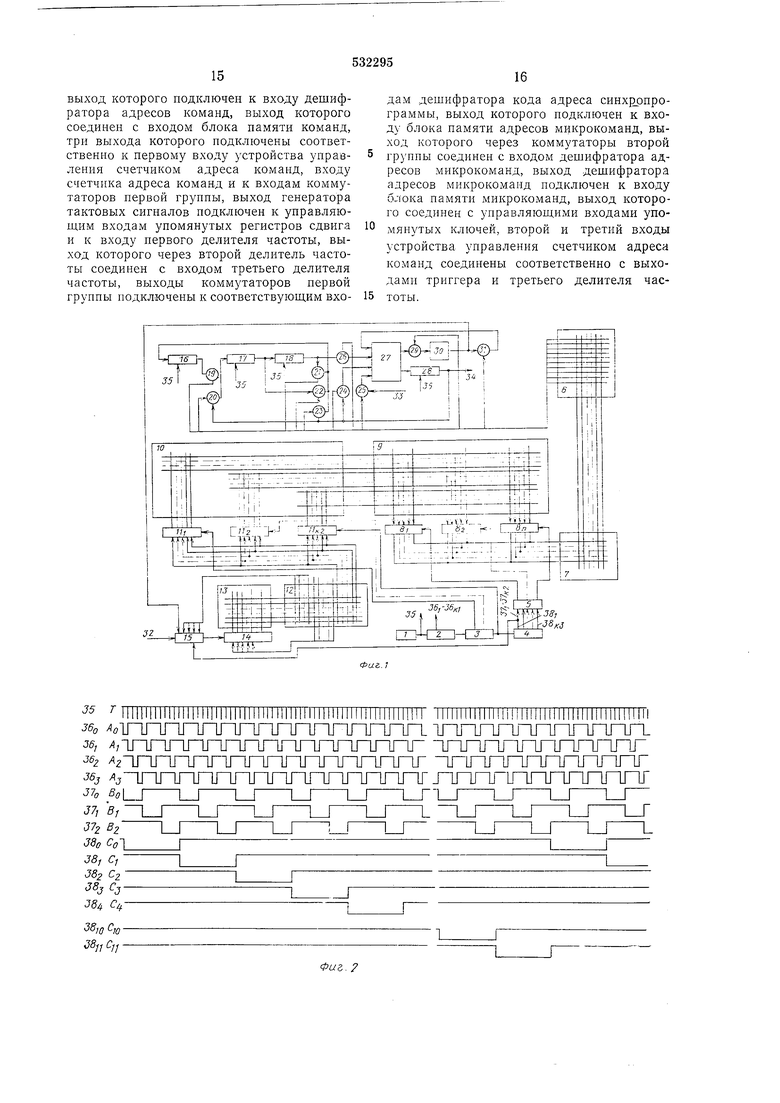

Информация в регистрах в момент времени CiBi расположена, как показано на фиг. 7, а продвижение информации из ячейку в ячейку, например из ячейки (а) в (с), осуществляется за время меладу моментами времени C|Bi и CiB2, причем за

это время сдвигаются все четыре бита одного разряда. Запись нуля в первый разряд слова (а) и девятый разряд слова (а) и (с) осуществляется запретом в моменты времени CiB., CgBi, СдВз связи выхода регистра 18 с входом регистра }6 (отсутствуют разрешающие сигналы на ключе 21 в указанные моменты времени). При этом для сохранения остальной информации в эти моменты времени необходимо подавать разрешающие сигналы на ключ 19. Сдвиг слова (Ь) на один разряд вправо осуществляется путем подачи разрешающих сигналов в моменты времени CiBj, С2В2, СзВг . . . Ci2B2 на ключ 22, при этом разрешающий сигнал в эти моменты времени на ключе 21 должен отсутствовать. Аналогично осуществлятся сдевиг 1-8 разрядов слова (с), только разрешающий сигнал на ключ 22 подается в моменты времени , С2Вз, СзВз . . . СдВз. Сдвиг 1-8 разрядов слова (а) влево осуществляется с помощью сумматора. Для этого в момент времени CiBj подается разрешающий сигнал на ключ 26 и содержимое первого разряда слова (а) записывается в сумматор. В моменты времени CiB2 и С|Вз подаются разрешающие сигналы на ключ 24, обеспечивая циркуляцию содержимого первого разряда слова (а) в кольце сумматор - регистр 28. В момент времени CjBi подается разрещающий сигнал на ключ 20 и содержимое регистра 28 (первый разряд слова (а) переписывается в регистр 77. Аналогично осуществляется адвиг влево остальных разрядов слова (а). Запись содержимого десятого разряда слова (а) в десятый разряд слова (Ь) осуществляется также с помощью сумматора. Для этого в момент времени СюВ подается разрешающий сигнал на ключ 26 и содержимое десятого разряда, регистра (а) переписывается в сумматор, а затем - в регистр 28. В момент времени CioB2 подается разрешающий сигнал на ключ 23. В этот момент времени на выходе регистра J8 будет десятый разряд слова (Ь), и содержимое регистра 28 переписывается в регистр 16.

Таким образом, осуществляется подмена содержимого десятого разряда слова (Ь) содерл имым десятого разряда слова (а).

Суммирование десятого разряда слова (а) с одиннадцатым разрядом слова (Ь) (йю + Ьц - Сц) И запись результата суммирования в одиннадцатый разряд слова (с) производится следую щим образом: так как в момент времени CjoBi был подан разрешающий сигнал на ключ 26, то в момент времени CiQB2 необходимо подать разрешающий сигнал на ключ 25 для осуществления циркуляции сумматор - регистр 28 и подавать этот сигнал в моменты времени СюВз, СцВь т. е. до прихода одиннадцатого разряда слова (Ь). Одиннадцатый разряд слова (Ь) будет на выходе регистра J8 в момент времени CiiB2. В этот момент времени необходимо подать разрешающий сигнал на ключ 26.

Таким образом, на одном из входов сумматора будет содержимое одиннадцатого разряда регистра (Ь), а на другом (так как в кольце сумматор-регистр 28 находилось содержимое десятого разряда слова (а) -

десятый разряд слова (а). Сумма а + Ьи с выхода регистра 28 в момент времени СцВз через ключ 23, на который необходимо подать разрешающий сигнал, переписывается Б регистр 16. На выходе регистра 18

в этот момент времени будет одиннадцатый разряд слова (с), но разрешающего сигнала на ключе 21 нет, поэтому через ключ 23 будет осуществляться подмена содержимого одиннадцатого разряда слова

(с) результатом суммирования аю + бц. Суммирование двенадцатого разряда словя (а) и двенадцатого разряда слова (Ь) производится аналогично.

Формат описанной выше синхропрограммы и последовательность разрещающих сигналов на ключах показаны на фиг. 8.

По окончании цикла работы ЭВМ по сигналу С в счетчик 14 переписывается адрес следующей команды (новый адрес).

Предположим, что следующая команда программы содержит КУС, соответствующий условному переходу по сигналу триггера 30, причем этот сигнал вырабатывается при суммировании содержимых ячеек

слов, если результат суммирования больше пятнадцати, и не вырабатывается, если результат меньше или равен пятнадцати, при наличии в этот момент времени разрешающего сигнала на ключе 29. Сигнал триггера 30 поступает в устройство 15 управления счетчиком, и в следующем цикле работы ЭВМ в счетчик 14 записывается либо «новый адрес при наличии сигнала, либо к его содержимому прибавляется 1 .з

случае отсутствия сигнала.

Кроме того, сформированный сигнал может быть использован как сигнал переноса в следующую или любую другую ячейку при наличии в данный момент разрешающего сигнала на ключе 31.

Внешняя информация подается на сумматор при наличии разрещающего сигнала на ключе 25 и может быть просуммирована с содержимым любой ячейки или записана без изменений в любую ячейку. Результат обработки выдается на внещнее устройство с выхода 34. Синхроирограммы для конкретного варианта ЭВМ выбирают

при разработке ее математического обеспечения, учитывая при разработке универсальность синхропрограмм, т. е. возможность многократного использования синхропрограмм при решении различных заданных для данного варианта ЭВМ программ.

13

Как видно из приведенного выше списания работы, ЭВМ позволяет, по сравнению с известными устройствами, дополнительно производить такие операции, как суммирование двух любых ячеек слов (слова с возможностью записи результата в любую ячейку любого слова, суммирование двух слов с возможностью подмены любого слова результатом суммирования, суммирование внешней информации с содержимым регистров, не изменяя (либо изменяя) при этом содержимого регистров, запоминание сигнала иереноса на триггере 30 и использование этого сигнала для осуш,ествлення условных переходов.

Программа решения определенной задачи состоит из последовательности синхропрограмм, адреса которых указаны н командах программной матрицы 12. Имел набор синхропрограмм, можно построить различные последовательности синхропрограмм из этого набора путем неоднократного их использования при решении различных задач, решаемых ЭВМ. Этому способствует также наличие в составе операций ЭВМ условных и безусловных переходов, осуществляемых с помощью устройства 15 управления счетчиком ири наличии соответствующих кодов КУС.

Так как сиихронрограмма ЭВМ формирует временную последовательность адресов микрокоманд, то формирование различных последовательностей микрокоманд возможно в результате многократного использования одних и тех же микрокоманд, а это позволяет ири определенном объеме матрицы 6 микрокоманд строить множество различных последовательностей микрокоманд (синхропрограмм), необходимых для решения определенной задачи. Для решения конкретных задач разработчик программ составляет пабор микрокоманд с учетом их многократного использования.

Таким образом, структура ЭВМ позволяет формировать новые последовательности микрокоманд (сиихропрограмм) путем многократЕюго использования в различное время набора одних и тех же микрокомаид (одних и тех же ячеек матрицы). Аналогично формирование различных последовательностей синхропрограмм возможно вследствие многократного использования одних и тех же (из существующего набора) синхропрограмм (одних и тех же адресов матрицы 9), что приводит к уменьшению аппаратурных затрат на единицу фиксированной длины иоследовательности синхропрограмм.

Одним из условий реализации устройств в микроинтегральном исполнении в виде больших интегральных схем является высокая степень регулярностп (упорядоченности) в их системе сигнальных связей и высокая повторяемость однотипных логических элементов. Рассматриваемая ЭВМ,

14

как видно из приведенной схемы и опислния, в основной своей части состонт из транзисторных матриц 6, 7, 9, 10, 12 и 13 и 1 оследовательных регистров 16, 17, 18 и 25 сдвига. Отсюда следует, что матрицы, имеющие абсолютно регулярную структуру монтажных соединений, а также последовательные регистры сдвига, содержащие большое число однотииных элементов (разряд регистра), соединенных последовательно, должны соответствовать технологии БИС.

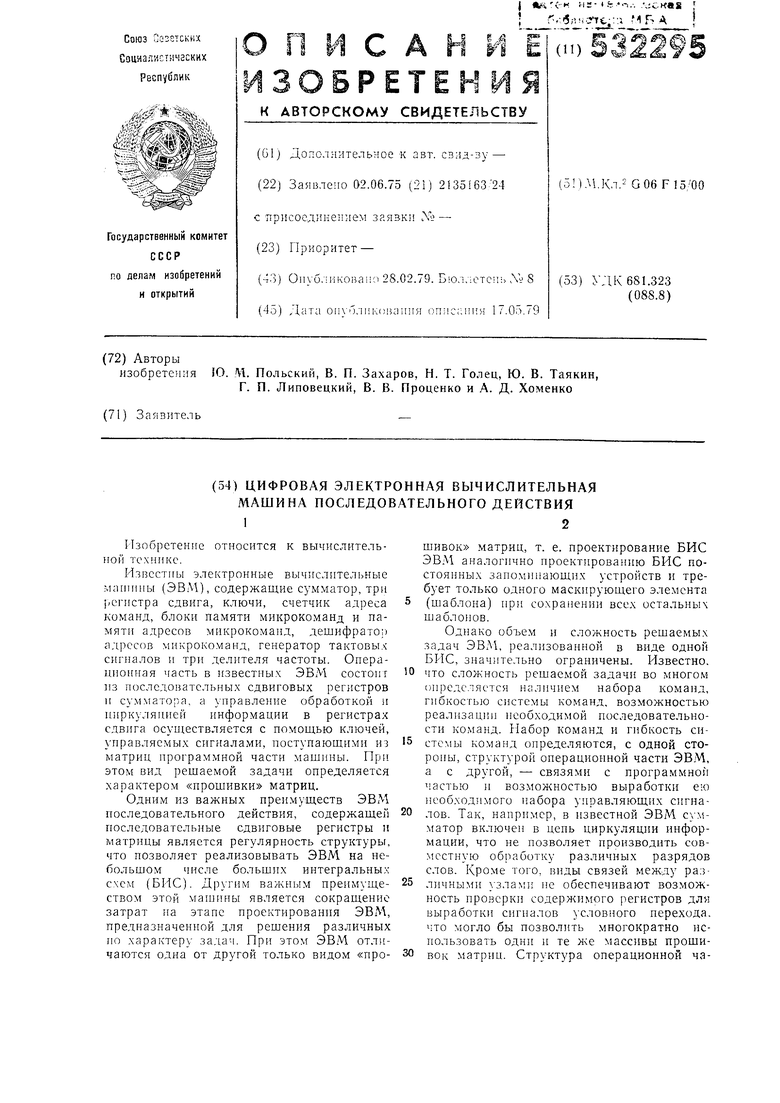

Формула изобретеиия

Цифровая электроиная вычислительная машина последовательного действия, содержащая су.мматор, три рег)стра сдвига, ключи, счетчик адреса команд, б.оки иамятн микрокоманд и памяти адресов микрокоманд, дешифратор адресов микрокоманд, генератор тактовых сигналов и три дел1ггеля частоты, отличающаяся тем, что, с целью повышения коэффициеита

использования оборудования и эффективности работы мащины, в нее введены устройства управления счетчиком адреса команд и управления синхросигналами, дешифратор кода адреса, блок памяти

команд, дещифратор адресов команд, триггер, четвертый регистр сдвига, две группы коммутаторов, причем управляющие входы коммутаторов первой группы подключены к соответствующпм выходам второго дслителя частоты, управляющие входы ко.мутаторов второй группы соединены с соответствующими выходами устройства управления синхросигналами, вход которого подключен к выходу третьего делителя частоты, выход первого регистра сдвига через первый ключ соединен с входом второго регистра сдвига, выход которого соединен с входом третьего регистра сдвига и через второй ключ - с входом первого регистра

сдвпга, выход третьего регистра сдвига через третий ключ соединен с входом первого регистра сдвига и через четвертый ключ - с первым входом сумматора, первый выход которого подключен к вход}

четвертого регистра сдвига, выход которого через пятый, щестой и седьмой ключи соединен соответственно с входами первого и второго регистров сдвига и с вторым входом сумматора, второй выход которого через восьмой ключ соединен с входом триггера, выход которого через девятый ключ соединен с третьнм входом сумматогл, четвертый вход сумматора нодк.тючеп к выходу девятого ключа, вход которого

соединен с информационным входом машины, выход четвертого регистра сдвига иодключеп к выходу машины, уиравляющий вход которой через устройство управлеиия счетчиком адреса команд соединен с управляющим входом счетчика адреса команд, выход которого подключен к входу дешифратора адресов команд, выход которого соединен с входом блока памяти команд, три выхода которого подключены соответственно к первому входу устройства управления счетчиком адреса команд, входу счетчика адреса команд и к входам коммутаторов первой группы, выход генератора тактовых сигналов подключен к управляющим входам упомянутых регистров сдвига и к входу первого делителя частоты, выход которого через второй делитель частоты соединен с входом третьего делителя частоты, выходы коммутаторов первой группы подключепы к соответствующим входам дешифратора кода адреса синх1К)программы, выход которого подключен к входу блока памяти адресов микрокоманд, выход которого через коммутаторы второй группы соединен с входом дешифратора адресов микрокоманд, выход дешифратора адресов микрокоманд подключен к входу блока памяти микрокоманд, выход которого соединен с управляющими входами упомянутых ключей, второй и третий входы устройства управления счетчиком адреса команд соединены соответственно с выходами триггера и третьего делителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровая электронная вычислительная машина последовательного действия | 1976 |

|

SU658564A2 |

| Цифровая электронная вычислительная машина последовательного действия | 1976 |

|

SU678486A2 |

| Цифровая электронная вычислительная машина последовательного действия | 1976 |

|

SU654948A2 |

| Электронные часы | 1980 |

|

SU928169A1 |

| Цифровая электронная вычислительная машина последовательного действия | 1976 |

|

SU591076A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

1П1 Т 1Г1ПО Ъ 1 ЛПГ1ПП1 П 1ППГиЛППППГ П

71ППГ 1Г 1Г 1Г ЛППГ и1Г 1Ги 1ПГ1П-Ги-1ПГ

2 2 и 1ПГ1ПЛГ1Г1Г 1Г1ГТГ Л и 1ППГЛГ1Ги 1ППГ 3 jnrYnJ ririr lOrinr rU irirJ irinj LnnrLririr rT

37о

}8o

J8j с, J82 с 2

ОJ5-J Cif. CIQ J8jj Cjj Мантиссамантиссыпорядка

КУС

Знак По/ГяЗок Знак

Т9 21 2

(П} OJ) о о о 9, 21, 2 б Г9, 21, Л

, .4

о о

рУ-й,

T)J) о о о 9, 21,2 /5,2Vlij

о оа о о

В2

о о 19, 21. 2«

О

Г, 1J, 19, 21. 2Ч О Оо оо

l№«,//H Adflec ,

СБ

Sol

Сз Bl

в

Во

Ж -ia;

Cw

41

О О 1 О G 0,21

00 1 (71 У5/2г г.«

ff о ICil 0,23,26

19, 21,26 W, IX2 7 , 2;, 2«

20,Zl2S, ,2, W,21,2V

Авторы

Даты

1979-02-28—Публикация

1975-06-02—Подача