мене информацией с внешними устройствами работает обычно в монопольном режиме и для передачи данных необходима лишь одна группа шин интерфейса (от внешнего устройства к каналу или от канала к внешнему устройству), в предлагаемом селекторном канале при установлении монопольного режима передачи данных обратная группа информационных шин используется для передачи контрольной информации. Синхронизация передачи контрольной информации осупдествляется но управляющим сигналам канала и внешнего устройства.

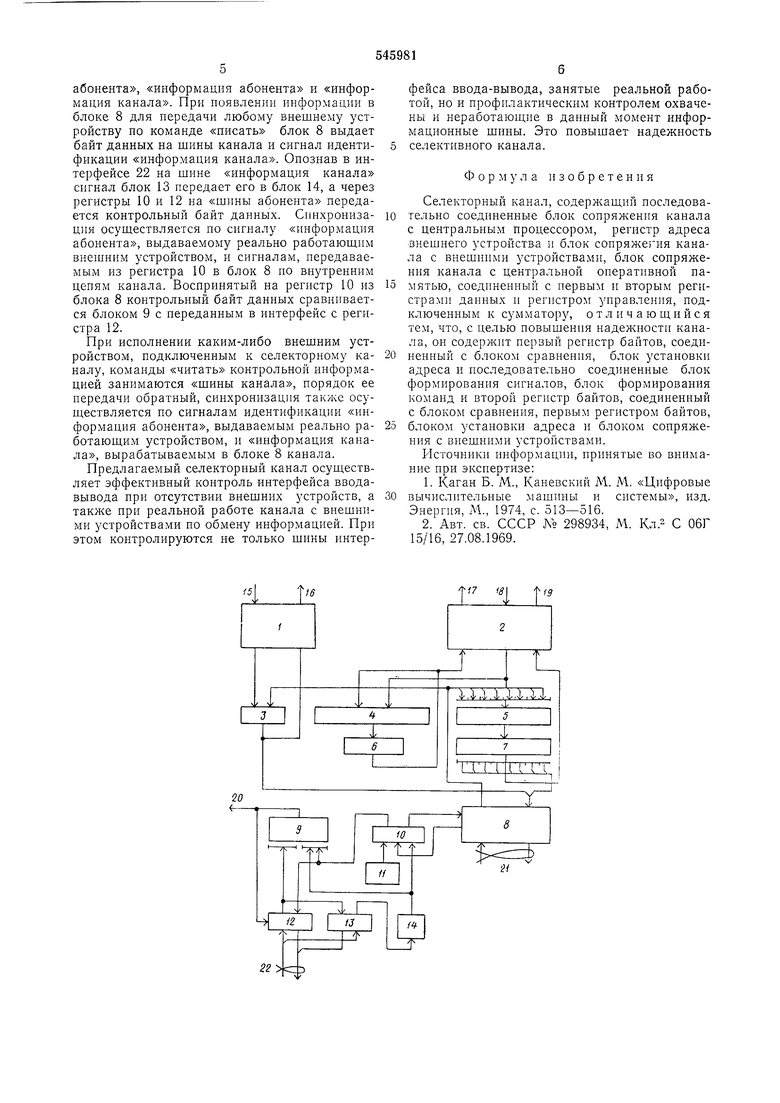

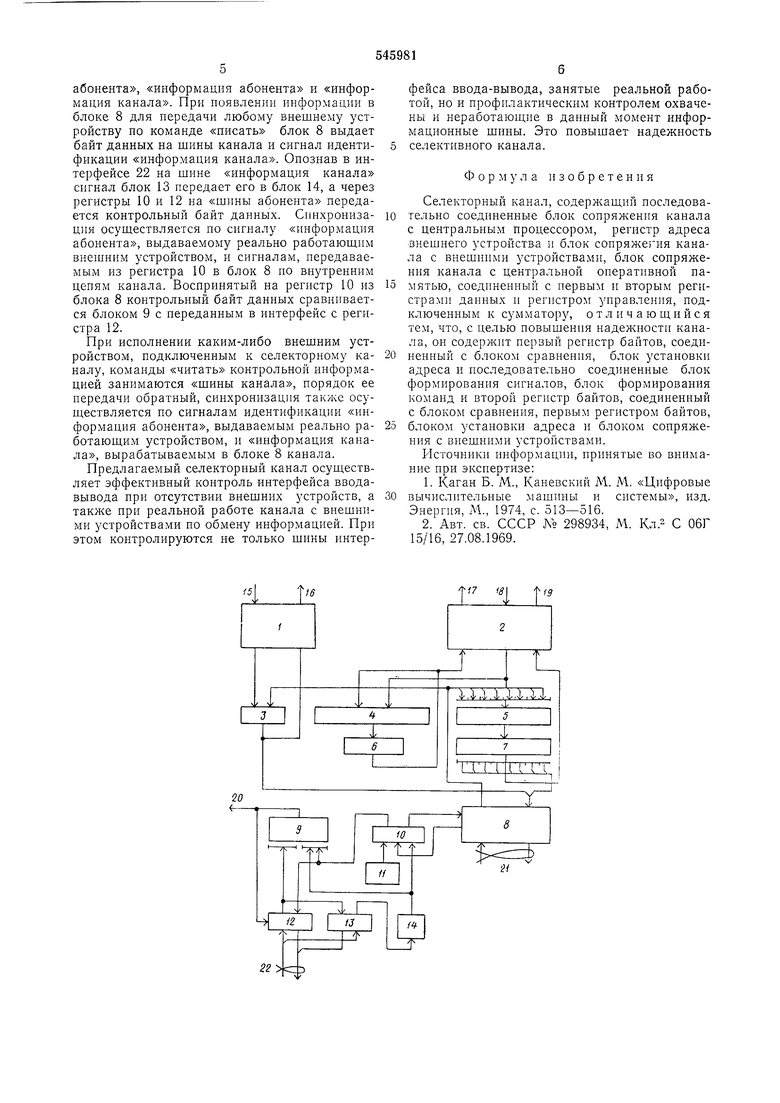

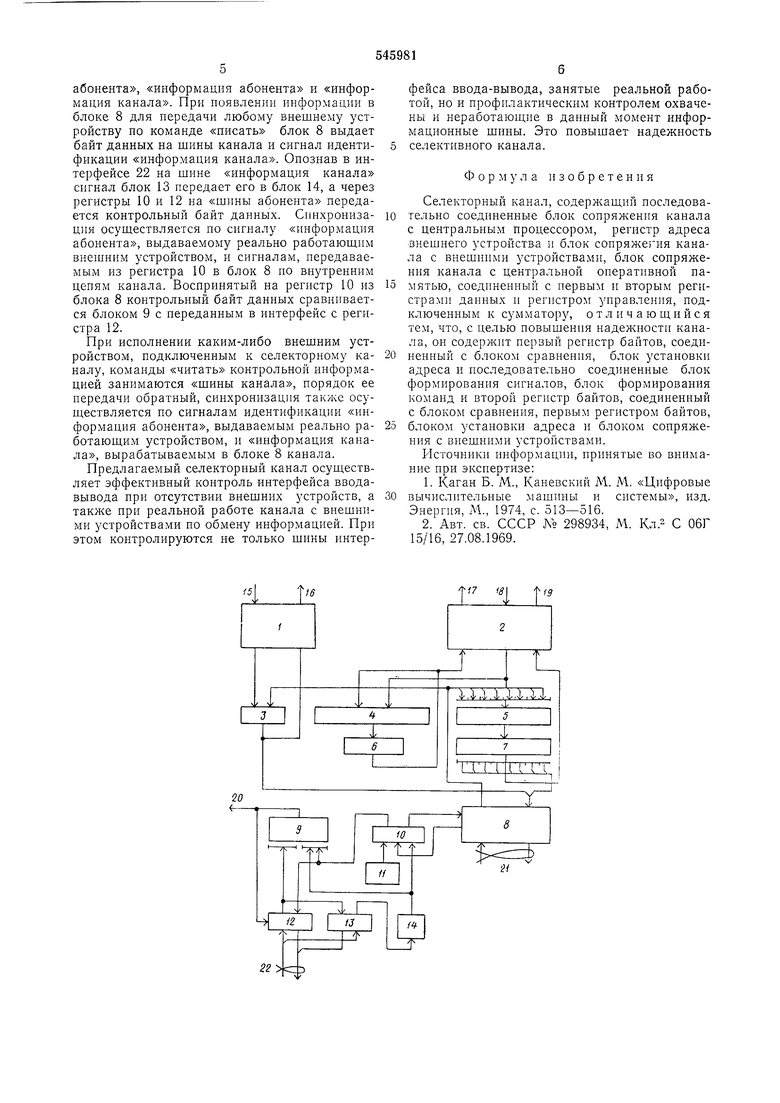

На чертеже прнведега структурная схема селекторного канала.

Селекторный канал содержит блок 1 сопряжения канала с центральным процессором, блок 2 сопряжения канала с центральной оперативной памятью, регистр 3 адреса внешнего устройства, регистр 4 управления, фиксирующий адреса команды и данных и счет данных, первый регистр 5 данных, сумматор 6, второй регистр 7 данных, блок 8 сопряжения с внепь нпми зстройствамп, блок 9 сравнення, первый регистр 10 байтов, блок 11 установки адреса, второй регнстр 12 байтов, блок 13 формирования сигналов п блок 14 формирования команд.

Подключение селекторного канала в вычислительной системе происходит с помощью следующих шин связн: входных шин 15 передачи инструкций; выходиых шин 16 выдачи кодов условий и прерываний; выходны.х шин 17 адреса ячейки центральной оперативной памяти; входных шин 18 информации; выходных шин 19 информацнн; шипы 20 выдачи сигнала ошибки и интерфейса 21 и 22 ввода-вывода.

Устройства управления внешними устройствами (УВУ) или внешние устройства подключаются к селекторному каналу с помощью интерфейса ввода-вывода 21 по стандартной схеме. Отличие состоит в том, что вход 22 канала дополнительно соединен с УВУ, последним в последовательной цепочке устройств. Селекторный канал управляется инструкциями и выполняет все операцни, определяемые системой команд ЕС ЭВМ.

В известных режимах по обмену информацией между центральной оперативной памятью и внешними устройствами работа селекторрюго канала сводится к следующему.

При иостуилении от процессора в канал но шинам 15 инструкции «начать ввод-вывод блок 1 сопряжения с центральиым процессором выдает признак инструкции и код номера внешнего устройства для фиксации на регистре 3 адреса внешнего устройства. Через блок 2 производится прием в канал адресного слова канала и по нему - управляющего слова канала с фиксацией их на регистре управления 4. Модификация адресов ячеек центральной оперативной памяти осуществляется сумматором 6, обмен данными с внешними устройствами через первый 5 и второй 7 регистры данных. Параллельно с приемом в канал управляющей информации по адресу, находящемуся

на регистре 3, через блок 8 сопряжения с внешними устройствами и интерфейс 21 вводавывода производится начальная выборка внешнего устройства, обмен с ним служебной информацией и пересылка ему кода команды. При правильном теченгщ оиерации соответствуюидий код условия формируется в блоке 1 и через шины 16 выдается в центральный процессор. Далее без разрыва логической связи между каналом и внешним устройством производится обмен данными в монопольном режиме. При исполнении команды «читать принятые от внешнего устройства через блок 8 байты данных формируются в слова на регистре 5

п по мере сформирования нереписываются на регистр 7, передаются в блок 2 и далее через шииы 19 - в центральную оперативную память. Адрес ячейки выдается из блока 2 па шипы 17. По команде «писать пнформация

пословно через шины 18 (адрес на шииах 17) поступает в блок 2, переписывается на регистр 5, регистр 7 и далее побайтно через блок 8, интерфейс 21 передается внешнему устройству. Обмен данными с внешним устройством продолжается пока счет даиных, зафиксированный на регистре 4 и модифицированный в процессе передачи данных сумматором 6, не станет равным нулю. В наладочном режиме селекториый канал

исиолпяет тестовую программу, при этом блоки 9, 11, 13 и 14 и регистры 10 и 12 работают как внешнее устройство, а работа остальных блоков канала в основном не отличается от описанной. Адрес из блока 11 установки адреса через первый регистр 10 байтов выдается в блок 8, интерфейс 21 (22) и поступает на второй регистр 12 байтов по последовательности начальной выборки. При сравнении блоком 9 выданного и принятого адресов в интерфейс

22 выдается ответный адрес, который через блок 8 принимается на регистр 10 и также сравнивается блоком 9. Блок 14 формирования команд выдает через регистр 10, блок 8 нервую команду (наиример, «читать) через интерфейс 21 (22). В ответ блок 14 формирует нулевой байт состояния, который воспринимается через интерфейс 21 блоком 8. Далее блок 14 продолжает формировать контрольные байты данных, пересылая их по команде «читать

через регистр 10, блок 8, интерфейс 21 (22) на регистр 12, а по команде «писать через регистр 10, регистр 12, интерфейс 22 (21), блок 8 на регистр 10. В обоих случаях после пересылки очередного байта данных содержимое регистра 10 и 12 сравнивается блоком 9. При сравнении тест нродолжается, нри несравнении сигнал ошибки выдается на шину 20.

При работе канала с реальным внешним устройством в предлагаемом канале шины интерфейса ввода-вывода, незанятые передачей ииформации, используются для профилактического (предварительного) контроля. В контрольном режиме блок 13 формирования управляющих сигналов постоянно анализирует

состояние управляющих шин: «требование

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал | 1976 |

|

SU590725A2 |

| Мультиплексный канал | 1974 |

|

SU525941A1 |

| Мультиплексный канал многопроцессорной вычислительной системы | 1973 |

|

SU521559A1 |

| Система обмена | 1978 |

|

SU809138A1 |

| Мультиплексный канал | 1975 |

|

SU561955A1 |

| Мультиплексный канал | 1973 |

|

SU525079A1 |

| Мультиплексный канал | 1977 |

|

SU750469A1 |

| Устройство для сопряжения внешних устройств с каналом ввода-вывода | 1975 |

|

SU552603A1 |

| Блок-мультиплексный канал | 1977 |

|

SU691841A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

Авторы

Даты

1977-02-05—Публикация

1975-05-26—Подача